傳統觀點認為,如果您非常關心延遲,那么嘗試將系統內存連接到 PCI-Express 總線并不是一個好主意。因為內存離 CPU 越遠,延遲就越高,這就是內存 DIMM 通常盡可能靠近插槽的原因。

從邏輯上講,PCI-Express 是千里之外的。隨著每一代 PCI-Express 帶寬翻倍,如果沒有重定時器的幫助也會增加延遲,它可以傳輸的距離也會縮短。對于我們習慣于連接到 PCI-Express 的大多數類型的內存來說,這不是什么大問題。閃存存儲的延遲以幾十微秒為單位的情況并不少見,這使得互連產生的額外幾百納秒成為一個有爭議的問題。然而,我們對DDR 和其他形式的易失性存儲器就沒有那么寬容了。

以前的內存擴展嘗試都陷入了妥協,特別是在延遲方面。例如,GigaIO 表示其FabreX 架構已經可以使用 DMA 在 PCI-Express 上進行內存池化,但這樣做需要應用程序能夠容忍 500 納秒到 1.5 微秒的延遲。

同樣,根據 Blocks and Files 的說法,在英特爾今年夏天毫不客氣地削減其 Optane 持久內存業務之前,部署該技術意味著會產生大約350 納秒的延遲。雖然可用,尤其是在分層內存配置中,但它比直接連接 CPU 的 DDR 內存預期的低于 100 納秒的往返延遲要長得多。

進入 CXL 內存生態系統

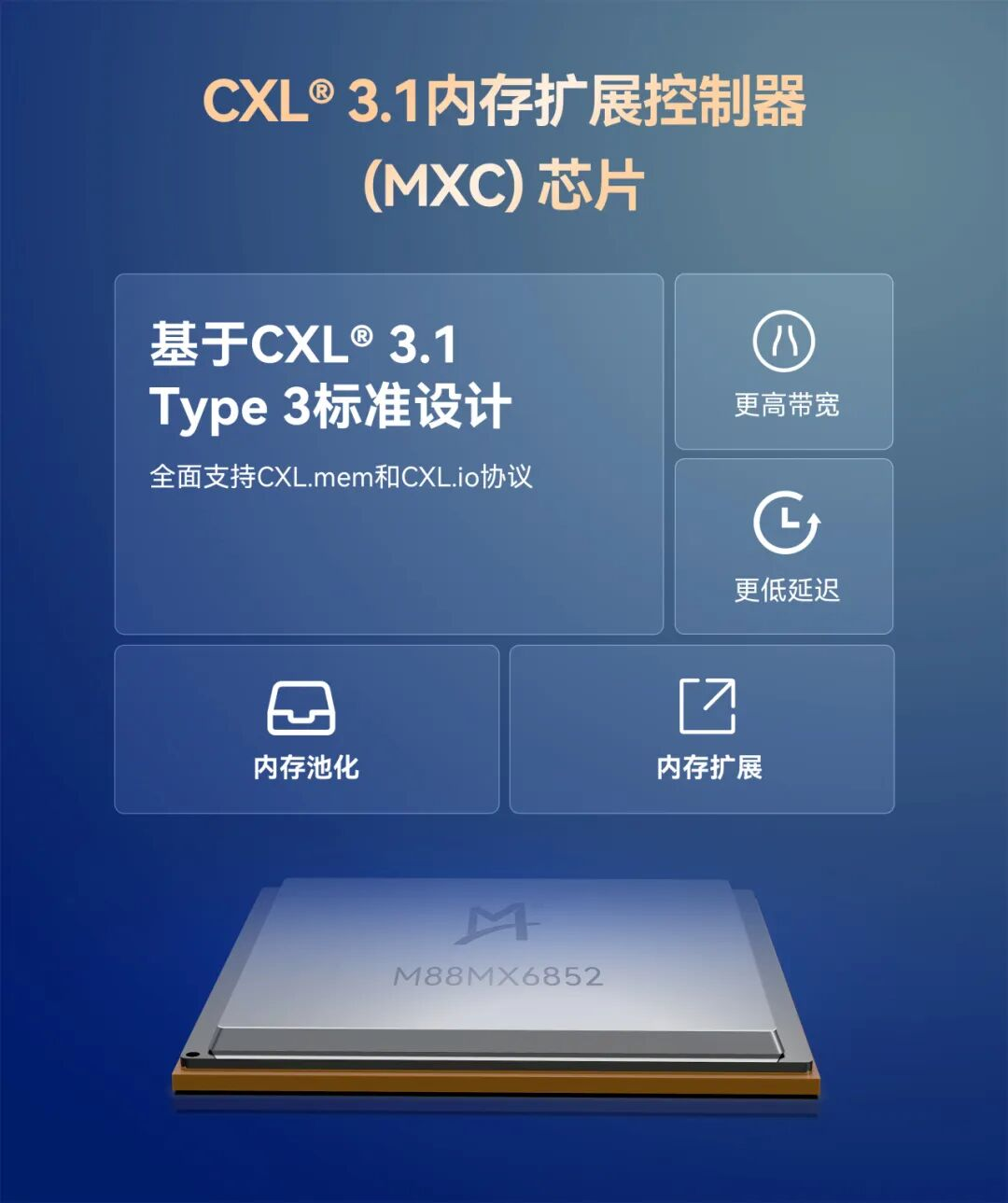

這為我們帶來了使用 Compute Express Link 協議或 CXL 的第一代內存擴展模塊。基于 AMD 的Epyc 9004“Genoa”處理器的系統是首批系統之一,擁有 64 條 CXL 連接通道——不同于其 128 至 160 條整體 PCI-Express 通道——最多可分為四到十六個設備。至于英特爾將如何在其“Sapphire Rapids”Xeon SP 處理器上實施 CXL,我們將不得不等到它們明年初問世。

與這些服務器相得益彰的是我們確信的第一個是許多 CXL 內存擴展模塊。雖然 CXL 最終將允許完全分解的系統,在這些系統中,資源可以通過高速結構在整個機架上共享,但距離那一天還有幾年的時間。

對于首次涉足數據中心,CXL 直接專注于內存擴展、分層內存和一些早期的內存池應用程序。目前,我們只關注內存擴展,因為在這個早期階段,它可以說是最簡單和最實用的,尤其是在以可用延遲附加內存時。

三星和Astera Labs已經展示了 CXL 內存模塊,他們說只需將它們插入兼容的 PCI-Express 5.0 插槽,即可為系統添加數 TB 的內存。從系統的角度來看,它們的外觀和行為就像通過內存總線連接到相鄰插槽的常規 DDR DRAM 內存。

在最長的時間里,一旦達到 CPU 內存控制器的限制,添加更多內存的唯一方法就是添加更多插槽。如果工作負載可以利用額外的線程,那就更好了,但如果不能,這將成為一種非常昂貴的添加內存的方式。實際上,額外的插槽只是一個內存控制器,上面附有一堆昂貴的、不需要的內核。

內存擴展模塊的行為方式大致相同,但它不是使用專有的插槽到插槽互連,如英特爾的 UPI 或 AMD 的 xGMI 鏈接,而是 CXL。這意味著您可以擁有這些設備的整個生態系統,事實上,我們已經看到一個相當充滿活力,有時甚至是令人向往的設備圍繞 CXL 展開。

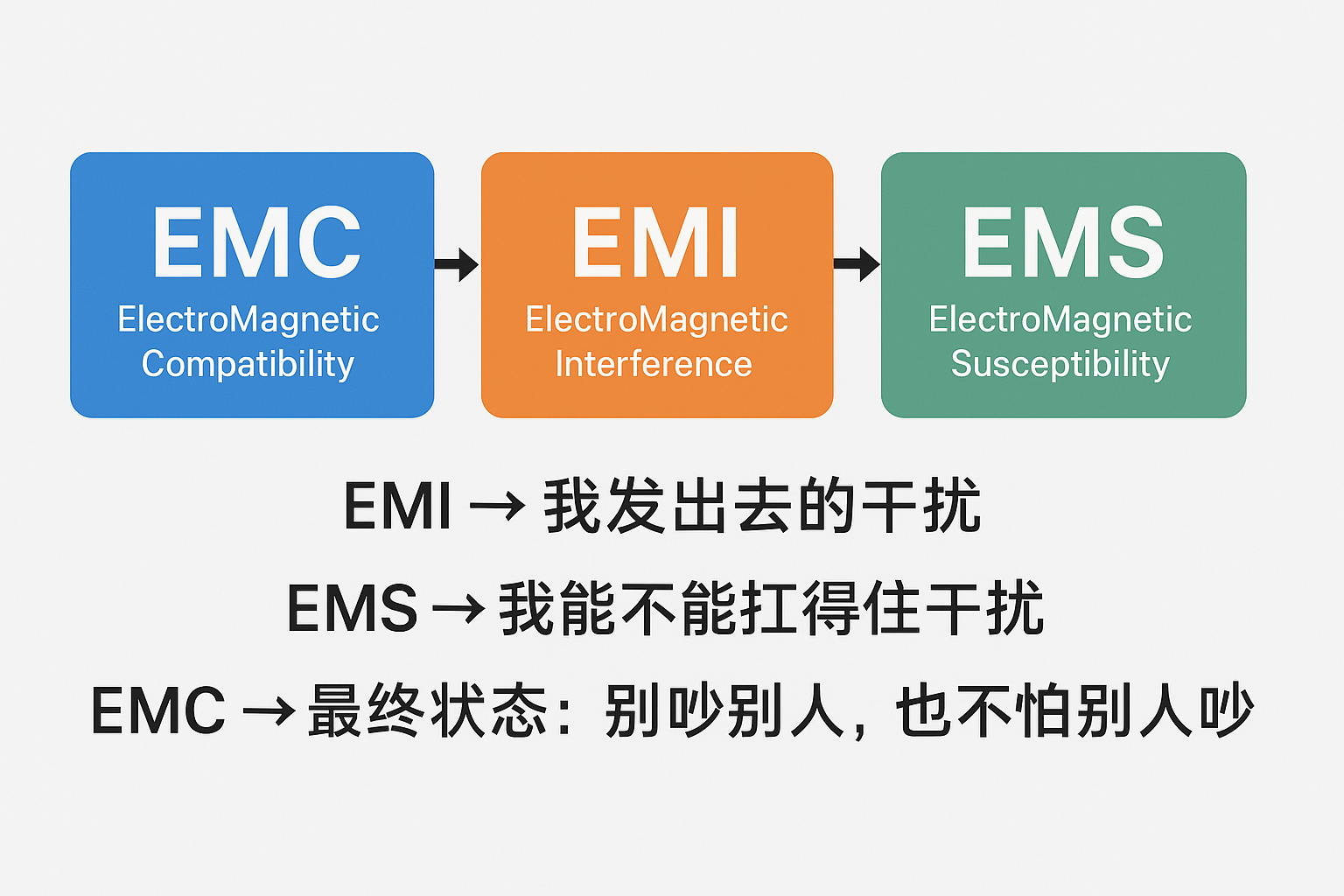

CXL 總裁 Siamak Tavallaei在 SC22上告訴 The Next Platform ,CXL 實際上包含三種協議,但并非所有協議都是延遲的靈丹妙藥。“CXL.io 仍然具有您預期的相同類型的延遲(來自 PCI-Express),但其他兩個協議——CXL.cache 和 CXL.mem——通過協議采用更快的路徑,并且它們減少了延遲。”

CXL 內存延遲到底有多糟糕?

如果 Astera 值得信任,延遲并不像您想象的那么糟糕。該公司的Leo CXL 內存控制器旨在接受高達 5600 MT/秒的標準 DDR5 內存 DIMM。他們聲稱客戶可以預期延遲與訪問第二個 CPU 上的內存大致相當,一個 NUMA 躍點。這使得它在 170 納秒到 250 納秒附近。事實上,就系統而言,這正是這些內存模塊向操作系統顯示的方式。

Tavallaei 解釋說,大多數 CXL 內存控制器會增加大約 200 納秒的延遲,額外的重定時器會增加或花費幾十納秒,具體取決于設備與 CPU 的距離。這與其他 CXL 早期采用者所看到的一致。GigaIO 首席執行官 Alan Benjamin 告訴The Next Platform,它所見過的大多數 CXL 內存擴展模塊的延遲都接近 250 納秒,而不是 170 納秒。

然而,正如 Tavallaei 指出的那樣,這仍然是對四插槽或八插槽系統的改進,在這些系統中,應用程序可能僅僅因為需要內存而不得不應對多個 NUMA 躍點。(不過,公平地說,IBM 和英特爾在 CPU 之間添加了更多更快的鏈接,以減少跳數和每跳延遲。)

話雖如此,許多芯片制造商很快指出,CXL 生態系統現在才剛剛起步。在 CXL 董事會任職的 AMD 的 Kurtis Bowman 告訴The Next Platform,許多早期的 CXL 概念驗證和產品都使用尚未針對延遲進行優化的 FPGA 或第一代 ASIC。隨著時間的推移,他預計延遲會大大改善。

如果 CXL 供應商能夠像他們聲稱的那樣,在展廳演示之外實現與多插槽系統同等的延遲,那么它應該在很大程度上消除利用它們所需的應用程序或操作系統特定定制的需要。好吧,至少就內存擴展而言。正如我們在 Optane 中看到的那樣,CXL 內存分層幾乎肯定需要某種操作系統或應用程序支持。

隨著插槽變得越來越大并且在板上安裝更多 DIMM 變得越來越難,這再合適不過了。放置它們的地方更少了。有可容納 32 個 DIMM 的雙插槽系統,但隨著芯片制造商增加更多通道以滿足更高核心數的帶寬需求,這是不可擴展的。

我們已經在某種程度上在 AMD 的 Genoa 芯片上看到了這一點,盡管該芯片將內存通道數量增加到 12 個,但在發布時每個通道僅支持一個 DIMM,將雙插槽配置中的 DIMM 數量限制為 24 個。即使您可以為每個通道連接兩個 DIMM,我們被告知將 48 個 DIMM 安裝到標準機箱中是不切實際的。

當我們希望在更遠的距離(例如跨機架)連接內存時,事情會變得更加復雜,因為電或光互連產生的延遲必須計入方程式。但對于機箱內 CXL 內存擴展,延遲似乎并不像許多人擔心的那么令人頭疼。

審核編輯 :李倩

-

amd

+關注

關注

25文章

5684瀏覽量

139976 -

內存

+關注

關注

9文章

3210瀏覽量

76376 -

生態系統

+關注

關注

0文章

711瀏覽量

21581

原文標題:CXL,面臨嚴峻的延遲問題

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

瀾起科技發布PCIe 6.x/CXL 3.x AEC解決方案

從內存接口到PCIe/CXL、以太網及光互連,高速互連芯片市場分析

Penguin Solutions SMART Modular CXL NV-CMM E3.S 2T 內存模塊通過 CXL 兼容性認證

漢威科技薄膜鉑電阻溫度傳感器到底有多強

64GT/s+8000MT/s:瀾起CXL 3.1芯片破解數據中心內存瓶頸

瀾起科技推出CXL? 3.1內存擴展控制器,助力下一代數據中心基礎設施性能升級

PCIe協議分析儀能測試哪些設備?

超低功耗藍牙模組的功耗到底有多低

第二代AMD Versal Premium系列SoC滿足各種CXL應用需求

世邁科技最新 128GB E3.S 2T CMM內存模塊榮獲 CXL 聯盟整合商認證

新思科技解讀CXL 3.1標準

CXL內存延遲到底有多糟糕?

CXL內存延遲到底有多糟糕?

評論