升級下,工程師們用起來也越來越得心應手,工作量都得到了簡化。但諸位后端設計工程師有沒有害怕自己吃飯的工具變得越來越智能,最終有一天替代自己? EDA 引入機器學習,是威脅還是福利? ? 許多頂尖的IC設計都需要在設計上進行優化,

2021-07-25 09:56:20 10988

10988 隨著芯片復雜度的提高,驗證測試變得越來越重要,對芯片最顯著的改進不僅在設計流程中產生,也在芯片調試和驗證流程中反復進行著。因此,為幫助IC設計企業縮短驗證時間、加快產品上市,大型EDA工具提供商均致力于加強硬件仿真工具的開發與相關市場的經營。

2013-10-29 09:17:50 2569

2569 作者丨Robei君? 圖片 | Robei 沒有EDA,就沒有芯片,EDA是造芯的工具。 如果沒有EAD軟件,可能全球所有的芯片設計公司都得停擺,代工廠在進行工藝研發與優化時也將無工具可用。 01

2021-01-05 14:20:08 7599

7599

整個實現階段,可以概括成玩EDA 工具及基于EDA 工具的方法學,EDA 工具無疑是實現階段的主導,一顆芯片做得好不好,在實現階段之前基本取決于工程師的能力強不強,而在實現階段之后基本取決于EDA 工具玩得好不好。

2023-06-07 11:43:52 4066

4066

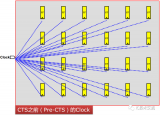

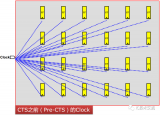

本節介紹后端處理的剩余部分,上節我們講到floorplan和placement。后面就到了CTS階段。

2023-08-31 14:31:07 5383

5383

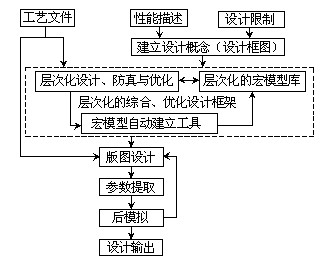

IC設計離不開EDA工具的支持,模擬設計也不例外。在9月20日舉行的2019年中國模擬半導體大會上,Cadence中國區技術支持總監欒志雨帶來了主題為《中國模擬IC升級更需要借力EDA工具》的演講。

2019-09-25 12:10:37 8164

8164 的方式。如果一款工具能夠覆蓋特定芯片在上述流程中的設計任務,那么我們就將其稱之為全流程EDA工具,或者是全流程EDA平臺。 在國產EDA發展初期,還有人質疑,在EDA三大家提供全流程工具的情況下,國產EDA是否還有必要繼續重走這條路。不過,隨著美國對中國科技制裁逐漸加大

2023-12-14 00:08:00 3440

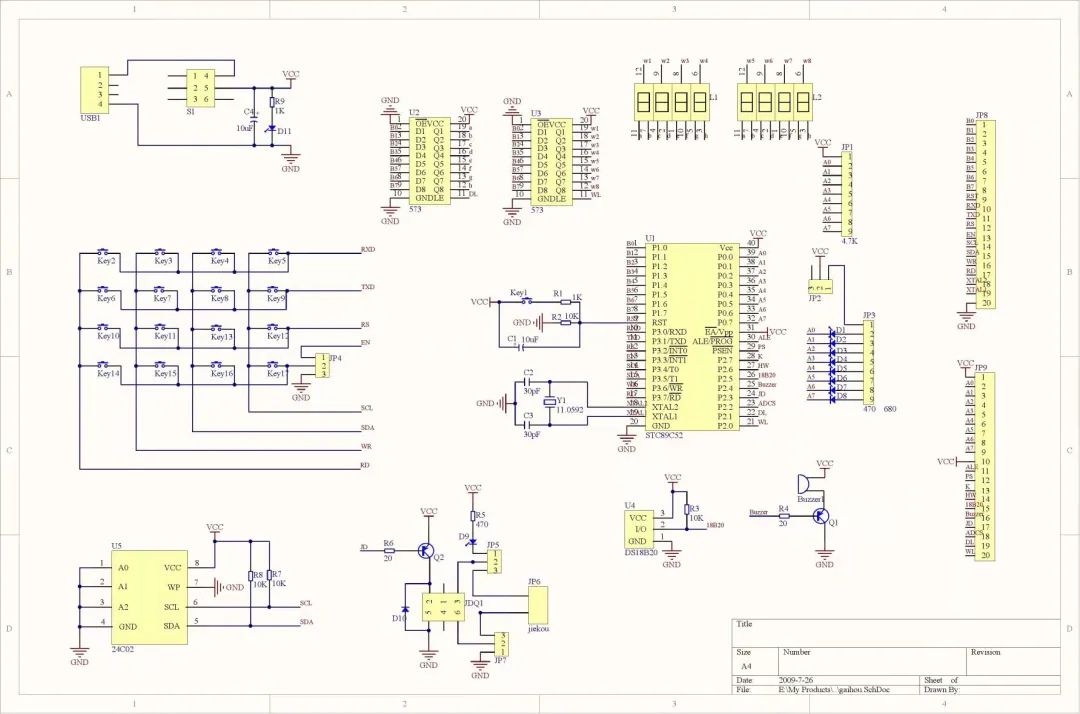

3440 EDA設計流程及其工具.ppt

2017-01-21 13:07:21

版圖(digital)。常用工具有L-EDIT,Cadence的se, virtuso等IC前端設計指邏輯設計;IC后端設計指物理設計。前端:就是將你的想法或別人的想法用你設計的電路來實現,也就是說你

2011-12-19 16:01:13

IC的設計過程可分為哪幾個部分?前端設計的主要流程有哪些?Backend design flow后端設計流程有哪些?

2021-10-20 06:23:43

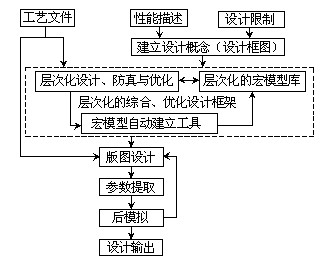

GDSⅡ的設計流程: 這個可以理解成半定制的設計流程,一般用來設計數字電路。 整個流程如下(左側為流程,右側為用到的相應EDA工具): 一個完整的半定制設計流程應該是:RTL代碼輸入、功能仿真、邏輯綜合

2012-01-11 13:49:27

1.1 從RTL到GDSⅡ的設計流程: 這個可以理解成半定制的設計流程,一般用來設計數字電路。整個流程如下(左側為流程,右側為用到的相應EDA工具): 一個完整的半定制設計流程應該是:RTL代碼

2018-08-16 09:14:32

,檢查短路和開路等電氣 規則違例;等等。工具為Synopsys的Hercules實際的后端流程還包括電路功耗分析,以及隨著制造工藝不斷進步產生的DFM(可制造性設計)問題,在此不說了。物理版圖驗證完成

2018-08-13 17:05:29

關于IC設計的流程是怎樣的?有關IC設計的方法有哪些?

2021-06-21 07:51:54

IC設計完整流程及工具IC的設計過程可分為兩個部分,分別為:前端設計(也稱邏輯設計)和后端設計(也稱物理設計),這兩個部分并沒有統一嚴格的界限,凡涉及到與工藝有關的設計可稱為后端設計。前端設計的主要

2021-07-28 07:51:27

(Electrical Rule Checking):電氣規則檢查,檢查短路和開路等電氣規則違例;等等。工具為Synopsys的Hercules實際的后端流程還包括電路功耗分析,以及隨著制造工藝不斷進步產生的DFM(可

2016-06-29 11:30:46

下出按用途對IC設計軟件作一些介紹。IC設計工具很多,其中按市場所占份額排行為Cadence、Mentor Graphics和Synopsys。這三家都是ASIC設計領域相當有名的軟件供應商。其它

2012-01-10 10:07:31

0185. 進入系統后就可以正常的使用 Synopsys2018 版的工具了;6. 希望你可以把這個分享給想學數字 IC 的同學;關于《Synopsys2018EDA 工具》就介紹到這里!!!你唯一需要保障的只是

2020-11-30 18:56:05

「Node學習」Koa+Mysql2+Vue前后端綜合例子

2020-06-02 17:38:14

[溫習]jqgrid 前后端交互實例

2020-06-10 17:30:45

當web前后端的基本功能實現以后,就需要考慮優化的問題,如何提高速度,如何充分利用現有的資源,如何根據現有的硬件資源作軟件適配優化等等。這些都是開發后期的工作重心。本文以嵌入式平臺的服務器為例,總結

2021-12-16 07:31:38

內部的測試電路,提高流片后的可測試性,降低測試成本。

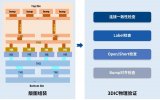

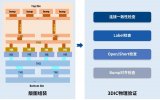

后端設計:將門級網表通過EDA設計工具進行布局布線和進行物理驗證,最后產生芯片的生產文件。

SignOff:完成IC設計的所有檢查的一個標志。

流片

2024-09-25 15:51:17

要求: 1.兩年以上數字后端工作經驗,熟練使用ICC或Encounter,熟悉IC后端流程。 2.具有大規模芯片流片經驗,有mixed signal layout經驗者優先。 3.理解時序/分析和優化

2017-03-03 14:53:07

使用的各種庫的格式和內容,比如.v, .lib了解某個應用領域的知識學會使用FPGA測試代碼具備DFT的基本概念<后端>熟悉后端流程,(IO plan, floorplan

2012-01-11 14:23:35

越大,win-win;在功能驗證,物理驗證環節,則有Mentor的一席之地,物理驗證會貫穿并頻繁往返于后端設計的全流程,對于軟件的效率和可視化要求很高,這點calibre做得非常好。另外EDA供應商還會

2020-06-14 08:01:07

隨著EDA平臺服務趨于網絡化,如何通過對資源和流程的有效管理,為用戶提供更為方便安全的遠程EDA平臺調用服務,已成為關鍵問題。在FPGA開發平臺上集成了EDA工具環境,并部署SGD軟件。在實現遠程

2019-07-16 21:09:34

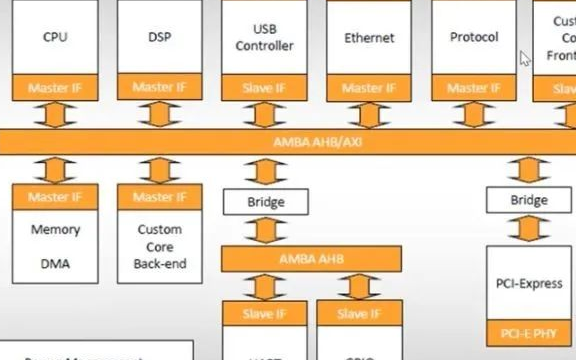

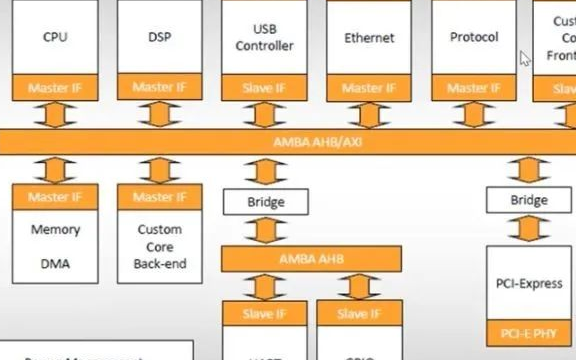

數字芯片內部的架構是由哪些部分組成的?數字IC設計的流程主要分為哪幾大步?每個流程使用的EDA工具有哪些?

2021-06-18 08:29:52

常用EDA工具軟件有哪些?探討數字電子技術與EDA技術是如何相結合的?有什么益處?

2021-04-07 06:26:04

設計(自動布局布線-APR)。 數字IC后端設計是指將前端設計產生的門級網表通過EDA設計工具進行布局布線和進行物理驗證并最終產生供制造用的GDSII數據的過程。其主要工作職責有:芯片物理結構分析、邏輯分析、建立

2020-12-29 11:53:01

IC流程。任職資格:1、 微電子或物理相關專業,本科以上學歷;2、 1-2年相關工作經驗;3、 擁有扎實的硬件電路基礎知識;4、 熟練掌握多種EDA Tools;5、 掌握Verilog、TCL、Perl、C語言;6、 具有后端APR經驗。

2013-04-08 17:23:48

數字IC是什么意思?數字IC前端設計流程有哪些?數字IC后端設計流程有哪些?

2021-10-20 06:24:49

數字后端,顧名思義,它處于數字IC設計流程的后端,屬于數字IC設計類崗位的一種。在IC設計中,數字后端所占的人數比重一直是最多的,而且隨著芯片規模不斷加大,后端工程師需要的人數將會越來越多。一般來說

2021-01-13 06:31:48

芯片設計流程及工具IC的設計過程可分為兩個部分,分別為:前端設計(也稱邏輯設計)和后端設計(也稱物理設計),這兩個部分并沒有統一嚴格的界限,凡涉及到與工藝有關的設計可稱為后端設計。前端設計的主要流程

2020-02-12 16:07:15

小弟剛剛開始接觸EDA。要做一個關于EDA常用仿真軟件的project,但是我看EDA仿真軟件不要太多啊,還分什么“電路設計與仿真工具、PCB設計軟件、IC設計軟件、PLD設計工具及其它EDA軟件

2014-05-15 20:57:06

本帖最后由 eehome 于 2013-1-5 09:47 編輯

前記:在很多電子網站上看到很多介紹IC或者FPGA設計工具系統的資料,但是感覺都不是很綜合。所以這里嘗試做一個2012

2012-12-28 17:00:22

設計工具及使用方法;項目設計實踐(C)。 CMOS集成電路設計原理;ASIC設計導論;IC布局布線設計;版圖驗證和提取;可測性設計;項目設計實踐。 Top-Down設計流程;Full-Customer設計流程;標準單元庫設計;單元庫的各種庫文件;各種單元的功能,結構和版圖。

2012-05-16 14:57:10

Fabless公司建立自己公司內部的EDA團隊 從事先進工藝的開發,或者從事特殊電路的設計,采用普通的EDA工具或者商業化的EDA工具是很難滿足需求的。因此,國際上領先的IC企業,如Intel, 三星,臺

2018-09-09 09:51:36

提出一種新的高平衡、高可靠性的前端可控時鐘樹設計方法,解決時鐘樹需要在后端工具中多次反復以達到滿足性能和功耗要求的問題。闡述了從前端優化和后端約束2個方面入手解

2009-04-21 09:06:16 26

26 EDA工具手冊.

Cadence 軟件是我們公司統一使用的原理圖設計、PCB 設計、高速仿真、自動布線的EDA 工具。本篇Cadence 使用手冊是一本基于Allegro SPB V15.2 版本的Cadence 軟件的基

2010-03-11 15:11:46 0

0 基于多種EDA工具的FPGA設計

介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配置下載等具體內容。并以實

2009-05-14 18:38:38 1036

1036

摘 要:在FPGA開發的各個階段,市場為我們提供了很多優秀的EDA工具。面對眼花繚亂的EDA工具,如何充分利用各種工具的特點,并規劃好各種工具的協同使用,對FPGA

2009-06-20 10:51:14 906

906 摘要:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配置下載等具體內容。并以實際操作介紹了

2009-06-20 11:42:45 674

674

IC設計中Accellera先進庫格式語言與EDA工具的結合應用

先進庫格式(ALF)是一種提供了庫元件、技術規則和互連模型的建模語言,不同抽象等級的ALF模型能被EDA同時用于IC規

2009-12-26 14:43:16 1027

1027

多種EDA工具的FPGA設計方案

概述:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配

2010-05-25 17:56:59 895

895

數字前端設計流程,使用PT進行STA lSYNOPSYS Prime Time l只是一個時序分析工具,本身不對電路做任何修改。 l在ASIC流程中對于電路進行任何修改過后都應該使用STA工具檢查其時序,以保證電

2011-10-28 10:28:08 41

41 數字后端流程 1. 數據準備。對于 CDN 的 Silicon Ensemble而言后端設計所需的數據主要有是Foundry廠提供的標準單元、宏單元和I/O Pad的庫文件,它包括物理庫、時序庫及網表庫,分別以.lef、

2011-10-28 10:31:06 40

40 前端設計(也稱邏輯設計)和后端設計(也稱物理設計)并沒有統一嚴格的界限,涉及到與工藝有關的設計就是后端設計。

2011-12-02 16:54:55 193

193 EDA設計流程及其工具

2016-12-11 23:38:39 0

0 就產業發展的現狀而言,國產EDA工具和Synopsys、Cadence、Mentor的產品差距過于懸殊,而且看不到趕超西方的希望,國內IC設計公司基本在使用國外EDA工具。

2016-12-30 10:14:10 4884

4884 ,右側為用到的相應EDA工具): 一個完整的半定制設計流程應該是:RTL代碼輸入、功能仿真、邏輯綜合、形式驗證、時序/功耗/噪聲分析,布局布線(物理綜合)、版圖驗證。 至于你說的FPGA設計,開發起來更加簡單,結合第三方軟件(像Modelsim和Synplify Pr

2017-10-20 11:38:20 25

25 IC就是半導體元件產品的統稱,IC按功能可分為:數字IC、模擬IC、微波IC及其他IC。數字IC就是傳遞、加工、處理數字信號的IC,是近年來應用最廣、發展最快的IC品種,可分為通用數字IC和專用數字IC。

2018-03-23 16:56:09 35459

35459 本文首先介紹了EDA工具廠商,其次對八種硬件設計的EDA工具做了對比分析,最后闡述了eda的應用。

2018-04-19 11:28:29 24054

24054 EDA公司以賣EDA工具license費作為主要的商業模式。以某家EDA公司的PnR工具為例,一套license三年的使用費大約為100萬美金左右。對于芯片設計公司來說,一般需要購買多套license才能滿足芯片設計需求。

2018-04-26 15:23:10 40614

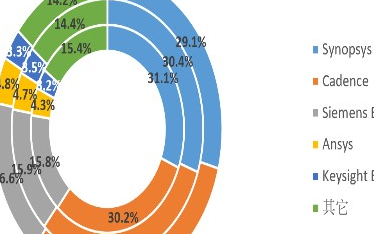

40614 EDA是IC電子行業必備的設計工具軟件,是IC產業鏈最上游的子行業。Cadence、Synopsys、Mentor Graphics是EDA工具軟件廠商全球三大巨頭。去年11月份,Mentor Graphics被西門子以45億美元現金方式的收購。

2018-05-08 14:36:00 28033

28033 在vring_avail和vring_used的flags字段,控制前后端的通信。vring_used中的flags用于通知driver端,當add一個buffer的時候不用notify后端。而vring_avail中的flags用于通知qemu端,當消費一個buffer的時候不用interrupt 客戶機。

2018-07-06 15:18:06 5009

5009

EDA技術可面向三個不同的層次,即系統級、電路級和物理實現級。進入20世紀90年代以來,EDA技術逐漸以高級語言描述、系統仿真(system simulation)和綜合優化(synthesis)為

2018-07-19 11:44:00 3399

3399

EDA(Electronic Design Automation)就是以計算機為工作平臺,以EDA軟件工具為開發環境,以PLD器件或者ASIC專用集成電路為目標器件設計實現電路系統的一種技術。

2018-09-18 17:19:59 45

45 世界三大EDA廠商一般指的是Cadence, Synopsys, Mentor Graphics,四強的話好包括Springsoft。就我個人的理解,Synopsys主要是強在前端,DC和PT是公認的標準。Cadence牛在后端,無論是RF, 數字,亦或是PCB級,它的后端布線工具都用的挺廣的。

2018-11-18 09:06:25 6841

6841 EDA技術進行電路設計的大部分工作是在EDA軟件平臺上進行的。EDA的設計流程主要包括設計輸入、設計處理、設計驗證、器件編程和硬件測試等5個步驟。

2020-05-15 11:44:02 15721

15721 目前國內電子工程師使用的EDA設計工具主要還是以國外的設計工具為主,顯然,國內EDA市場已被高度壟斷。其實早在2014年開始,國內就已經誕生了一款專為國人的使用習慣研發的EDA工具——EasyEDA。

2020-07-09 15:47:36 4479

4479 EDA 是 IC 設計必需、也是最重要的集成電路軟件設計工具,EDA 產業是 IC 設計最上游的產業。經過幾十年發展,從仿真、綜合到版圖,從前端到后端,從模擬到數字再到混合設計,以及后面的工藝制造

2020-07-15 15:39:39 2570

2570 因此,僅有點工具是不夠的,從提供點工具過渡到支持整個流程,這是EDA廠商的未來發展方向。把端到端流程進行優化是最好的理念,從架構到節能設計,都貫穿了設計、布局布線和驗證整個過程。

2020-10-02 11:46:00 561

561 1 ? EDA 全景概述 EDA 是 IC 設計必需、也是最重要的集成電路軟件設計工具,EDA 產業是 IC 設計最上游的產業。經過幾十年發展,從仿真、綜合到版圖,從前端到后端,從模擬到數字再到混合

2020-10-30 16:49:22 1224

1224 芯片設計公司希望通過工藝升級生產更高性能,更低功耗和更小芯片。為解決7nm漏電效應,為了滿足相應工藝的生產規則,需要在支持芯片設計尤其是后端設計階段的EDA工具增加了大量的硬性規則,使EDA設計的變通性大大降低,而在14nm以上,則沒有太多硬性規則。

2020-11-16 12:05:49 6817

6817 AI 框架的?程挑戰和可?解決?案。在本文中,我們將進?步結合 Rosetta 介紹如何定制化改造 TensorFlow 前后端相關組件,以集成 MPC (Multi-Party

2020-11-26 09:36:10 3001

3001

的設計來例系統地介紹了利用多種EDA工具進行 FPGA協同設計的實現原理及方法近年來,隨著微電子學的迅速發展以及SoC(System on Chip ,片上系統) 技術在設計領域引起的深刻變革,EDA(Electornic Design Automatic ,電子設計自動化) 工具在系統設計中的地位愈發重要

2020-11-27 17:57:34 29

29 ? ? 數字IC設計流程是每個IC從業者的第一課,無論你是做前端,后端,還是驗證,都需要對芯片的整個設計流程有個基本的了解。 本文章主要介紹以下三點內容: 一. 數字IC設計的流程及每個流程需要

2020-12-09 10:12:11 8021

8021

EDA 是IC 設計必需、也是最重要的集成電路軟件設計工具,EDA 產業是IC 設計最上游的產業。經過幾十年發展,從仿真、綜合到版圖,從前端到后端,從模擬到數字再到混合設計,以及后面的工藝制造等等

2021-01-01 09:52:00 1086

1086 Silvaco的打法為產業發展提供了新的思路,EDA工具的應用場景應該不僅僅局限于IC設計 臺積電、蘋果共同推進IC設計進入3nm工藝時代,新能源汽車等新應用的興起也在帶動碳化硅等新材料

2021-02-01 11:45:03 2978

2978 數字后端,顧名思義,它處于數字IC設計流程的后端,屬于數字IC設計類崗位的一種。 在IC設計中,數字后端所占的人數比重一直是最多的,而且隨著芯片規模不斷加大,后端工程師需要的人數將會越來越多。

2021-02-26 16:06:20 14994

14994 IC的設計過程可分為兩個部分,分別為:前端設計(也稱邏輯設計)和后端設計(也稱物理設計),這兩個部分并沒有統一嚴格的界限,凡涉及到與工藝有關的設計可稱為后端設計。

2021-04-09 14:05:24 88

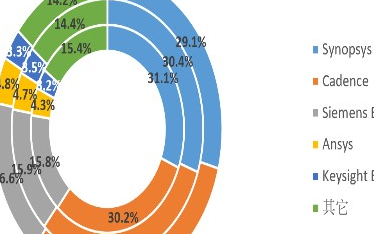

88 設計全流程EDA工具解決方案的企業,集中了全球超77%的EDA工具市場。此外,Ansys憑借熱分析、壓電分析等優勢點工具,Keysight EEsof憑借電磁仿真、射頻綜合等優勢點工具,獲得市場第四

2021-06-12 10:32:00 4694

4694

數字IC就是傳遞、加工、處理數字信號的IC,是近年來應用最廣、發展最快的IC品種,可分為通用數字IC和專用數字IC。數字前端以設計架構為起點,以生成可以布局布線的網表為終點;是用設計的電路實現想法

2021-11-06 16:51:05 26

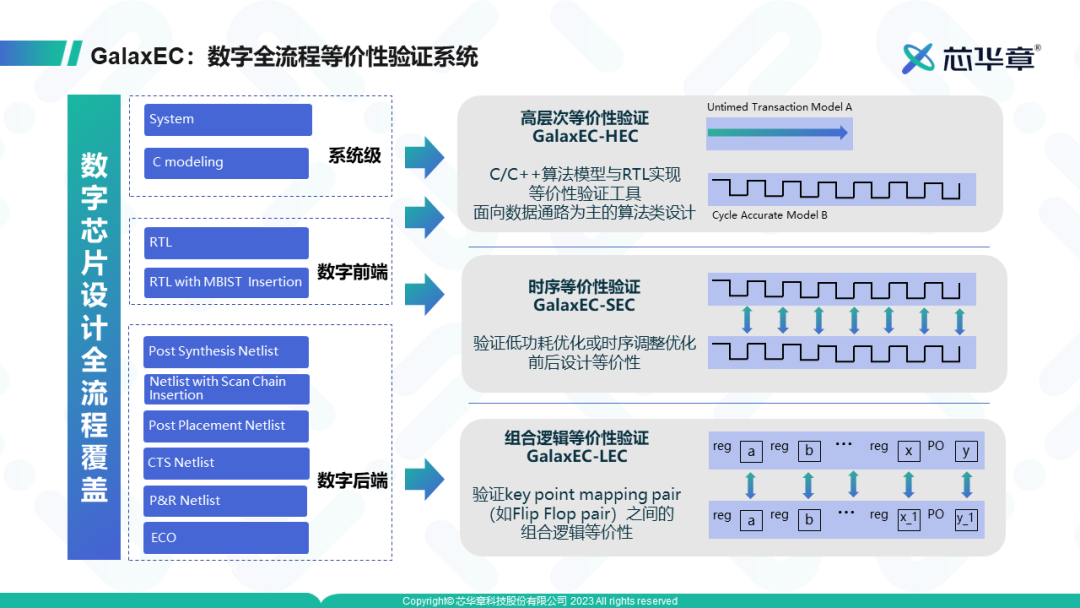

26 實現國產的EDA全流程工具,一直是大家最關注的,可以說是所有中國EDA人的重要目標。目前華大九天已經實現模擬IC設計的全流程,而數字全流程依舊等待著大家將多個點工具連接起來。

2022-09-21 11:11:09 1003

1003 EDA工具最大的好處,就是能極大的縮短芯片設計的時間,從而提升芯片設計的效率。手動畫電路圖可能又慢又容易出錯,但是用計算機幾分鐘就完成了,而且還可以去隨便的修改。時間就是金錢,越早讓芯片制造出來,就能越早的去占據市場先機。在前端和后端的每個步驟和流程里,都需要用到各種各樣的EDA工具。

2022-11-03 15:27:27 2394

2394 IC設計底層工具EDA發展加速 上海立芯發布兩款數字后端工具 日前華鑫證券在一篇計算機行業的研究報告中指出,國產化及數據要素化驅動數字經濟長牛;比如國產自主可控EDA軟件或將迎來大的發展機遇。EDA

2022-11-22 16:17:43 1221

1221 01 演講題目 ? 開源硬件系列03期: 數字芯片后端EDA工具的挑戰與機遇 02 演講時間 ? 2022年12月19日 晚上?19:00 03 內容簡介 ? 數字電路后端EDA工具多種多樣

2022-12-15 08:10:02 3936

3936 本以為ChatGPT對于IC后端設計幫助應該不大,畢竟它非常依賴EDA工具,它對于EDA工具這種非常專業的、非常Custom的東西了解和訓練的數據應該不多,所以可能幫不上什么忙。

2023-03-07 09:23:47 2205

2205 設計一款芯片,明確需求(功能和性能)之后,先由架構工程師設計架構,得出芯片設計方案,前端設計工程師形成RTL代碼,驗證工程師進行代碼驗證,再通過后端設計工程師和版圖工程師生成物理版圖。

2023-05-12 14:10:05 2705

2705 隨著互聯網的高速發展,前端頁面的展示、交互體驗越來越靈活、炫麗,響應體驗也要求越來越高,后端服務的高并發、高可用、高性能、高擴展等特性的要求也愈加苛刻,從而導致前后端研發各自專注于自己擅長的領域深耕細作。

2023-05-15 17:16:54 1528

1528

導語中美科技競爭激烈,中國半導體也已飛速發展了20年,作為其中小又重的一環——EDA,如今到底是個什么水平呢?如果真的使用國產EDA,對于中國IC產業到底是進步還是倒退呢?想要知道答案,還是要從國產

2022-11-04 10:05:45 1823

1823

EDA工具的技術來源主要包括描述統計學、可視化技術、探索性數據分析方法、數據挖掘技術,以及可交互性與用戶界面設計。這些技術和方法的應用使得EDA工具成為數據分析和發現中不可或缺的工具之一。

2023-07-21 15:09:44 1314

1314 IC(Integrated Circuit)設計涉及兩個主要的階段:前端設計和后端設計。它們在IC設計流程中扮演著不同的角色和職責,具有以下區別

2023-08-15 14:49:34 6590

6590 迅為國產化RK3588開發板在安防前后端應用解決方案

2023-05-10 16:04:29 1946

1946

在IC設計中,設計師使用電路設計工具(如EDA軟件)來設計和模擬各種電路,例如邏輯電路、模擬電路、數字信號處理電路等。然后,根據設計電路的規格要求,進行布局設計和布線,確定各個電路元件的位置和連線方式。最后,進行物理設計,考慮電磁兼容性、功耗優化、時序等問題,并生成芯片制造所需的掩膜信息。

2023-08-30 17:07:54 6985

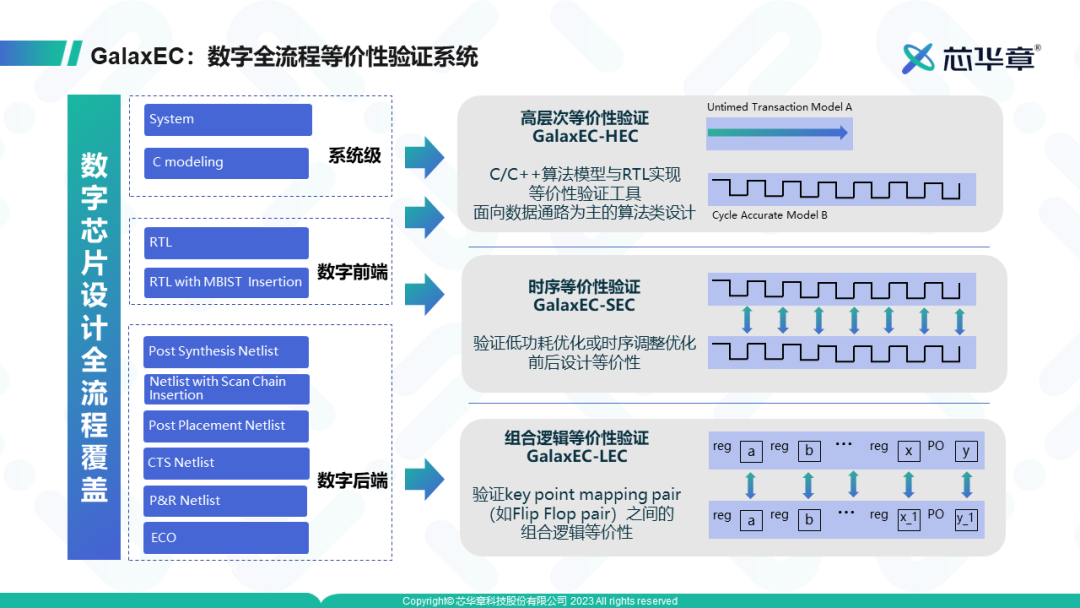

6985 及相關專業人士,業內領先的系統級驗證EDA解決方案提供商芯華章,隆重發布 首款自主研發的數字全流程等價性驗證系統穹鵬GalaxEC 。 隨著GalaxEC的發布, 芯華章自主EDA工具完成了對數字驗證全

2023-09-19 11:05:04 1259

1259

中興EDA工具手冊

2022-12-30 09:21:00 11

11 難受的,那就是使用Django自帶的模版,這種通常需要自己利用HTML+CSS+Jquery的方式總感覺是上一個時代的做法,前后端分離無論對于開發效率、多端支持等等都是很有好處的。 所以,本文希望通過一個簡單的demo,講一講基于Django+Vue的前后端分離開發,將

2023-11-01 09:22:36 1989

1989

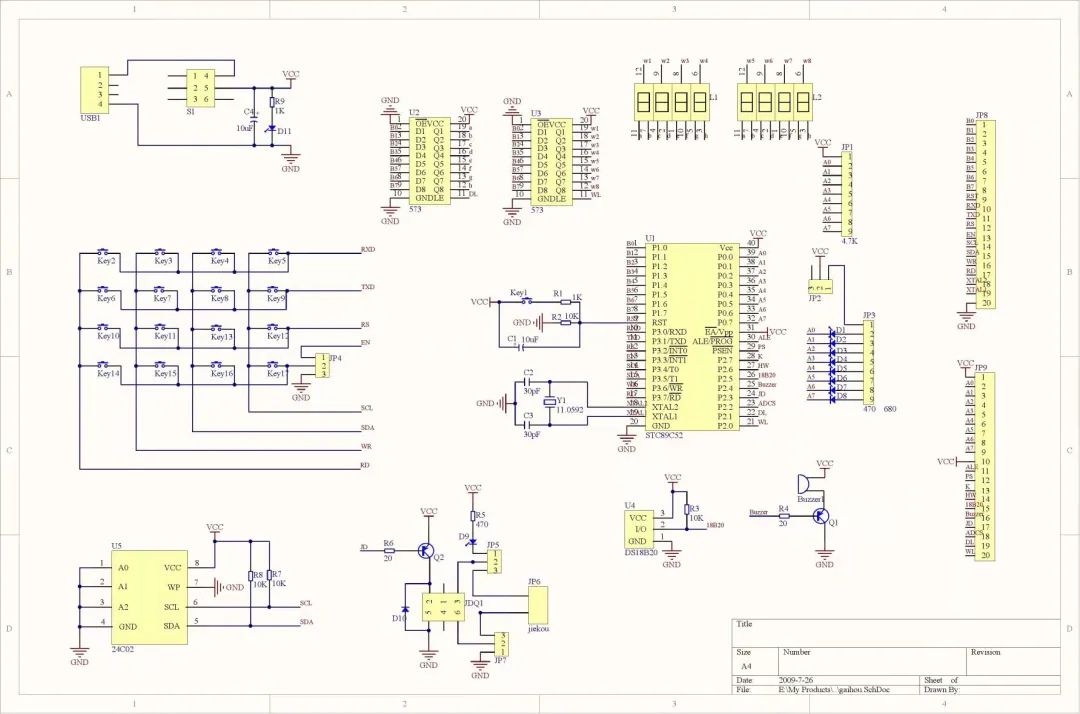

在進行電子硬件EDA設計時,一般都需要按照一套完整的設計步驟流程,經過這些流程下來設計的產品,就不會有產生設計紕漏的現象。 在電子硬件設計中,不管是大公司還是小公司,都會大差不差的按下面這個流程來

2023-11-07 10:41:14 2933

2933

Boot 進行開發時,前后端交互是一個非常重要的部分,本文將詳細介紹 Spring Boot 前后端交互的流程。 前后端交互的基本原理 在前后端交互的過程中,前端負責向后端發送請求并接收響應,而后端則負責處理接收到的請求并返回相應的數據。通常情況下,前后端之間的交互采用 HTTP 協

2023-11-22 16:00:26 3701

3701 機遇總是與挑戰并存,目前國內在高端EDA工具研發方面,面臨著如Synopsys、Cadence和Mentor等國際EDA供應商的巨大挑戰,即使是作為本土最大的EDA公司,華大九天目前也只能夠提供產業所需EDA解決方案的1/3左右。

2024-01-18 15:19:13 3256

3256

和預測提供基礎。在進行EDA過程中,使用合適的工具軟件可以顯著提升效率和準確性。本文將介紹幾種常見的EDA工具軟件。 Python和其相關的庫 Python是一種廣泛使用的編程語言,擁有豐富的庫和工具支持,可以進行各種數據處理和分析任務。在EDA過程中,Python可以通過使用NumPy、

2024-01-30 13:57:15 2728

2728 近日,國內數字后端全流程EDA企業日觀芯設宣布完成數千萬元的Pre-A輪融資。本輪融資由藍馳創投領投,源碼資本跟投,本輪融資資金將用于市場推廣以及產品升級迭代的研發。

2024-04-07 16:23:58 1803

1803 1 目的 穩定可靠,降本增效 ? 前后端數據傳輸約定旨在提升系統穩定性、可靠性,降低線上線下bug率;并提升研發效率、降低溝通成本、降低延期率。是確保項目前端和后端開發順利進行的重要規約之一,定義了

2024-07-08 19:10:55 1079

1079

西門子EDA工具以其先進的技術和解決方案,在全球半導體設計領域扮演著舉足輕重的角色。本文將從汽車IC、3D IC和EDA AI三個方向,深入探討西門子EDA工具如何助力行業克服技術挑戰,推動創新發展。

2025-03-20 11:36:00 2084

2084 西門子數字化工業軟件于 2025 年設計自動化大會 (DAC 2025) 上宣布推出用于 EDA 設計流程的 AI 增強型工具集,并在大會期間展示 AI 技術如何助力 EDA 行業提升生產力、加快產品上市速度,幫助客戶以市場所需的快節奏探索創新機遇。

2025-06-30 13:50:23 2880

2880 在芯片設計的流片之路充滿挑戰,物理驗證EDA工具無疑是這“最后一公里”關鍵且不可或缺的利器。它通過設計規則檢查、版圖與原理圖一致性驗證等關鍵流程,為IC設計契合制造需求提供堅實保障。作為簽核(Signoff)環節的關鍵防線,物理驗證EDA工具有力保障了流片的可靠性與成功率,堪稱芯片成功流片的守護者。

2025-07-03 11:30:23 3176

3176

來自一位資深用戶反饋:“GloryEX在全芯片RC提取方面表現出色,處理大規模設計時速度快、精度高,對復雜互連結構的寄生參數捕捉準確。工具在后端Sign-off流程中能快速定位時序瓶頸,顯著提升

2025-12-19 12:52:04 311

311

電子發燒友App

電子發燒友App

評論