推動科技進步的半導(dǎo)體技術(shù)真的會停滯不前嗎?這也不太可能,7nm工藝節(jié)點將開始應(yīng)用EUV光刻工藝,研發(fā)EUV光刻機的ASML表示EUV工藝將會支持未來15年,部分客戶已經(jīng)在討論2030年的1.5nm工藝路線圖了。

2017-01-22 11:45:42 3754

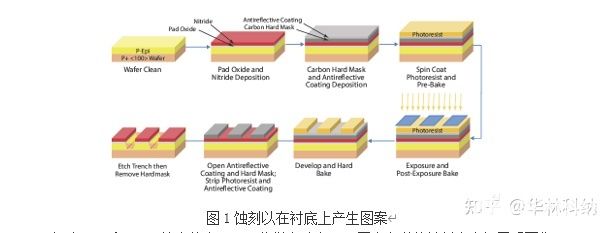

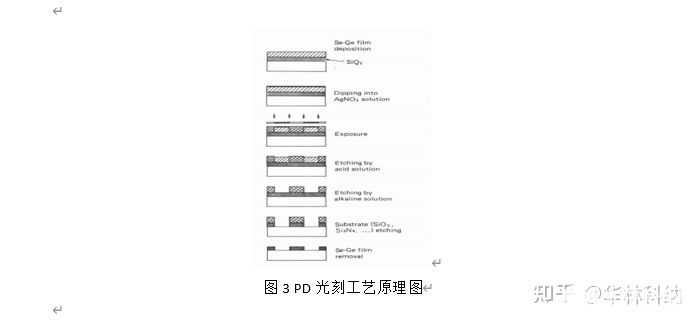

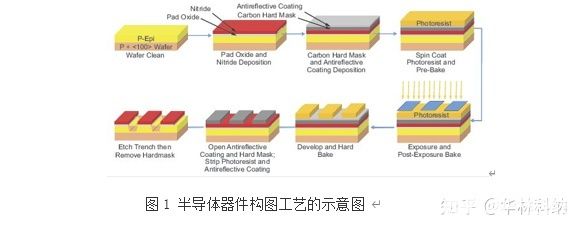

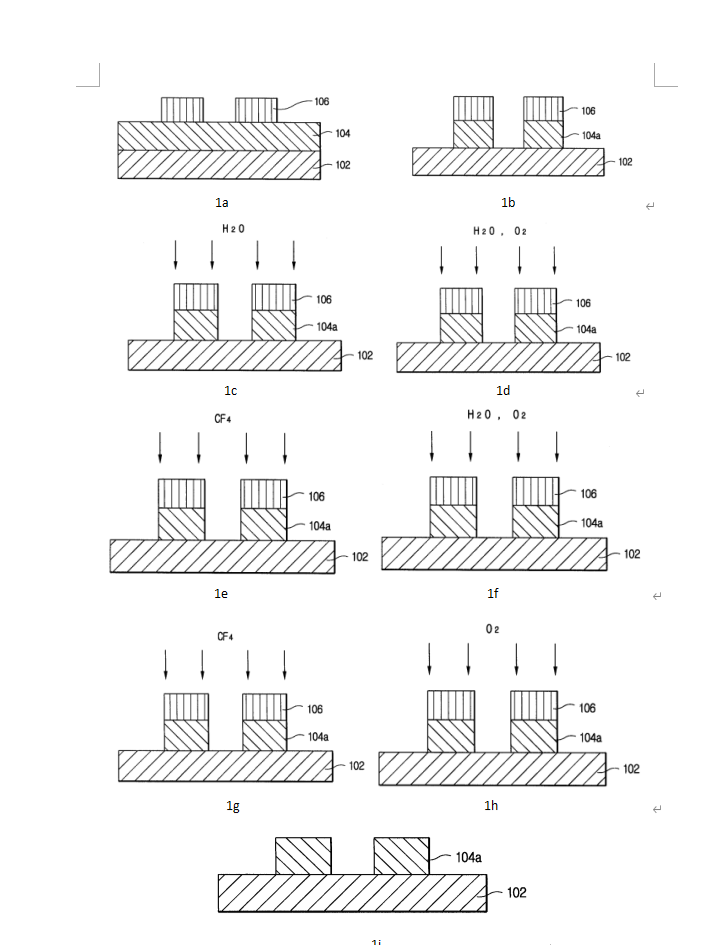

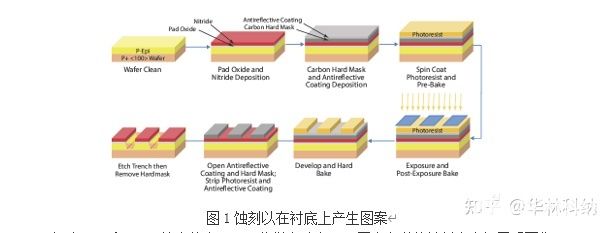

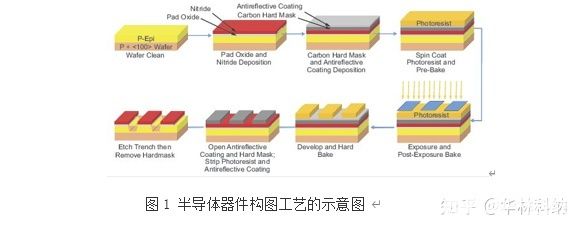

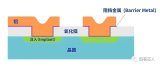

3754 在半導(dǎo)體器件制造中,蝕刻指的是從襯底上的薄膜選擇性去除材料并通過這種去除在襯底上產(chǎn)生該材料的圖案的任何技術(shù),該圖案由抗蝕刻工藝的掩模限定,其產(chǎn)生在光刻中有詳細(xì)描述,一旦掩模就位,可以通過濕法化學(xué)或“干法”物理方法對不受掩模保護的材料進行蝕刻,圖1顯示了這一過程的示意圖。

2022-07-06 17:23:52 4745

4745

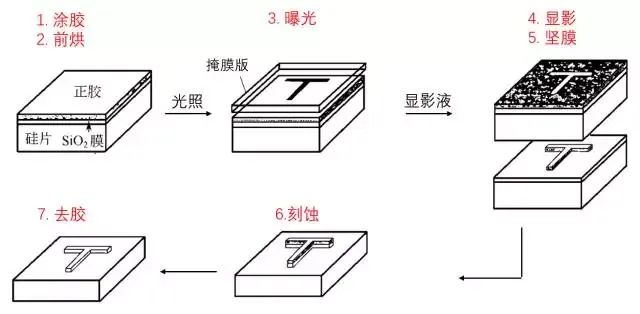

目前為止,在日常生活中使用的每一個電氣和電子設(shè)備中,都是由利用半導(dǎo)體器件制造工藝制造的集成電路組成。電子電路是在由純半導(dǎo)體材料(例如硅和其他半導(dǎo)體化合物)組成的晶片上創(chuàng)建的,其中包括光刻和化學(xué)工藝的多個步驟。

2022-09-22 16:04:44 4357

4357

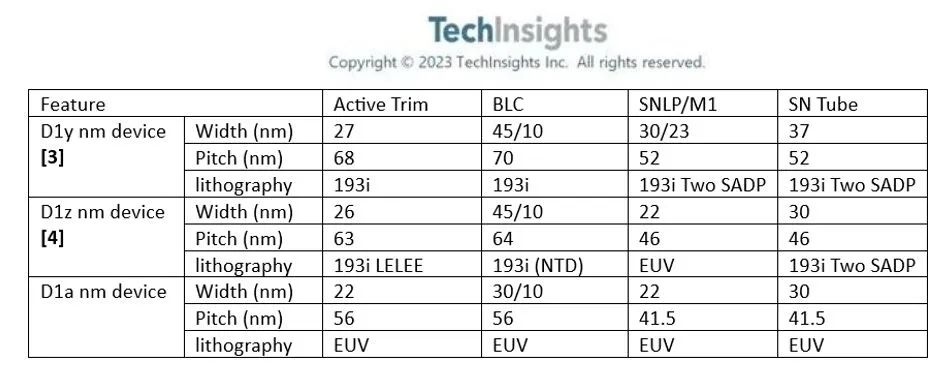

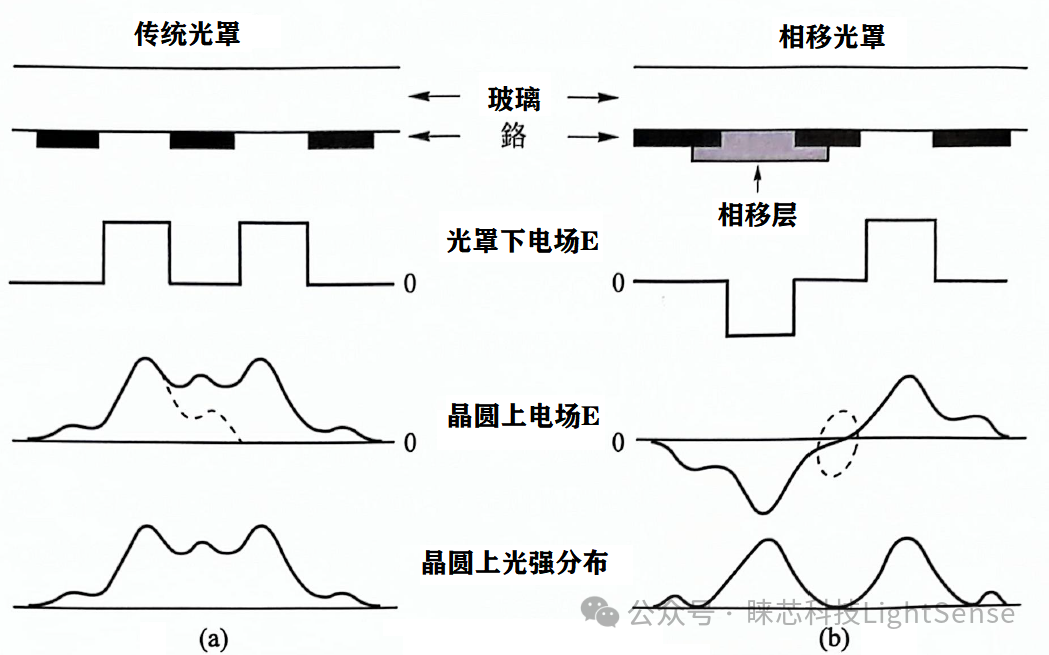

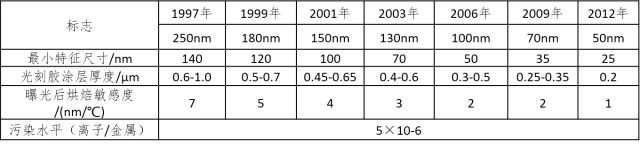

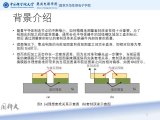

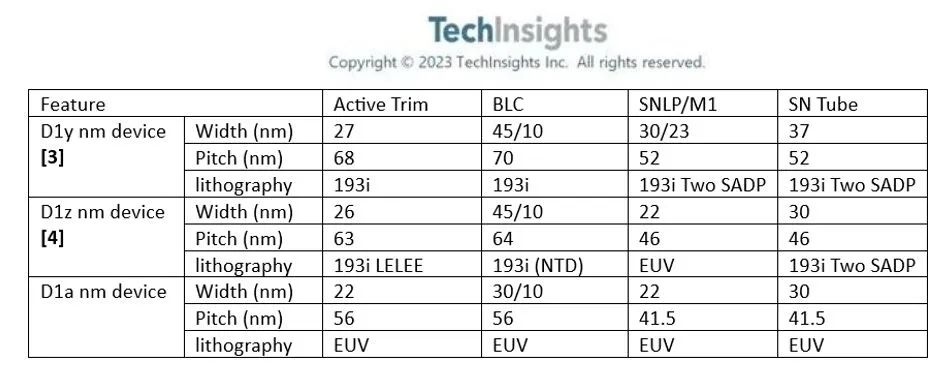

傳統(tǒng)的光刻工藝是相對目前已經(jīng)或尚未應(yīng)用于集成電路產(chǎn)業(yè)的先進光刻工藝而言的,普遍認(rèn)為 193nm 波長的 ArF 深紫外光刻工藝是分水嶺(見下表)。這是因為 193nm 的光刻依靠浸沒式和多重曝光技術(shù)的支撐,可以滿足從 0.13um至7nm 共9個技術(shù)節(jié)點的光刻需要。

2022-10-18 11:20:29 17458

17458 在上一篇文章,我們介紹了光刻工藝,即利用光罩(掩膜)把設(shè)計好的電路圖形繪制在涂覆了光刻膠的晶圓表面上。下一步,將在晶圓上進行刻蝕工藝,以去除不必要的材料,只保留所需的圖形。

2023-06-28 10:04:58 2105

2105

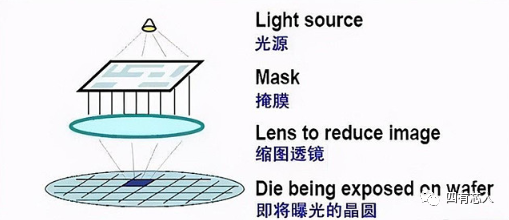

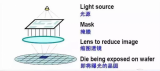

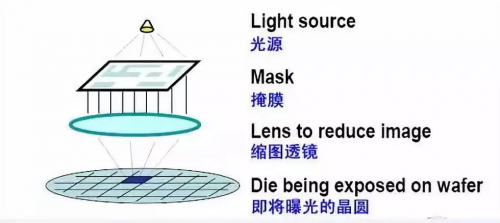

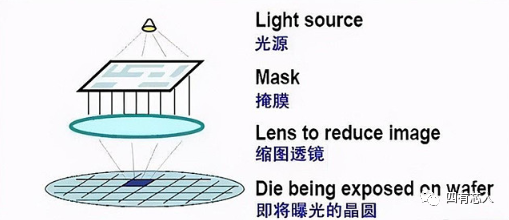

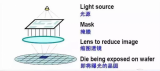

在之前的文章里,我們介紹了晶圓制造、氧化過程和集成電路的部分發(fā)展史。現(xiàn)在,讓我們繼續(xù)了解光刻工藝,通過該過程將電子電路圖形轉(zhuǎn)移到晶圓上。光刻過程與使用膠片相機拍照非常相似。但是具體是怎么實現(xiàn)的呢?

2023-06-28 10:07:47 6929

6929

光刻工藝就是把芯片制作所需要的線路與功能做出來。利用光刻機發(fā)出的光通過具有圖形的光罩對涂有光刻膠的薄片曝光,光刻膠見光后會發(fā)生性質(zhì)變化,從而使光罩上得圖形復(fù)印到薄片上,從而使薄片具有電子線路圖的作用

2023-12-04 09:17:24 6309

6309

光刻工藝貫穿整個芯片制造流程的多次重復(fù)轉(zhuǎn)印環(huán)節(jié),對于集成電路的微縮化和高性能起著決定性作用。隨著半導(dǎo)體制造工藝演進,對光刻分辨率、套準(zhǔn)精度和可靠性的要求持續(xù)攀升,光刻技術(shù)也將不斷演化,支持更為先進的制程與更復(fù)雜的器件設(shè)計。

2025-03-27 09:21:33 3277

3277

工藝設(shè)計與優(yōu)化應(yīng)用領(lǐng)域:集成電路(硅柵、鋁柵CMOS、BiCMOS)、分立器件(DIODE、TRANSISTOR、MOS)、功率器件(DMOS、VDMOS、LDMOS、BCD、IGBT)、特種器件、光電子器件、半導(dǎo)體傳感器、MEMS等`

2015-01-07 16:15:47

介質(zhì)層上的光致抗蝕劑薄層上。 ②刻蝕工藝:利用化學(xué)或物理方法,將抗蝕劑薄層未掩蔽的晶片表面或介質(zhì)層除去,從而在晶片表面或介質(zhì)層上獲得與抗蝕劑薄層圖形完全一致的圖形。集成電路各功能層是立體重疊的,因而光刻工藝

2012-01-12 10:51:59

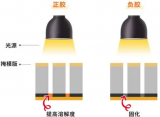

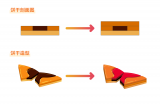

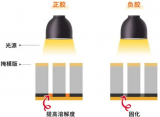

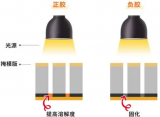

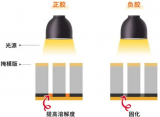

一、光刻膠的選擇光刻膠包括兩種基本的類型:正性光刻和負(fù)性光刻,區(qū)別如下

2021-01-12 10:17:47

關(guān)于光刻工藝的原理,大家可以想象一下膠片照片的沖洗,掩膜版就相當(dāng)于膠片,而光刻機就是沖洗臺,它把掩膜版上的芯片電路一個個的復(fù)制到光刻膠薄膜上,然后通過刻蝕技術(shù)把電路“畫”在晶圓上。 當(dāng)然

2020-07-07 14:22:55

,小米9pro,oppo Reno3以及vivo X30)分別采用了什么芯片? 3協(xié)同通信的方式有哪些? 4大數(shù)據(jù)及認(rèn)知無線電(名詞解釋) 4半導(dǎo)體工藝的4個主要步驟: 4簡敘半導(dǎo)體光刻技術(shù)基本原理 4給出4個全球著名的半導(dǎo)體設(shè)備制造商并指出其生產(chǎn)的設(shè)備核心技術(shù): 5衛(wèi)

2021-07-26 08:31:09

半導(dǎo)體光刻蝕工藝

2021-02-05 09:41:23

本帖最后由 eehome 于 2013-1-5 09:51 編輯

半導(dǎo)體工藝

2012-08-20 09:02:05

有沒有半導(dǎo)體工藝方面的資料啊

2014-04-09 22:42:37

半導(dǎo)體發(fā)展至今,無論是從結(jié)構(gòu)和加工技術(shù)多方面都發(fā)生了很多的改進,如同Gordon E. Moore老大哥預(yù)測的一樣,半導(dǎo)體器件的規(guī)格在不斷的縮小,芯片的集成度也在不斷提升,工藝制程從90nm

2020-12-10 06:55:40

業(yè)界對哪種半導(dǎo)體工藝最適合某一給定應(yīng)用存在著廣泛的爭論。雖然某種特殊工藝技術(shù)能更好地服務(wù)一些應(yīng)用,但其它工藝技術(shù)也有很大的應(yīng)用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-07-05 08:13:58

業(yè)界對哪種半導(dǎo)體工藝最適合某一給定應(yīng)用存在著廣泛的爭論。雖然某種特殊工藝技術(shù)能更好地服務(wù)一些應(yīng)用,但其它工藝技術(shù)也有很大的應(yīng)用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-08-20 08:01:20

半導(dǎo)體工藝講座ObjectiveAfter taking this course, you will able to? Use common semiconductor terminology

2009-11-18 11:31:10

半導(dǎo)體器件與工藝

2012-08-20 08:39:08

功率半導(dǎo)體的熱管理對于元件運行的可靠性和使用壽命至關(guān)重要。本設(shè)計實例介紹的愛普科斯(EPCOS)負(fù)溫度系數(shù)(NTC)和正溫度系數(shù)(PTC)熱敏電阻系列,可以幫助客戶可靠地監(jiān)測半導(dǎo)體元件的溫度。

2020-08-19 06:50:50

` 誰來闡述一下半導(dǎo)體集成電路是什么?`

2020-03-24 17:12:08

ofweek電子工程網(wǎng)訊 國際半導(dǎo)體制造龍頭三星、臺積電先后宣布將于2018年量產(chǎn)7納米晶圓制造工藝。這一消息使得業(yè)界對半導(dǎo)體制造的關(guān)鍵設(shè)備之一極紫外光刻機(EUV)的關(guān)注度大幅提升。此后又有媒體

2017-11-14 16:24:44

`請問PCB蝕刻工藝質(zhì)量要求有哪些?`

2020-03-03 15:31:05

和可靠性。 3 半導(dǎo)體晶圓制造廠的SPC實際應(yīng)用 3.1 半導(dǎo)體生產(chǎn)的特點半導(dǎo)體制造是一個極其復(fù)雜的過程,從氧化擴散,光刻,刻蝕,洗滌,淀積等大約有不少于三四百個工序;特別是現(xiàn)在各類專用集成電路的需求

2018-08-29 10:28:14

一個比較經(jīng)典的半導(dǎo)體工藝制作的課件,英文的,供交流……

2012-02-26 13:12:24

書籍:《炬豐科技-半導(dǎo)體工藝》文章:光刻前 GaAs 表面處理以改善濕化學(xué)蝕刻過程中的光刻膠附著力和改善濕蝕刻輪廓[/td][td]編號:JFSJ-21-0作者:炬豐科技網(wǎng)址:http

2021-07-06 09:39:22

由于集成電路 (IC) 規(guī)模的不斷減小以及對降低成本 、提高產(chǎn)量和環(huán)境友好性的要求不斷提高,半導(dǎo)體器件制造創(chuàng)新技術(shù)的發(fā)展從未停止過。最近在硅濕法清洗工藝中引入臭氧技術(shù)以取代傳統(tǒng)的 RCA 方法引起了業(yè)界的興趣

2021-07-06 09:36:27

`書籍:《炬豐科技-半導(dǎo)體工藝》文章:GaN 納米線制造和單光子發(fā)射器器件應(yīng)用的蝕刻工藝編號:JFSJ-21-045作者:炬豐科技網(wǎng)址:http://www.wetsemi.com

2021-07-08 13:11:24

`書籍:《炬豐科技-半導(dǎo)體工藝》文章:IC制造工藝編號:JFSJ-21-046作者:炬豐科技網(wǎng)址:http://www.wetsemi.com/index.html摘要:集成電路的制造主要包括以下工藝

2021-07-08 13:13:06

書籍:《炬豐科技-半導(dǎo)體工藝》文章:III-V族半導(dǎo)體納米線結(jié)構(gòu)的光子學(xué)特性編號:JFSJ-21-075作者:炬豐科技 摘要:III-V 族半導(dǎo)體納米線 (NW) 由于其沿納米線軸對電子和光子

2021-07-09 10:20:13

:MacEtch 是一種濕法蝕刻工藝,可提供對取向、長度、形態(tài)等結(jié)構(gòu)參數(shù)的可控性,此外,它是一種制造極高縱橫比半導(dǎo)體納米結(jié)構(gòu)的簡單且低成本的方法。 3 該工藝利用了在氧化劑(例如過氧化氫 (H2O2))和酸(例如

2021-07-06 09:33:58

`書籍:《炬豐科技-半導(dǎo)體工藝》文章:超大規(guī)模集成電路制造技術(shù)簡介編號:JFSJ-21-076作者:炬豐科技概括VLSI制造中使用的材料材料根據(jù)其導(dǎo)電特性可分為三大類:絕緣體導(dǎo)體半導(dǎo)體

2021-07-09 10:26:01

曝光部分,負(fù)性光刻膠去除未曝光部分)->預(yù)烘烤->曝光->顯影

提到了一個公式R=kλ/NA即分辨率正比于波長λ

然后介紹了蝕刻工藝的形狀加工

2024-12-16 23:35:46

哪種半導(dǎo)體工藝最適合某一指定應(yīng)用?對此,業(yè)界存在著廣泛的爭論。雖然某種特殊工藝技術(shù)能更好地服務(wù)一些應(yīng)用,但其它工藝技術(shù)也有很大的應(yīng)用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-08-02 08:23:59

1、GaAs半導(dǎo)體材料可以分為元素半導(dǎo)體和化合物半導(dǎo)體兩大類,元素半導(dǎo)體指硅、鍺單一元素形成的半導(dǎo)體,化合物指砷化鎵、磷化銦等化合物形成的半導(dǎo)體。砷化鎵的電子遷移速率比硅高5.7 倍,非常適合

2019-07-29 07:16:49

1、 電子、物理、通信、材料等專業(yè),本科以上學(xué)歷,3年以上的PECVD\LPCVD沉積工作經(jīng)驗; 2、 了解半導(dǎo)體工藝、精通PECVD或LPCVD材料生長技術(shù); 3、 精通PECVD或LPCVD設(shè)備

2012-12-19 22:42:16

——薄膜制作(Layer)、圖形光刻(Pattern)、刻蝕和摻雜,再到測試封裝,一目了然。 全書共分20章,根據(jù)應(yīng)用于半導(dǎo)體制造的主要技術(shù)分類來安排章節(jié),包括與半導(dǎo)體制造相關(guān)的基礎(chǔ)技術(shù)信息;總體流程圖

2025-04-15 13:52:11

問個菜的問題:半導(dǎo)體(或集成電路)工藝 來個人講講 半導(dǎo)體工藝 集成電路工藝 硅工藝 CMOS工藝的概念和區(qū)別以及聯(lián)系吧。查了一下:集成電路工藝(integrated

2009-09-16 11:51:34

氮化鎵功率半導(dǎo)體技術(shù)解析基于GaN的高級模塊

2021-03-09 06:33:26

circuit)是一種微型電子器件或部件。采用一定的工藝,把一個電路中所需的晶體管、電阻、電容和電感等元件及布線互連一起,制作在一小塊或幾小塊半導(dǎo)體晶片或介質(zhì)基片上,然后封裝在一個管殼內(nèi),成為具有所需電路功能

2020-02-18 13:23:44

solasidobobo@126.com地址-受新加坡公司委托現(xiàn)招聘半導(dǎo)體工程師數(shù)名。主要包括:半導(dǎo)體制成整合,光刻,蝕刻,薄膜,擴散等工藝和設(shè)備工程師要求:本科及以上相關(guān)專業(yè)畢業(yè),一年以上fab工作經(jīng)驗待遇:月薪

2009-10-12 11:10:18

solasidobobo@126.com地址-受新加坡公司委托現(xiàn)招聘半導(dǎo)體工程師數(shù)名。主要包括:半導(dǎo)體制成整合,光刻,蝕刻,薄膜,擴散等工藝和設(shè)備工程師要求:本科及以上相關(guān)專業(yè)畢業(yè),一年以上fab工作經(jīng)驗待遇:月薪

2009-10-12 11:15:49

,元素半導(dǎo)體指硅、鍺單一元素形成的半導(dǎo)體,化合物指砷化鎵、磷化銦等化合物形成的半導(dǎo)體。隨著無線通信的發(fā)展,高頻電路應(yīng)用越來越廣,今天我們來介紹適合用于射頻、微波等高頻電路的半導(dǎo)體材料及工藝情況。

2019-06-27 06:18:41

集成電路是一種微型電子器件或部件,它是采用一定的工藝,把一個電路中所需的晶體管、電阻、電容和電感等元件及布線互連一起,制作在一小塊或幾小塊半導(dǎo)體晶片或介質(zhì)基片上,然后封裝在一個管殼內(nèi),成為具有

2021-09-15 06:45:56

Intel 22nm光刻工藝背后的故事

去年九月底的舊金山秋季IDF 2009論壇上,Intel第一次向世人展示了22nm工藝晶圓,并宣布將在2011年下半年發(fā)布相關(guān)產(chǎn)品。

2010-03-24 08:52:58 1395

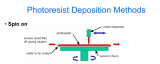

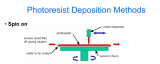

1395 光刻膠與光刻工藝技術(shù) 微電路的制造需要把在數(shù)量上精確控制的雜質(zhì)引入到硅襯底上的微小 區(qū)域內(nèi),然后把這些區(qū)域連起來以形成器件和VLSI電路.確定這些區(qū)域圖形 的工藝是由光刻來完成的,也就是說,首先在硅片上旋轉(zhuǎn)涂覆光刻膠,再將 其曝露于某種光源下,如紫外光,

2011-03-09 16:43:21 0

0 光刻的本質(zhì)是把制作在掩膜版上的圖形復(fù)制到以 后要進行刻蝕和離子注入的晶圓上。其原理與照相 相似,不同的是半導(dǎo)體晶圓與光刻膠代替了照相底 片與感光涂層。

2016-06-08 14:55:42 0

0 光刻是半導(dǎo)體芯片生產(chǎn)流程中最復(fù)雜、最關(guān)鍵的工藝步驟,耗時長、成本高。半導(dǎo)體芯片生產(chǎn)的難點和關(guān)鍵點在于將電路圖從掩模上轉(zhuǎn)移至硅片上,這一過程通過光刻來實現(xiàn), 光刻的工藝水平直接決定芯片的制程水平和性能

2018-04-08 16:10:52 171954

171954

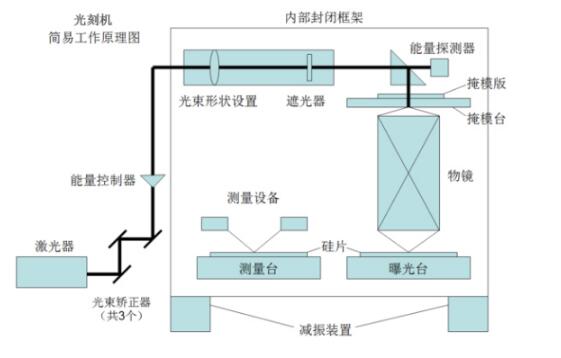

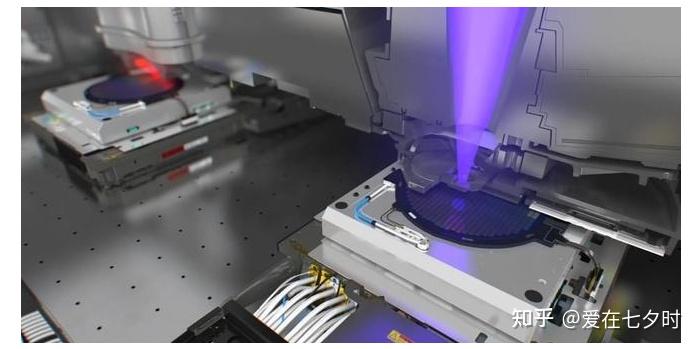

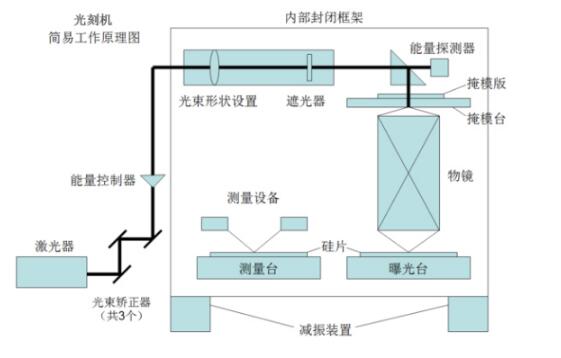

光刻機(Mask Aligner) 又名:掩模對準(zhǔn)曝光機,曝光系統(tǒng),光刻系統(tǒng)等。一般的光刻工藝要經(jīng)歷硅片表面清洗烘干、涂底、旋涂光刻膠、軟烘、對準(zhǔn)曝光、后烘、顯影、硬烘、刻蝕等工序。

2018-04-10 09:49:17 134949

134949

本文首先介紹了PCB蝕刻工藝原理和蝕刻工藝品質(zhì)要求及控制要點,其次介紹了PCB蝕刻工藝制程管控參數(shù)及蝕刻工藝品質(zhì)確認(rèn),最后闡述了PCB蝕刻工藝流程詳解,具體的跟隨小編一起來了解一下吧。

2018-05-07 09:09:09 48549

48549 隨著三星宣布7nm EUV工藝的量產(chǎn),2018年EUV光刻工藝終于商業(yè)化了,這是EUV工藝研發(fā)三十年來的一個里程碑。不過EUV工藝要想大規(guī)模量產(chǎn)還有很多技術(shù)挑戰(zhàn),目前的光源功率以及晶圓產(chǎn)能輸出還沒有

2018-10-30 16:28:40 4245

4245 圖形化工藝是要在晶圓內(nèi)和表面層建立圖形的一系列加工,這些圖形根據(jù)集成電路中物理部件的要求來確定其尺寸和位置。 圖形化工藝還包括光刻、光掩模、掩模、去除氧化膜、去除金屬膜和微光刻。圖形化工藝是半導(dǎo)體

2018-12-03 16:46:01 2620

2620 的占地面積。

半導(dǎo)體制造

在光刻工藝中,通常首先在硅晶圓上沉積一層光敏性光致抗蝕劑材料(光刻膠)。然后,光束通過光掩模照射到晶圓上,以將掩模圖形呈現(xiàn)在光刻膠上,再使用顯影劑溶解掉經(jīng)過曝光

2019-05-08 15:27:34 3275

3275 KLA-Tencor光刻工藝控制解決方案將產(chǎn)量優(yōu)化至0.13微米 SAN JOSE - KLA-Tencor公司推出了一款工藝模塊控制(PMC)解決方案芯片制造商實施和控制0.13微米及更小

2020-02-14 11:05:23 1983

1983 重要要點 l 什么是光刻? l 光刻工藝的類型。 l 光刻處理如何用于電路板成像。 l 工業(yè)平版印刷處理設(shè)計指南。 可以說,有史以來研究最多的文物是都靈裹尸布。進行廣泛檢查的原因,從來源的宗教建議

2020-09-16 21:01:16 2207

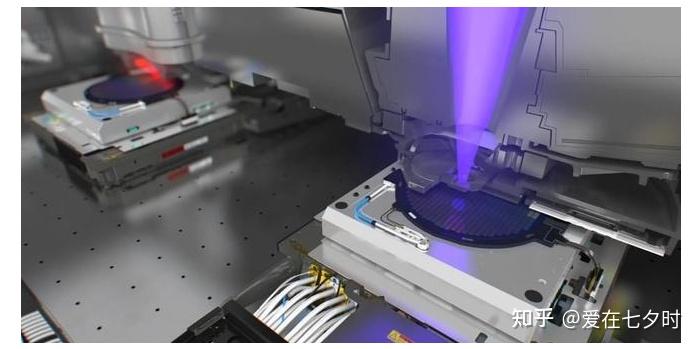

2207 光刻機又名:掩模對準(zhǔn)曝光機,曝光系統(tǒng),光刻系統(tǒng)等,是制造芯片的核心裝備。它采用類似照片沖印的技術(shù),把掩膜版上的精細(xì)圖形通過光線的曝光印制到硅片上。光刻機是半導(dǎo)體產(chǎn)業(yè)中最關(guān)鍵設(shè)備,光刻工藝決定了半導(dǎo)體線路的線寬,同時也決定了芯片的性能和功耗。

2020-09-30 16:17:13 6909

6909

在一顆芯片誕生的過程中,光刻是最關(guān)鍵又最復(fù)雜的一步。 說最關(guān)鍵,是因為光刻的實質(zhì)將掩膜版上的芯片電路圖轉(zhuǎn)移至硅片,化虛為實。說最復(fù)雜,是因為光刻工藝需要經(jīng)歷硅片表面清洗烘干、涂底、旋涂光刻膠、軟烘

2020-11-26 16:19:19 3224

3224 。后一種工藝是集成電路微制造技術(shù)的基礎(chǔ)。微電子工業(yè)不斷增長的需求需要光刻材料(光刻劑),具有亞微米分辨率、高靈敏度、對微電子中常用的基質(zhì)的良好粘附,以及對廣泛的等離子體和濕化學(xué)蝕刻劑的高抗性。 非晶態(tài)半導(dǎo)體材料

2022-01-19 16:08:46 847

847

平版印刷術(shù)被定義為“一種從已經(jīng)準(zhǔn)備好的平坦表面(如光滑的石頭或金屬板)印刷的方法,以便油墨僅粘附在將要印刷的設(shè)計上”。在半導(dǎo)體器件制造中,石頭是硅片,而墨水是沉積、光刻和蝕刻工藝的綜合效果,從而產(chǎn)生

2022-03-14 15:20:53 3396

3396

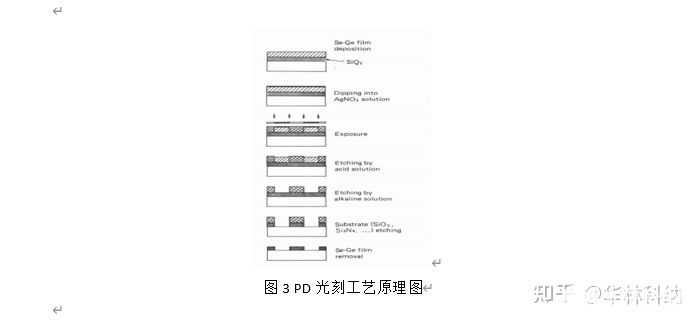

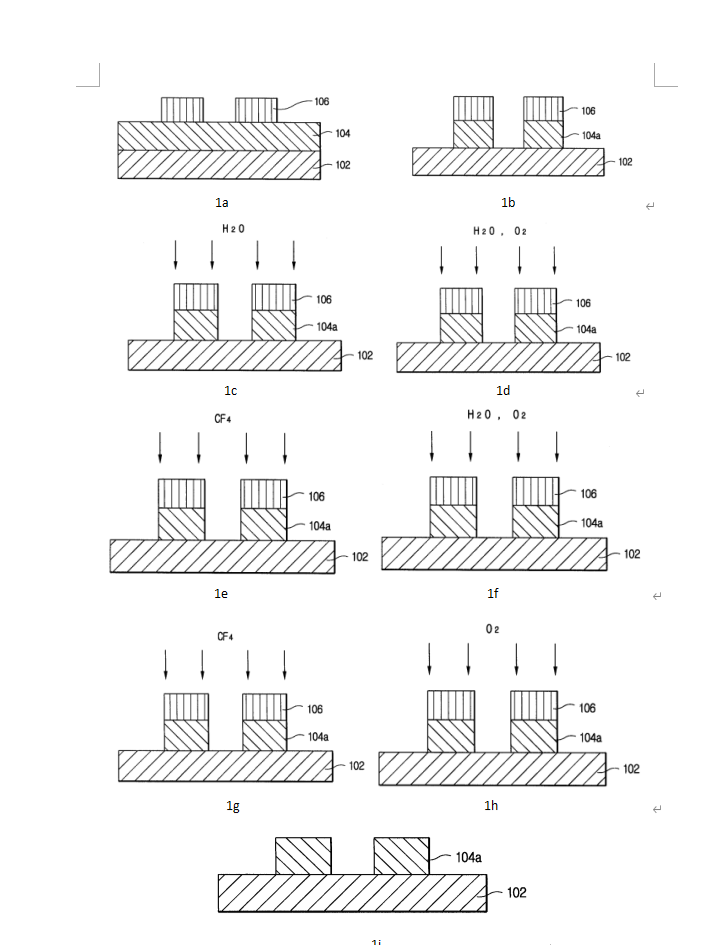

本發(fā)明涉及一種去除光刻膠的方法,更詳細(xì)地說,是一種半導(dǎo)體制造用光刻膠去除方法,該方法適合于在半導(dǎo)體裝置的制造過程中進行吹掃以去除光刻膠。在半導(dǎo)體裝置的制造工藝中,將殘留在晶片上的光刻膠,在H2O

2022-04-13 13:56:42 1659

1659

先進光刻工藝EUV相關(guān)知識,適合對半導(dǎo)體工藝有興趣的人員,或者是從事光刻工藝的工程師

2022-06-13 14:48:23 1

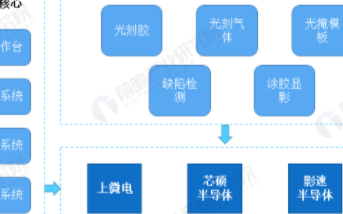

1 光刻膠作為影響光刻效果核心要素之一,是電子產(chǎn)業(yè)的關(guān)鍵材料。光刻膠由溶劑、光引發(fā)劑和成膜樹脂三種主要成分組成,是一種具有光化學(xué)敏感性的混合液體。其利用光化學(xué)反應(yīng),經(jīng)曝光、顯影等光刻工藝,將所需要的微細(xì)圖形從掩模版轉(zhuǎn)移到待加工基片上,是用于微細(xì)加工技術(shù)的關(guān)鍵性電子化學(xué)品。

2022-06-21 09:30:09 22720

22720 光刻是半導(dǎo)體工藝中最關(guān)鍵的步驟之一。EUV是當(dāng)今半導(dǎo)體行業(yè)最熱門的關(guān)鍵詞,也是光刻技術(shù)。為了更好地理解 EUV 是什么,讓我們仔細(xì)看看光刻技術(shù)。

2022-10-18 12:54:05 6458

6458 光刻機譽為“現(xiàn)代半導(dǎo)體行業(yè)皇冠上的明珠”,是一種高度復(fù)雜的設(shè)備。光刻機是通過紫外光作為“畫筆”,把預(yù)先設(shè)計好的芯片電路路線書寫在硅晶圓旋涂的光刻膠上,光刻工藝直接決定了芯片中晶體管的尺寸和性能,是芯片生產(chǎn)中最為關(guān)鍵的過程。

2022-10-27 09:39:02 4799

4799 光刻是半導(dǎo)體工業(yè)的核心技術(shù)。自1960年Fairchild Semiconductor的羅伯特·諾伊斯發(fā)明單片集成電路以來,光刻一直是主要的光刻技術(shù)。

2022-11-14 11:36:46 4275

4275 來源:云天半導(dǎo)體 廈門云天半導(dǎo)體繼九月初812吋 “晶圓級封裝與無源器件生產(chǎn)線”正式通線后,經(jīng)過團隊的不懈努力, 8英寸晶圓Fine Pitch光刻工藝開發(fā)終破2/2um L/S大關(guān); 以下為部分工藝

2022-11-30 17:07:07 2533

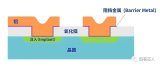

2533 功率半導(dǎo)體分立器件的主要工藝流程包括:在硅圓片上加工芯片(主要流程為薄膜制造、曝光和刻蝕),進行芯片封裝,對加工完畢的芯片進行技術(shù)性能指標(biāo)測試,其中主要生產(chǎn)工藝有外延工藝、光刻工藝、刻蝕工藝、離子注入工藝和擴散工藝等。

2023-02-24 15:34:13 6139

6139 那時集成電路也剛剛發(fā)明不久,光刻工藝還在微米級別,工藝步驟也比現(xiàn)在簡單很多美國是走在世界前列的。在那個對工藝要求并不高的年代,很多半導(dǎo)體公司通常自己用鏡頭設(shè)計光刻工具,光刻機在當(dāng)時甚至不如照相機的結(jié)構(gòu)復(fù)雜。

2023-04-20 09:22:33 2429

2429 金屬-氧化物半導(dǎo)體場效應(yīng)晶體管(MOSFET)的革命,讓我們可以在相同面積的晶圓上同時制造出更多晶體管。MOSFET體積越小,單個 MOSFET的耗電量就越少,還可以制造出更多的晶體管,讓其發(fā)揮作用,可謂是一舉多得。

2023-06-13 12:29:09 1688

1688

Dimension, CD)小型化(2D視角),刻蝕工藝從濕法刻蝕轉(zhuǎn)為干法刻蝕,因此所需的設(shè)備和工藝更加復(fù)雜。由于積極采用3D單元堆疊方法,刻蝕工藝的核心性能指數(shù)出現(xiàn)波動,從而刻蝕工藝與光刻工藝成為半導(dǎo)體制造的重要工藝流程之一。

2023-06-26 09:20:10 3193

3193

在半導(dǎo)體制程中,移除殘余材料的“減法工藝”不止“刻蝕”一種,引入其他材料的“加法工藝”也非“沉積”一種。比如,光刻工藝中的光刻膠涂敷,其實也是在基底上形成各種薄膜;又如氧化工藝中晶圓(硅)氧化,也需要在基底表面添加各種新材料。那為什么唯獨要強調(diào)“沉積”工藝呢?

2023-06-29 16:58:37 1956

1956

半導(dǎo)體同時具有“導(dǎo)體”的特性,因此允許電流通過,而絕緣體則不允許電流通過。離子注入工藝將雜質(zhì)添加到純硅中,使其具有導(dǎo)電性能。我們可以根據(jù)實際需要使半導(dǎo)體導(dǎo)電或絕緣。 重復(fù)光刻、刻蝕和離子注入步驟會在

2023-07-03 10:21:57 4672

4672

外,學(xué)生還就感興趣的課題做深入調(diào)研。師生共同討論調(diào)研報告,實現(xiàn)教學(xué)互動。調(diào)研的內(nèi)容涉及光刻工藝、光刻成像理論、SMO、OPC和DTCO技術(shù)。

2023-07-07 11:21:32 1451

1451

半導(dǎo)體制作工藝可分為前端和后端:前端主要是晶圓制作和光刻(在晶圓上繪制電路);后端主要是芯片的封裝。

2023-07-24 15:46:05 4234

4234

金屬-氧化物半導(dǎo)體場效應(yīng)晶體管(MOSFET)的革命,讓我們可以在相同面積的晶圓上同時制造出更多晶體管。

2023-07-27 15:24:51 1869

1869

在半導(dǎo)體制程中,移除殘余材料的“減法工藝”不止“刻蝕”一種,引入其他材料的“加法工藝”也非“沉積”一種。比如,光刻工藝中的光刻膠涂敷,其實也是在基底上形成各種薄膜;又如氧化工藝中晶圓(硅)氧化,也需要在基底表面添加各種新材料。那為什么唯獨要強調(diào)“沉積”工藝呢?

2023-08-17 15:33:27 2485

2485

光刻是半導(dǎo)體芯片生產(chǎn)流程中最復(fù)雜、最關(guān)鍵的工藝步驟,耗時長、成本高。半導(dǎo)體芯片生產(chǎn)的難點和關(guān)鍵點在于將電路圖從掩模上轉(zhuǎn)移至硅片上,這一過程通過光刻來實現(xiàn), 光刻的工藝水平直接決定芯片的制程水平和性能水平。

2023-08-23 10:47:53 5496

5496

半導(dǎo)體制造工藝之光刻工藝詳解

2023-08-24 10:38:54 3038

3038

光刻膠作為影響光刻效果核心要素之一,是電子產(chǎn)業(yè)的關(guān)鍵材料。光刻膠由溶劑、光引發(fā)劑和成膜樹脂三種主要成分組成,是一種具有光化學(xué)敏感性的混合液體。其利用光化學(xué)反應(yīng),經(jīng)曝光、顯影等光刻工藝,將所需要的微細(xì)圖形從掩模版轉(zhuǎn)移到待加工基片上,是用于微細(xì)加工技術(shù)的關(guān)鍵性電子化學(xué)品。

2023-10-09 14:34:49 5550

5550

三星D1a nm LPDDR5X器件的EUV光刻工藝

2023-11-23 18:13:02 2010

2010

[半導(dǎo)體前端工藝:第三篇] 光刻——半導(dǎo)體電路的繪制

2023-11-29 11:25:52 1682

1682

光照條件的設(shè)置、掩模版設(shè)計以及光刻膠工藝等因素對分辨率的影響都反映在k?因子中,k?因子也常被用于評估光刻工藝的難度,ASML認(rèn)為其物理極限在0.25,k?體現(xiàn)了各家晶圓廠運用光刻技術(shù)的水平。

2023-12-18 10:53:05 2730

2730

在萬物互聯(lián),AI革命興起的今天,半導(dǎo)體芯片已成為推動現(xiàn)代社會進步的心臟。而光刻(Lithography)技術(shù),作為先進制造中最為精細(xì)和關(guān)鍵的工藝,不管是半導(dǎo)體芯片、MEMS器件,還是微納光學(xué)元件都離不開光刻工藝的參與,其重要性不言而喻。本文將帶您一起認(rèn)識光刻工藝的基本知識。

2024-08-26 10:10:07 3247

3247

原文標(biāo)題:一文看懂光刻膠的堅膜工藝及物理特性和常見光刻

2024-11-01 11:08:07 3091

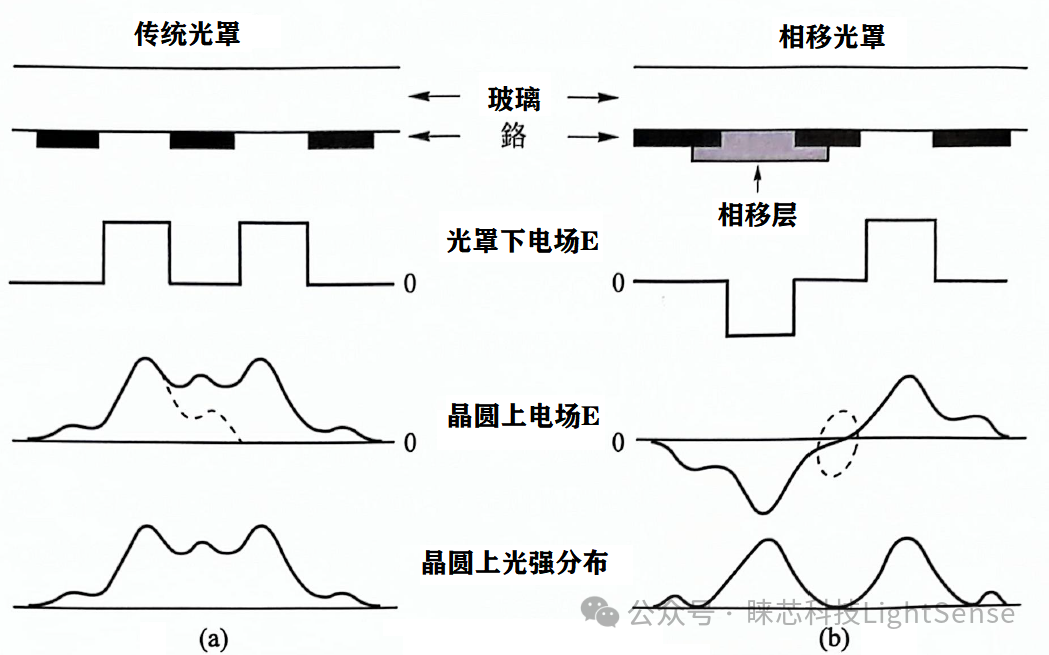

3091 分辨率增強及技術(shù)(Resolution Enhancement Technique, RET)實際上就是根據(jù)已有的掩膜版設(shè)計圖形,通過模擬計算確定最佳光照條件,以實現(xiàn)最大共同工藝窗口(Common Process Window),這部分工作一般是在新光刻工藝研發(fā)的早期進行 。

2024-10-18 15:11:47 2854

2854

“ 光刻作為半導(dǎo)體中的關(guān)鍵工藝,其中包括3大步驟的工藝:涂膠、曝光、顯影。三個步驟有一個異常,整個光刻工藝都需要返工處理,因此現(xiàn)場異常的處理顯得尤為關(guān)鍵”

2024-10-22 13:52:10 3498

3498 對光的敏感度。在半導(dǎo)體制造過程中,光刻膠通過光化學(xué)反應(yīng),將掩膜版上的圖案精確地轉(zhuǎn)移到硅片表面。 光刻工藝是半導(dǎo)體制造的核心步驟之一。在硅片表面涂上光刻膠(負(fù)膠)后,使用特定波長的光線通過掩膜版照射到光刻膠上,被

2024-12-19 13:57:36 2091

2091 半導(dǎo)體設(shè)備安裝防震裝置主要有以下幾方面原因:一、高精度加工要求1,光刻工藝(1)光刻是半導(dǎo)體制造的關(guān)鍵步驟,其精度要求極高。例如,在芯片制造中,光刻設(shè)備需要將電路圖案精確地投射到硅片上。現(xiàn)代光刻技術(shù)

2025-02-05 16:48:03 874

874

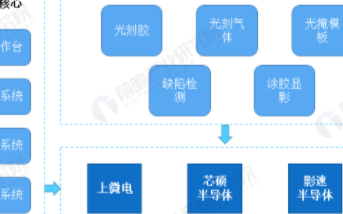

光刻是廣泛應(yīng)用的芯片加工技術(shù)之一,下圖是常見的半導(dǎo)體加工工藝流程。

2025-03-04 17:07:04 2121

2121

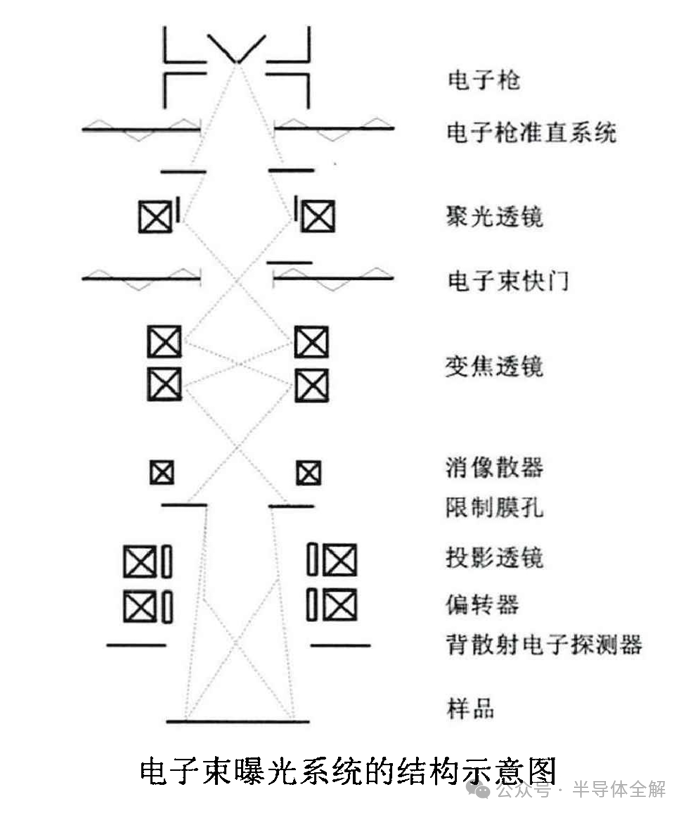

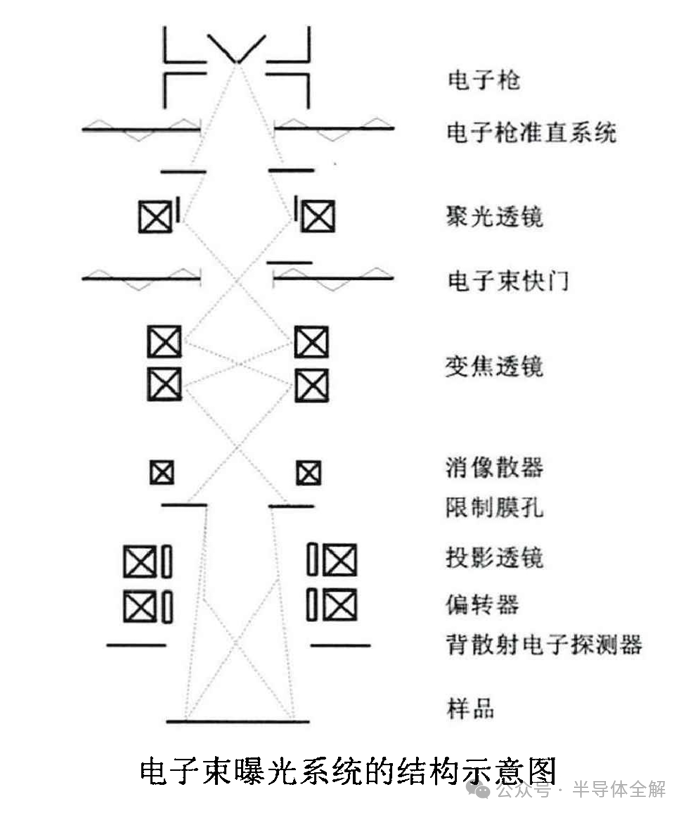

一、光刻工藝概述 光刻工藝是半導(dǎo)體制造的核心技術(shù),通過光刻膠在特殊波長光線或者電子束下發(fā)生化學(xué)變化,再經(jīng)過曝光、顯影、刻蝕等工藝過程,將設(shè)計在掩膜上的圖形轉(zhuǎn)移到襯底上,是現(xiàn)代半導(dǎo)體、微電子、信息產(chǎn)業(yè)

2025-06-09 15:51:16 2129

2129 光刻工藝是芯片制造的關(guān)鍵步驟,其精度直接決定集成電路的性能與良率。隨著制程邁向3nm及以下,光刻膠圖案三維結(jié)構(gòu)和層間對準(zhǔn)精度的控制要求達納米級,傳統(tǒng)檢測手段難滿足需求。光子灣3D共聚焦顯微鏡憑借非

2025-08-05 17:46:43 946

946

一、引言

玻璃晶圓在半導(dǎo)體制造、微流控芯片等領(lǐng)域應(yīng)用廣泛,光刻工藝作為決定器件圖案精度與性能的關(guān)鍵環(huán)節(jié),對玻璃晶圓的質(zhì)量要求極為嚴(yán)苛 。總厚度偏差(TTV)是衡量玻璃晶圓質(zhì)量的重要指標(biāo),其厚度

2025-10-09 16:29:24 576

576

如有雷同或是不當(dāng)之處,還請大家海涵。當(dāng)前在各網(wǎng)絡(luò)平臺上均以此昵稱為ID跟大家一起交流學(xué)習(xí)! 在半導(dǎo)體行業(yè),光刻(Photo)工藝技術(shù)就像一位技藝高超的藝術(shù)家,負(fù)責(zé)將復(fù)雜的電路圖案從掩模轉(zhuǎn)印到光滑的半導(dǎo)體晶圓上。作為制造過

2025-11-10 09:27:48 1755

1755

泊蘇 Type C 系列防震基座在半導(dǎo)體光刻加工電子束光刻設(shè)備的應(yīng)用案例-江蘇泊蘇系統(tǒng)集成有限公司一、企業(yè)背景與光刻加工電子束光刻設(shè)備挑戰(zhàn)某大型半導(dǎo)體制造企業(yè)專注于高端芯片的研發(fā)與生產(chǎn)

2025-01-07 15:13:21

電子發(fā)燒友App

電子發(fā)燒友App

評論