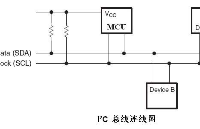

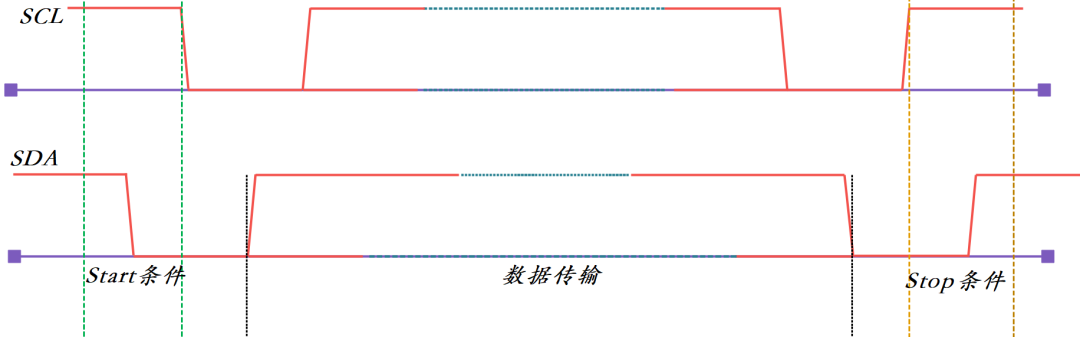

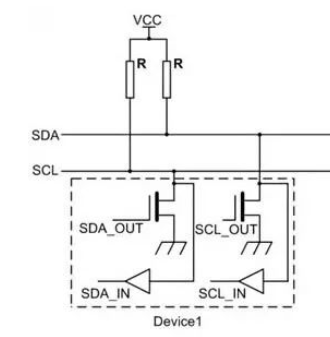

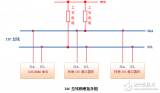

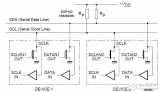

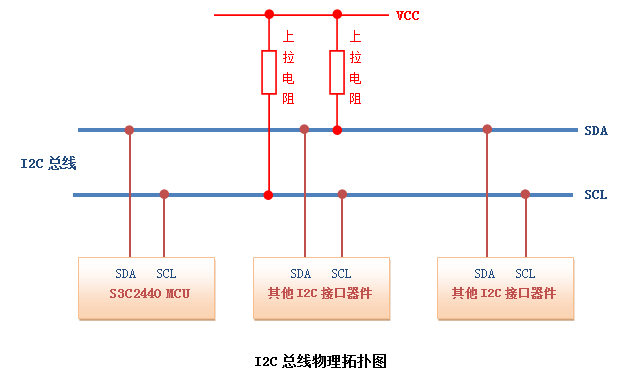

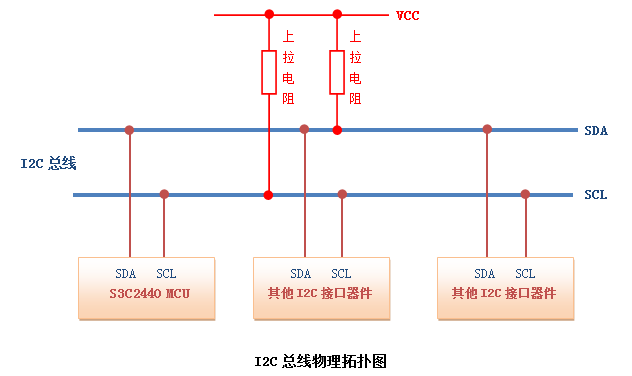

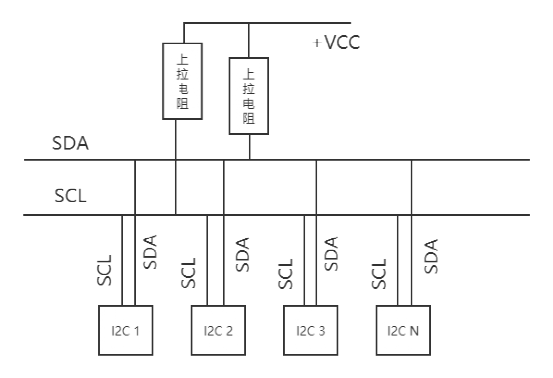

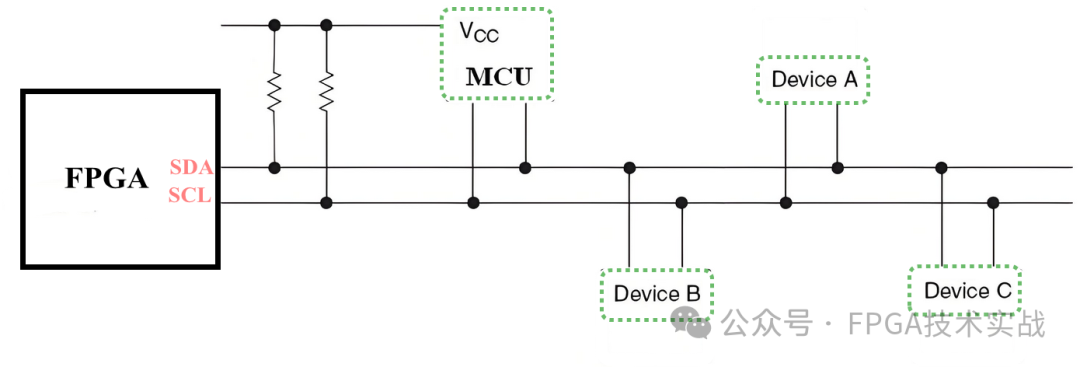

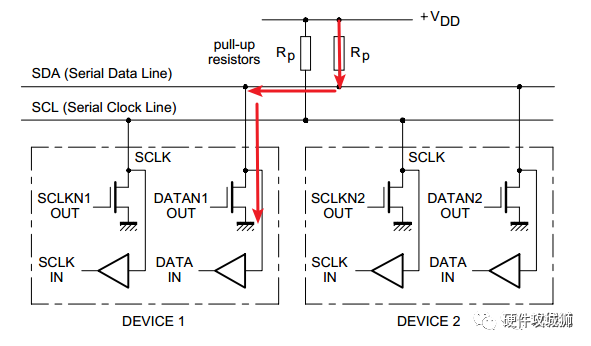

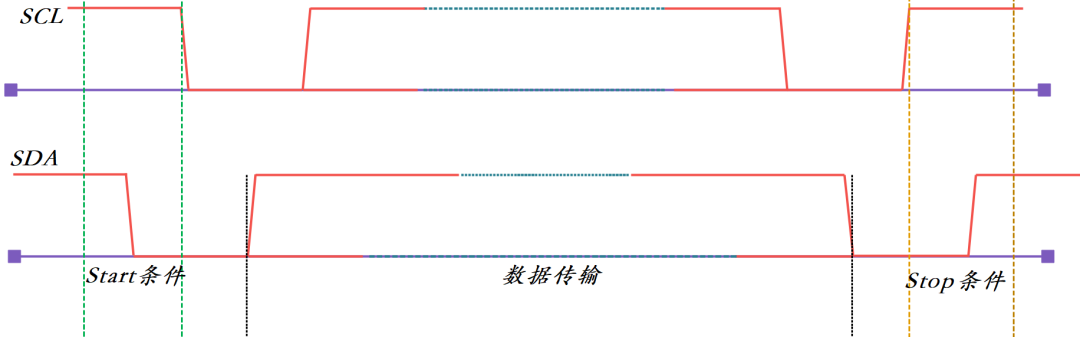

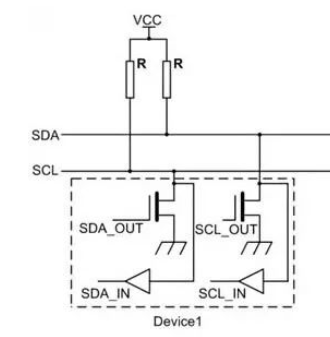

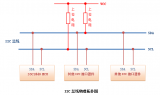

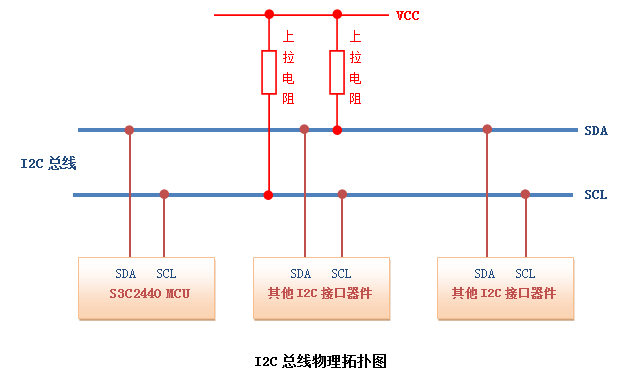

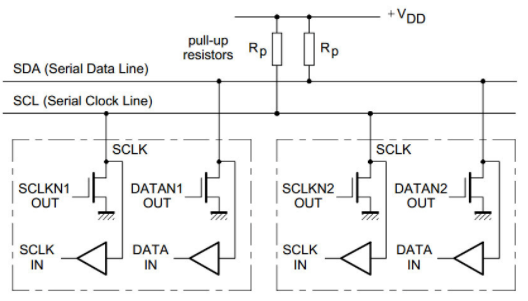

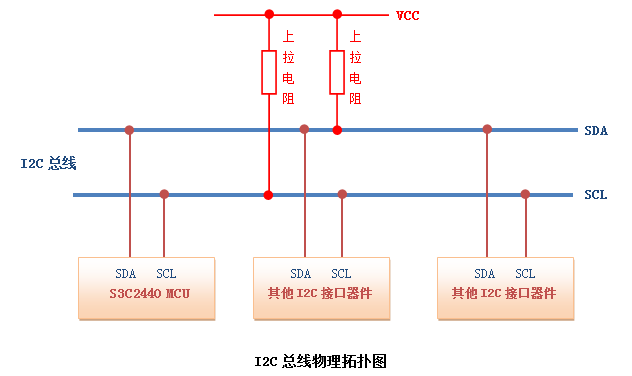

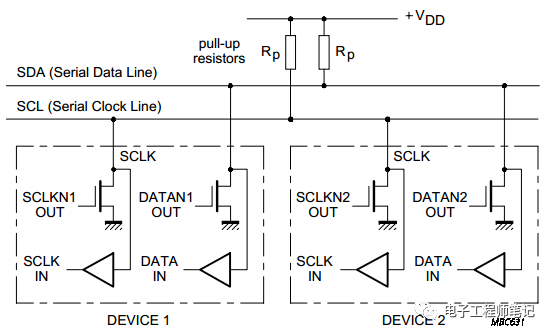

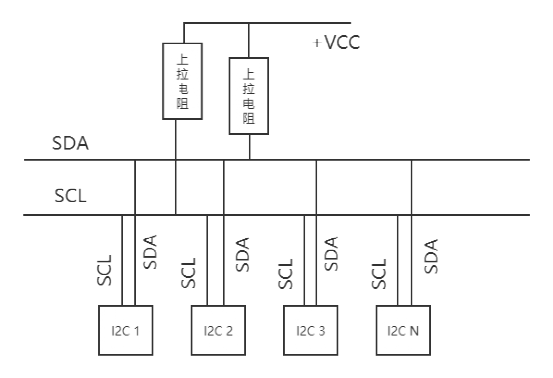

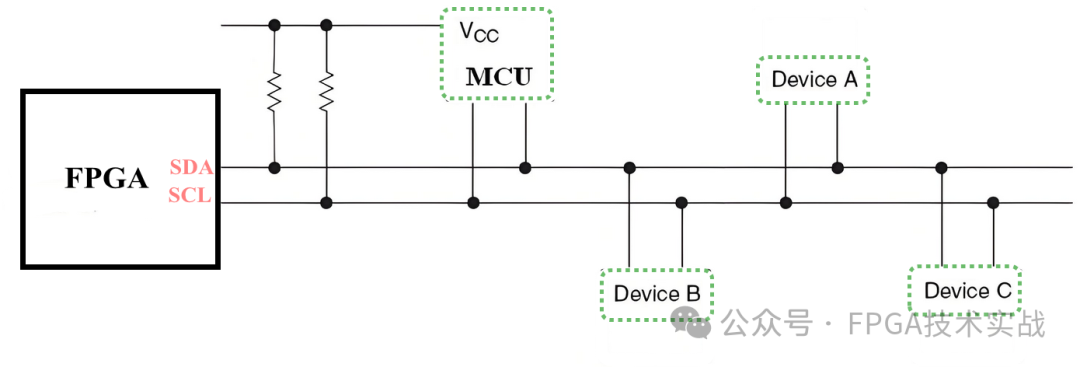

I2C 總線在物理連接上非常簡單,分別由SDA(串行數據線)和SCL(串行時鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時序的控制,來 產生I2C總線協議所需要的信號進行數據的傳遞。在總線空閑狀態時,這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2022-08-04 08:51:58 1091

1091 我們知道,在I2C的電路中,在SCL、SDA線與電源之間通常會接一個電阻,這個電阻稱之為上拉電阻。 但什么是上拉電阻? 上拉電阻主要用于為信號線或GPIO引腳提供默認狀態。

2022-09-08 14:43:24 8554

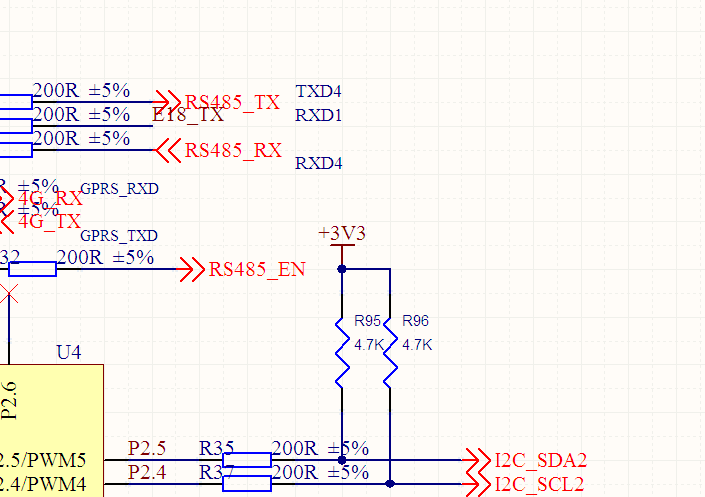

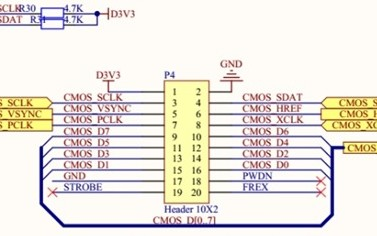

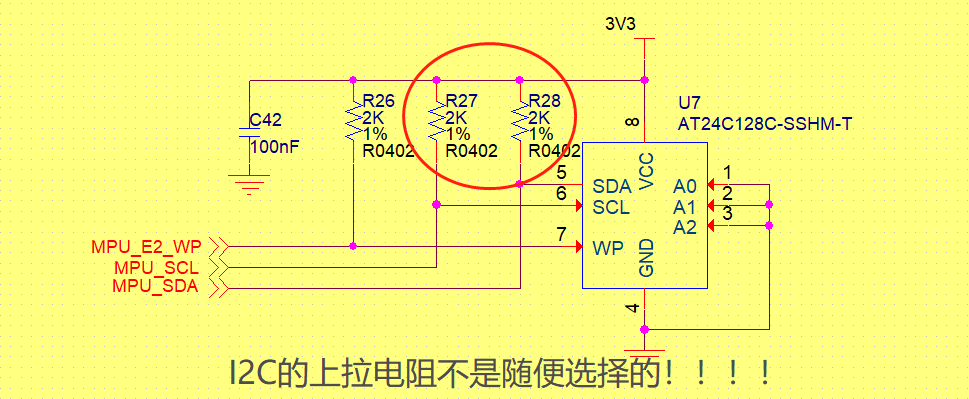

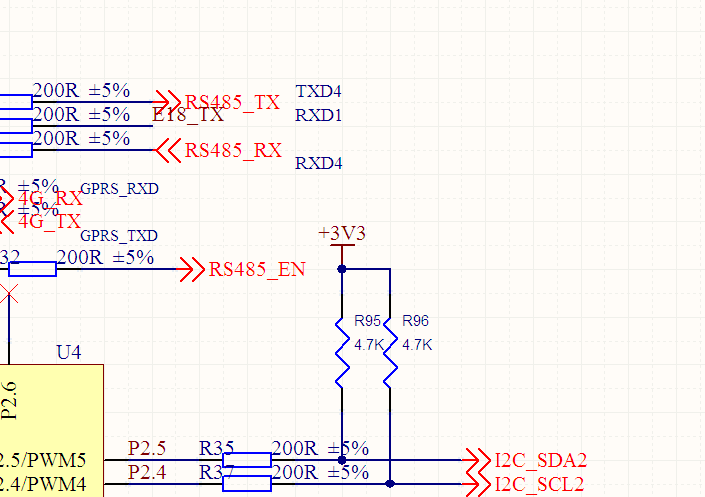

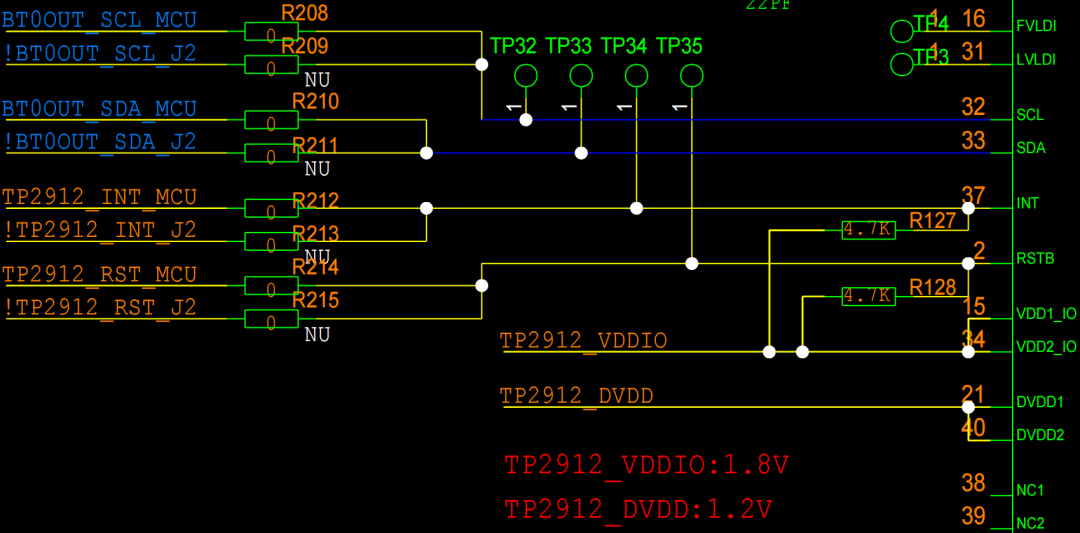

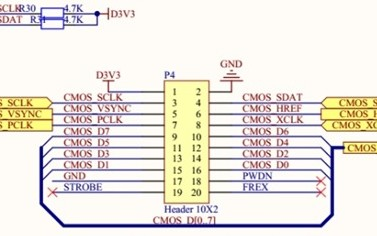

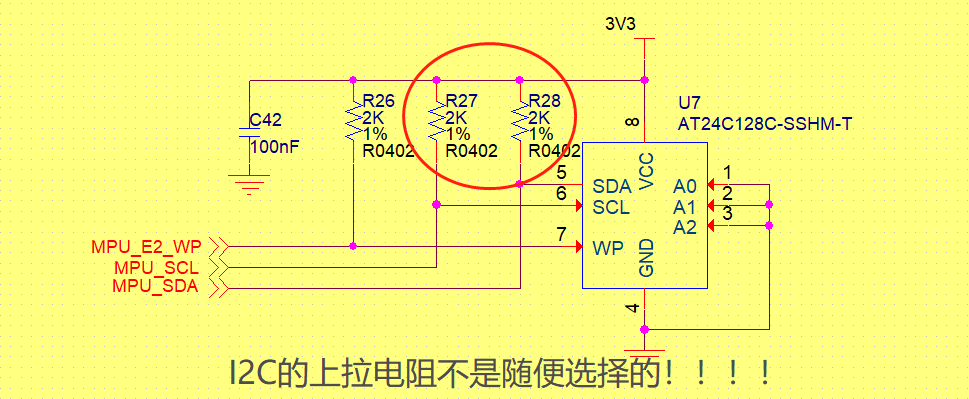

8554 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。

2022-10-08 10:53:21 1841

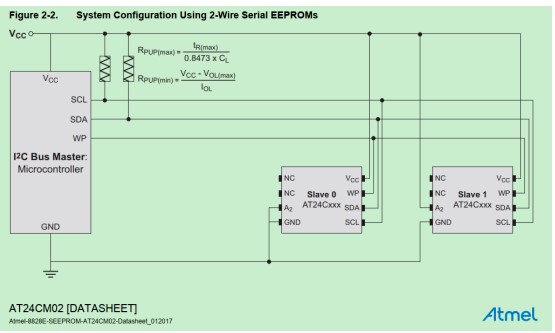

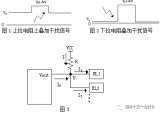

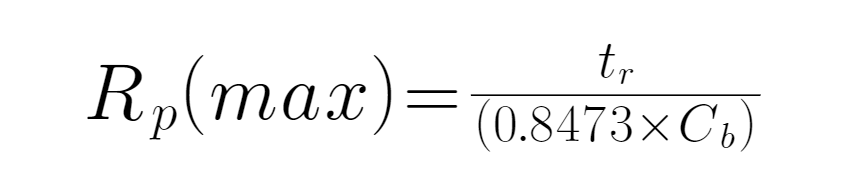

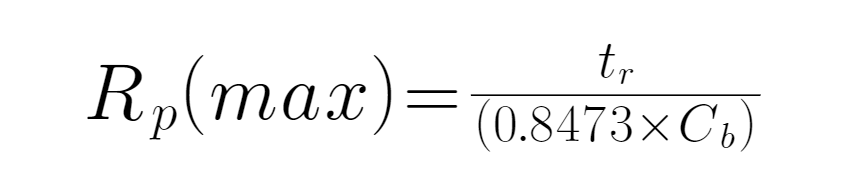

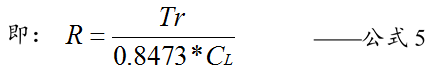

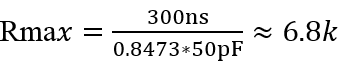

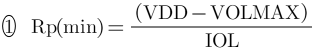

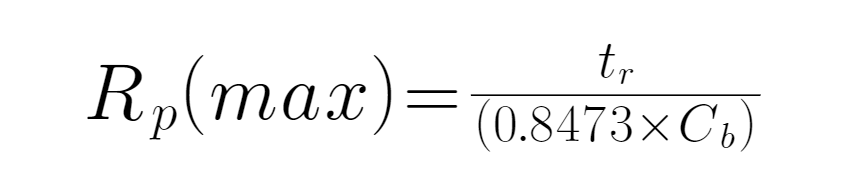

1841 上周翻了下AT24CM02芯片的數據手冊,里面提到了I2C上拉電阻的設計要點,只有兩個公式就簡潔地把上拉電阻阻值范圍確定了,非常實用,詳細見圖1。實際上,以前我從來沒有注意過I2C上拉電阻

2022-11-28 17:12:35 4015

4015

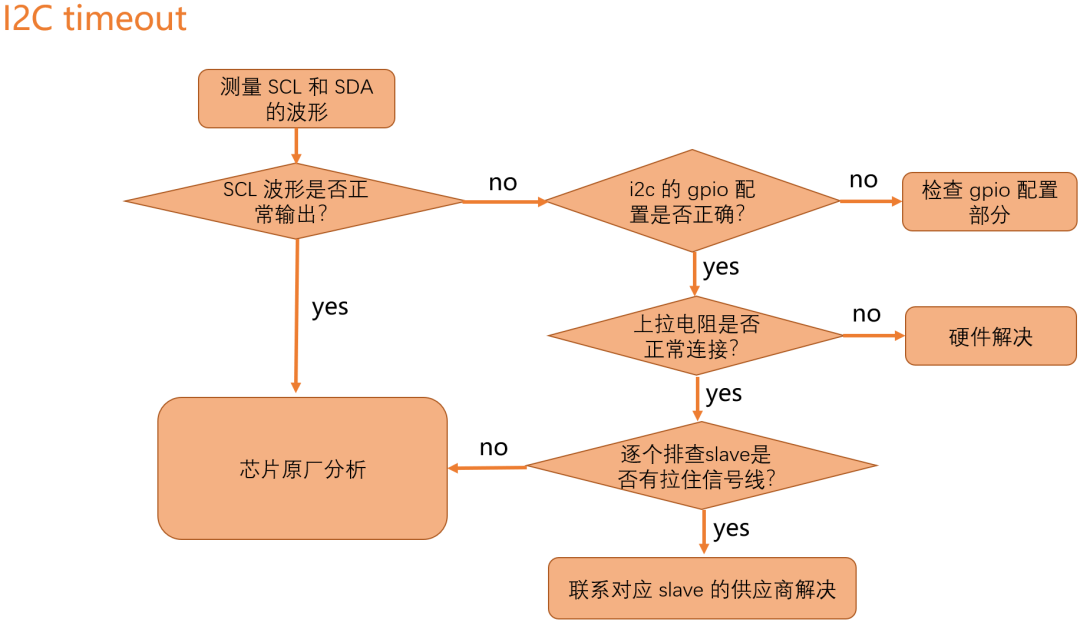

本文主要講解的是I2C開發過程中會遇到的坑以及I2C的個人總結經驗,很實用,可以i幫助開發人員更好的理解I2C調試。

2023-04-17 16:35:00 2194

2194

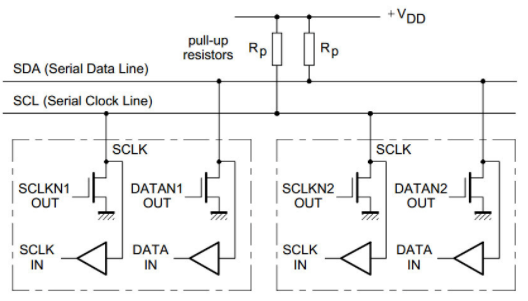

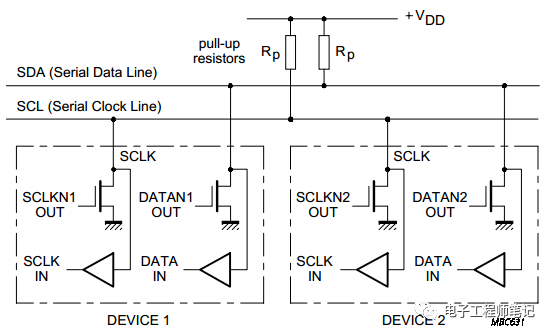

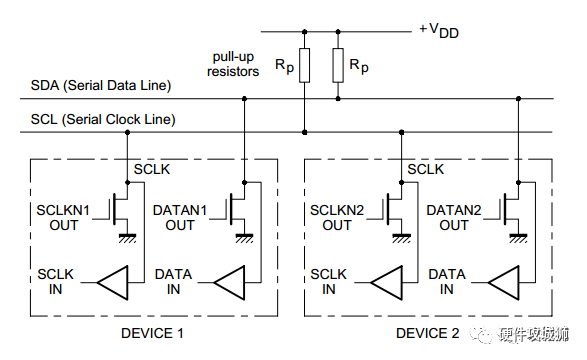

I2C 總線是一個標準的雙向接口,使用一個稱為主器件的控制器與從器件進行通信。物理I2C接口由串行時鐘線SCL和串行數據線SDA組成。SDA和SCL線都必須通過上拉電阻器連接到VCC。上拉電阻

2023-06-02 10:17:25 2414

2414

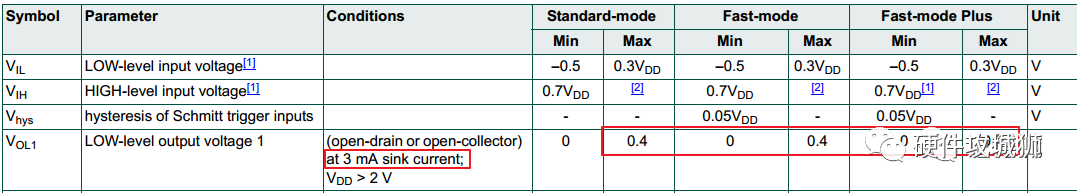

。當開路漏極接口未將線路驅動為低電平時,上拉電阻器將線路拉高。上拉電阻器的值是I2C系統的重要設計考慮因素,因為不正確的值會導致信號丟失。在本文中,展示了用于上拉電阻計算的簡單方程,系統設計者可以使用這些方程為其設計進行快速計算。

2023-06-02 10:17:57 2336

2336

I2C為什么要接上拉電阻?因為它是開漏輸出。

2023-07-08 16:14:32 3418

3418

I2C總線上拉電阻的選擇以及作用,以及計算方法。

2023-07-14 12:49:21 6371

6371

引言:I2C作為使用最為廣泛的通訊接口,調試各類I2C器件,大家應該都很輕車熟路。一般對于外掛電阻配置器件的I2C地址,例如電阻上拉之后,器件的地址就會固定下來不再變動,但是今天給大家分享一個自己的調試案例,即I2C地址跳變問題。

2023-11-22 10:51:33 3444

3444

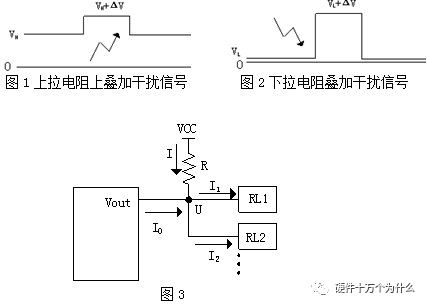

導讀I2C總線在產品設計中被廣泛應用,盡管其結構簡單,但經常發生上拉電阻設計不合理的問題。本文將對I2C上拉電阻的選擇進行簡要分析。一根信號線上,通過電阻連接一個固定的高電平VCC,信號線初始、空閑

2024-12-27 11:34:09 2595

2595

I2C信號一般需要外接上拉電阻,如果主控內部有上拉電阻,是否可以省略外部上拉?這個是否需要上拉根據什么來決定?是根據從器件的輸入電流來決定的嗎?芯片的輸入電流參數(Ii 即input current)怎么理解,設計電路時針對這個參數需要注意什么?

2018-06-07 10:01:00

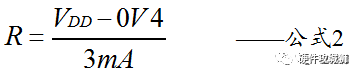

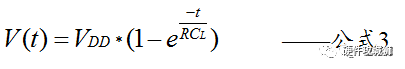

上周翻了下AT24CM02芯片的數據手冊,里面提到了I2C上拉電阻的設計要點,只有兩個公式就簡潔地把上拉電阻阻值范圍確定了,非常實用,詳細見圖1。實際上,以前我從來沒有注意過I2C上拉電阻設計,總是

2022-11-29 08:00:00

非常重要。

上拉電阻: I2C 需要使用連接到 SDA 和 SCL 線的上拉電阻。這些電阻器維持總線上默認的高邏輯電平。選擇適當的電阻值對于確保可靠的信號電平和正確的總線操作至關重要。電阻值不足或過高都會

2025-11-27 06:10:50

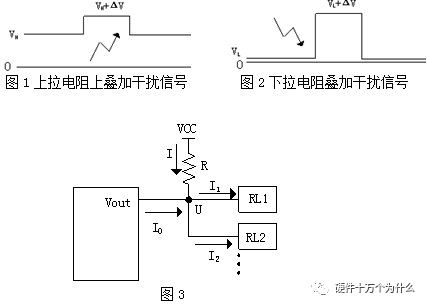

要注意上拉電阻的阻值太大的時候,容易產生干擾,尤其是線路板的線條很長的時候,這種干擾更嚴重,這種情況下上拉電阻不宜過大,一般要小于100K,有時候甚至小于10K。 5、關于I2C的上拉電阻:因為I2C

2018-10-19 16:30:19

開發板I2C連接到RTC(RX8010)芯片,I2C總線上沒有接上拉電阻,LS1012A手冊上說它的I2C是open drain輸出的,為什么沒有上拉電阻? 哪位能幫助解釋一下,謝謝

2022-01-05 06:28:48

波干擾。 8、在數字電路中不用的輸入腳都要接固定電平,通過1k電阻接高電平或接地。 四、上拉電阻阻值選擇原則 1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。 2、從確保足夠

2020-12-14 17:21:30

AVR微控制器的I/O口是雙向口。具有如下的特點:AVR IO具備多種IO模式:1 高阻態,多用于高阻模擬信號輸入,例如ADC數模轉換器輸入,模擬比較器輸入2 弱上拉狀態(Rup=20K~50K

2011-11-15 14:10:42

LTC4311 I2C邏輯緩沖器的典型低壓應用電路。利用LTC4311低壓I2C / SMBus加速器,利用低功耗總線加速器提高I2C或SMBU數據速率并降低功耗,LTC4311的強上拉電流允許用戶選擇更大的總線上拉電阻值以降低VOL

2019-06-05 09:06:39

上拉下拉電阻的定義以及用法為什么要使用拉電阻上拉電阻阻值的選擇原則

2021-04-06 06:06:42

I2C分為哪幾種模式?I2C的上拉電阻取值是什么?上拉電阻的上限如何確定呢?關于I2C有什么問題嗎?那么一般如何解決呢?

2021-06-27 06:59:35

拉下拉。電阻在電路上拉或者下拉,常見于單片機的IO端口,以及MOS的驅動輸出或者I2C這樣的信號上,有人選擇1K,有人選擇10K,有人選擇100K,那么我們在電路設計中,到底選擇多大的電阻比較合適呢

2022-01-14 07:17:24

過低的頻率導致通信錯誤。

上拉電阻的選擇與配置:探討I2C總線上拉電阻的作用,如何根據線纜長度、負載電容等實際情況,選擇合適的上拉電阻,增強通信信號的完整性。

信號完整性與抗干擾設計:分析可能

2025-12-03 07:29:35

I2C上拉電阻 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。 I2C接口 對于

2022-01-14 07:22:21

1:僅僅一根線路就可能發生短路(左),一個上拉電阻就可以防止輸入管腳懸空,同時防止不必要短路現象的發生那么我們怎樣選擇合適的電阻呢?正如大多數工程的問題一樣,答案取決于你的應用。首先我們以極端條件0

2018-11-30 09:12:02

。圖1:剛剛運行導線可以實現短路(左)。上拉電阻可防止浮動輸入,同時防止不必要的短路(右)。(來源:作者)那么我們如何選擇合適尺寸的電阻呢?與大多數優秀的工程問題一樣,答案取決于您的應用。讓我們首先

2018-11-09 09:14:56

使用的從器件。要獲得正確的上拉電阻值,請參考器件數據表。多個從器件可以共用一條I2C總線,單個上拉電阻器 I2C軟件協議 不論何種應用,每個支持I2C器件都需要遵守針對全部I2C器件所定義的共同

2020-12-14 14:17:25

確定上拉電阻值時需要考慮哪些注意事項?穩定可靠的I2C通信的設計計算公式

2021-05-25 06:35:11

。但是,I2C總線拓撲要依賴于阻值合適的上拉電阻才能實現穩定可靠的通信。電阻值選擇錯誤不僅會造成電能浪費,還可能導致總線狀態和傳輸過程由于噪聲、溫度變化、工作電壓變化以及器件間的制造差異而出

2012-12-17 11:52:52

對于I2C總線,拉出電阻值是多少?

2020-12-15 06:24:49

stm32f051的i2c需要外接上拉電阻嗎,直接用內部上拉行不行,還有庫中的I2C_Init函數中有這么一句/* Enable I2Cx Peripheral */I2Cx->CR1 |= I2C_CR1_PE;為什么初始化有些i2c寄存器需要使能i2c。最后附上波形,希望哪位大哥幫幫忙,看看是什么問題。

2019-03-12 07:14:31

請問為什么有時在I2C中將SDA和SCL 上加各加個上拉電阻呢?

2023-05-08 18:01:37

請問用TMS320C5515的GPIO口模擬I2C總線需要接外部上拉電阻嗎?需要的話阻值為多少比較合適呢?

2019-10-28 09:37:43

I2C總線應用中的幾個問題:i2c上拉電阻阻值的確定,PCB布局布線與抗干擾設計,軟件模擬I2C時序,I2C 應用中上拉電阻電源問題。

2009-09-13 14:27:55 51

51 I2C Guid I2C指南

The I2C bus is used in a wide rangeof applications because it is simpleand

2010-04-23 13:55:40 36

36 AVR管腳外部上拉電阻阻值選擇分析

AVR微控制器的I/O口是雙向口。具有如下的特點:

AVR IO具備多種IO模式:

2008-10-26 10:48:44 1833

1833 I2C 的上拉電阻可以是1.5K,2.2K,4.7K, 電阻的大小對時序有一定影響,對信號的上升時間和下降時間也有影響,一般接1.5K 或2.2K.

2012-03-21 15:05:07 116

116 I2C總線在單片機和其他芯片組中具有廣泛的硬件支持,并且信號傳遞方式簡單,可采用極小的硅片有效實現,但是,I2C總線拓撲要依賴于阻值合適的上拉電阻才能實現穩定可靠的通信。

2012-11-15 14:37:29 2958

2958 I2C應用中的幾個問題,I2C上拉電阻的確定,抗干擾設計

2016-02-25 14:48:37 4

4 單片機i2c總線操作;單片機i2c總線操作;單片機i2c總線操作;

2016-05-17 11:09:40 35

35 上拉電阻和下拉電阻的作用及選擇

2016-12-15 18:39:07 27

27 從TI的tpa2051d3音頻子系統采用I2C總線集成電路之間的通信一個系統。本文檔說明如何選擇合適的I2C接口電阻值連接到tpa2051d3。 概述 TPA2051d3采用I2C總線之間的通信集

2017-05-23 16:13:20 8

8 I2C(Inter-Intergrated Circuit)總線是微電子通信控制領域中常用的一種總線標準,具有接線少,控制方式簡單,通信速率高等優點。

2017-11-06 17:34:22 77909

77909

I2C總線在物理連接上非常簡單,分別由SDA(串行數據線)和SCL(串行時鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時序的控制,來產生I2C總線協議所需要的信號進行數據的傳遞。在總線空閑狀態時,這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2017-12-06 10:48:01 4058

4058

開發板,即可接收STM32串口發送給電腦的調試信息。 【*】 引腳分配 EEPROM(AT24C02): EEPROM芯片的I2C接口與STM32的I2C1相連,且已接上拉電阻。 SCL 《

2017-12-13 15:12:33 23

23 手機原理設計中,上拉電阻常用在中斷,GPIO控制,I2C等信號上,本文希望能通過實例分析加深對上拉電阻的理解。

2017-12-21 17:03:44 5968

5968

上拉電阻的作用及阻值的選擇原則

2018-03-21 11:17:55 2

2 對于驅動TTL集成電路,上拉電阻的阻值要用1~10K之間的,有時候電阻太大的話是拉不起來的,因此用的阻值較小。但是對于CMOS集成電路,上拉電阻的阻值就可以用的很大,一般不小于20K,通常用100K

2018-05-26 09:16:09 25913

25913

本文首先介紹了上拉電阻阻值的選擇原則,其次介紹了上拉電阻阻值計算原則。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2018-08-30 18:37:13 21819

21819 LPC2124有一個標準的I2C總線接口,可配置為主機或從機,總線時鐘速率可調整,最高可支持400KHZ總線速率。使用I2C總線時,要將相應得引腳設置連接SCL和SDA,并且總線上要上拉電阻,阻值為

2019-02-11 10:00:00 2274

2274 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。

2019-10-03 16:57:00 24293

24293

I2C 總線在物理連接上非常簡單,分別由SDA(串行數據線)和SCL(串行時鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時序的控制,來 產生I2C總線協議所需要的信號進行數據的傳遞。在總線空閑狀態時,這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2020-09-24 14:12:09 7088

7088

I2C的上拉電阻可以是1.5K,2.2K,4.7K, 電阻的大小對時序有一定影響,對信號的上升時間和下降時間也有影響,一般接1.5K或2.2K。

2020-11-24 14:27:02 28314

28314 I2C總線物理拓撲結構

I2C 總線在物理連接上非常簡單,分別由SDA(串行數據線)和SCL(串行時鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時序的控制,來 產生I2C

2022-02-09 14:08:17 2837

2837

I2C為什么要接上拉電阻?因為它是開漏輸出。 1 為什么是開漏輸出? I2C協議支持多個主設備與多個從設備在一條總線上,如果不用開漏輸出,而用推挽輸出,會出現主設備之間短路的情況。 所以總線一般會使

2021-06-21 10:30:02 16500

16500 I2C為什么要接上拉電阻?因為它是開漏輸出!

2021-06-21 16:34:33 13557

13557

硬件I2C對應芯片上的I2C外設,有相應I2C驅動電路,其所使用的I2C管腳也是專用的,因而效率要遠高于軟件模擬的I2C;一般也較為穩定,但是程序較為繁瑣。硬件(固件)I2C是直接調用內部寄存器進行

2021-12-28 19:14:11 81

81 拉下拉。電阻在電路上拉或者下拉,常見于單片機的IO端口,以及MOS的驅動輸出或者I2C這樣的信號上,有人選擇1K,有人選擇10K,有人選擇100K,那么我們在電路設計中,到底選擇多大的電阻比較合適呢

2022-01-14 14:09:36 4

4 I2C上拉電阻 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。 I2C接口 對于

2022-01-14 14:10:36 10

10 把一個信號通過一個電阻接到高電平,叫作上拉,這個電阻充當的作用就是上拉電阻。

2022-03-29 14:16:51 4

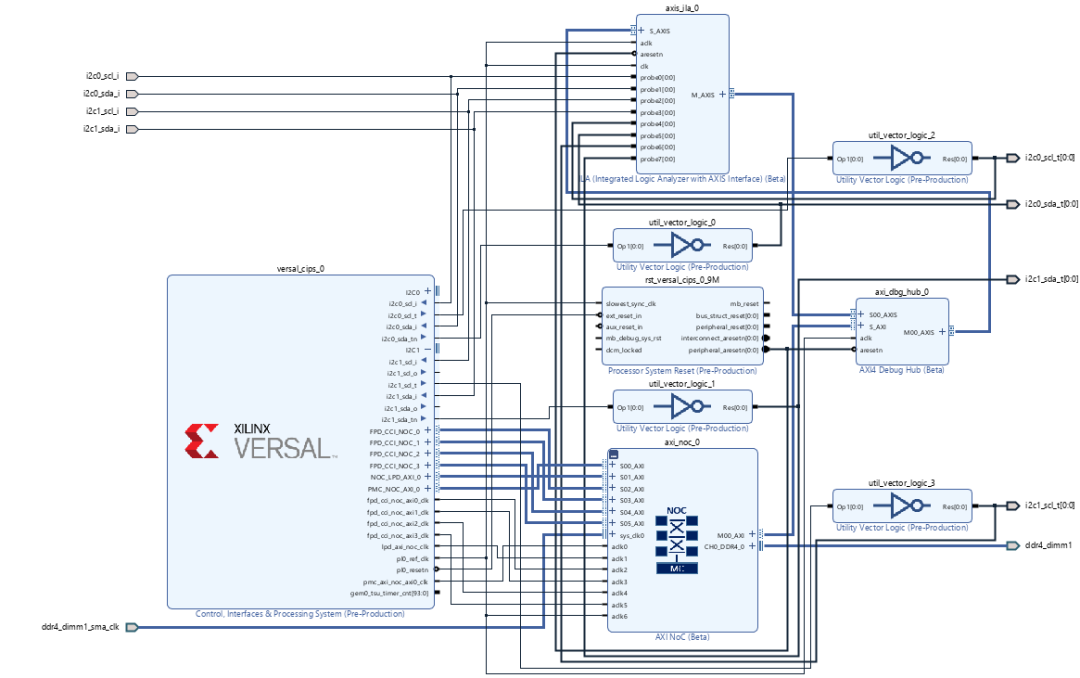

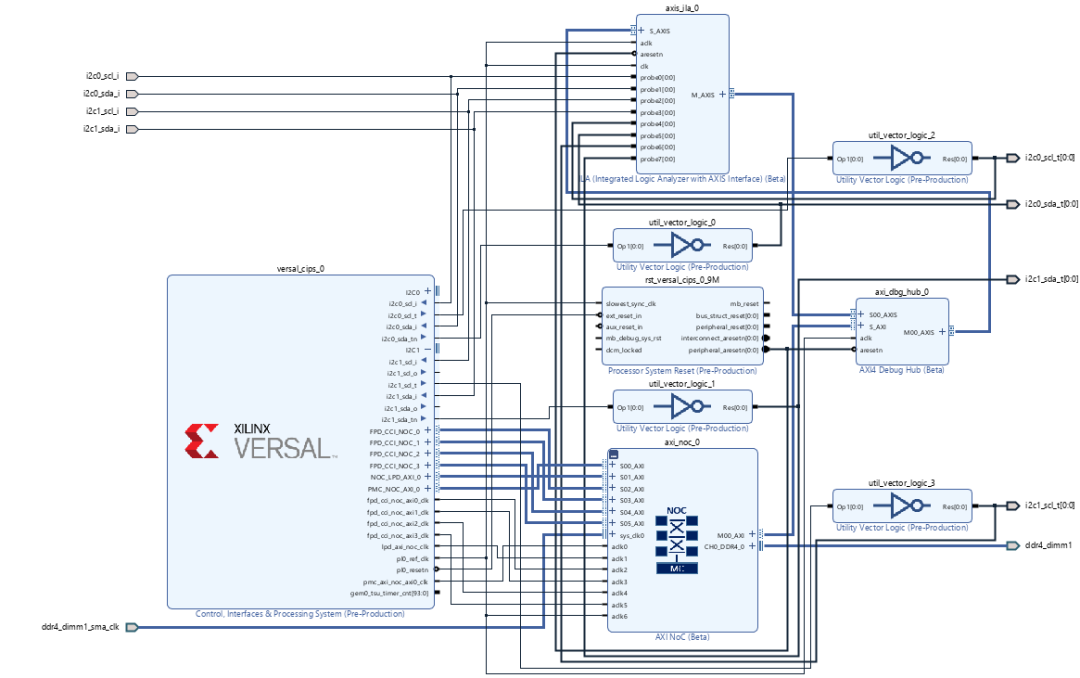

4 I2C 總線的兩根信號線 SCL 和 SDA 需要上拉才能正常工作,當板卡上沒有合適的硬件設置或者沒有合適的 I2Cslave 設備,我們就無法進行 I2C 軟件測試。那么是否可以將兩個 PSI2C 控制器通過 EMIO 接口互連起來呢?

2022-04-13 08:35:00 2961

2961 SDA和SCL需要外接上拉電阻,根據總線上的I2C設備數量,系統的通信速度,設計選擇不同的上拉電阻。I2C設備數量決定了總線上母線電容的大小,母線電容和上拉電阻限制了系統的通信速率。

2022-06-29 11:28:56 7845

7845

I2C 總線的兩根信號線 SCL 和 SDA 需要上拉才能正常工作,當板卡上沒有合適的硬件設置或者沒有合適的 I2Cslave 設備,我們就無法進行 I2C 軟件測試。那么是否可以將兩個 PSI2C 控制器通過 EMIO 接口互連起來呢?

2022-08-02 09:23:23 927

927

I2C一般為開漏結構,需要在外部加上拉電阻,常見的阻值有1k、1.5k、2.2k、4.7k、5.1k、10k等。

2022-09-02 09:49:29 5149

5149 I2C總線為什么要接上拉電阻 1、根據I2C總線規范,總線空閑時兩根線都必須為高; 這是規定,動不了的,不然什么叫標準呢?其實所謂的這個神圣的標準也并不是多么邪乎,你想啊,只有是高的才能拉成低

2022-10-25 20:36:14 1604

1604 I2C總線為什么要接上拉電阻 1、根據I2C總線規范,總線空閑時兩根線都必須為高; 這是規定,動不了的,不然什么叫標準呢?其實所謂的這個神圣的標準也并不是多么邪乎,你想啊,只有是高的才能拉成低

2022-11-09 13:21:04 4203

4203 我們知道,在I2C的電路中,在SCL、SDA線與電源之間通常會接一個電阻,這個電阻稱之為上拉電阻。

2022-11-24 09:19:55 10562

10562 I2C總線為什么要接上拉電阻 1、根據I2C總線規范,總線空閑時兩根線都必須為高; 這是規定,動不了的,不然什么叫標準呢?其實所謂的這個神圣的標準也并不是多么邪乎,你想啊,只有是高的才能拉成低

2022-12-13 16:30:04 4286

4286 電子發燒友網站提供《I2C掃描儀之如何在Arduino上查找I2C地址.zip》資料免費下載

2023-01-31 10:19:31 2

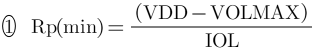

2 如果上拉阻值過小,VDD灌入端口的電流將較大,功耗會很大,導致端口輸出的低電平值增大(I2C協議規定,端口輸出低電平的最高允許值為0.4V)。

2023-02-06 10:53:18 2407

2407 I2C 總線在物理連接上非常簡單,分別由SDA(串行數據線)和SCL(串行時鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時序的控制,來 產生I2C總線協議所需要的信號進行數據的傳遞。在總線空閑狀態時,這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2023-02-11 09:54:39 773

773 I2C 總線在物理連接上非常簡單,分別由SDA(串行數據線)和SCL(串行時鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時序的控制,來 產生I2C總線協議所需要的信號進行數據的傳遞。在總線空閑狀態時,這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2023-02-13 10:14:21 2183

2183

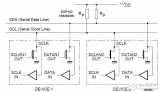

I2C協議支持多個主設備與多個從設備在一條總線上,如果不用開漏輸出,而用推挽輸出,會出現主設備之間短路的情況。所以總線一般會使用開漏輸出。

2023-02-24 09:18:48 2640

2640 上拉就是將不確定的信號通過一個電阻嵌位在高電平!電阻同時起限流作用!下拉同理

2、上拉是對器件注入電流,下拉是輸出電流

3、弱強只是上拉電阻的阻值不同,沒有什么嚴格區分

4、對于非集電極

2023-03-17 15:57:32 3947

3947

I2C總線是微電子通信控制領域中常用的一種總線標準,具備接線少,控制簡單,速率高等優點。在I2C電路中常見的上拉電阻有1k、1.5k、2.2k、4.7k、5.1k、10k等等,但是應該如何根據開發要求選擇合適的阻值呢?下圖為I2C內部結構

2023-05-10 16:17:05 9281

9281

信息和接收信息無法同時進行,I2C工作時的傳輸速率在標準模式下可達100kbit/s,快速模式下可達400kbit/s,高速模式下可達3.4Mbit/s。I2C總線采用漏極開路的設計,且SDA和SCL通過上拉電阻連接V~CC~。今天就和大家來探討一下I2C為什么需要用開漏輸出和上拉電阻。

2023-07-02 16:39:21 7469

7469

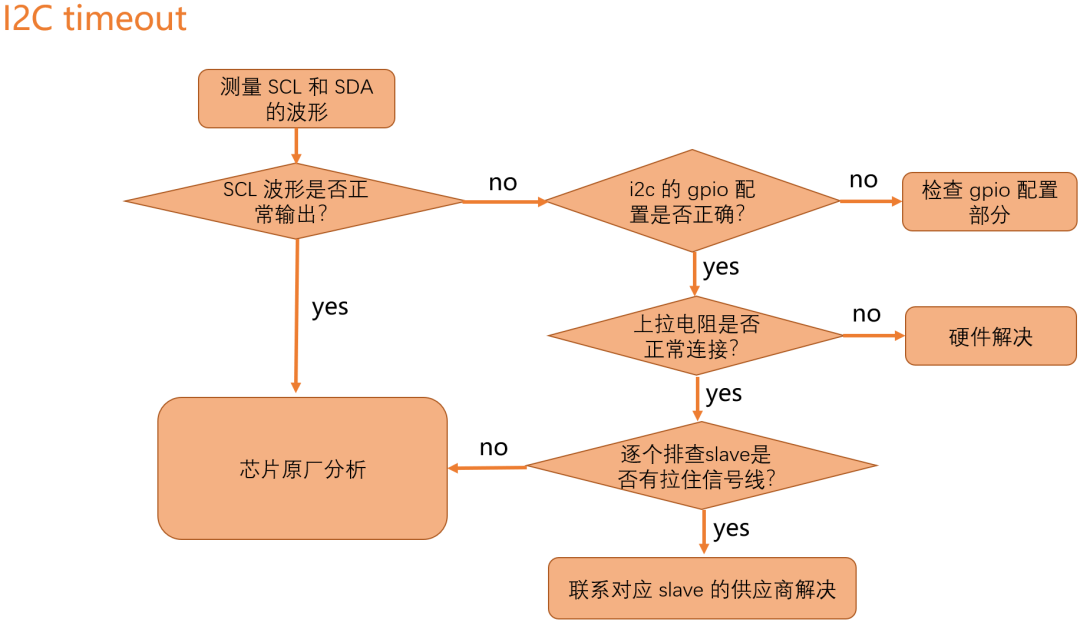

,transfer timeout 1、GPIO check 以下幾個部分 GPIO 電流驅動能力 GPIO 工作模式是否是 I2C 模式 GPIO 是否有內部上拉電阻 GPIO 默認電平狀態 2、排查 slave

2023-07-22 14:46:40 4238

4238

RK 平臺 I2C debug 1、I2C 通信失敗,出現 log: “timeout, ipd: 0x00, state: 1” 請檢查硬件上拉是否給電。 2、調用 i2c

2023-07-22 15:00:27 5997

5997 上拉電阻和等效電容決定(RC)。 I2C 是一種多主從架構總線 I2C 的讀寫均由 master 端發起。

2023-07-25 09:41:01 6084

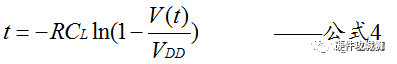

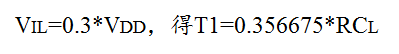

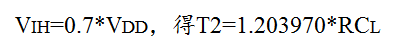

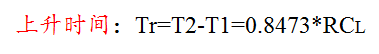

6084 上拉電阻計算 1、上拉電阻過小,電流大,端口低電平 level 增大。 2、上拉電阻過大,上升沿時間增大,方波可能會變成三角波。 因此計算出一個精確的上拉電阻阻值是非常重要的。計算上拉電阻的阻值,有

2023-07-25 10:03:23 2809

2809

相信很多人都清楚,在I2C總線上需要接上拉電阻?但是您針對對I2C上拉電阻足夠了解嗎?本文帶您詳細掌握一下I2C的上拉電阻。

2023-07-25 10:37:59 4272

4272

上拉電阻計算 1、上拉電阻過小,總線上電流增大,端口輸出低電平增大。 2、上拉電阻過大,上升沿時間增大,方波可能會變成三角波。 因此計算出一個精確的上拉電阻阻值是非常重要的。 計算上拉電阻的阻值

2023-09-28 14:29:36 4300

4300

上拉電阻主要用于為信號線或GPIO引腳提供默認狀態。通常選擇幾K或幾十K阻值的電阻。阻值較大的電阻確保不會通過電阻不斷地將過多的電流引入到信號線上(5V Vdd / 10KΩ = 0.5mA 電流)。在常見的MCU中有大約幾十K的電阻可以通過代碼啟用的上拉電阻將 GPIO 引腳預設為邏輯高電平狀態。

2023-10-12 09:19:38 9369

9369

本篇說明了在內置上拉電阻、下拉電阻的IC中,如果沒有規定上拉電阻、下拉電阻的電阻值時的計算方法。

2023-10-18 09:27:45 4957

4957 I2C總線上的上拉電阻范圍是多少?

回答: 總線電容是走線部分、連接部分、管腳部分的電容的總和。總線電容限制了上拉電阻(Rp) 的最大值,因為I2C規定了上升時間(SDA和SCL信號的上升時間)。

2023-12-25 09:19:03 2928

2928 上拉電阻有助于降低系統的總功耗,同時保持電路的功能性和穩定性。那么上拉電阻如何實現低功耗設計呢? 以下是上拉電阻實現低功耗設計的幾種方法: 選擇合適的上拉電阻值: 功耗與電阻值成反比關系,一個較大

2024-05-02 15:00:00 2180

2180 每個設備都可以將線拉低(Ground),但不能將線拉高(Vcc)。這種設計使得多個設備可以共享同一條總線,以進行通信。二、I2C接口接外部上拉電阻的原因I2C(I

2024-05-16 08:10:40 10901

10901

。這通常基于電路的功能、性能要求和元件之間的匹配關系。 阻值公差:考慮電阻的標稱阻值和實際阻值之間可能存在的誤差。誤差范圍通常用百分比表示,如1%、5%等。根據電路對精度的要求,選擇合適的阻值公差。 2. 考慮電路特性 高頻電

2024-08-30 14:59:18 1113

1113 數據線加上拉電阻。這一設計不僅關乎技術的實現,更涉及系統安全和信號傳輸效率的優化。本文將深入探討在I2C總線上加上拉電阻的必要性及其帶來的技術優勢。 我們需要理解I2C總線的基本架構。I2C總線是一種多主多從的通信網絡,允許多個設備通過

2024-09-09 17:16:33 2532

2532 ,但在對性能有更高要求或特定條件下,則需要通過更為精確的計算來確定電阻值。本文將詳細介紹如何計算上拉電阻的值。 首先,我們需要理解上拉電阻在I2C總線中的基本作用。在I2C的開漏輸出設計中,上拉電阻負責在無設備驅動總線時,將SC

2024-09-09 17:20:30 1541

1541 電子發燒友網站提供《I2C總線上拉電阻計算.pdf》資料免費下載

2024-10-08 09:54:21 1

1 本文從I2C協議的概述開始,描述協議的歷史、不同速度模式、物理層和數據幀結構,最后介紹I2C混合電壓系統中電平兼容性以及上拉電阻大小計算。

2024-10-22 15:51:28 4365

4365

I2C為什么要接上拉電阻?因為它是開漏輸出。 為什么是開漏輸出? I2C協議支持多個主設備與多個從設備在一條總線上,如果不用開漏輸出,而用推挽輸出,會出現主設備之間短路的情況。所以總線一般會使用開漏

2024-11-20 10:07:42 1905

1905

I2C總線是一種廣泛使用的串行通信協議,它允許多個設備通過兩條線(數據線SDA和時鐘線SCL)進行通信。為了確保數據信號的穩定性和減少反射,I2C總線的數據線SDA和時鐘線SCL都需要適當的上拉電阻

2025-01-17 15:43:19 1348

1348 在電子電路設計中,上拉電阻是一種常用的元件,它的阻值選擇至關重要,需要綜合考慮多個因素來確定合適的阻值。 一、功耗因素 功耗是選擇上拉電阻阻值時需要考慮的一個重要方面。當電阻兩端有電壓時,就會產生

2025-02-05 17:25:00 1424

1424

電子發燒友App

電子發燒友App

評論