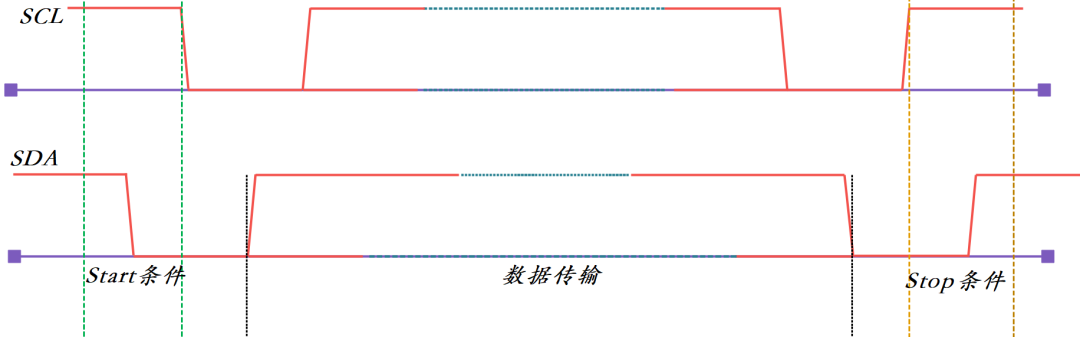

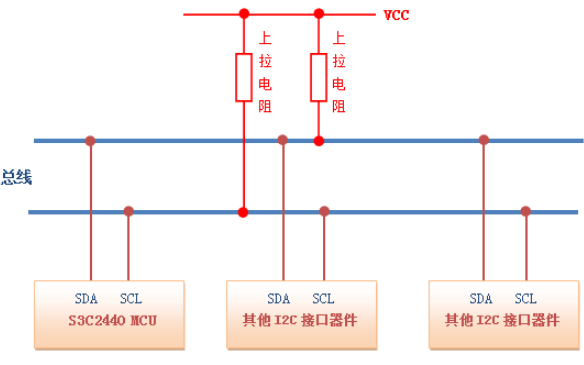

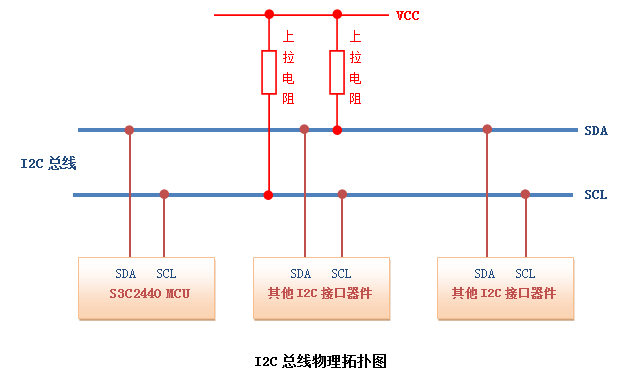

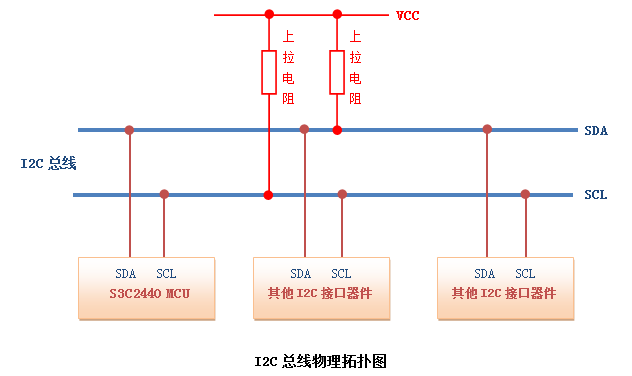

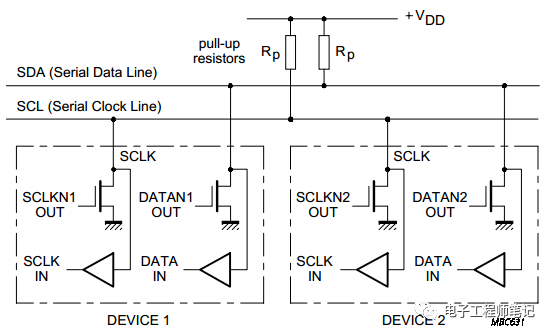

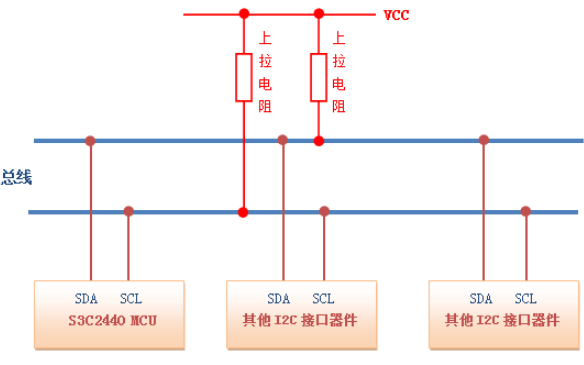

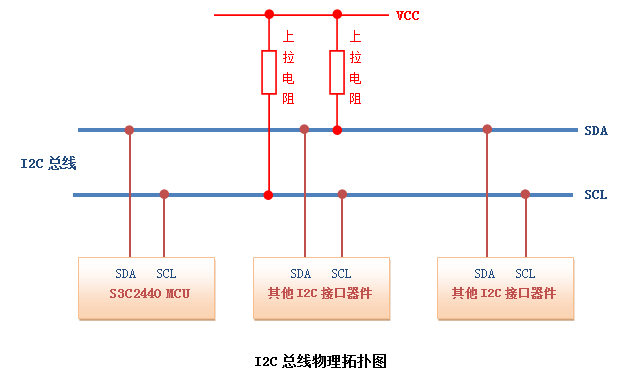

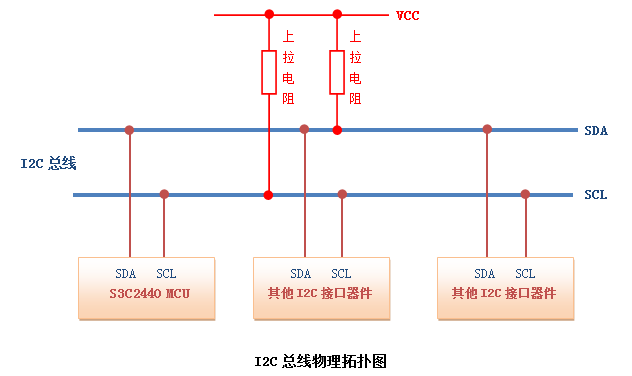

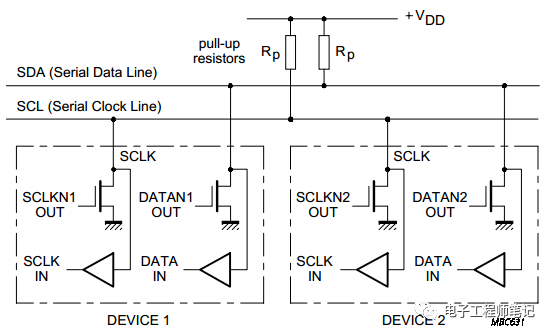

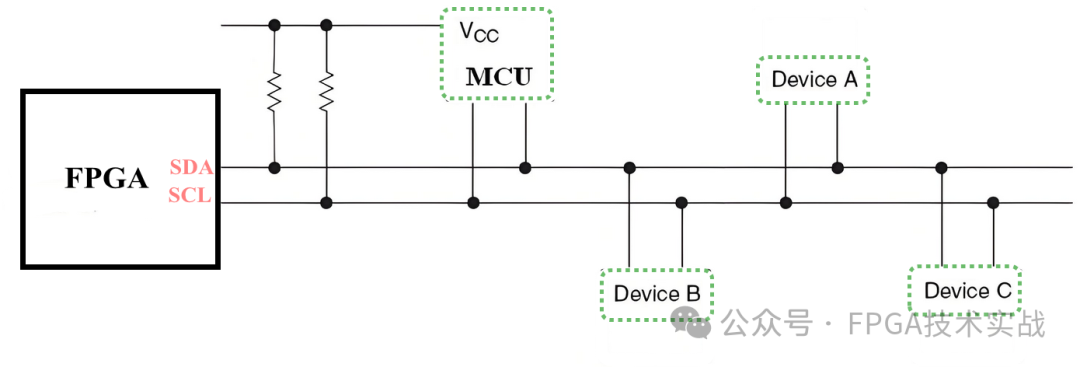

I2C 總線在物理連接上非常簡單,分別由SDA(串行數(shù)據(jù)線)和SCL(串行時(shí)鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時(shí)序的控制,來 產(chǎn)生I2C總線協(xié)議所需要的信號進(jìn)行數(shù)據(jù)的傳遞。在總線空閑狀態(tài)時(shí),這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2022-08-04 08:51:58 1092

1092 我們知道,在I2C的電路中,在SCL、SDA線與電源之間通常會接一個(gè)電阻,這個(gè)電阻稱之為上拉電阻。 但什么是上拉電阻? 上拉電阻主要用于為信號線或GPIO引腳提供默認(rèn)狀態(tài)。

2022-09-08 14:43:24 8554

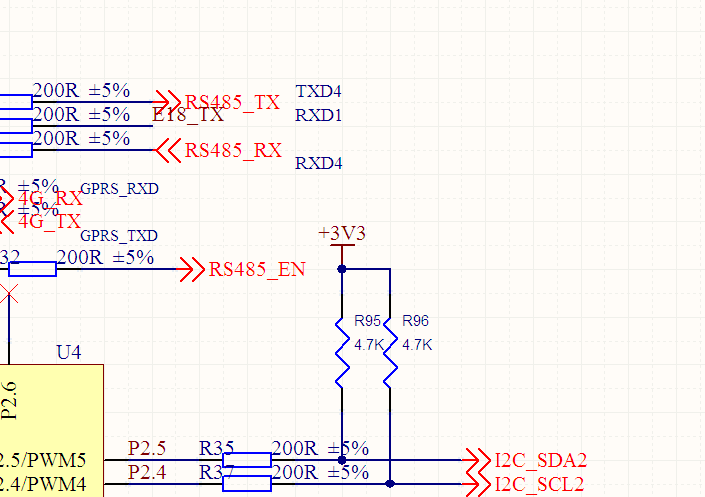

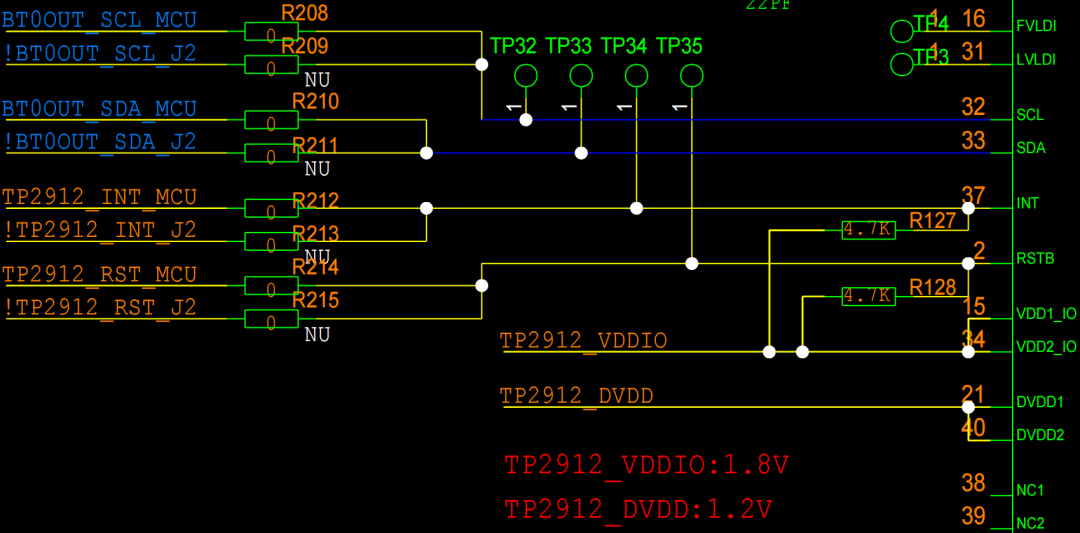

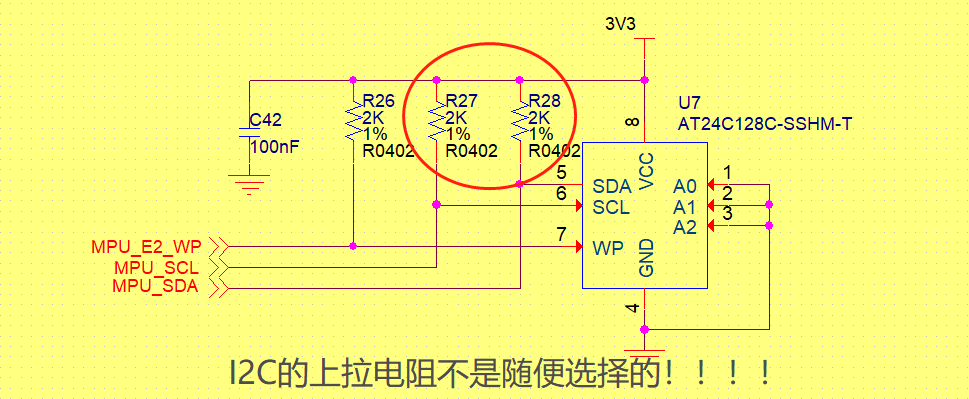

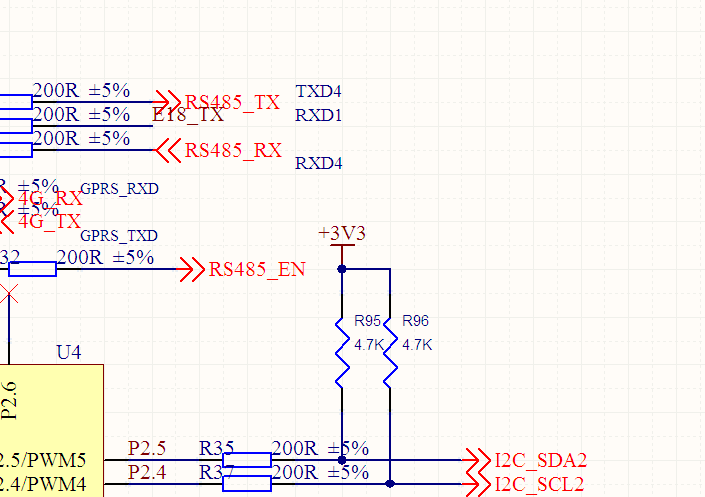

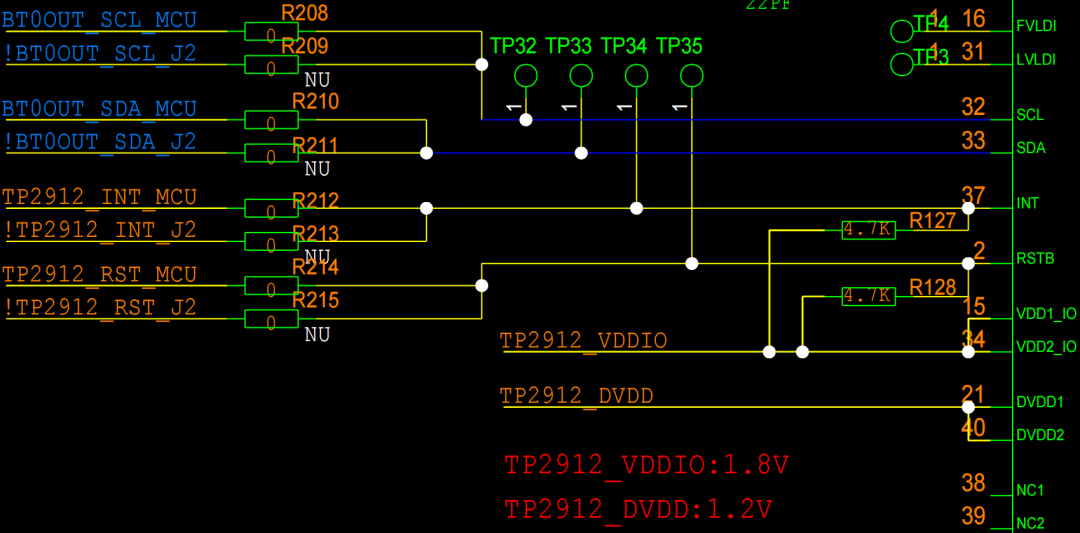

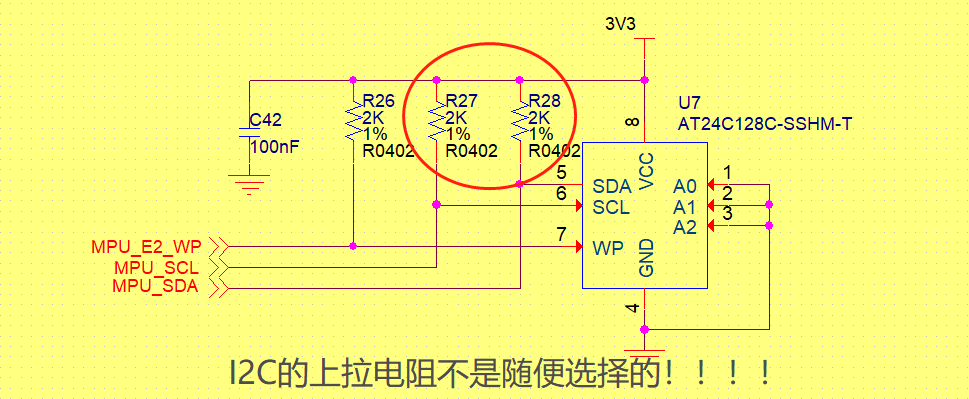

8554 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個(gè)4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。

2022-10-08 10:53:21 1841

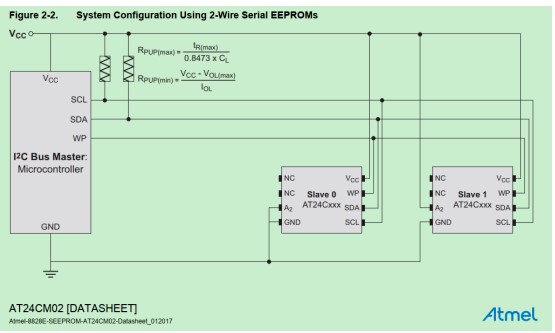

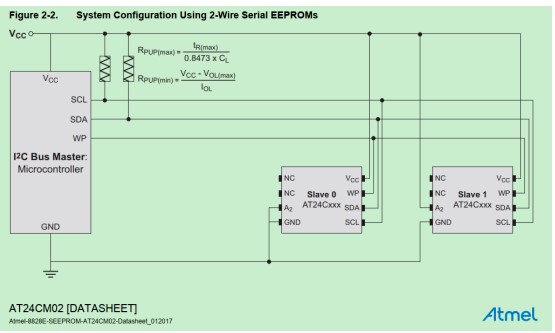

1841 上周翻了下AT24CM02芯片的數(shù)據(jù)手冊,里面提到了I2C上拉電阻的設(shè)計(jì)要點(diǎn),只有兩個(gè)公式就簡潔地把上拉電阻阻值范圍確定了,非常實(shí)用,詳細(xì)見圖1。實(shí)際上,以前我從來沒有注意過I2C上拉電阻

2022-11-28 17:12:35 4015

4015

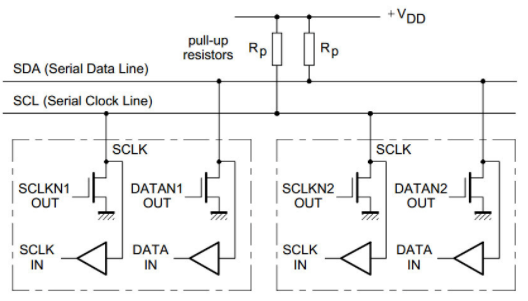

I2C 總線是一個(gè)標(biāo)準(zhǔn)的雙向接口,使用一個(gè)稱為主器件的控制器與從器件進(jìn)行通信。物理I2C接口由串行時(shí)鐘線SCL和串行數(shù)據(jù)線SDA組成。SDA和SCL線都必須通過上拉電阻器連接到VCC。上拉電阻

2023-06-02 10:17:25 2417

2417

引言:I2C通信標(biāo)準(zhǔn)是當(dāng)今電子系統(tǒng)中最廣泛使用的芯片間通信標(biāo)準(zhǔn)。這是一種開放漏極/開放集電極通信標(biāo)準(zhǔn),意味著可以連接具有不同電壓供電軌的集成電路進(jìn)行通信。需要將上拉電阻器從I2C線路連接到電源

2023-06-02 10:17:57 2336

2336

I2C總線上拉電阻的選擇以及作用,以及計(jì)算方法。

2023-07-14 12:49:21 6376

6376

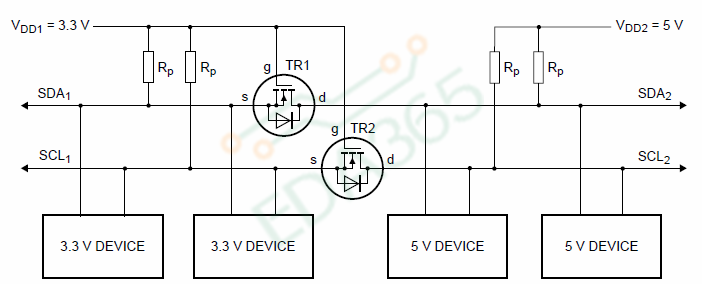

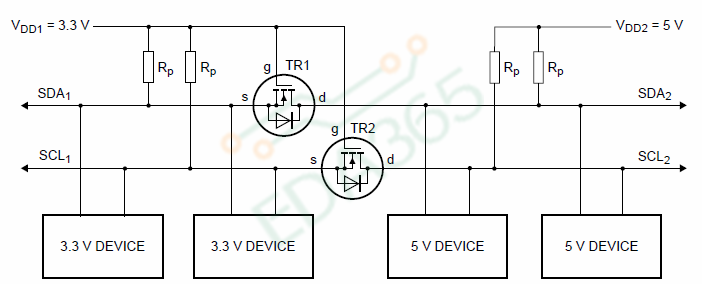

我們先來看一張圖,熟悉I2C的人一看,這不是I2C的level shifter電路嘛,在Philip的I2C標(biāo)準(zhǔn)里面有,沒有啥復(fù)雜的。

2023-11-02 12:32:20 7582

7582

引言:I2C作為使用最為廣泛的通訊接口,調(diào)試各類I2C器件,大家應(yīng)該都很輕車熟路。一般對于外掛電阻配置器件的I2C地址,例如電阻上拉之后,器件的地址就會固定下來不再變動(dòng),但是今天給大家分享一個(gè)自己的調(diào)試案例,即I2C地址跳變問題。

2023-11-22 10:51:33 3444

3444

導(dǎo)讀I2C總線在產(chǎn)品設(shè)計(jì)中被廣泛應(yīng)用,盡管其結(jié)構(gòu)簡單,但經(jīng)常發(fā)生上拉電阻設(shè)計(jì)不合理的問題。本文將對I2C上拉電阻的選擇進(jìn)行簡要分析。一根信號線上,通過電阻連接一個(gè)固定的高電平VCC,信號線初始、空閑

2024-12-27 11:34:09 2595

2595

、I2C設(shè)計(jì)數(shù)學(xué):電容和電阻了解I 2 C及其隨之而來的一些設(shè)計(jì)挑戰(zhàn),包括邏輯閾值,影響電容的因素以及最小和最大上拉電阻。本文介紹了哪些變量會影響總線的電容。它還考察了用于確定上拉電阻器尺寸并確定電路

2020-09-22 09:31:41

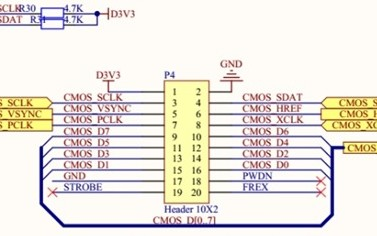

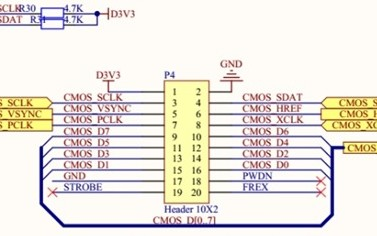

如圖,像這種IIC的電路為什么要加這些4.7kΩ、100Ω的上拉電阻?

2019-02-15 09:58:53

I2C信號一般需要外接上拉電阻,如果主控內(nèi)部有上拉電阻,是否可以省略外部上拉?這個(gè)是否需要上拉根據(jù)什么來決定?是根據(jù)從器件的輸入電流來決定的嗎?芯片的輸入電流參數(shù)(Ii 即input current)怎么理解,設(shè)計(jì)電路時(shí)針對這個(gè)參數(shù)需要注意什么?

2018-06-07 10:01:00

在設(shè)計(jì)時(shí)對產(chǎn)品進(jìn)行靜電干擾測試時(shí),出現(xiàn)I2C的CLK被異常拉低,接上位機(jī)讀取I2C狀態(tài)寄存器,發(fā)現(xiàn)寄存器值有變化,這種問題如何解?

2020-02-07 15:23:49

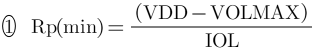

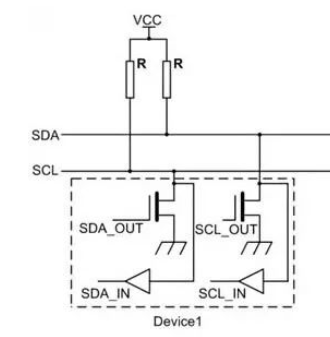

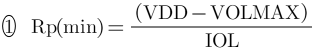

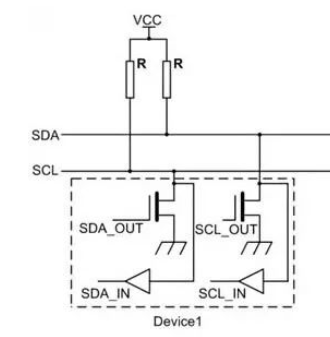

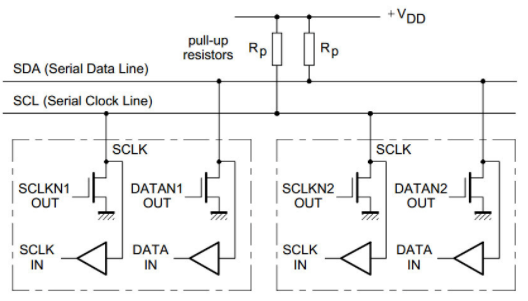

,I2C上拉電阻最小值確定為什么I2C需要上拉電阻才能通訊呢?因?yàn)镾DA和SCL是開路漏極或者開路集電極輸出,所以如果沒有上拉電阻,芯片是無法輸出高電平的,可參見圖2。圖2 I2C硬件框圖要理解I2C上拉

2022-11-29 08:00:00

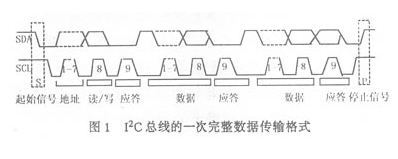

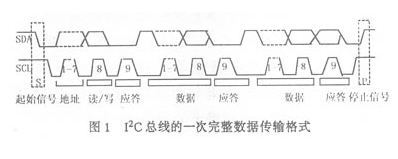

SDA,另外一根時(shí)鐘線SCL,接上拉電阻,總線空閑為高電平。只要有低電平,總線就會被拉低電平。主機(jī)通過I2C總線來傳輸數(shù)據(jù)給掛載的器件。通過總線仲裁,來判斷哪一臺主機(jī)來控制。SCL...

2022-01-18 07:36:05

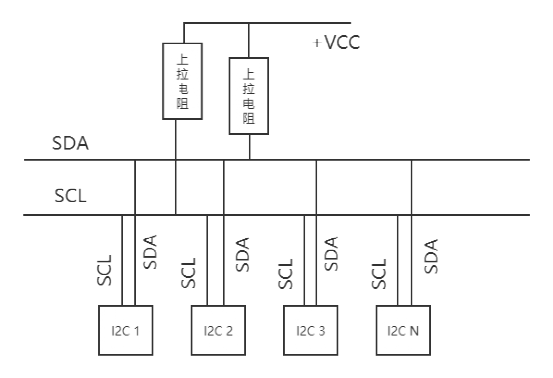

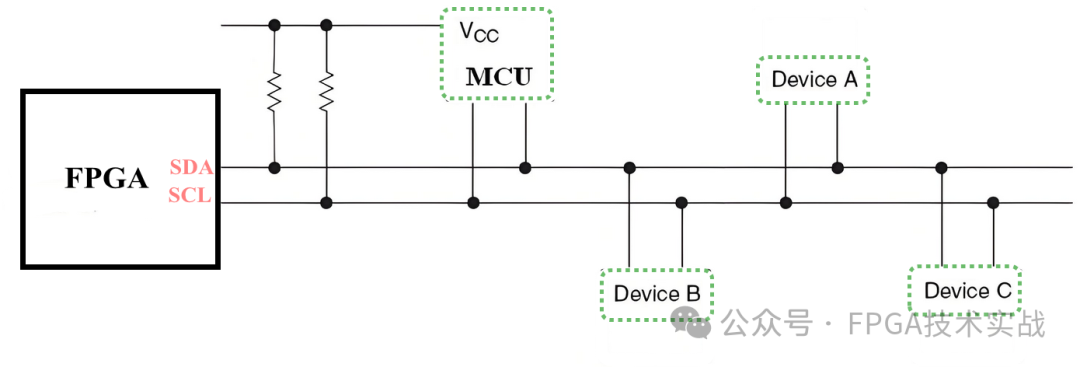

在硬件上,I2C 總線是由時(shí)鐘總線 SCL 和數(shù)據(jù)總線 SDA 兩條線構(gòu)成,連接到總線上的所有器件的 SCL 都連到一起,所有 SDA 都連到一起。I2C 總線是開漏引腳并聯(lián)的結(jié)構(gòu),因此我們外部要

2022-01-07 06:03:45

................................................................... 3016.1 標(biāo)準(zhǔn)模式I2C 總線器件電阻Rp 和RS 的最大和最小值

2009-04-09 18:34:35

這一屆爽是真的爽,hal庫和cubemx節(jié)省一半時(shí)間工作量23333終于學(xué)到I2C了,單片機(jī)的時(shí)候就沒把I2C學(xué)好,現(xiàn)在來惡補(bǔ),,,這個(gè)博主把為什么I2C讀、寫要先設(shè)置0xA1、0xA0講得很到位

2022-01-11 07:12:02

查找從機(jī)。因?yàn)?b class="flag-6" style="color: red">I2C 通信IO口輸出結(jié)構(gòu)都是配置為漏極開路或集電極開路輸出。所以時(shí)鐘線和數(shù)據(jù)線必須外部都接上拉電阻,當(dāng)一對多輸出的時(shí)候,很多GPIO口會連接在同一根線上,可能會存在某個(gè)GPIO輸出高電平

2021-09-07 14:22:56

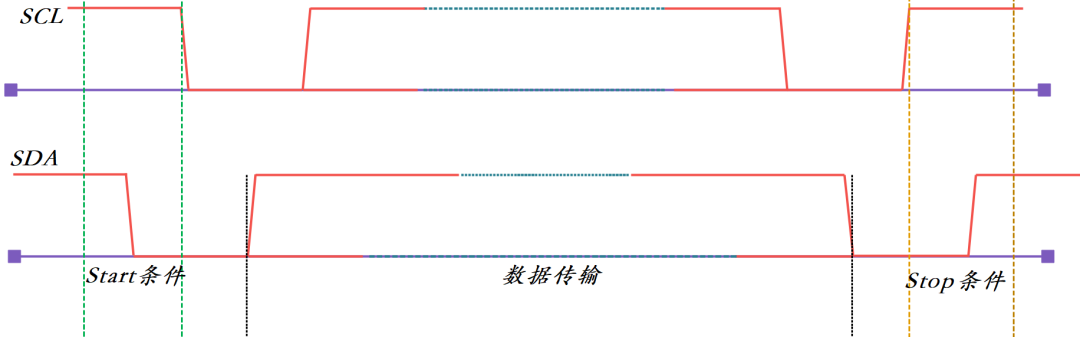

單片機(jī) I2C 時(shí)序介紹在硬件上,I2C 總線是由時(shí)鐘總線 SCL 和數(shù)據(jù)總線 SDA 兩條線構(gòu)成,連接到總線上的所有器件的 SCL 都連到一起,所有 SDA 都連到一起。I2C 總線是開漏引腳并聯(lián)

2022-01-07 06:19:47

I2C上拉電阻 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個(gè)4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。 I2C接口 對于

2022-01-14 07:22:21

開發(fā)板I2C連接到RTC(RX8010)芯片,I2C總線上沒有接上拉電阻,LS1012A手冊上說它的I2C是open drain輸出的,為什么沒有上拉電阻? 哪位能幫助解釋一下,謝謝

2022-01-05 06:28:48

請問用TMS320C5515的GPIO口模擬I2C是否需要加上拉電阻?

2018-07-31 07:48:20

SMT8S003F3P的I2C模塊使用時(shí)需要外接上拉電阻嗎?

2024-05-08 06:19:48

stm32f051的i2c需要外接上拉電阻嗎,直接用內(nèi)部上拉行不行,還有庫中的I2C_Init函數(shù)中有這么一句/* Enable I2Cx Peripheral */I2Cx->CR1 |= I2C_CR1_PE;為什么初始化有些i2c寄存器需要使能i2c。最后附上波形,希望哪位大哥幫幫忙,看看是什么問題。

2019-03-12 07:14:31

I2C總線器件應(yīng)用第一節(jié) I2C總線器件應(yīng)用概述I2C總線工作原理I2C總線系統(tǒng)結(jié)構(gòu)I2C總線系統(tǒng)結(jié)構(gòu)如圖7-1所示。其中,SCL是時(shí)鐘線,SDA是數(shù)據(jù)線。總線上的各器件都采用漏

2008-08-13 17:34:34 0

0

i2c總線的特點(diǎn):2 I2C 總線使設(shè)計(jì)人員和廠商都得益.. 3

2.1 設(shè)計(jì)人員的得益.. 4

2.2 廠商的得益. 5

3 介紹I2C 總線規(guī)范 6

4 I2C 總線的概念. 6

5 總體特征.. 7

2009-08-05 09:05:43 26

26 I2C總線規(guī)范與I2C器件C51讀寫程序:本文簡要介紹了I2C總線,并給出了I2C器件的C51讀寫程序,極大的方便了大家對I2C總線的學(xué)習(xí)和設(shè)計(jì)應(yīng)用。程序設(shè)計(jì)采用模塊化設(shè)計(jì),方便向目標(biāo)板的

2009-08-22 17:51:07 95

95 I2C總線應(yīng)用中的幾個(gè)問題:i2c上拉電阻阻值的確定,PCB布局布線與抗干擾設(shè)計(jì),軟件模擬I2C時(shí)序,I2C 應(yīng)用中上拉電阻電源問題。

2009-09-13 14:27:55 51

51 關(guān)鍵詞 I2C/SMBus、I/O 口擴(kuò)展摘 要CAT9554 是是一款基于I2C 和SMBus 接口的8 位通用型輸入輸出(GPIO)擴(kuò)展器件

2009-11-02 14:27:44 19

19 I2C Guid I2C指南

The I2C bus is used in a wide rangeof applications because it is simpleand

2010-04-23 13:55:40 36

36 什么是i2c總線 下載請點(diǎn)擊: i2c總線協(xié)議中文版

2007-11-05 09:26:07 3182

3182 在電路設(shè)計(jì)中,I2C總線是比較常用的兩線式串行通信方式,大多數(shù)的CPU都擅長于并口操作,不具備直接操作I2C總線接口的能力。為了使不具備I2C總線接口能力的CPU通過對并口的簡單操作實(shí)現(xiàn)對I2C總線接口的控制,在分析I2C總線常用工作模式的基礎(chǔ)上,設(shè)計(jì)實(shí)現(xiàn)工作

2011-02-12 16:11:01 96

96 I2C 的上拉電阻可以是1.5K,2.2K,4.7K, 電阻的大小對時(shí)序有一定影響,對信號的上升時(shí)間和下降時(shí)間也有影響,一般接1.5K 或2.2K.

2012-03-21 15:05:07 116

116 I2C總線在單片機(jī)和其他芯片組中具有廣泛的硬件支持,并且信號傳遞方式簡單,可采用極小的硅片有效實(shí)現(xiàn),但是,I2C總線拓?fù)?b class="flag-6" style="color: red">要依賴于阻值合適的上拉電阻才能實(shí)現(xiàn)穩(wěn)定可靠的通信。

2012-11-15 14:37:29 2958

2958 I2c總線,基于51的I2c總線,程序?qū)W習(xí)。快來下載學(xué)習(xí)吧

2016-01-13 11:49:54 34

34 I2C應(yīng)用中的幾個(gè)問題,I2C上拉電阻的確定,抗干擾設(shè)計(jì)

2016-02-25 14:48:37 4

4 單片機(jī)i2c總線操作;單片機(jī)i2c總線操作;單片機(jī)i2c總線操作;

2016-05-17 11:09:40 35

35 成電路系統(tǒng)。它作為一個(gè)I2C奴隸,并采用兩個(gè)信號:SDA(數(shù)據(jù))和SCL(時(shí)鐘)。I2C引腳功能開漏架構(gòu);因此,外部上拉電阻必須用于SDA和SCL信號設(shè)置總線邏輯電平。 圖1顯示了一個(gè)

2017-05-23 16:13:20 8

8 I2C LCD 器件通過驅(qū)動(dòng)帶有 I2C 接口的 2 線式 16 字符 LCD

2017-10-10 08:22:19 13

13 I2C(Inter-Intergrated Circuit)總線是微電子通信控制領(lǐng)域中常用的一種總線標(biāo)準(zhǔn),具有接線少,控制方式簡單,通信速率高等優(yōu)點(diǎn)。

2017-11-06 17:34:22 77913

77913

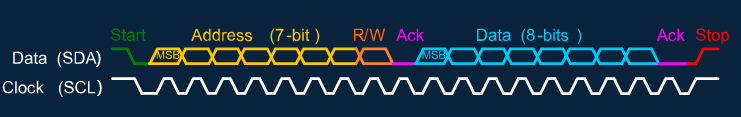

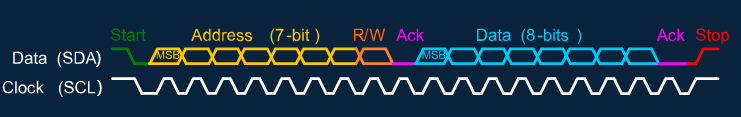

I2C總線在物理連接上非常簡單,分別由SDA(串行數(shù)據(jù)線)和SCL(串行時(shí)鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時(shí)序的控制,來產(chǎn)生I2C總線協(xié)議所需要的信號進(jìn)行數(shù)據(jù)的傳遞。在總線空閑狀態(tài)時(shí),這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2017-12-06 10:48:01 4058

4058

開發(fā)板,即可接收STM32串口發(fā)送給電腦的調(diào)試信息。 【*】 引腳分配 EEPROM(AT24C02): EEPROM芯片的I2C接口與STM32的I2C1相連,且已接上拉電阻。 SCL 《

2017-12-13 15:12:33 23

23 AD(I2C通信)光敏電阻控制LED程序下載

2018-04-18 16:36:37 3

3 LPC2124有一個(gè)標(biāo)準(zhǔn)的I2C總線接口,可配置為主機(jī)或從機(jī),總線時(shí)鐘速率可調(diào)整,最高可支持400KHZ總線速率。使用I2C總線時(shí),要將相應(yīng)得引腳設(shè)置連接SCL和SDA,并且總線上要上拉電阻,阻值為

2019-02-11 10:00:00 2274

2274 I2C總線在物理連接上非常簡單,分別由SDA(串行數(shù)據(jù)線)和SCL(串行時(shí)鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時(shí)序的控制,來產(chǎn)生I2C總線協(xié)議所需要的信號進(jìn)行數(shù)據(jù)的傳遞。

2019-05-14 15:55:33 2229

2229

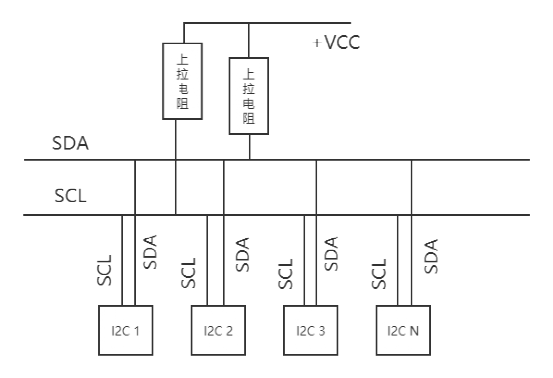

進(jìn)入TC總線系統(tǒng)中的設(shè)備都帶有fC總線接口,符合I2C總線電氣規(guī)范的特性,只需將I2C總線上所有節(jié)點(diǎn)的串行數(shù)據(jù)線SDA和時(shí)鐘線SCL分別與總線的SDA和SCL相連即可。各節(jié)點(diǎn)供電可以不同,但需共地,另外SDA和SCL需分別接上拉電阻。

2019-06-18 17:44:00 0

0 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個(gè)4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。

2019-10-03 16:57:00 24293

24293

I2C總線接口的數(shù)據(jù)線SDA和時(shí)鐘線SCL必須經(jīng)過上拉電阻接到正電源VDD上,各個(gè)I2C接口電路輸出端必須是漏極開路或集電極開路,以便完成“線與”的功能。I2C的SDA和SCL都是雙向傳輸線,當(dāng)總線空閑時(shí),此兩線都是“1”(高電平)。

2019-10-10 15:46:34 1435

1435

這篇文章給大家?guī)砹?b class="flag-6" style="color: red">I2C系列的合集,可以系統(tǒng)學(xué)習(xí)I2C協(xié)議。大家趕緊看看吧! 1、I2C總線:何時(shí)使用I2C緩沖器 本文討論了使用I2C緩沖區(qū)的用例,好處和應(yīng)用。 在用于嵌入式設(shè)備的所有串行接口

2020-09-23 15:28:10 3841

3841 I2C 總線在物理連接上非常簡單,分別由SDA(串行數(shù)據(jù)線)和SCL(串行時(shí)鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時(shí)序的控制,來 產(chǎn)生I2C總線協(xié)議所需要的信號進(jìn)行數(shù)據(jù)的傳遞。在總線空閑狀態(tài)時(shí),這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2020-09-24 14:12:09 7089

7089

I2C總線(SDA,SCL)內(nèi)部都使用漏極開路驅(qū)動(dòng)器(開漏驅(qū)動(dòng)),因此SDA和SCL 可以被拉低為低電平,但是不能被驅(qū)動(dòng)為高電平,所以每條線上都要使用一個(gè)上拉電阻,默認(rèn)情況下將其保持在高電平;

2020-11-16 16:32:30 5840

5840 I2C的上拉電阻可以是1.5K,2.2K,4.7K, 電阻的大小對時(shí)序有一定影響,對信號的上升時(shí)間和下降時(shí)間也有影響,一般接1.5K或2.2K。

2020-11-24 14:27:02 28314

28314 FPGA 芯片通過 I2C 總線連接 EEPROM 24LC04, I2C 的兩根總線各上拉一個(gè) 4.7K的電阻到 3.3V,所以當(dāng)總線上沒有輸出時(shí)會被拉高, 24LC04 的寫保護(hù)沒有使能,丌然

2020-11-26 14:30:26 8166

8166 I2C總線物理拓?fù)浣Y(jié)構(gòu)

I2C 總線在物理連接上非常簡單,分別由SDA(串行數(shù)據(jù)線)和SCL(串行時(shí)鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時(shí)序的控制,來 產(chǎn)生I2C

2022-02-09 14:08:17 2837

2837

I2C總線物理拓?fù)浣Y(jié)構(gòu)

I2C 總線在物理連接上非常簡單,分別由SDA(串行數(shù)據(jù)線)和SCL(串行時(shí)鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時(shí)序的控制,來 產(chǎn)生I2C總線

2021-03-02 06:00:24 5

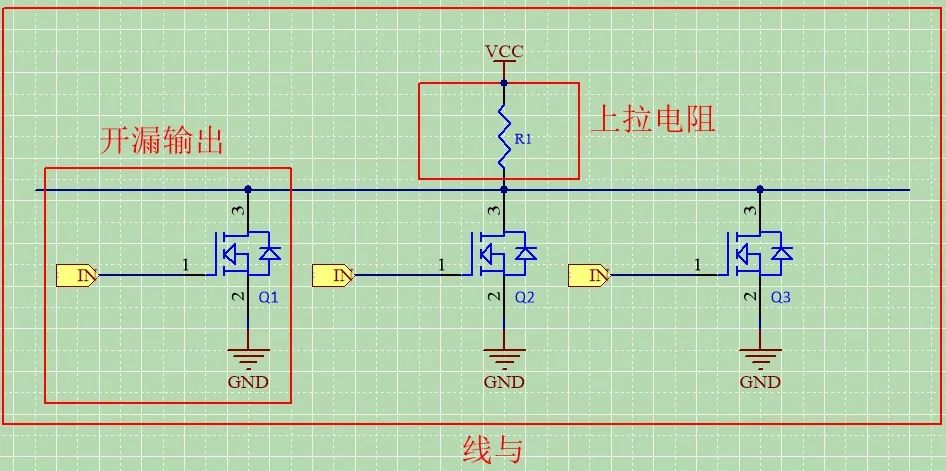

5 I2C為什么要接上拉電阻?因?yàn)樗情_漏輸出。 1 為什么是開漏輸出? I2C協(xié)議支持多個(gè)主設(shè)備與多個(gè)從設(shè)備在一條總線上,如果不用開漏輸出,而用推挽輸出,會出現(xiàn)主設(shè)備之間短路的情況。 所以總線一般會使

2021-06-21 10:30:02 16500

16500 I2C為什么要接上拉電阻?因?yàn)樗情_漏輸出!

2021-06-21 16:34:33 13557

13557

在電子設(shè)計(jì)開發(fā)中I2C大家已經(jīng)很熟悉了,每一種電子產(chǎn)品小到電子開關(guān),大到衛(wèi)星通信都會利用的I2C總線。據(jù)統(tǒng)計(jì)I2C在電子產(chǎn)品中占據(jù)了93%的份額,幾乎任何一種電路都要使用。 I2C是由PHILIPS

2021-08-26 14:08:36 19393

19393

1、所有的I2C接口都是OD開漏輸出的模式(可以實(shí)現(xiàn)線與的功能),因此在使用MCU模擬I2C通信時(shí),SCL和SDA必須配置為OD模式,不能配置為PP推挽輸出模式(不能正常通信)2、SCL和SDA總線

2021-12-02 14:21:13 9

9 硬件I2C對應(yīng)芯片上的I2C外設(shè),有相應(yīng)I2C驅(qū)動(dòng)電路,其所使用的I2C管腳也是專用的,因而效率要遠(yuǎn)高于軟件模擬的I2C;一般也較為穩(wěn)定,但是程序較為繁瑣。硬件(固件)I2C是直接調(diào)用內(nèi)部寄存器進(jìn)行

2021-12-28 19:14:11 81

81 使用STM32的GPIO模擬I2C總線時(shí)序,GPIO設(shè)置為開漏模式,SDA和SCK外部必須使用上拉電阻,一般是4.7K。開漏模式的好處是,可以同時(shí)讀取輸入電平,而無需切換輸入/輸出模式。注意事項(xiàng):在

2021-12-28 19:36:15 13

13 I2C上拉電阻 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個(gè)4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。 I2C接口 對于

2022-01-14 14:10:36 10

10 SDA和SCL需要外接上拉電阻,根據(jù)總線上的I2C設(shè)備數(shù)量,系統(tǒng)的通信速度,設(shè)計(jì)選擇不同的上拉電阻。I2C設(shè)備數(shù)量決定了總線上母線電容的大小,母線電容和上拉電阻限制了系統(tǒng)的通信速率。

2022-06-29 11:28:56 7845

7845

電子發(fā)燒友網(wǎng)站提供《ESP 12E I2c基卡的I2C IO卡設(shè)計(jì).zip》資料免費(fèi)下載

2022-08-15 09:27:09 3

3 I2C一般為開漏結(jié)構(gòu),需要在外部加上拉電阻,常見的阻值有1k、1.5k、2.2k、4.7k、5.1k、10k等。

2022-09-02 09:49:29 5149

5149 I2C總線為什么要接上拉電阻 1、根據(jù)I2C總線規(guī)范,總線空閑時(shí)兩根線都必須為高; 這是規(guī)定,動(dòng)不了的,不然什么叫標(biāo)準(zhǔn)呢?其實(shí)所謂的這個(gè)神圣的標(biāo)準(zhǔn)也并不是多么邪乎,你想啊,只有是高的才能拉成低

2022-10-25 20:36:14 1604

1604 I2C總線為什么要接上拉電阻 1、根據(jù)I2C總線規(guī)范,總線空閑時(shí)兩根線都必須為高; 這是規(guī)定,動(dòng)不了的,不然什么叫標(biāo)準(zhǔn)呢?其實(shí)所謂的這個(gè)神圣的標(biāo)準(zhǔn)也并不是多么邪乎,你想啊,只有是高的才能拉成低

2022-11-09 13:21:04 4212

4212 我們知道,在I2C的電路中,在SCL、SDA線與電源之間通常會接一個(gè)電阻,這個(gè)電阻稱之為上拉電阻。

2022-11-24 09:19:55 10562

10562 I2C總線為什么要接上拉電阻 1、根據(jù)I2C總線規(guī)范,總線空閑時(shí)兩根線都必須為高; 這是規(guī)定,動(dòng)不了的,不然什么叫標(biāo)準(zhǔn)呢?其實(shí)所謂的這個(gè)神圣的標(biāo)準(zhǔn)也并不是多么邪乎,你想啊,只有是高的才能拉成低

2022-12-13 16:30:04 4286

4286 如果上拉阻值過小,VDD灌入端口的電流將較大,功耗會很大,導(dǎo)致端口輸出的低電平值增大(I2C協(xié)議規(guī)定,端口輸出低電平的最高允許值為0.4V)。

2023-02-06 10:53:18 2407

2407 I2C 總線在物理連接上非常簡單,分別由SDA(串行數(shù)據(jù)線)和SCL(串行時(shí)鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時(shí)序的控制,來 產(chǎn)生I2C總線協(xié)議所需要的信號進(jìn)行數(shù)據(jù)的傳遞。在總線空閑狀態(tài)時(shí),這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2023-02-11 09:54:39 773

773 I2C 總線在物理連接上非常簡單,分別由SDA(串行數(shù)據(jù)線)和SCL(串行時(shí)鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時(shí)序的控制,來 產(chǎn)生I2C總線協(xié)議所需要的信號進(jìn)行數(shù)據(jù)的傳遞。在總線空閑狀態(tài)時(shí),這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

2023-02-13 10:14:21 2184

2184

I2C協(xié)議支持多個(gè)主設(shè)備與多個(gè)從設(shè)備在一條總線上,如果不用開漏輸出,而用推挽輸出,會出現(xiàn)主設(shè)備之間短路的情況。所以總線一般會使用開漏輸出。

2023-02-24 09:18:48 2640

2640 I2C總線是微電子通信控制領(lǐng)域中常用的一種總線標(biāo)準(zhǔn),具備接線少,控制簡單,速率高等優(yōu)點(diǎn)。在I2C電路中常見的上拉電阻有1k、1.5k、2.2k、4.7k、5.1k、10k等等,但是應(yīng)該如何根據(jù)開發(fā)要求選擇合適的阻值呢?下圖為I2C內(nèi)部結(jié)構(gòu)

2023-05-10 16:17:05 9283

9283

信息和接收信息無法同時(shí)進(jìn)行,I2C工作時(shí)的傳輸速率在標(biāo)準(zhǔn)模式下可達(dá)100kbit/s,快速模式下可達(dá)400kbit/s,高速模式下可達(dá)3.4Mbit/s。I2C總線采用漏極開路的設(shè)計(jì),且SDA和SCL通過上拉電阻連接V~CC~。今天就和大家來探討一下I2C為什么需要用開漏輸出和上拉電阻。

2023-07-02 16:39:21 7470

7470

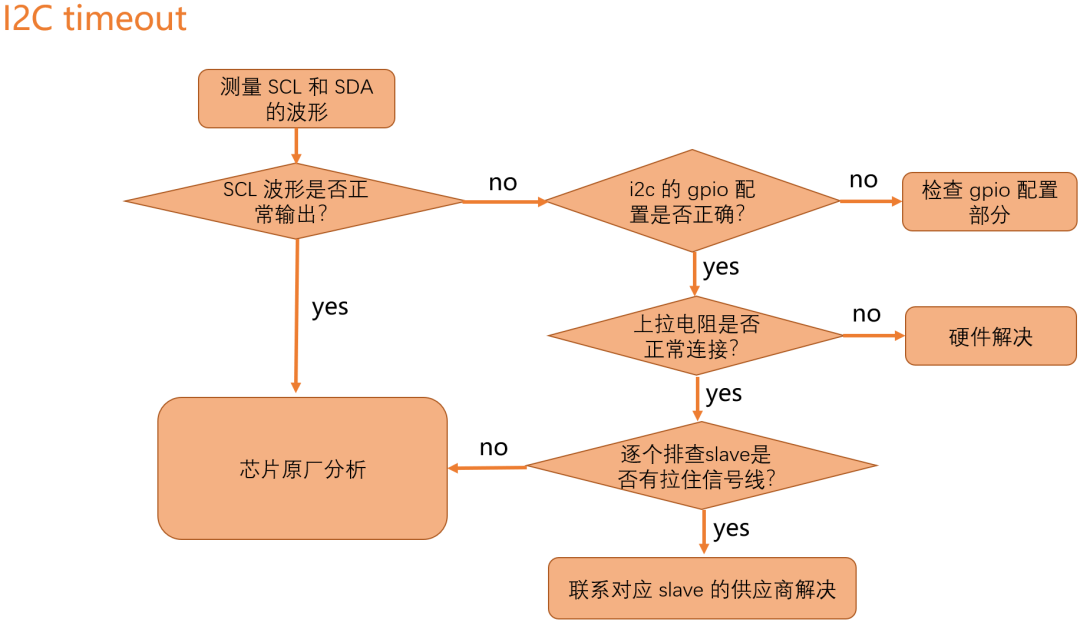

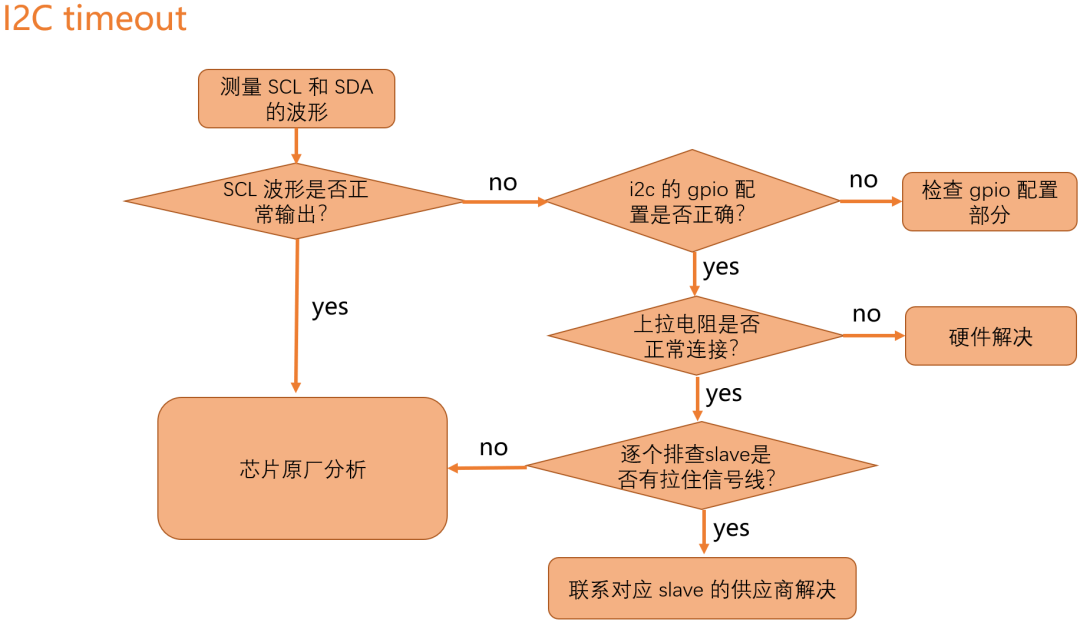

,transfer timeout 1、GPIO check 以下幾個(gè)部分 GPIO 電流驅(qū)動(dòng)能力 GPIO 工作模式是否是 I2C 模式 GPIO 是否有內(nèi)部上拉電阻 GPIO 默認(rèn)電平狀態(tài) 2、排查 slave

2023-07-22 14:46:40 4238

4238

RK 平臺 I2C debug 1、I2C 通信失敗,出現(xiàn) log: “timeout, ipd: 0x00, state: 1” 請檢查硬件上拉是否給電。 2、調(diào)用 i2c

2023-07-22 15:00:27 6009

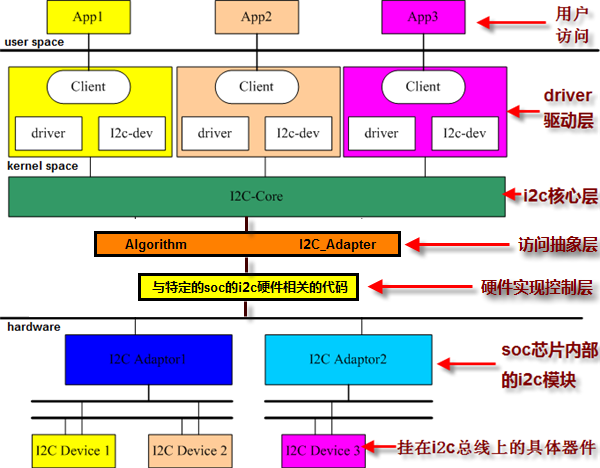

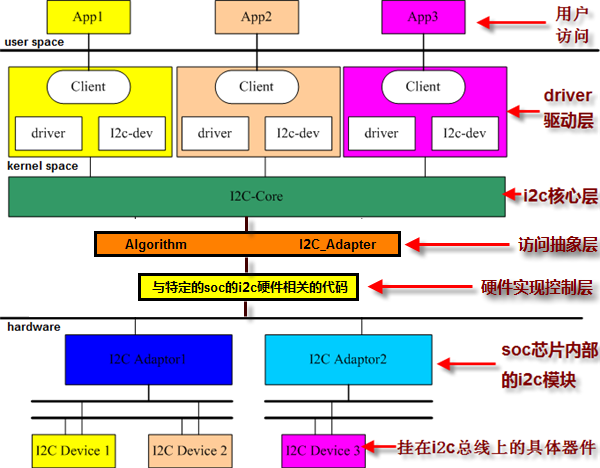

6009 I2C SW Architecture 【driver 驅(qū)動(dòng)層】由普通驅(qū)動(dòng)工程師負(fù)責(zé),【i2c 核心層】由 Linux 提供,【i2c 核心層】以下由芯片原廠負(fù)責(zé)。 I2C 子系統(tǒng)

2023-07-22 16:01:00 1514

1514

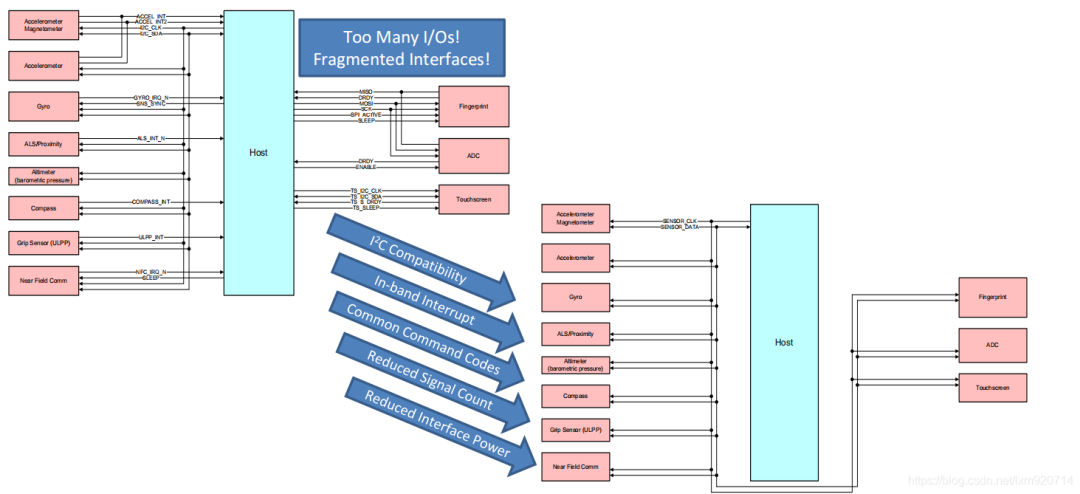

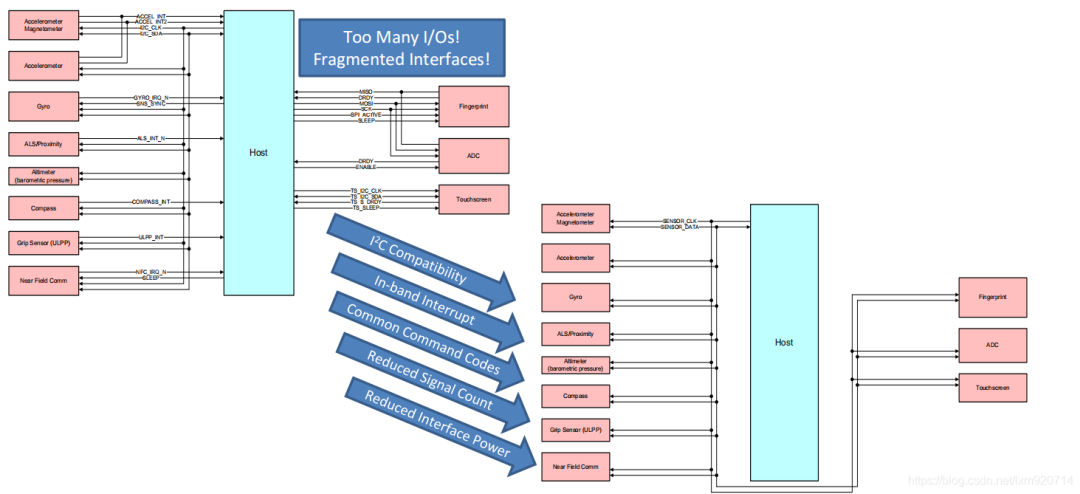

I2C 和 I3C 主要區(qū)別如下: I2C 雖然也是兩條線,但是很多時(shí)候傳感器需要一條額外的中斷線,來告訴主控?cái)?shù)據(jù)已經(jīng)準(zhǔn)備好。I3C 允許從設(shè)備直接在總線上產(chǎn)生中斷,不再需要一條額外的中斷

2023-07-22 16:20:20 9525

9525

上拉電阻和等效電容決定(RC)。 I2C 是一種多主從架構(gòu)總線 I2C 的讀寫均由 master 端發(fā)起。

2023-07-25 09:41:01 6084

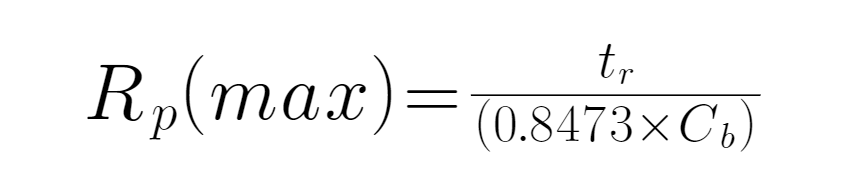

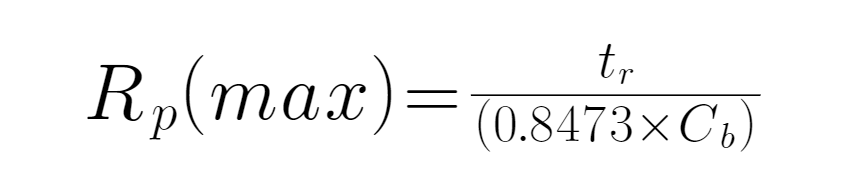

6084 上拉電阻計(jì)算 1、上拉電阻過小,電流大,端口低電平 level 增大。 2、上拉電阻過大,上升沿時(shí)間增大,方波可能會變成三角波。 因此計(jì)算出一個(gè)精確的上拉電阻阻值是非常重要的。計(jì)算上拉電阻的阻值,有

2023-07-25 10:03:23 2809

2809

相信很多人都清楚,在I2C總線上需要接上拉電阻?但是您針對對I2C上拉電阻足夠了解嗎?本文帶您詳細(xì)掌握一下I2C的上拉電阻。

2023-07-25 10:37:59 4277

4277

i2c采樣是上升沿嗎??

I2C采樣是指在

I2C總線上對數(shù)據(jù)進(jìn)行采樣。在

I2C總線上,數(shù)據(jù)的傳輸是通過

2條線傳遞。一條是時(shí)鐘線(SCL),另一條是數(shù)據(jù)線(SDA)。采樣的目的是為了準(zhǔn)確地讀取或?qū)懭?/div>

2023-09-19 17:16:05 4510

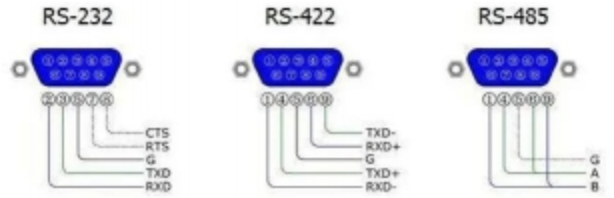

4510 UART、SPI、I2C比較 I2C線更少,比UART、SPI更為強(qiáng)大,但是技術(shù)上也更加麻煩些,因?yàn)?b class="flag-6" style="color: red">I2C需要有雙向IO的支持,而且使用上拉電阻,抗干擾能力較弱,一般用于同一板卡上芯片之間的通信

2023-11-09 18:06:42 2597

2597

通信從I2C總線空閑開始,時(shí)鐘和數(shù)據(jù)線都不被驅(qū)動(dòng),因此被上拉電阻拉高。然后,主機(jī)(啟動(dòng)通信的器件)啟動(dòng)通信,首先拉低SDA線,然后拉低SCL線,這被定義為起始條件。

2023-11-27 15:32:18 1164

1164

I2C總線上的上拉電阻范圍是多少?

回答: 總線電容是走線部分、連接部分、管腳部分的電容的總和。總線電容限制了上拉電阻(Rp) 的最大值,因?yàn)?b class="flag-6" style="color: red">I2C規(guī)定了上升時(shí)間(SDA和SCL信號的上升時(shí)間)。

2023-12-25 09:19:03 2928

2928 每個(gè)設(shè)備都可以將線拉低(Ground),但不能將線拉高(Vcc)。這種設(shè)計(jì)使得多個(gè)設(shè)備可以共享同一條總線,以進(jìn)行通信。二、I2C接口接外部上拉電阻的原因I2C(I

2024-05-16 08:10:40 10904

10904

數(shù)據(jù)線加上拉電阻。這一設(shè)計(jì)不僅關(guān)乎技術(shù)的實(shí)現(xiàn),更涉及系統(tǒng)安全和信號傳輸效率的優(yōu)化。本文將深入探討在I2C總線上加上拉電阻的必要性及其帶來的技術(shù)優(yōu)勢。 我們需要理解I2C總線的基本架構(gòu)。I2C總線是一種多主多從的通信網(wǎng)絡(luò),允許多個(gè)設(shè)備通過

2024-09-09 17:16:33 2536

2536 I2C總線不僅能夠確保信號傳輸?shù)姆€(wěn)定,還能有效地防止多設(shè)備操作中的電氣沖突。確定適當(dāng)?shù)纳?b class="flag-6" style="color: red">拉電阻值對于保證I2C通信的可靠性和效率至關(guān)重要。雖然在大多數(shù)應(yīng)用中,使用標(biāo)準(zhǔn)的4.7kΩ電阻通常可以滿足需求

2024-09-09 17:20:30 1542

1542 電子發(fā)燒友網(wǎng)站提供《I2C總線上拉電阻計(jì)算.pdf》資料免費(fèi)下載

2024-10-08 09:54:21 1

1 本文從I2C協(xié)議的概述開始,描述協(xié)議的歷史、不同速度模式、物理層和數(shù)據(jù)幀結(jié)構(gòu),最后介紹I2C混合電壓系統(tǒng)中電平兼容性以及上拉電阻大小計(jì)算。

2024-10-22 15:51:28 4365

4365

I2C為什么要接上拉電阻?因?yàn)樗情_漏輸出。 為什么是開漏輸出? I2C協(xié)議支持多個(gè)主設(shè)備與多個(gè)從設(shè)備在一條總線上,如果不用開漏輸出,而用推挽輸出,會出現(xiàn)主設(shè)備之間短路的情況。所以總線一般會使用開漏

2024-11-20 10:07:42 1905

1905

I2C總線是一種廣泛使用的串行通信協(xié)議,它允許多個(gè)設(shè)備通過兩條線(數(shù)據(jù)線SDA和時(shí)鐘線SCL)進(jìn)行通信。為了確保數(shù)據(jù)信號的穩(wěn)定性和減少反射,I2C總線的數(shù)據(jù)線SDA和時(shí)鐘線SCL都需要適當(dāng)?shù)纳?b class="flag-6" style="color: red">拉電阻

2025-01-17 15:43:19 1350

1350 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論