本文來(lái)自 XILINX產(chǎn)品應(yīng)用工程師 Davis Zhang

I2C 總線的兩根信號(hào)線 SCL 和 SDA 需要上拉才能正常工作,當(dāng)板卡上沒(méi)有合適的硬件設(shè)置或者沒(méi)有合適的 I2Cslave 設(shè)備,我們就無(wú)法進(jìn)行 I2C 軟件測(cè)試。那么是否可以將兩個(gè) PSI2C 控制器通過(guò) EMIO 接口互連起來(lái)呢?

因?yàn)樵?PL 內(nèi)部無(wú)法設(shè)置信號(hào)線上拉,所以不能直接將 I2Cmaster 控制器的 scl_o/sda_o 連接到 I2C slave 控制器的 scl_i/sda_i。有另一種方法來(lái)實(shí)現(xiàn)上拉的效果,就是通過(guò)在頂層 wrapper 里 scl_T 和 sda_T 的組合邏輯來(lái)模擬 scl_i 和 sda_i,具體邏輯如下,

assign i2c0_scl_i = i2c1_scl_t && i2c0_scl_t;

assign i2c0_sda_i = i2c1_sda_t && i2c0_sda_t;

assign i2c1_scl_i = i2c0_scl_t && i2c1_scl_t;

assign i2c1_sda_i = i2c0_sda_t && i2c1_sda_t;

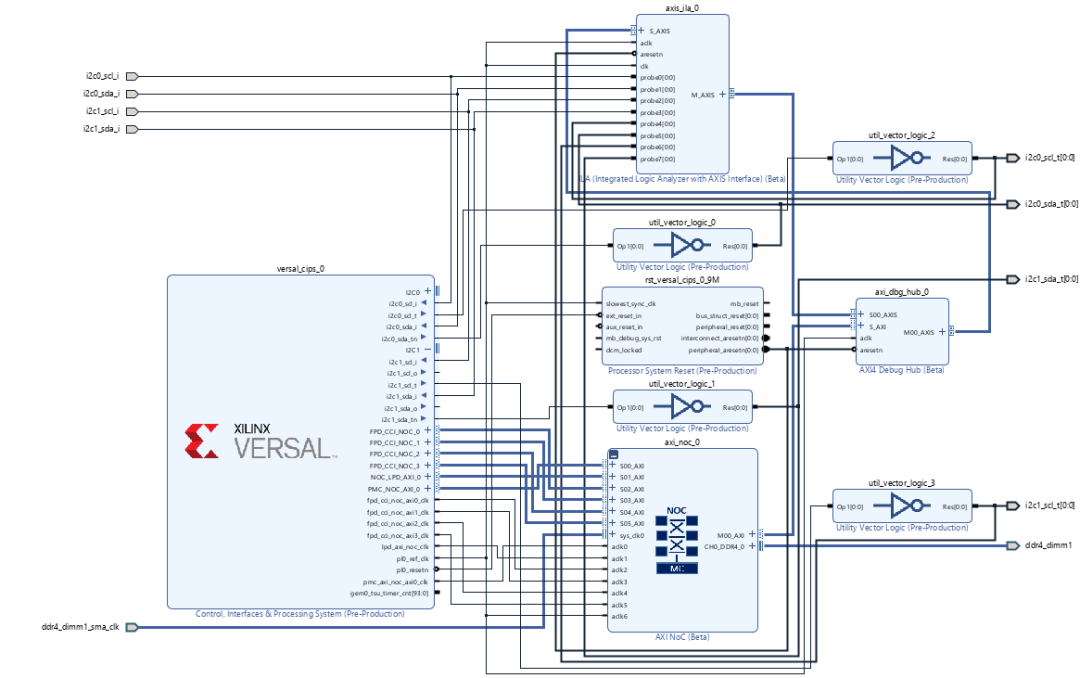

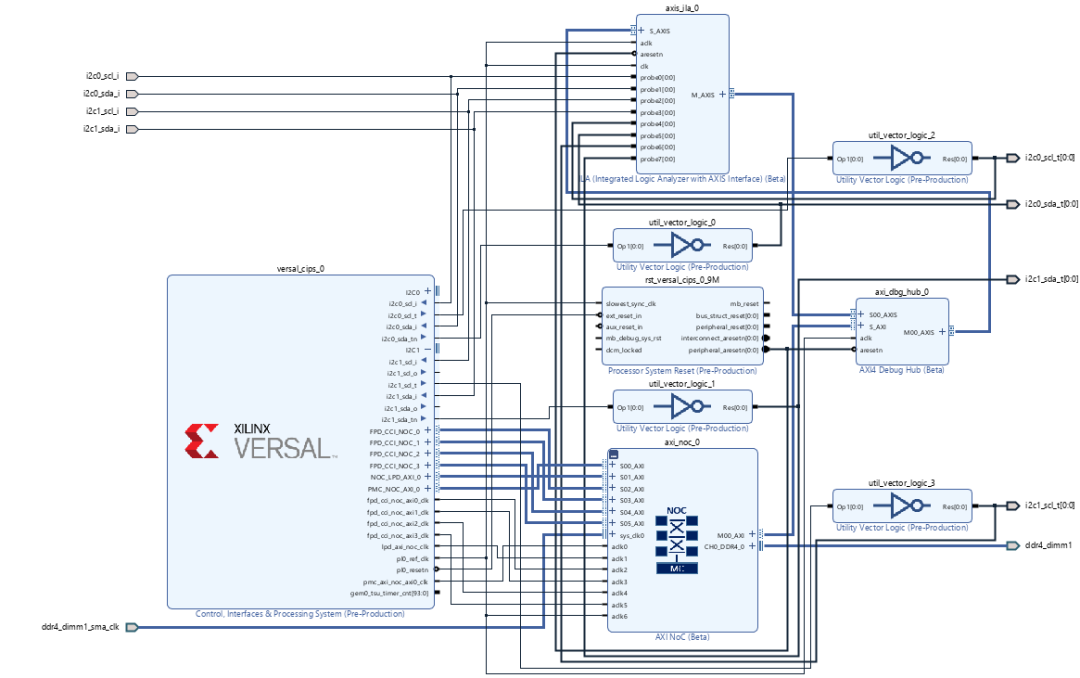

這些信號(hào)都是兩個(gè) PS I2C 控制器的 emio 信號(hào)從 block design 導(dǎo)出到頂層 wrapper,其中四個(gè) emio 信號(hào)在從 block design 導(dǎo)出到頂層 wrapper 之前需要做邏輯反相。

i2c0_scl_t、i2c0_sda_tn、i2c1_scl_t、i2c1_sda_tn

反相操作如圖中 util_vector_logic_0~3所示,

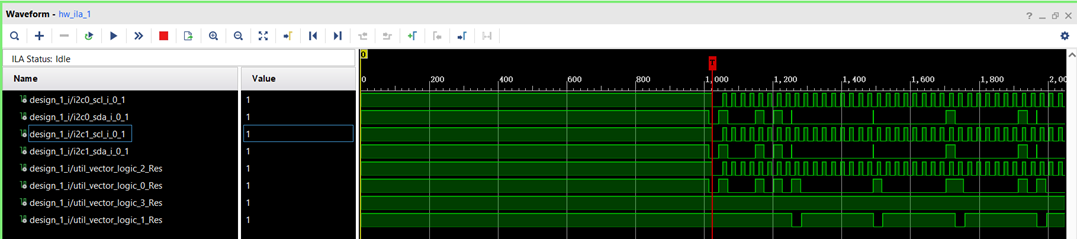

附件是個(gè)例子工程 (附件可點(diǎn)擊閱讀原文 輸入0513獲取),基于 vck190 es1 board 和 Vivado2020.2。里面包含 block design tcl腳本、頂層 wrapper、prebuilt xsa 文件和 vitis application 源碼。Vitis application 把i2c0 配置為 master、i2c1 為 slave,然后做讀寫校驗(yàn)測(cè)試。可以通過(guò)串口輸出信息來(lái)判斷是否測(cè)試成功,block design 里也介入了 ila,可以在 hardware manager 里檢查相關(guān)信號(hào)。下面是 i2c0_scl_i/i2c0_sda_i/i2c1_scl_i/i2c1_sda_i 波形 :

原文標(biāo)題:開(kāi)發(fā)者分享 | 如何在 Versal 平臺(tái)實(shí)現(xiàn)兩個(gè) PS I2C 控制器的回環(huán)

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

控制器

+關(guān)注

關(guān)注

114文章

17791瀏覽量

193167 -

Xilinx

+關(guān)注

關(guān)注

73文章

2200瀏覽量

131137 -

I2C

+關(guān)注

關(guān)注

28文章

1556瀏覽量

131235

原文標(biāo)題:開(kāi)發(fā)者分享 | 如何在 Versal 平臺(tái)實(shí)現(xiàn)兩個(gè) PS I2C 控制器的回環(huán)

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

為什么I2C總線忙于兩個(gè)設(shè)備?

實(shí)現(xiàn)I2C總線控制器的VHDL源代碼

基于I2C和雙ARM的PCB鉆床控制器設(shè)計(jì)

LM3S系列微控制器I2C應(yīng)用文檔

基于Verilog的I2C控制器的設(shè)計(jì)與綜合

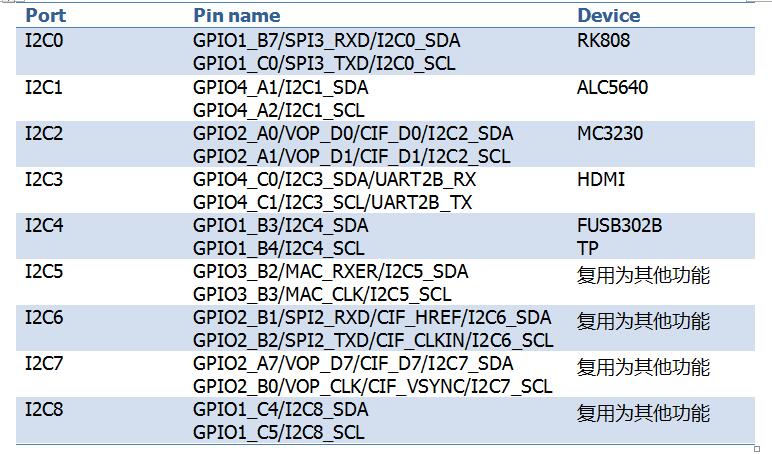

Firefly-RK3128主板I2C控制器

i2c總線用來(lái)做什么_i2c總線數(shù)據(jù)傳輸過(guò)程

如何將兩個(gè)PSI2C控制器通過(guò)EMIO接口互連起來(lái)?

如何在Versal平臺(tái)實(shí)現(xiàn)兩個(gè)PS I2C控制器的回環(huán)

使用I2C通信連接兩個(gè)Arduino

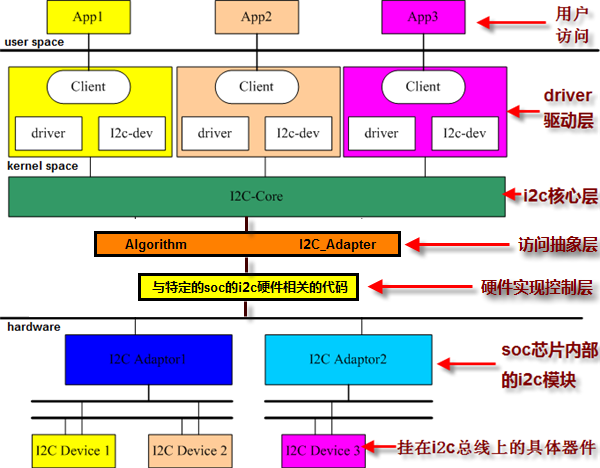

I2C控制器驅(qū)動(dòng)介紹

I2C設(shè)備驅(qū)動(dòng)的兩個(gè)數(shù)據(jù)結(jié)構(gòu)

I2C子系統(tǒng)SW Architecture

兩個(gè)PS I2C控制器的回環(huán)測(cè)試

兩個(gè)PS I2C控制器的回環(huán)測(cè)試

評(píng)論