晶片鍵合是指通過一系列物理過程將兩個(gè)或多個(gè)基板或晶片相互連接和化學(xué)過程。晶片鍵合用于各種技術(shù),如MEMS器件制造,其中傳感器組件封裝在應(yīng)用程序中。其他應(yīng)用領(lǐng)域包括三維集成、先進(jìn)的封裝技術(shù)和CI制造業(yè)在晶圓鍵合中有兩種主要的鍵合,臨時(shí)鍵合和永久鍵合,兩者都是在促進(jìn)三維集成的技術(shù)中發(fā)揮著關(guān)鍵作用。

2022-07-21 17:27:43 3882

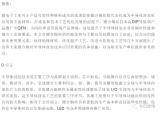

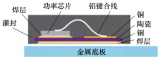

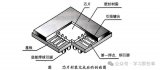

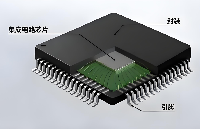

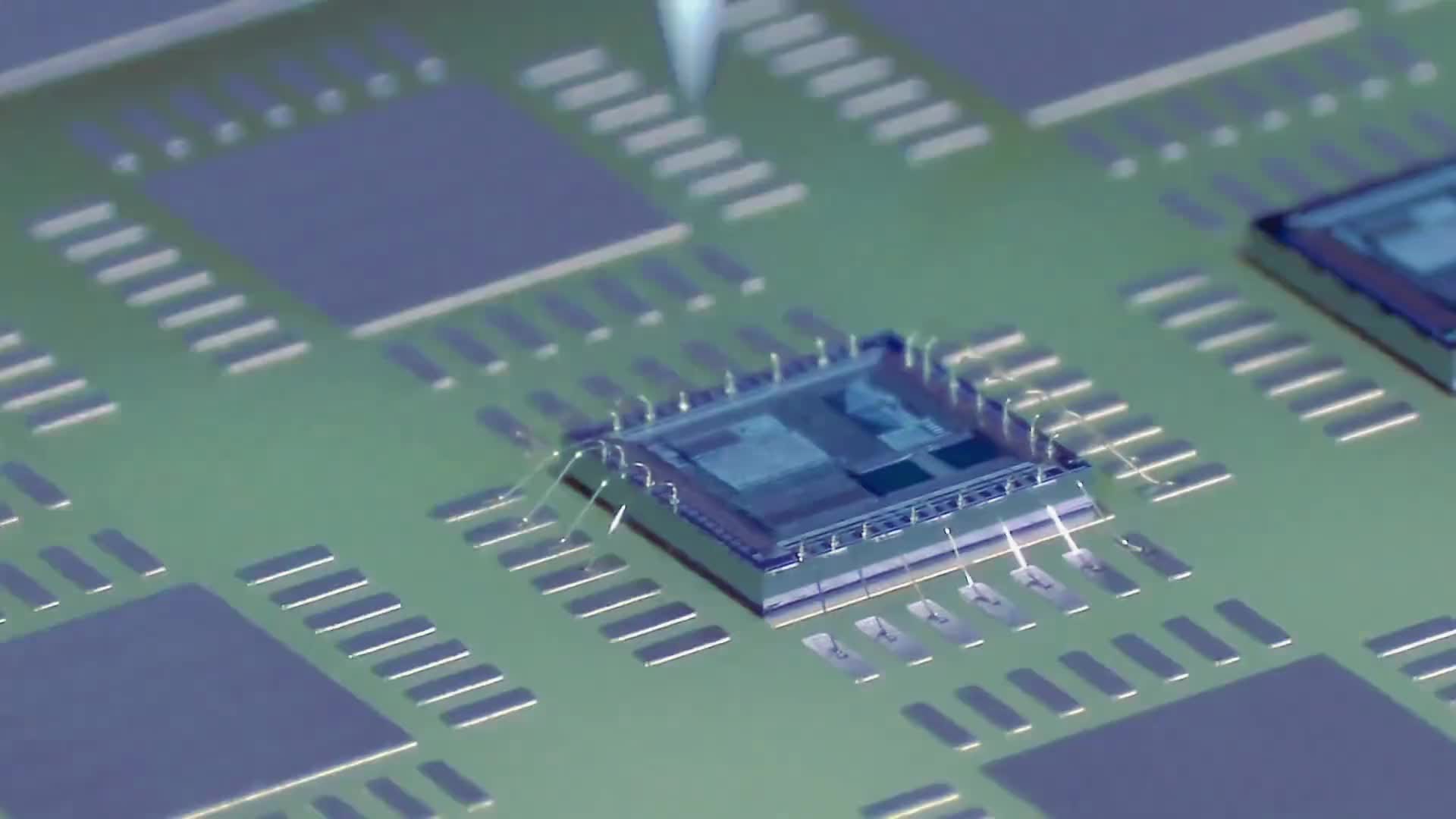

3882 作為半導(dǎo)體制造的后工序,封裝工藝包含背面研磨(Back Grinding)、劃片(Dicing)、芯片鍵合(Die Bonding)、引線鍵合(Wire Bonding)及成型(Molding)等步驟。

2023-03-27 09:33:37 17002

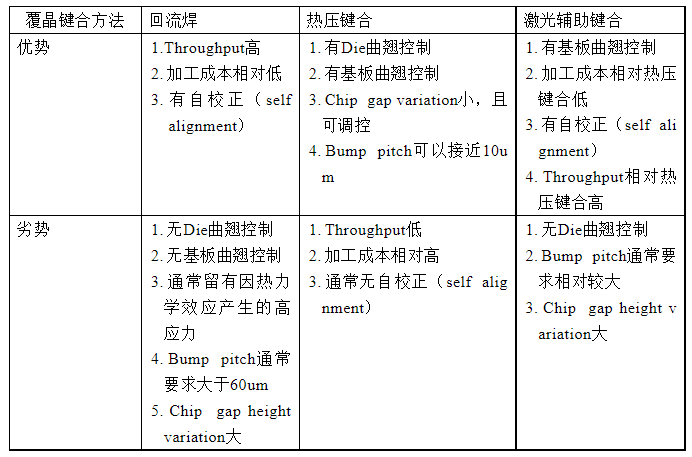

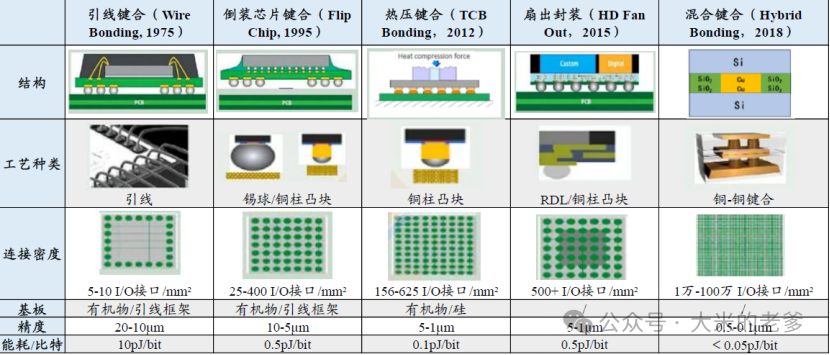

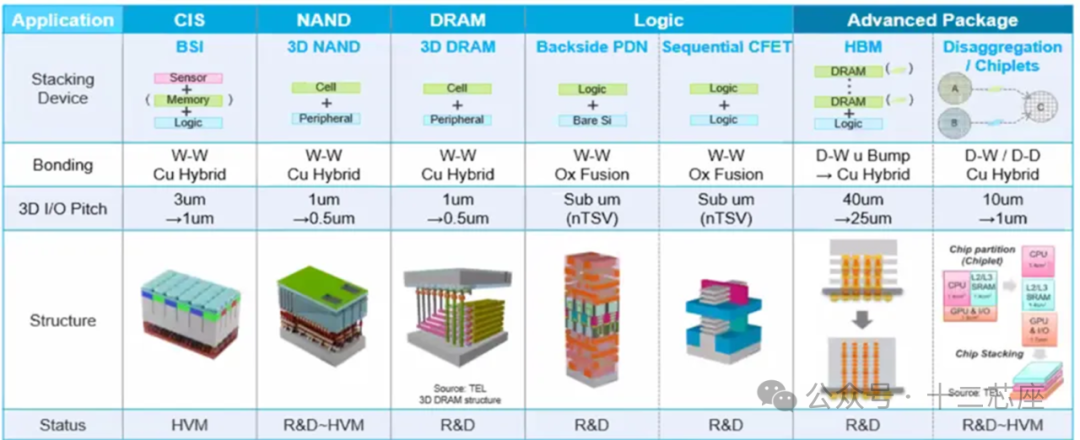

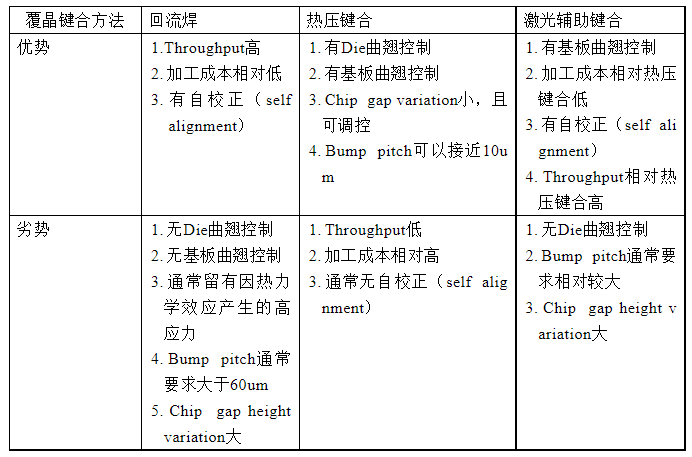

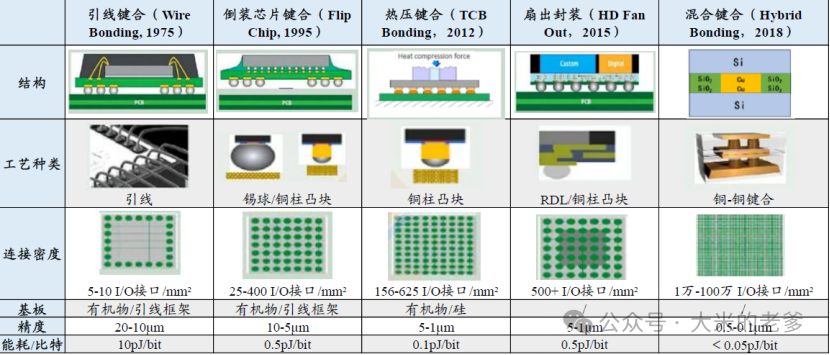

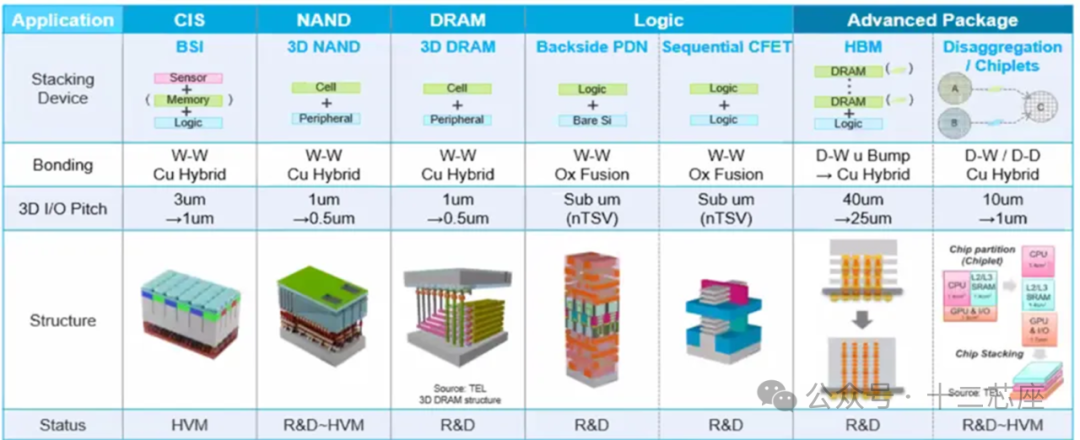

17002 (858mm2)以及制程的縮小也變得非常艱難且性價(jià)比遇到挑戰(zhàn), 多芯片封裝技術(shù)來到了舞臺(tái)的中心成為進(jìn)一步提升芯片性能的關(guān)鍵。 覆晶鍵合技術(shù)已然成為先進(jìn)多芯片封裝最重要的技術(shù)之一。

2023-04-19 09:42:52 2771

2771

(858mm2)以及制程的縮小也變得非常艱難且性價(jià)比遇到挑戰(zhàn), 多芯片封裝技術(shù)來到了舞臺(tái)的中心成為進(jìn)一步提升芯片性能的關(guān)鍵。覆晶鍵合技術(shù)已然成為先進(jìn)多芯片封裝最重要的技術(shù)之一。

2023-05-11 10:24:38 1639

1639

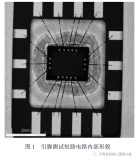

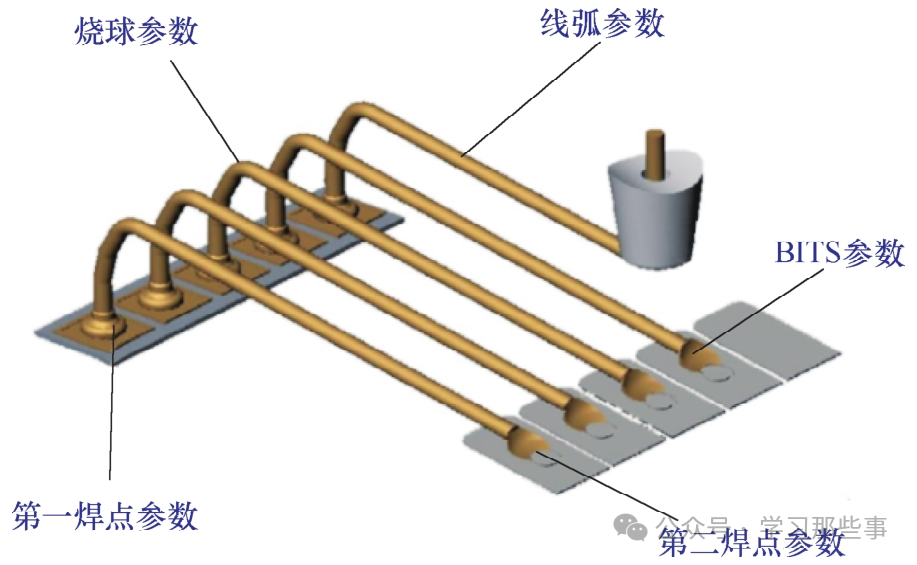

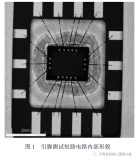

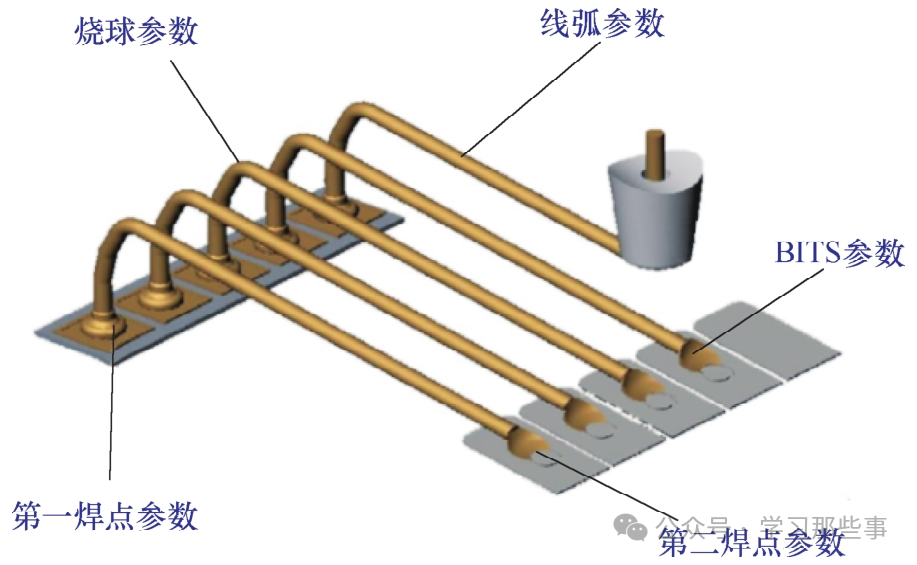

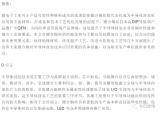

等問題,分析其失效原因,通過試驗(yàn),確認(rèn)鍵合點(diǎn)間距是弧形狀態(tài)的重要影響因素。據(jù)此,基于鍵合設(shè)備的能力特點(diǎn),在芯片設(shè)計(jì)符合鍵合工藝規(guī)則的前提下,提出鍵合工藝的優(yōu)化。深入探討在設(shè)計(jì)芯片和制定封裝工藝方案時(shí),保證鍵合點(diǎn)與周圍金屬化區(qū)域的合理間距以及考慮芯片PAD與管殼鍵合指的距離的重要性。

2023-11-02 09:34:05 2182

2182

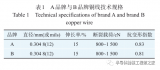

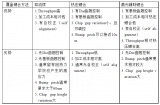

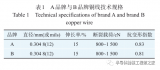

為了提高功率模塊銅線鍵合性能,采用6因素5水平的正交試驗(yàn)方法,結(jié)合BP(Back Propaga‐tion)神經(jīng)網(wǎng)絡(luò)與遺傳算法,提出了一種銅線鍵合工藝參數(shù)優(yōu)化設(shè)計(jì)方案。首先,對選定樣品進(jìn)行正交試驗(yàn)

2024-01-03 09:41:19 2467

2467

在微電子封裝領(lǐng)域,銅線鍵合技術(shù)以其低成本、高效率和良好的電氣性能等優(yōu)勢,逐漸成為芯片與基板連接的主流方式。然而,銅線鍵合過程中的焊接一致性問題是制約其進(jìn)一步發(fā)展和應(yīng)用的關(guān)鍵難題。焊接一致性不僅

2024-03-13 10:10:08 2005

2005

,金絲鍵合工藝便能與其他耐受溫度在300℃以下的微組裝工藝相互適配,在高可靠集成電路封裝領(lǐng)域得到廣泛運(yùn)用。

2025-03-12 15:28:38 3669

3669

細(xì)分領(lǐng)域中位列第一。 ? 封裝的另一大趨勢則是小型化,現(xiàn)階段更小、更薄、更高密度的封裝結(jié)構(gòu)已成為行業(yè)新常態(tài)。為了滿足各種設(shè)計(jì)場景對封裝尺寸的苛刻要求,諸多封裝技術(shù)已經(jīng)不再使用膠水來進(jìn)行芯片粘接,而是會(huì)選擇使用芯片粘貼膠膜。 ? 引線鍵合封裝

2023-10-17 09:05:07 2520

2520 電子發(fā)燒友網(wǎng)綜合報(bào)道 半導(dǎo)體封裝技術(shù)正經(jīng)歷從傳統(tǒng)平面架構(gòu)向三維立體集成的革命性躍遷,其中銅 - 銅混合鍵合技術(shù)以其在互連密度、能效優(yōu)化與異構(gòu)集成方面的突破,成為推動(dòng) 3D 封裝發(fā)展的核心

2025-06-29 22:05:13 1519

1519 (UV)、加熱或機(jī)械方式解鍵合移除。 ? 需要注意區(qū)別玻璃載板與玻璃基板,玻璃載板屬于臨時(shí)支撐工具,可重復(fù)使用3-4次,而玻璃基板為永久性芯片平臺(tái),是最終產(chǎn)品結(jié)構(gòu)的一部分。 ? 之所以需要在半導(dǎo)體封裝中采用鍵合玻璃載板,核心原因是傳統(tǒng)載板已難以滿足先進(jìn)

2026-01-05 09:23:37 569

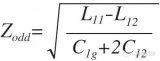

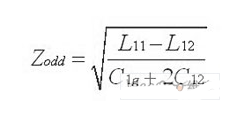

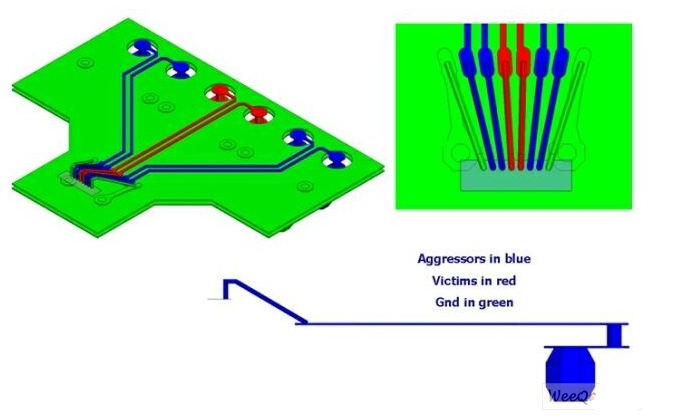

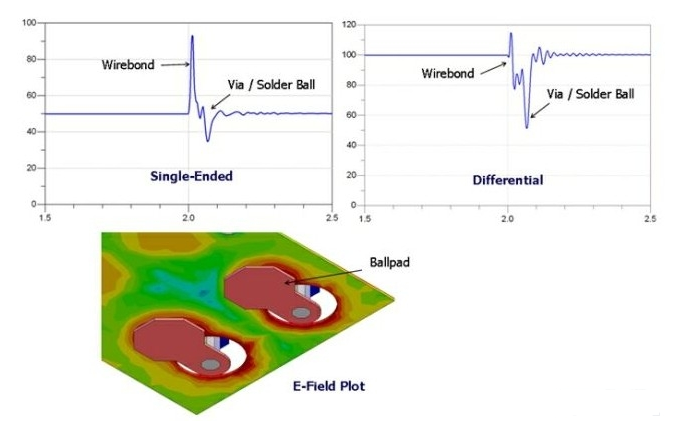

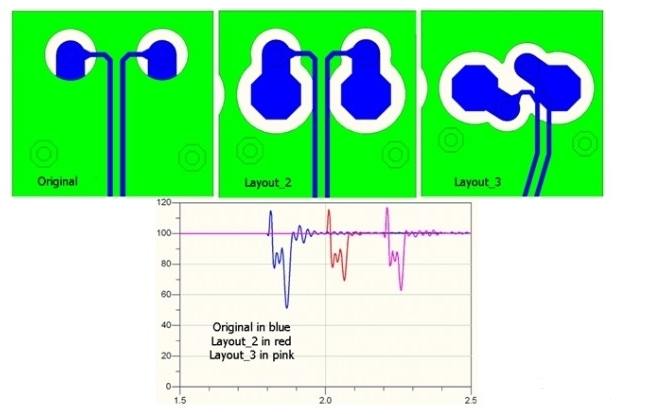

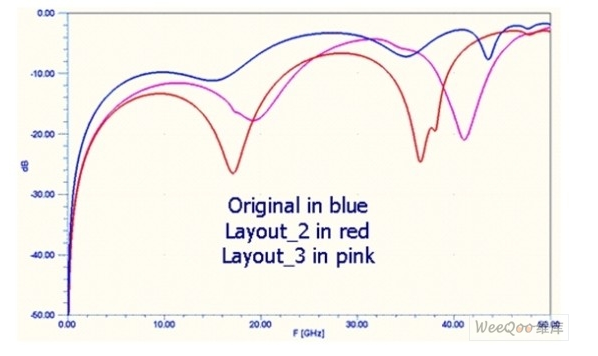

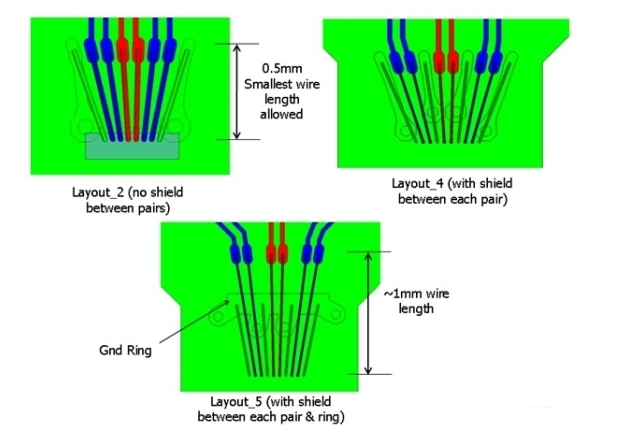

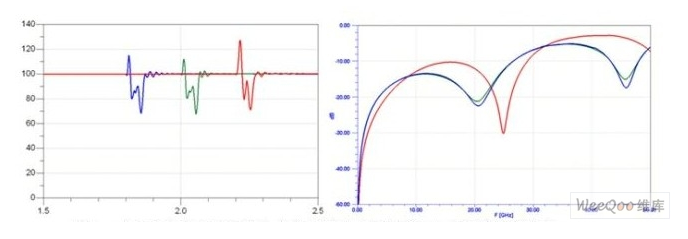

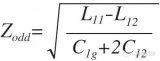

569 的阻抗不連續(xù)性和改善其回波損耗性能,以滿足10Gbps SerDes鍵合線封裝規(guī)范。 差分阻抗 一個(gè)典型的SerDes通道包含使用兩個(gè)單獨(dú)互連結(jié)構(gòu)的互補(bǔ)信號(hào)發(fā)射器和接收器之間的信息交換。兩個(gè)端點(diǎn)之間

2018-09-12 15:29:27

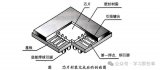

和基板介質(zhì)間還要具有較高的粘附性能。 BGA封裝技術(shù)通常采用引線鍵合、等離子清洗、模塑封裝、裝配焊料球、回流焊等工藝流程。引線鍵合PBGA的封裝工藝流程包括PBGA基板的制備和封裝

2023-04-11 15:52:37

文章目錄1、GPIO構(gòu)件封裝方法與規(guī)范2、利用構(gòu)件方法控制小燈閃爍3、工程文件組織框架與第一個(gè)C語言工程分析1、GPIO構(gòu)件封裝方法與規(guī)范構(gòu)件封裝建議、必要性與優(yōu)點(diǎn)建議按底層硬件操作功能封裝構(gòu)件

2021-11-08 06:58:21

樹脂),其組件符合工業(yè)規(guī)范要求。圖2 采用鍵合線的PQFN封裝圖3 采用銅片的PQFN封裝 例如,PQFN 5×6銅片封裝可在與現(xiàn)有SO-8相當(dāng)?shù)墓I(yè)標(biāo)準(zhǔn)尺寸中,實(shí)現(xiàn)優(yōu)于0.5mΩ的電阻,從裸片到

2018-09-12 15:14:20

本帖最后由 eehome 于 2013-1-5 10:11 編輯

connex金線鍵合機(jī)編程

2012-05-19 09:03:56

印刷電路板上的半導(dǎo)體封裝。在大多數(shù) BGA 中,半導(dǎo)體芯片和封裝基板是通過金線鍵合連接的。這些封裝基板和主板通過焊球連接。為了滿足這些連接所需的可靠性,封裝基板兩側(cè)的端子均鍍金。化學(xué)鍍金在更高

2021-07-09 10:29:30

請教:最近在書上講解電感時(shí)提到一個(gè)名詞——鍵合線,望大家能給出通俗詳細(xì)解釋

2014-06-22 13:21:45

WLP的命名上還存在分歧。CSP晶片級(jí)技術(shù)非常獨(dú)特,封裝內(nèi)部并沒有采用鍵合方式。封裝芯片的命名也存在分歧。常用名稱有:倒裝芯片(STMicroelectronics和Dalias

2018-08-27 15:45:31

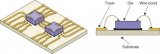

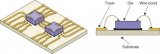

中芯片問的連接距離,持續(xù)縮小的封裝尺寸促使芯片三維重疊結(jié)構(gòu)的運(yùn)用,生產(chǎn)效率的提高需要把單個(gè)芯片的連接上藝擴(kuò)展到整個(gè)硅片卜進(jìn)行。硅片鍵合工藝把多層圓片上下相連同時(shí)形成電氣和機(jī)械連接以滿足這些要求。硅片

2018-11-23 17:03:35

本文將討論通過優(yōu)化封裝內(nèi)的阻抗不連續(xù)性和改善其回波損耗性能,以滿足10Gbps SerDes鍵合線封裝規(guī)范。

2021-04-25 07:42:13

論述了微電子封裝技術(shù)的發(fā)展歷程 發(fā)展現(xiàn)狀及發(fā)展趨勢 主要介紹了微電子封裝技術(shù)中的芯片級(jí)互聯(lián)技術(shù)與微電子裝聯(lián)技術(shù) 芯片級(jí)互聯(lián)技術(shù)包括引線鍵合技術(shù) 載帶自動(dòng)焊技術(shù) 倒裝芯片技術(shù) 倒裝芯片技術(shù)是目前

2013-12-24 16:55:06

有人又將其稱為圓片級(jí)-芯片尺寸封裝(WLP-CSP),以晶圓圓片為加工對象,在晶圓上封裝芯片。晶圓封裝中最關(guān)鍵的工藝為晶圓鍵合,即是通過化學(xué)或物理的方法將兩片晶圓結(jié)合在一起,以達(dá)到密封效果。如下

2021-02-23 16:35:18

滿足加速度大于30000g應(yīng)用場景。

完成大尺寸QFN封裝金線鍵合工藝開發(fā)。

其它信息請加qq了解。(qq:972186757)

2024-03-10 14:14:51

微電子封裝,首先我們要敘述一下三級(jí)封裝的概念。一般說來,微電子封裝分為三級(jí)。所謂一級(jí)封裝就是在半導(dǎo)體圓片裂片以后,將一個(gè)或多個(gè)集成電路芯片用適宜的封裝形式封裝起來,并使芯片的焊區(qū)與封裝的外引腳用引線鍵合

2023-12-11 01:02:56

芯片封裝鍵合技術(shù)各種微互連方式簡介微互連技術(shù)簡介定義:將芯片凸點(diǎn)電極與載帶的引線連接,經(jīng)過切斷、沖壓等工藝封裝而成。載帶:即帶狀載體,是指帶狀絕緣薄膜上載有由覆 銅箔經(jīng)蝕刻而形成的引線框架,而且芯片

2012-01-13 14:58:34

芯片(Die)必須與構(gòu)裝基板完成電路連接才能發(fā)揮既有的功能,焊線作業(yè)就是將芯片(Die)上的信號(hào)以金屬線鏈接到基板。iST宜特針對客戶在芯片打線封裝(Bonding, COB, Quick

2018-08-29 15:35:01

芯片封裝設(shè)計(jì)中的wire_bonding知識(shí)介紹Wire Bond/金線鍵合: 指在對芯片和基板間的膠粘劑處理以使其有更好的粘結(jié)性能后,用高純金線把芯片的接口和基板的接口鍵合 成分為金(純度為

2012-01-13 15:13:50

7系列系列中的SERDES是否有最小延遲規(guī)范?我想了解如果SERDES直接(最短路徑)連接到另一個(gè)SERDES以實(shí)現(xiàn)GTH收發(fā)器之間的最小延遲串行到串行連接,那將是什么樣的。

2020-07-22 13:45:34

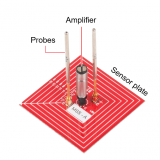

鍵合圖法在傳感器優(yōu)化配置的應(yīng)用

2009-01-09 17:47:47 20

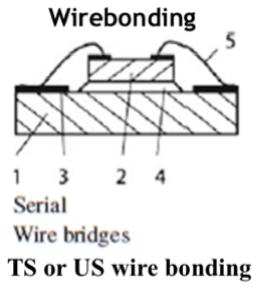

20 研究了芯片封裝中鍵合線的建模和模型參數(shù)提取方法。根據(jù)二端口網(wǎng)絡(luò)參量, 提出了單鍵合線的Π型等效電路并提取了模型中的R、L 和C 參量。最后,設(shè)計(jì)出一個(gè)簡單、低成本的測

2009-12-14 11:24:42 25

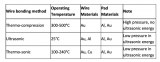

25 從超聲引線鍵合的機(jī)理入手,對大功率IGBT 模塊引線的材料和鍵合界面特性進(jìn)行了分析,探討了鍵合參數(shù)對鍵合強(qiáng)度的影響。最后介紹了幾種用于檢測鍵合點(diǎn)強(qiáng)度的方法,利用檢測結(jié)果

2011-10-26 16:31:33 69

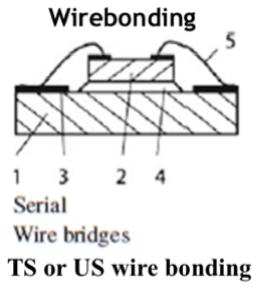

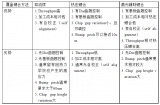

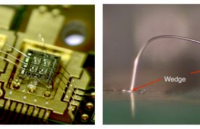

69 在回顧現(xiàn)行的引線鍵合技術(shù)之后,本文主要探討了集成電路封裝中引線鍵合技術(shù)的發(fā)展趨勢。球形焊接工藝比楔形焊接工藝具有更多的優(yōu)勢,因而獲得了廣泛使用。傳統(tǒng)的前向拱絲越來越

2011-10-26 17:13:56 86

86 目前IC器件在各個(gè)領(lǐng)域的應(yīng)用越來越廣泛,對封裝工藝的質(zhì)量及檢測技術(shù)提出了更高的要求,如何實(shí)現(xiàn)復(fù)雜封裝的工藝穩(wěn)定、質(zhì)量保證和協(xié)同控制變得越來越重要。目前國外對引線鍵合

2011-10-26 17:18:27 88

88 銅線具有優(yōu)良的機(jī)械、電、熱性能,用其代替金線可以縮小焊接間距、提高芯片頻率和可靠性。介紹了引線鍵合工藝的概念、基本形式和工藝參數(shù);針對銅絲易氧化的特性指出,焊接時(shí)

2011-12-27 17:11:49 64

64 對基于BCB的圓片級(jí)封裝工藝進(jìn)行了研究,該工藝代表了MEMS加速度計(jì)傳感器封裝的發(fā)展趨勢,是MEMS加速度計(jì)產(chǎn)業(yè)化的關(guān)鍵。選用3000系列BCB材料進(jìn)行MEMS傳感器的粘結(jié)鍵合工藝試驗(yàn),解決了

2012-09-21 17:14:24 0

0 已有研究表明,鍵合線老化脫落失效是影響絕緣柵雙極型晶體管( IGBT)可靠性的主要因素之一。以此為研究背景,首先根據(jù)IGBT模塊內(nèi)部鍵合線的結(jié)構(gòu)布局與物理特性,分析鍵合線等效電阻與關(guān)斷暫態(tài)波形的關(guān)系

2018-01-02 11:18:14 5

5 由于現(xiàn)在對功率半導(dǎo)體和功率模塊的節(jié)能有所要求,封裝成為產(chǎn)品整體性能的一個(gè)重要考慮因素。各種封裝普遍采用傳統(tǒng)的引線鍵合方式。這是一種成熟、經(jīng) 濟(jì)高效且靈活的工藝,目前已有經(jīng)過驗(yàn)證的裝配基礎(chǔ)設(shè)施。然而

2018-06-12 08:46:00 4631

4631 同時(shí)得到減小。銅線在焊接后能夠形成比金線更穩(wěn)定、剛性更好。? ? ?熟悉半導(dǎo)體封裝的朋友都知道鍵合銅絲這種材料,現(xiàn)在很多大陸半導(dǎo)體公司用的大都是進(jìn)口的鍵合銅絲。但是進(jìn)口的產(chǎn)品就真的要好過國內(nèi)嗎?1998

2018-04-24 14:52:55 2145

2145 ,進(jìn)一步優(yōu)化組織結(jié)構(gòu),保證得到合適的機(jī)械性能,以滿足不同的需求1,能夠真正應(yīng)用于集成電路等高級(jí)封裝中,部分或全部取代鍵合金絲。鍵合銀絲已廣泛應(yīng)用于LED封裝,IC封閉領(lǐng)域,可使成本下降。它的散熱

2018-04-26 17:28:36 2713

2713 如果設(shè)計(jì)不合適,一個(gè)通道中的這些多重轉(zhuǎn)換將會(huì)影響信號(hào)完整性性能。在10Gbps及以上,通過最大限度地減少阻抗不連續(xù)性,得到適合的互連設(shè)計(jì)已成為提高系統(tǒng)性能的一個(gè)重要的考慮因素。由于封裝內(nèi)有許多不連續(xù)區(qū),該收發(fā)器封裝在提高回波損耗性能方面存在一個(gè)重要瓶頸。

2020-11-12 15:31:05 3909

3909

為解決銅絲硬度大帶來的鍵合難度,半導(dǎo)體封裝企業(yè)通常選擇應(yīng)用超聲工藝或鍵合壓力工藝提升鍵合效果,這也導(dǎo)致焊接期間需要耗費(fèi)更多的時(shí)間完成鍵合工作。

2022-12-15 15:44:46 4437

4437 本試驗(yàn)提供了確定芯片鍵合面上的金絲球鍵合點(diǎn)的鍵合強(qiáng)度測定方法,可在元器件封裝前或封裝后進(jìn)行測定。

2022-12-20 10:17:04 4477

4477 ,不斷創(chuàng)造新的技術(shù)極限。傳統(tǒng)的金線、鋁線鍵合與封裝技術(shù)的要求不相匹配。銅線鍵合在成本和材料特性方面有很多優(yōu)于金、鋁的地方,但是銅線鍵合技術(shù)還面臨一些挑戰(zhàn)和問題。如果這些問題能夠得到很好的解決,銅線鍵合技術(shù)

2023-02-07 11:58:35 3219

3219 金價(jià)不斷上漲增加了半導(dǎo)體制造業(yè)的成本壓力,因此業(yè)界一直在改善銅線的性能上努力,希望最終能夠用成本更低但鍵合性能相當(dāng)甚至更好的銅線來代替金線鍵合。

2023-02-13 09:21:41 4688

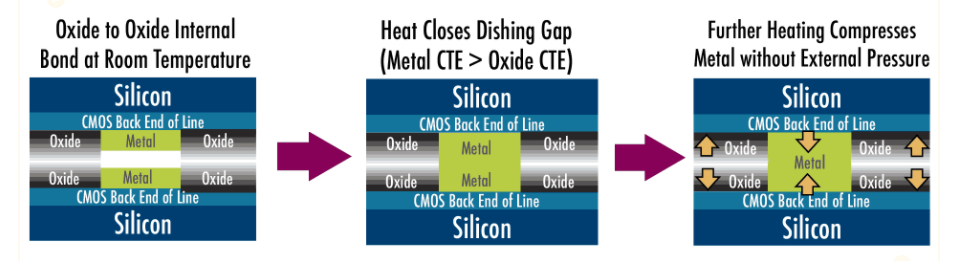

4688 引線鍵合是一種芯片到封裝的互連技術(shù),其中在芯片上的每個(gè) I/O 焊盤與其相關(guān)的封裝引腳之間連接一根細(xì)金屬線。細(xì)線(通常為 25 μm 厚的 Au 線)鍵合在 IC 焊盤和引線框或封裝和基板焊盤之間。引線鍵合是電子封裝中最重要和最關(guān)鍵的制造工藝之一。引線鍵合的優(yōu)點(diǎn)是:

2023-02-17 09:59:47 2630

2630

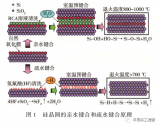

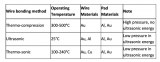

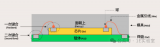

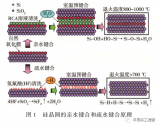

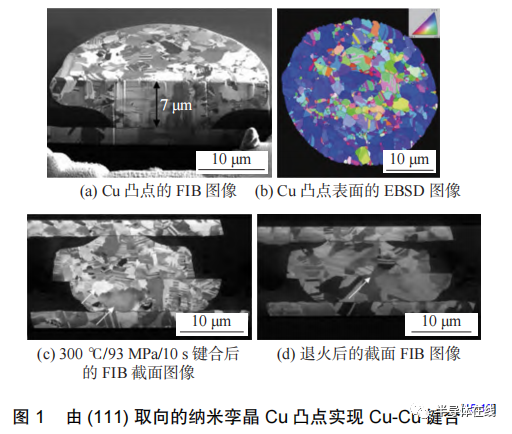

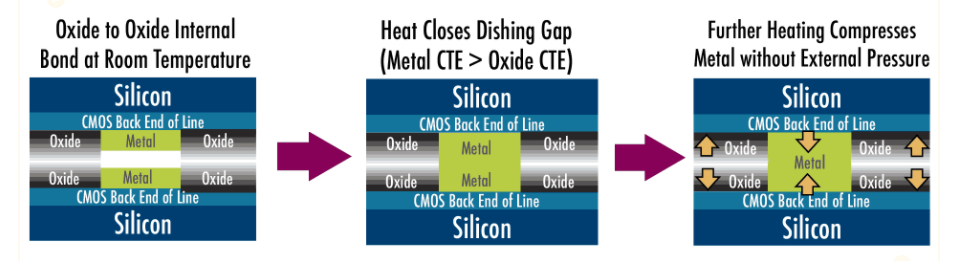

熱壓鍵合工藝的基本原理與傳統(tǒng)擴(kuò)散焊工藝相同,即上下芯片的Cu 凸點(diǎn)對中后直接接觸,其實(shí)現(xiàn)原子擴(kuò)散鍵合的主要影響參數(shù)是溫度、壓力、時(shí)間. 由于電鍍后的Cu 凸點(diǎn)表面粗糙并存在一定的高度差。

2023-05-05 11:30:17 5150

5150

將半導(dǎo)體芯片壓焊區(qū)與框架引腳之間用鋁線連接起來的封裝工藝技術(shù)!季豐電子所擁有的ASM綁定焊線機(jī)AB550為桌面式焊線機(jī),其為全自動(dòng)超聲波焊線機(jī),應(yīng)用于細(xì)鋁線的引線鍵合,主要應(yīng)用于COB及PCB領(lǐng)域。

2023-05-08 12:38:51 6214

6214

微電子封裝用主流鍵合銅絲半導(dǎo)體封裝技術(shù)

2023-06-06 10:25:48 1130

1130

晶圓直接鍵合技術(shù)可以使經(jīng)過拋光的半導(dǎo)體晶圓,在不使用粘結(jié)劑的情況下結(jié)合在一起,該技術(shù)在微電子制造、微機(jī)電系統(tǒng)封裝、多功能芯片集成以及其他新興領(lǐng)域具有廣泛的應(yīng)用。對于一些溫度敏感器件或者熱膨脹系數(shù)差異

2023-06-14 09:46:27 3533

3533

Cu-Cu 低溫鍵合技術(shù)是先進(jìn)封裝的核心技術(shù),相較于目前主流應(yīng)用的 Sn 基軟釬焊工藝,其互連節(jié)距更窄、導(dǎo) 電導(dǎo)熱能力更強(qiáng)、可靠性更優(yōu). 文中對應(yīng)用于先進(jìn)封裝領(lǐng)域的 Cu-Cu 低溫鍵合技術(shù)進(jìn)行了

2023-06-20 10:58:48 4693

4693

本文通過對典型案例的介紹,分析了鍵合工藝不當(dāng),以及器件封裝因素對器件鍵合失效造成的影響。通過對鍵合工藝參數(shù)以及封裝環(huán)境因素影響的分析,以及對各種失效模式總結(jié),闡述了鍵合工藝不當(dāng)及封裝不良,造成鍵合本質(zhì)失效的機(jī)理;并提出了控制有缺陷器件裝機(jī)使用的措施。

2023-07-26 11:23:15 3525

3525 介紹了封裝鍵合過程中應(yīng)用的銀合金鍵合線與鋁墊之間形成的共金化合物(IMC),提出了侵蝕對IMC的影響,由于銀合金線IMC不能通過物理方法確認(rèn),需通過軟件測量計(jì)算和化學(xué)腐蝕試驗(yàn)得到IMC覆蓋面積。詳述

2023-10-20 12:30:02 3369

3369

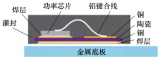

功率芯片通過封裝實(shí)現(xiàn)與外部電路的連接,其性能的發(fā)揮則依賴著封裝的支持,在大功率場合下通常功率芯片會(huì)被封裝為功率模塊進(jìn)行使用。芯片互連(interconnection)指芯片上表面的電氣連接,在傳統(tǒng)模塊中一般為鋁鍵合線。

2023-10-24 10:52:09 5797

5797

引線鍵合是在硅芯片上的 IC 與其封裝之間創(chuàng)建互連的常用方法,其中將細(xì)線從器件上的鍵合焊盤連接到封裝上的相應(yīng)焊盤(即引線)。此連接建立了從芯片內(nèi)部電路到連接到印刷電路板 (PCB) 的外部引腳的電氣路徑。

2023-10-24 11:32:13 3691

3691

要了解混合鍵合,需要了解先進(jìn)封裝行業(yè)的簡要?dú)v史。當(dāng)電子封裝行業(yè)發(fā)展到三維封裝時(shí),微凸塊通過使用芯片上的小銅凸塊作為晶圓級(jí)封裝的一種形式,在芯片之間提供垂直互連。凸塊的尺寸范圍很廣,從 40 μm 間距到最終縮小到 20 μm 或 10 μm 間距。

2023-11-22 16:57:42 6764

6764

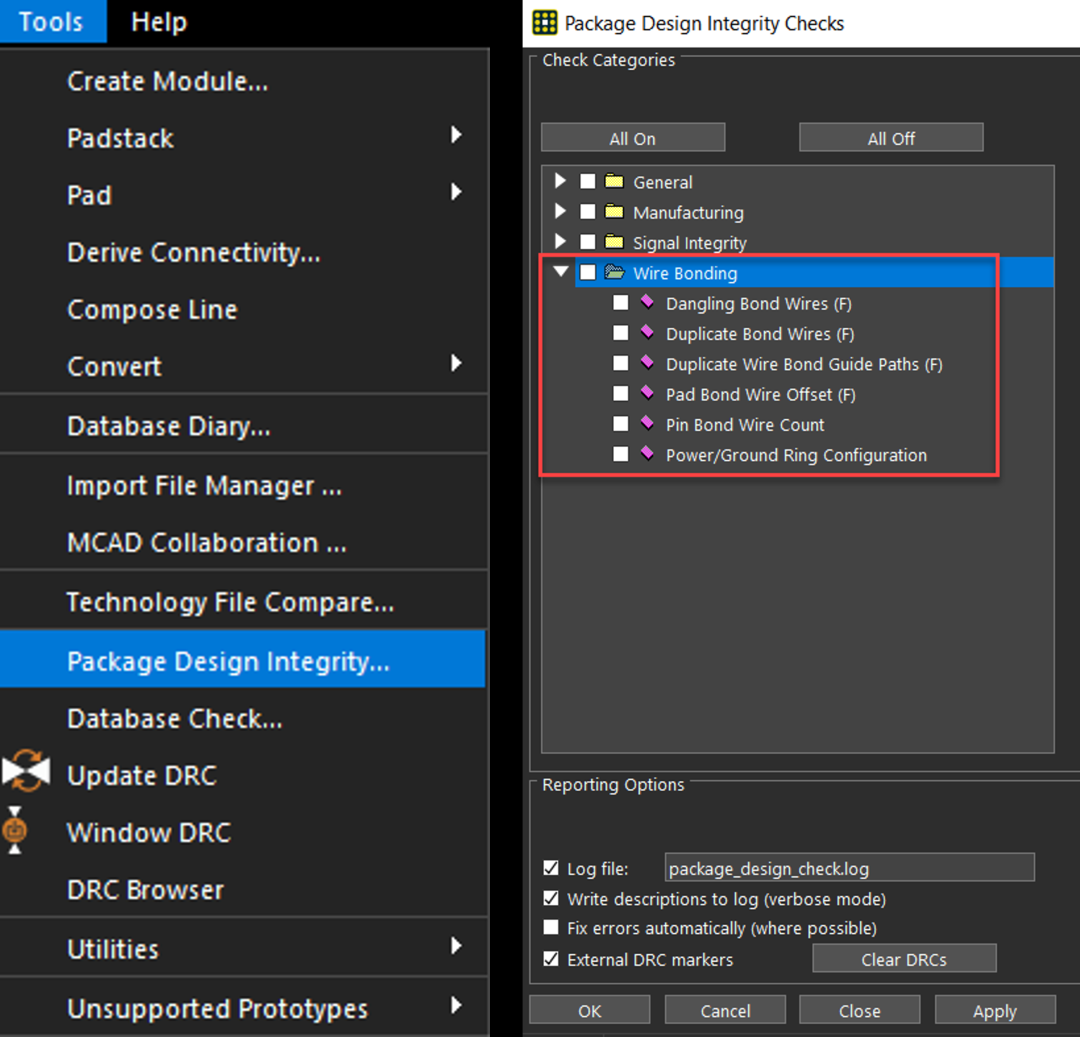

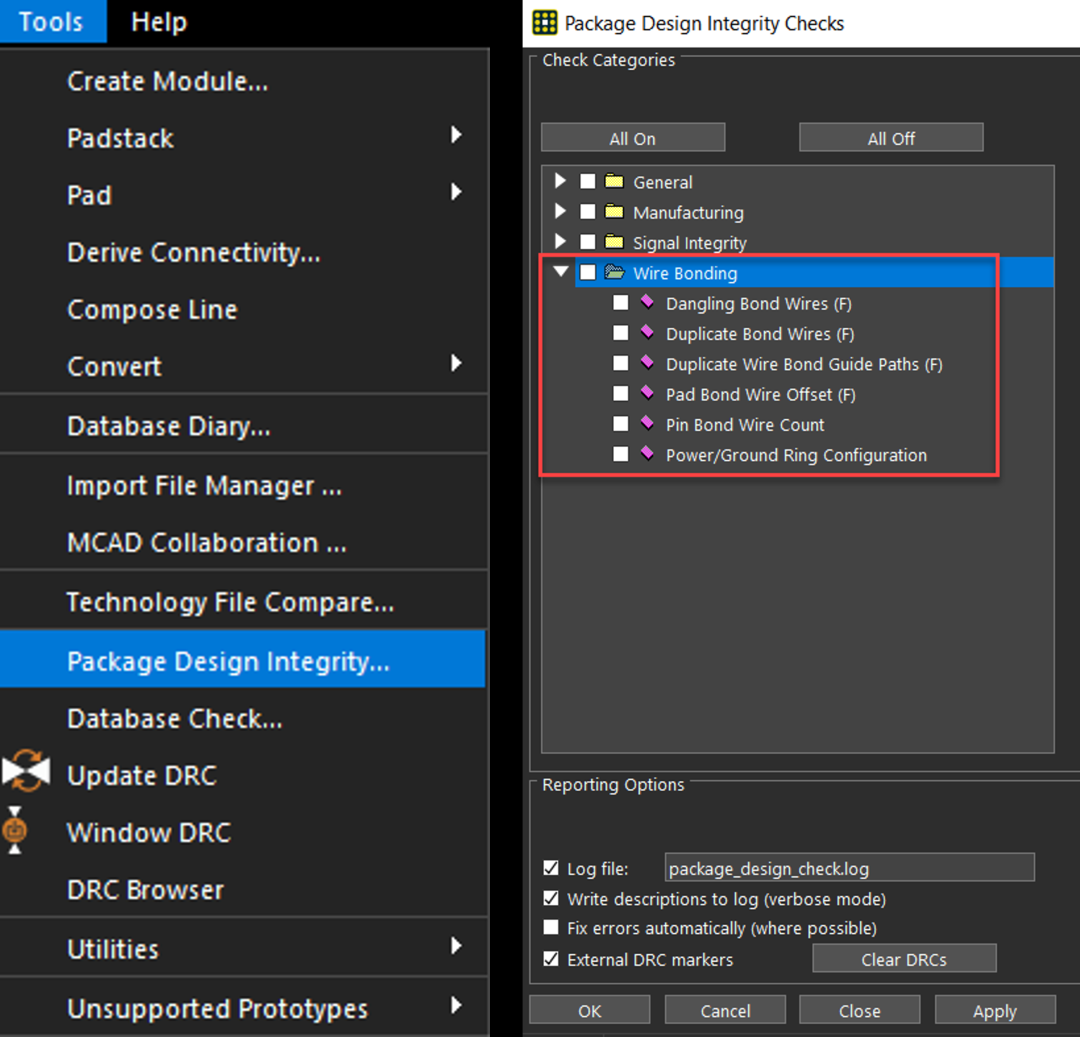

如何在IC 封裝中分析并解決與具體引線鍵合相關(guān)的設(shè)計(jì)問題?

2023-11-28 17:08:46 1599

1599

本文將幫助您更好地理解合封芯片、芯片合封和SiP系統(tǒng)級(jí)封裝這三種不同的技術(shù)。合封芯片是一種將多個(gè)芯片或不同功能的電子模塊封裝在一起的定制化芯片,以實(shí)現(xiàn)更復(fù)雜、更高效的任務(wù)。合封芯片可定制組成方式包括CoC封裝技術(shù)、SiP封裝技術(shù)等。

2023-11-23 16:03:42 2538

2538 自從IBM于20世紀(jì)60年代開發(fā)出可控塌陷芯片連接(Controlled Collapse Chip Connect,C4)技術(shù),或稱倒裝芯片技術(shù),凸點(diǎn)鍵合在微電子封裝領(lǐng)域特別是芯片與封裝基板的鍵合

2023-12-05 09:40:00 3259

3259

共讀好書 王帥奇 鄒貴生 劉磊 (清華大學(xué)) 摘要: Cu-Cu 低溫鍵合技術(shù)是先進(jìn)封裝的核心技術(shù),相較于目前主流應(yīng)用的 Sn 基軟釬焊工藝,其互連節(jié)距更窄、導(dǎo)電導(dǎo)熱能力更強(qiáng)、可靠性更優(yōu). 文中對應(yīng)

2024-03-25 08:39:56 2316

2316

隨著科技的飛速發(fā)展,集成電路已成為現(xiàn)代電子設(shè)備中不可或缺的組件。而在集成電路的生產(chǎn)過程中,封裝工藝是至關(guān)重要的一環(huán),它直接關(guān)系到集成電路的性能和可靠性。鋁線鍵合技術(shù)作為一種重要的封裝工藝,被廣泛應(yīng)用于集成電路的制造中。本文將對集成電路封裝工藝中的鋁線鍵合技術(shù)進(jìn)行詳細(xì)介紹。

2024-04-09 09:53:55 2916

2916

引線鍵合是微電子封裝領(lǐng)域中的一項(xiàng)關(guān)鍵技術(shù),它負(fù)責(zé)實(shí)現(xiàn)芯片與封裝基板或其他芯片之間的電氣連接。隨著集成電路技術(shù)的不斷進(jìn)步,引線鍵合技術(shù)也在不斷發(fā)展,以適應(yīng)更高性能、更小尺寸和更低成本的需求。本文將詳細(xì)介紹引線鍵合技術(shù)的發(fā)展歷程、現(xiàn)狀以及未來趨勢。

2024-04-28 10:14:33 2444

2444

紅外探測器在現(xiàn)代科技領(lǐng)域中扮演著舉足輕重的角色,廣泛應(yīng)用于溫度檢測、環(huán)境監(jiān)控、醫(yī)學(xué)研究等領(lǐng)域。為了提升紅外探測器的性能和可靠性,其封裝過程中的鍵合工藝尤為關(guān)鍵。本文旨在深入探討紅外探測器芯片的高可靠性鍵合工藝,以期為相關(guān)領(lǐng)域的實(shí)踐提供有益的參考。

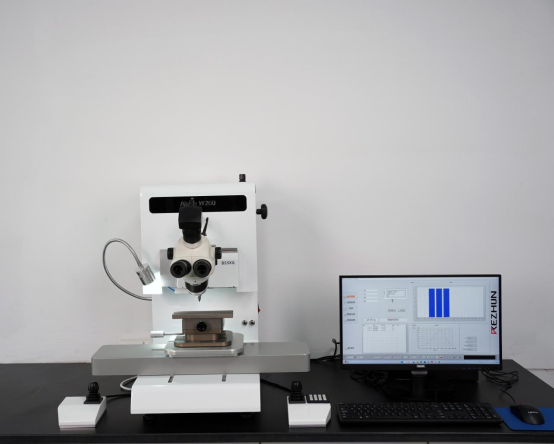

2024-05-23 09:38:20 1924

1924

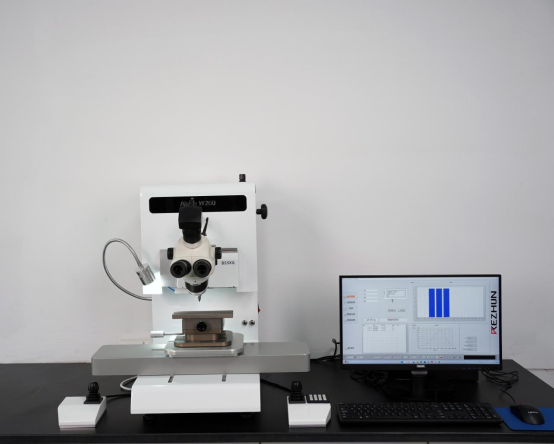

金絲鍵合強(qiáng)度測試儀是測量引線鍵合強(qiáng)度,評(píng)估鍵合強(qiáng)度分布或測定鍵合強(qiáng)度是否符合有關(guān)的訂購文件的要求。鍵合強(qiáng)度試驗(yàn)機(jī)可應(yīng)用于采用低溫焊、熱壓焊、超聲焊或有關(guān)技術(shù)鍵合的、具有內(nèi)引線的器件封裝內(nèi)部的引線

2024-07-06 11:18:59 2227

2227

在微電子封裝領(lǐng)域,金絲鍵合(Wire Bonding)工藝作為一種關(guān)鍵的電氣互連技術(shù),扮演著至關(guān)重要的角色。該工藝通過細(xì)金屬線(主要是金絲)將芯片上的焊點(diǎn)與封裝基板或另一芯片上的對應(yīng)焊點(diǎn)連接起來

2024-08-16 10:50:14 4901

4901

在半導(dǎo)體制造領(lǐng)域,技術(shù)的每一次革新都標(biāo)志著行業(yè)邁向新的里程碑。近年來,隨著芯片性能需求的不斷提升,傳統(tǒng)的二維封裝技術(shù)已難以滿足日益增長的數(shù)據(jù)處理速度和功耗控制要求。在此背景下,混合鍵合(Hybrid

2024-08-26 10:41:54 2476

2476

DieBound芯片鍵合,是在封裝基板上安裝芯片的工藝方法。本文詳細(xì)介紹一下幾種主要的芯片鍵合的方法和工藝。什么是芯片鍵合在半導(dǎo)體工藝中,“鍵合”是指將晶圓芯片連接到基板上。連接可分為兩種類型,即

2024-09-20 08:04:29 2714

2714

引線鍵合廣泛應(yīng)用于電子設(shè)備、半導(dǎo)體行業(yè)和微電子領(lǐng)域。它實(shí)現(xiàn)了集成電路(IC)中芯片與其他電子元件(如晶體管和電阻)之間的互連。引線鍵合通過在芯片的焊盤與封裝基板或其他芯片上的對應(yīng)焊盤之間建立電氣連接

2024-10-16 09:23:52 2457

2457

取代了傳統(tǒng)的粗鋁絲鍵合,尤其在小型貼片封裝SOP和PDFN中得到了批量性應(yīng)用。然而,鋁帶鍵合工藝在推廣應(yīng)用過程中,鍵合點(diǎn)根部損傷問題日益凸顯,成為制約其進(jìn)一步發(fā)展的

2024-10-16 10:16:03 2154

2154

要求,傳統(tǒng)互聯(lián)技術(shù)如引線鍵合、倒裝芯片鍵合和硅通孔(TSV)鍵合等,正逐步顯露其局限。在這種背景下,混合鍵合技術(shù)以其革命性的互聯(lián)潛力,正成為行業(yè)的新寵。

2024-10-18 17:54:54 1775

1775

微電子鍵合線有多種純材料和合金材料。除了圓線外,扁帶材料還可用于射頻和微波電路等特殊應(yīng)用中。圓線是迄今為止最常見的,直徑小至 5 μm 的細(xì)圓線已商業(yè)化生產(chǎn)。直徑達(dá) 500 μm 的大直徑圓線用于電力應(yīng)用。扁帶線的寬度范圍為 50 μm 至 1200 μm,并且有各種厚度。

2024-10-27 16:37:03 4849

4849

隨著半導(dǎo)體技術(shù)的飛速發(fā)展,芯片的性能需求不斷提升,傳統(tǒng)的二維封裝技術(shù)已難以滿足日益增長的數(shù)據(jù)處理速度和功耗控制要求。在此背景下,混合鍵合(Hybrid Bonding)技術(shù)應(yīng)運(yùn)而生,并迅速成為三維

2024-11-13 13:01:32 3341

3341

線鍵合與倒裝芯片作為封裝技術(shù)中兩大重要的連接技術(shù),各自承載著不同的使命與優(yōu)勢。那么,芯片倒裝(Flip Chip)相對于傳統(tǒng)線鍵合(Wire Bonding)究竟有哪些優(yōu)勢呢?倒裝芯片在封裝技術(shù)演進(jìn)

2024-11-21 10:05:15 2312

2312

談一談先進(jìn)封裝中的互連工藝,包括凸塊、RDL、TSV、混合鍵合,有哪些新進(jìn)展?可以說,互連工藝是先進(jìn)封裝的關(guān)鍵技術(shù)之一。在市場需求的推動(dòng)下,傳統(tǒng)封裝不斷創(chuàng)新、演變,出現(xiàn)了各種新型的封裝結(jié)構(gòu)。 下游

2024-11-21 10:14:40 4681

4681

在微電子封裝領(lǐng)域,鍵合絲作為芯片與封裝引線之間的連接材料,扮演著至關(guān)重要的角色。隨著科技的進(jìn)步和電子產(chǎn)品向高密度、高速度和小型化方向發(fā)展,鍵合絲的性能和材料選擇成為影響封裝質(zhì)量的關(guān)鍵因素之一。近年來

2024-11-25 10:42:08 1398

1398

中,引線鍵合技術(shù)是實(shí)現(xiàn)芯片與外部電路連接的重要手段,而鍵合材料的選擇和鍵合工藝參數(shù)的優(yōu)化則是確保鍵合質(zhì)量的關(guān)鍵因素。 銅線作為一種新型的鍵合材料,相較于傳統(tǒng)的鋁線和金線,展現(xiàn)出了更為優(yōu)異的導(dǎo)電和導(dǎo)熱性能。這使得銅線在

2025-02-08 10:59:15 1055

1055

微電子封裝中的引線鍵合技術(shù)引線鍵合技術(shù)在微電子封裝領(lǐng)域扮演著至關(guān)重要的角色,它通過金屬線將半導(dǎo)體芯片與外部電路相連,實(shí)現(xiàn)電氣互連和信息傳遞。在理想條件下,金屬引線與基板之間的連接可以達(dá)到原子級(jí)別的鍵

2024-12-24 11:32:04 2832

2832

引線鍵合是一種將裸芯片的焊墊與封裝框架的引腳或基板上的金屬布線焊區(qū)通過金屬引線(如金線、銅線、鋁線等)進(jìn)行連接的工藝。 這一步驟確保了芯片與外部電路的有效電氣連接和信號(hào)傳輸。 鍵合前的等離子體清洗 在引線鍵合之前,通常需

2025-01-02 10:18:01 2679

2679

隨著半導(dǎo)體技術(shù)的飛速發(fā)展,封裝技術(shù)作為連接芯片與外界環(huán)境的橋梁,其重要性日益凸顯。在眾多封裝技術(shù)中,TCB(Thermal Compression Bonding,熱壓鍵合)技術(shù)以其獨(dú)特的優(yōu)勢,在

2025-01-04 10:53:10 6366

6366

線鍵合(WireBonding)線鍵合是一種使用細(xì)金屬線,利用熱、壓力、超聲波能量為使金屬引線與基板焊盤緊密焊合,實(shí)現(xiàn)芯片與基板間的電氣互連和芯片間的信息互通。在理想控制條件下,引線和基板間會(huì)發(fā)

2025-01-06 12:24:10 1966

1966

芯片封裝是半導(dǎo)體制造的關(guān)鍵環(huán)節(jié),承擔(dān)著為芯片提供物理保護(hù)、電氣互連和散熱的功能,這其中的鍵合技術(shù)就是將裸芯片與外部材料連接起來的方法。鍵合可以通俗的理解為接合,對應(yīng)的英語表達(dá)是Bonding,音譯

2025-03-22 09:45:31 5449

5449

芯片封裝是半導(dǎo)體制造的關(guān)鍵環(huán)節(jié),承擔(dān)著為芯片提供物理保護(hù)、電氣互連和散熱的功能,這其中的鍵合技術(shù)(Bonding)就是將晶圓芯片固定于基板上。

2025-04-10 10:15:38 2841

2841

芯片封裝作為半導(dǎo)體制造的核心環(huán)節(jié),承擔(dān)著物理保護(hù)、電氣互連和散熱等關(guān)鍵功能。其中,鍵合技術(shù)作為連接裸芯片與外部材料的橋梁,直接影響芯片的性能與可靠性。當(dāng)前,芯片封裝領(lǐng)域存在引線鍵合、倒裝芯片、載帶

2025-04-11 14:02:25 2627

2627

打線鍵合就是將芯片上的電信號(hào)從芯片內(nèi)部“引出來”的關(guān)鍵步驟。我們要用極細(xì)的金屬線(多為金線、鋁線或銅線)將芯片的焊盤(bond pad)和支架(如引線框架或基板)之間做電連接。

2025-06-03 18:25:49 1870

1870 引線鍵合的定義--什么是引線鍵合?引線鍵合(WireBonding)是微電子封裝中的關(guān)鍵工藝,通過金屬細(xì)絲(如金線、鋁線或銅線)將芯片焊盤與外部基板、引線框架或其他芯片的焊區(qū)連接,實(shí)現(xiàn)電氣互連。其

2025-06-06 10:11:41 1010

1010

在半導(dǎo)體封裝工藝中,金線鍵合(Gold Wire Bonding)和銅線鍵合(Copper Wire Bonding)是芯片與封裝基板電氣互連的關(guān)鍵技術(shù)。鍵合強(qiáng)度直接影響器件的機(jī)械穩(wěn)定性和長期可靠性

2025-06-12 10:14:34 1455

1455

電子發(fā)燒友網(wǎng)為你提供()硅限幅器二極管、封裝和可鍵合芯片相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有硅限幅器二極管、封裝和可鍵合芯片的引腳圖、接線圖、封裝手冊、中文資料、英文資料,硅限幅器二極管、封裝和可鍵合芯片真值表,硅限幅器二極管、封裝和可鍵合芯片管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-07-09 18:32:29

電子發(fā)燒友網(wǎng)為你提供()Silicon PIN 二極管、封裝和可鍵合芯片相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有Silicon PIN 二極管、封裝和可鍵合芯片的引腳圖、接線圖、封裝手冊、中文資料、英文資料

2025-07-14 18:32:06

電子發(fā)燒友網(wǎng)為你提供()硅肖特基勢壘二極管:封裝、可鍵合芯片和光束引線相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有硅肖特基勢壘二極管:封裝、可鍵合芯片和光束引線的引腳圖、接線圖、封裝手冊、中文資料、英文資料,硅

2025-07-15 18:32:18

一、引言 在 IGBT 模塊的可靠性研究中,鍵合線失效是導(dǎo)致器件性能退化的重要因素。研究發(fā)現(xiàn),芯片表面平整度與鍵合線連接可靠性存在緊密關(guān)聯(lián)。當(dāng)芯片表面平整度不佳時(shí),鍵合線與芯片連接部位易出現(xiàn)應(yīng)力集中

2025-09-02 10:37:35 1788

1788

一、引言 在 IGBT 模塊散熱系統(tǒng)中,封裝底部與散熱器的貼合狀態(tài)直接影響熱傳導(dǎo)效率。研究發(fā)現(xiàn),貼合面平整度差不僅導(dǎo)致散熱性能下降,還會(huì)通過力學(xué)傳遞路徑引發(fā)鍵合線與芯片連接部位的應(yīng)力集中,最終造成鍵

2025-09-07 16:54:00 1684

1684

在先進(jìn)封裝中, Hybrid bonding( 混合鍵合)不僅可以增加I/O密度,提高信號(hào)完整性,還可以實(shí)現(xiàn)低功耗、高帶寬的異構(gòu)集成。它是主要3D封裝平臺(tái)(如臺(tái)積電的SoIC、三星的X-Cube

2025-09-17 16:05:36 1469

1469

在半導(dǎo)體封裝工藝中,芯片鍵合(Die Bonding)是指將晶圓芯片固定到封裝基板上的關(guān)鍵步驟。鍵合工藝可分為傳統(tǒng)方法和先進(jìn)方法:傳統(tǒng)方法包括芯片鍵合(Die Bonding)和引線鍵合(Wire

2025-10-21 17:36:16 2060

2060

如有雷同或是不當(dāng)之處,還請大家海涵。當(dāng)前在各網(wǎng)絡(luò)平臺(tái)上均以此昵稱為ID跟大家一起交流學(xué)習(xí)! 半導(dǎo)體引線鍵合(Wire Bonding)是應(yīng)用最廣泛的鍵合技術(shù),也是半導(dǎo)體封裝工藝中的一個(gè)重要環(huán)節(jié),主要利用金、鋁、銅、錫等金屬導(dǎo)線建

2025-12-01 17:44:47 2057

2057

如有雷同或是不當(dāng)之處,還請大家海涵。當(dāng)前在各網(wǎng)絡(luò)平臺(tái)上均以此昵稱為ID跟大家一起交流學(xué)習(xí)! 在半導(dǎo)體封裝領(lǐng)域,隨著電子設(shè)備向更高性能、更小尺寸和更輕重量的方向發(fā)展,封裝技術(shù)的重要性日益凸顯。金線球焊鍵合工藝,作為連

2025-12-07 20:58:27 779

779

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論