摘要:本文講述了引線框架的主要特性以及引線框架對封裝的影響,提出了一些改進方法。

關鍵詞:引線框架;塑封;IC

中圖分類號:305.94 文獻標識碼

1引言

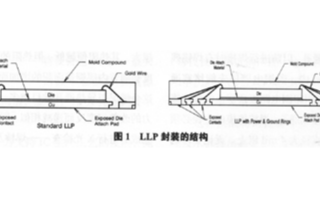

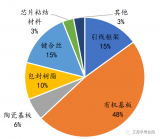

近年來,隨著集成電路技術的進步,集成電路封裝也得到了很大的發展。國外廠商紛紛來大陸投資設廠,使國內的封裝業變得更為興旺,這樣,作為電子信9、制造業的基礎--電子信息材料越來越受到政府各部門、各地區和企業界的關注和重視。集成電路塑封中使用的引線框架是集成電路封裝的一種主要結構材料。它在電路中主要起承載IC芯片的作用,同時起連接芯片與外部線路板電信號的作用,以及安裝固定的機械作用等(見圖1)。

集成電路引線框架一般采用銅材(Cu)或鐵鎳合金(42#Fe-Ni),考慮到電氣、散熱與塑封匹配以及成本等方面的因素,目前主要使用銅材,特別是DIP和SIP插入式封裝以及SOIC、QFP、PLCC等適合SMT技術要求的封裝大多數都采用銅材。

2引線框架的主要性能

根據引線框架在封裝體中的作用,要求引線框架具備以下性能:

2.1 良好的導電性能

由圖1可以看出,引線框架在塑封體中起到芯片和外面的連接作用,因此要求它要有良好的導電性。另外,在電路設計時,有時地線通過芯片的隔離墻連到引線框架的基座,這就更要求它有良好的導電性。如圖2所示。

有的集成電路的工作頻率較高,為減少電容和電感等寄生效應,對引線框架的導電性能要求就更高,導電性越高,引線框架產生的阻抗就越小。

一般而言,銅材的導電性比鐵鎳材料的導電性要好。如:Fe58%-Ni42%的鐵鎳合金,其電導率為3.0%IACS;摻0.1%Zr的銅材料,其電導率為90%IACS;摻2.3%Fe、0.03%P、0.1%Zn的銅材料,其電導率為65%IACS,因此從上面可以看出,銅材的電導率較好,并且根據摻雜不同,其電導率有較大的差別

2.2 良好的導熱性

集成電路在使用時,總要產生熱量,尤其是功耗較大的電路,產生的熱量就更大,因此在工作時要求主要結構材料引線框架能有很好的導熱性,否則在工作狀態會由于熱量不能及時散去而"燒壞"芯片。導熱性一般可由兩方面解決,一是增加引線框架基材的厚度,二是選用較大導熱系數的金屬材料做引線框架。

Fe58%-Ni42%的鐵鎳合金導熱系數為15.89W/cm~℃;摻0.1%Zr的銅材料,其導熱系數為359.8W/cm~℃;摻0.1%Fe、0.058%P的銅材料,其導熱系數為435.14W/cm℃。可見銅材料的導熱系數最好,而且根據摻雜的不同,其導熱系數不一樣。

2.3良好的熱匹配(即熱膨脹)

材料受熱產生膨脹,在封裝體中,引線框架和塑封體的塑封樹脂相接觸,也和芯片間接接觸,因此要求它們有一個良好的熱匹配。Fe58%-Ni42%的鐵鎳合金,其線膨脹系數為43×10-7/℃,一般的銅材料引線框架,其線膨脹系數為(160~180)×10-7/℃,由此可見,鐵鎳材料的膨脹系數較小,銅材料的膨脹系數較大。銅質引線框架的膨脹系數和塑封樹脂的膨脹系數(200×10''7/~C左右)相近,但是和硅芯片的膨脹系數相差較大,硅的膨脹系數為26×l0-7/℃。不過,現在采用的樹脂導電膠作為粘片材料,它們的柔韌性強,足以吸收芯片和銅材之間所出現的應力形變。如果是共晶裝片,那么就不宜采用線膨脹系數大的鋼材做引線框架了。

2.4良好的強度

引線框架無論是在封裝過程中,還是在隨后的測試及客戶在插到印刷線路板的使用過程中,都要求其有良好的抗拉強度。Fe58%-Ni42%的鐵鎳合金的抗拉強度為0.64GPa,而銅材料合金的抗拉強度一般為0.5GPa以下,因此銅材料的抗拉強度要稍差一些,同樣它可以通過摻雜來改善抗拉強度。作為引線框架,一般要求抗拉強度至少應達到441MPa,延伸率大于5%。

2.5 耐熱性和耐氧化性

耐熱性用軟化溫度進行衡量。軟化溫度是將材料加熱5分鐘后,其硬度變化到最初始硬度的80%的加熱溫度。通常軟化溫度在400℃以上便可以使用。材料的耐氧化性對產品的可靠性有很大的影響,要求由于加熱而生成的氧化膜盡可能少。

2.6具有一定的耐腐蝕性

引線框架不應發生應力腐蝕裂紋,在一般潮濕氣候下不應腐蝕而產生斷腿現象。

3封裝工藝對引線框架的要求

引線框架作為主要結構材料,從裝片開始進人生產過程一直到結束,幾乎貫穿整個封裝過程,它的設計是否合理、質量控制得好與壞,將影響到封裝的幾乎所有的重要工序,如裝片、鍵合、塑封、電鍍、切筋等,因此根據封裝工藝,對引線框架具有以下的要求:

3.1一定的硬度

引線框架在使用過程中,要重復在不同工序的設備的導軌中傳送,如果引線框架的硬度不好,極易變形,引起產品報廢,甚至損壞設備,現在一般選用1H左右的硬度。硬度Hv應大于130,國外要求引線腳的反復彎曲次數大于等于3次,以后要求會更高。

3.2引線框架的步進特性

一條引線框架上可以裝5只~20只電路芯片,甚至更多,因此要求引線框架的定位孔的孔徑大小和塑封模及切筋模頂針剛好匹配。其次還要求定位孔的孔徑精度和定位孔之間的累積誤差都不能太大,否則在設備傳輸和模具上操作時,會產生不到位和壓出金屬飛邊等。

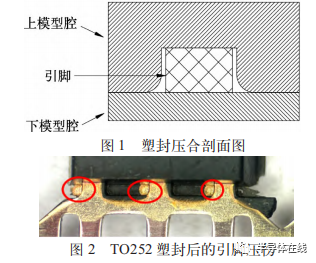

3.3 引線框架的小島設計要和芯片匹配- 引線框架的小島要和芯片匹配,同一種封裝形式有不同的IC芯片尺寸,因此同一種引線框架也應有很多種小島尺寸供選擇。同時,引線本身也有內引線腳間距以及內引線腳和小島之間間距的匹配要求,如圖3所示:

3.4 外引線腳的鎖定和潮氣隔離結構

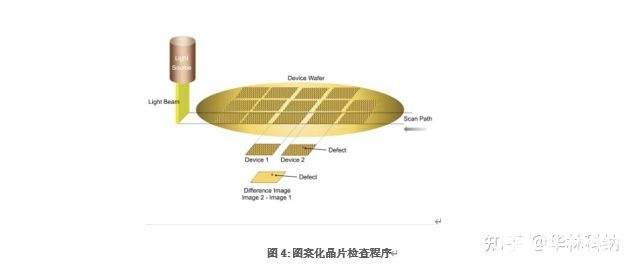

引線框架和塑封體之間是機械粘接的,因此在引線框架上應有一定的凸起或孔洞將引線框架的腳鎖定在固化的塑封體中,這樣能很好地阻止在使用過程中的潮氣進入到塑封體體內。如圖4所示。

3.5應力釋放

引線框架產生的兩類應力可以通過引線框架設計減少。

最嚴重的應力之-是由于塑封與金屬之間內在的熱膨脹系數失配引起的。嚴重的情況可能發生在熱沖擊試驗時,封裝體會彎曲變形到足夠的程度而損害器件的功能。將芯片表面放在封裝體的中心彎曲軸線上,這樣芯片表面的應力就會減小。芯片的粘接平臺下凹就是為了達到這種效果。所遇到的另一種應力情況是由應力的集中點產生的。集中點位于每個沖制引線框架底部的邊緣,如圖5所示。當沖制成形時,沖頭穿過片狀金屬形成一個圓角,它由于摩擦力拉動材料時形成。相反,在出口面一些金屬會凸,出形成毛刺,毛刺很鋒利并且是應力容易集中之處。一旦出現裂紋,裂紋就會沿著粘接芯片的支撐平臺邊緣的毛刺向一條水汽浸入通道,這種內部裂紋比較隱蔽,無法用普通的X射線技術探測。給跳步模裝置增加一道精壓工序來去毛刺,毛刺被鍛壓成邊緣倒角。

3.6塑封支撐基體

引線框架對塑封料起-個支撐基體的作用,塑料可以黏附在它的上面并在模具中形成封裝體。塑封模具的上下兩部分相互結合在一起,這時塑封料在上下模具之間整體連結在一起,當金屬區域增加時,上下兩部分切開所需的力會減小,此時在引線彎曲成形或焊接操作時沿著金屬與塑料的接觸面會產生斷裂。

水汽沿金屬與塑料連接界面處滲透官幼的減緩與金屬框架周圍塑料收縮有關,一般情況下,塑料覆蓋范圍越大,收縮力越大,設計引線框架時理想的塑料與金屬面積之比為:

Am/Ap≤1

其中:Am是金屬面積,Ap是塑料面積。

3.7內引線腳的鍍層質量

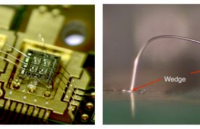

為了保證封裝工藝中的裝片/鍵合性能,使芯片和金絲與引線框架形成良好的擴散焊接,引線框架的裝片/鍵合區域(內引線腳上和小島)一般要求壓印,然后在上面鍍金或鍍銀,如圖6所示。

通過壓印可以形成-個光滑致密的表面以獲得高質量的鍍層,同時提供了一個充足平坦的鍵合點區域。壓印深度一般控制在0.013mm。早期在壓印區域都采用鍍金工藝,厚度控制在2ltm左右。采用鍍金工藝是因為鍍金層與引線框架基體和金絲有比其它金屬更加好的結合力和焊接性能,保證了很好的裝片/鍵合強度,而且化學性質穩定、耐腐蝕、耐氧化、可靠性好。但是其成本過于昂貴制約了集成電路的飛速發展,于是金的替代品銀逐漸被廣泛采用。

目前,在引線框架鍍銀工藝中,一般分為半光亮和光亮鍍銀兩種。鍍銀層的質量直接影響裝片和金絲鍵合強度,從而最終影響產品的成品率和可靠性。一般鍍銀層的厚度控制在3~8}μm,銀層表面應致密光滑,色澤均勻,呈鍍層本色,不允許有起皮、起泡、沾污、斑點、水跡、異物和發花等缺陷。應無明顯的污點、脫落或鍍層漏鍍,無貫穿鍍層的劃痕;在冷態和熱態(250℃)應無明顯變色,不允許起皮,起泡,剝落,發花,斑點等缺陷;鍵合區應易于鍵合,鍵合強度大于4gf;外引線腳經彎曲試驗后不應出現斷裂。另外,光亮度過高的銀層,在鍵合高溫時會析出碳氫物質,降低了銀面的致密性,提高了空隙率,最終影響鍵合。

3.8 引線框架的共面性

由于現在引線框架的腳數越來越多,引線框架的內外引腳和小島的共面性要求較高,否則鍵合后會斷絲等,或者在塑封模具中造成金絲斷開。一般要求共面性在100~130μm左右,實際使用時愈嚴愈好。

3.9 引線框架的彎曲

由于現在封裝都是采用自動化設備和精度較高的模具,因此要求引線框架在長度和寬度方向的側彎較小,否則會在設備導軌中傳輸時引線變形,在塑封/切筋模具中產生金屬飛邊。一般在長度方向的彎曲(俗稱為側彎)應控制在50-100μm。

3.10 引線框架的機械位置一致性

由于現在操作都是高速自動化生產,先將引線框架的機械位置等輸人到設備里,然后設備認準該數據進行快速自動化生產,如果機械位置不一致,則會造成經常停機,并且會產生大量不合格品,如圖7所示。

現在有些引線框架廠家為提高產量,上下兩排引線框架同時沖壓(也就是相當于兩付模具分別同時沖壓),然后再切開,這時就不允許這上下兩排引線框架混放在一起,因為這兩排引線框架不可能完全一致,極有可能造成鍵合機能識別上排引線框架就無法識別下排引線框架的現象。

有時雖然是同一模具沖壓出來的引線框架,但是模具沖壓次數過多,或者后面的電鍍等相應工序的控制不好,也會產生機械位置不一致。

3.11引線框架的運輸過程控制

現在的引線框架大都是基島下凹的。如果運輸過程控制不好,就會造成引線框架基島的吊筋浮起或下沉,特別是有四根吊筋的引線框架,如QFP引線框架尤為嚴重。如圖8所示。

一般引線框架出廠時,吊筋是正常的,而到了客戶那里,就會出現吊筋上浮和下沉的現象,顯然是運輸過程中造成的。對生產線上的引線框架進行抽樣調查和統計,吊筋上浮一般是在每包引線框架最上面的5條,而吊筋下沉一般是在每包引線框架的最后5條。改變角度,減少運輸過程中的震動,對減少吊筋異常是有幫助的。

4結束語

隨著微電子技術的迅速發展,集成電路復雜度的增加,集成電路具有更小的外形,更高的性能。這就對集成電路塑封引線框架提出了更高的要求,要求引線框架具備更高的電性能,更高的可靠性。因此引線框架制造要不斷技術更新,嚴格質量管理,更好地適應封裝技術和集成電路發展的需求。

- 集成電路(373294)

- 使用要求(5653)

詳解CSP封裝的類型與工藝

3725

3725

無引線框架封裝的特點優勢及在印刷電路板中的應用

6462

6462

引線框架貼膜工藝在QFN封裝制程中的應用

3923

3923

集成電路傳統封裝技術的材料與工藝

3118

3118

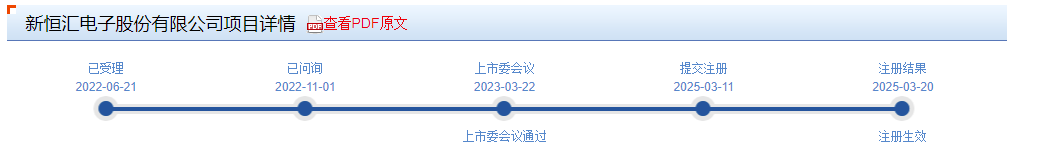

智能卡龍頭沖刺IPO,年產24億顆!柔性引線框架業務全球第二大

3911

3911

引線框芯片級封裝的建議返修程序

電路分析中的集成電路應用電路的識圖

集成電路測試儀有什么類別?

集成電路的好壞怎么判斷?

CMOS集成電路使用時的技術要求

CMOS數字集成電路是什么?CMOS數字集成電路有什么特點?

《炬豐科技-半導體工藝》集成電路加工

【轉】電路分析中的集成電路應用電路的識圖

中國集成電路大全 接口集成電路

什么是集成電路?

什么是集成電路?集成電路的分類

射頻集成電路半導體和CAD技術討論

射頻集成電路設計有什么技巧?

數字集成電路必須注意事項

模擬集成電路測試有什么技巧?

混合集成電路EMC設計產生的原因闡述

混合集成電路電磁干擾產生的原因是什么

電子元器件基礎:集成電路應用電路識圖方法

芯片失效分析

全自動影像儀 引線框架一鍵測量設備

KFC引線框架銅合金帶材的生產工藝研究

82

82引線框架用Cu.Cr.Zr合金的加工與性能研究

20

20集成電路引線焊接方法無損檢測的研究

39

39集成電路引線焊接無損檢測技術的研究

22

22集成電路封裝中的引線鍵合技術

86

86引線框芯片級封裝(LFCSP)的建議返修程序

16

16基于CPS的智能控制生產線框架網絡化設計

13

13銅合金引線框架成為封裝主要研發方向

1676

1676集成電路怎樣進行封裝?集成電路封裝有什么目的?

7401

7401大面板QFN引線框 降低制造流程的成本

4362

4362嵌入式芯片封裝你了解的有多少

5844

5844安世半導體的成功將再次復制?

4925

4925歐菲光成功研發半導體封裝用高端引線框架

4938

4938行業突破!歐菲光半導體封裝用高端引線框架成功研發

3074

3074我國引線框架市場規模到2024年市場規模達到120億元

9473

9473帶你們深度解讀集成電路封測行業

18065

18065

Inside<SPAN class=“analog-coupler”>i</span>Coupler<sup>?</sup>技術:封裝和引線框架設計

4

4集成電路處理概述:集成電路的處理方法報告

1143

1143

新恒匯募資5.19億元 擴充高密度QFN/DFN蝕刻引線框架產能

3163

3163如何測試半導體集成電路引線牢固性?

2326

2326半導體集成電路引線鍵合的技術有哪些?

3445

3445集成電路封裝的分類與演進

3466

3466等離子清洗在引線框架封裝工藝中的應用

3057

3057等離子清洗在引線框架封裝工藝中有哪些應用

2010

2010常用的引線框架拉伸測試標準及其步驟,全面解析

2088

2088

半導體集成電路黏附強度原理是什么?如何測試

1162

1162

半導體集成電路引線疲勞測試作用與方法介紹!廠家技術解答

1664

1664

9.7.1 引線框架材料∈《集成電路產業全書》

694

694

9.5.1 集成電路對光掩模材料的要求及發展∈《集成電路產業全書》

1123

1123

CH系列全自動影像儀在封測行業的應用

1792

1792

如何高效測量引線框架尺寸?中圖儀器影像一鍵解決測量難題

2490

2490

等離子清洗機在陶瓷封裝、引線框架、芯片鍵合、引線鍵合的應用

1516

1516

“高端集成電路引線框架銅合金材料研發與應用”里程碑節點考核會在博威合金召開

2059

2059

一文讀懂半導體引線框架

13111

13111

集成電路塑封工藝流程及質量檢測

4644

4644

怎么解決功率器件塑封過程中引腳壓傷的問題?

3614

3614

車規驗證對銅線的可靠性要求

2644

2644

簡述專用集成電路設計的基本要求有哪些

1904

1904專用集成電路和通用集成電路的區別在哪 專用集成電路 通用集成電路有哪些類型

3282

3282QFN引線框架可靠性揭秘:關鍵因素全解析

3312

3312

金融界:萬年芯申請用于引線框架的同步預熱設備及預熱控制方法專利

703

703

帶你一文了解什么是引線鍵合(WireBonding)技術?

2832

2832

引線框架質量大起底:影響集成電路的關鍵因素

2082

2082

聚焦塑封集成電路:焊錫污染如何成為可靠性“絆腳石”?

1086

1086

引線框架對半導體器件的影響

1519

1519 電子發燒友App

電子發燒友App

評論