電子發(fā)燒友網(wǎng)>PCB設(shè)計(jì)>Allegro>

凡億Allegro Skill字符功能-添加中文字符

? ?在使用Allegro軟件進(jìn)行PCB設(shè)計(jì)的過程中,我們可能會(huì)遇到一個(gè)問題,那就是該軟件并不支持直接放置中文字符,它僅支持英文字符。特別是在PCB設(shè)計(jì)完成之后,可能需要在絲印層上添加公司名...

2025-07-01 標(biāo)簽:pcbCadencePCB設(shè)計(jì)allegroskill 268

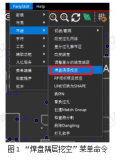

Allegro Skill布線功能--過孔助手

在進(jìn)行PCB設(shè)計(jì)的過程中,一個(gè)經(jīng)常需要執(zhí)行的操作就是打孔。 打孔基本存在于散熱焊盤的打孔、整板地過孔放置或者特定區(qū)域的打孔,以及在銅皮上進(jìn)行的打孔等。如果這些操作是通過手動(dòng)方...

2025-06-22 標(biāo)簽:pcbPCB設(shè)計(jì)PCB布線allegro過孔 487

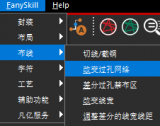

凡億Allegro Skill布線功能-檢查跨分割

在進(jìn)行高速PCB設(shè)計(jì)的過程中,高速信號(hào)線需要進(jìn)行阻抗控制,那么參考平面的完整性對(duì)于高速信號(hào)的完整性和穩(wěn)定性至關(guān)重要。然而,如果僅僅依賴于肉眼去檢查參考平面的完整性,往往容易遺...

2025-06-19 標(biāo)簽:PCB設(shè)計(jì)PCB布線allegro高速PCB 565

高速PCB設(shè)計(jì)挑戰(zhàn) Allegro Skill布線功能 自動(dòng)創(chuàng)建match_group

在進(jìn)行高速PCB設(shè)計(jì)的過程中,常常會(huì)遇到一個(gè)挑戰(zhàn),那就是高速信號(hào)的時(shí)序匹配問題。為了確保信號(hào)的同步到達(dá),設(shè)計(jì)者需要對(duì)特定的高速信號(hào)組進(jìn)行等長設(shè)計(jì)。手動(dòng)進(jìn)行這樣的操作可能會(huì)非常...

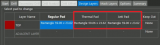

Allegro Skill布線功能-改變過孔網(wǎng)絡(luò)介紹與演示

? ?在PCB設(shè)計(jì)時(shí),有時(shí)候需要改變過孔網(wǎng)絡(luò),例如在一個(gè)位置不同層有不同網(wǎng)絡(luò)的銅皮,這時(shí)候在這個(gè)區(qū)域拷貝過孔,過孔就有可能不會(huì)成為需要的網(wǎng)絡(luò),就可以用到Fanyskill的改變過孔網(wǎng)絡(luò)功能...

2025-05-28 標(biāo)簽:pcbPCB設(shè)計(jì)PCB布線allegro過孔 558

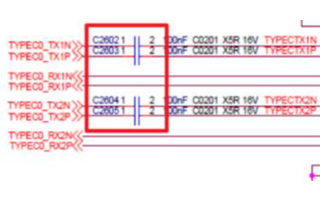

Allegro Skill布線功能-添加差分過孔禁布區(qū)

在高速PCB設(shè)計(jì)中,差分過孔之間設(shè)置禁止布線區(qū)域具有重要意義。首先它能有效減少其他信號(hào)線對(duì)差分信號(hào)的串?dāng)_,保持差分對(duì)的信號(hào)完整性。其次禁止布線區(qū)域有助于維持差分對(duì)的對(duì)稱性,確...

Allegro Skill封裝原點(diǎn)-優(yōu)化焊盤

在PCB設(shè)計(jì)中,部分文件可能因從Altium Designer或PADS軟件轉(zhuǎn)換而來,導(dǎo)致兼容性問題。這些問題通常表現(xiàn)為貼片焊盤會(huì)自動(dòng)增加Thermal Pad、Anti Pad以及焊盤缺失阻焊層和鋼網(wǎng)信息,如圖1所示,同時(shí)焊...

2025-03-31 標(biāo)簽:封裝PCB設(shè)計(jì)allegro焊盤skill 1093

Allegro工程師能力升級(jí)建議 工程師技能如何升級(jí)進(jìn)階

根據(jù)Cadence認(rèn)證體系及中國企業(yè)需求,Allegro工程師能力分三級(jí),分別是初級(jí)、中級(jí)、高級(jí)工程師。那么這三種工程師技能如何升級(jí)進(jìn)階? ? 1、初級(jí)工程師(Layout基礎(chǔ)) ①六層板設(shè)計(jì) 掌握消費(fèi)電...

2025-03-31 標(biāo)簽:工程師LayoutallegroAllegro設(shè)計(jì) 591

AI賦能PCB設(shè)計(jì):Allegro X AI的變革力量

傳統(tǒng) PCB 設(shè)計(jì)的困境 在電子產(chǎn)品迭代迅速的當(dāng)下,傳統(tǒng) PCB 設(shè)計(jì)流程的局限性愈發(fā)凸顯。布局布線作為 PCB 設(shè)計(jì)的關(guān)鍵環(huán)節(jié),以往依賴人工手動(dòng)操作,這一過程極為繁瑣且耗時(shí)。工程師需逐一確...

2025-02-07 標(biāo)簽:pcbPCB設(shè)計(jì)AIallegro 8525

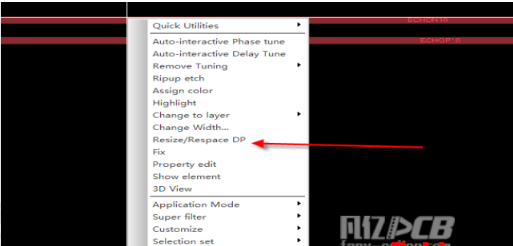

Allegro設(shè)計(jì)小技巧 | 如何刪除、復(fù)制修整好的銅皮避讓區(qū)域

點(diǎn)擊上方藍(lán)色字關(guān)注我們~我們通常所說的銅皮避讓區(qū)域,一般指的是手動(dòng)對(duì)銅皮進(jìn)行修整過的地方。在處理相同模塊的時(shí)候,手動(dòng)進(jìn)行調(diào)整過的地方是可以進(jìn)行復(fù)制的,本文向大家講解,如何...

2022-06-18 標(biāo)簽:Allegro設(shè)計(jì) 7559

Allegro設(shè)計(jì)小技巧 | 如何手動(dòng)在PCB中修改網(wǎng)絡(luò)連接關(guān)系

點(diǎn)擊上方藍(lán)色字關(guān)注我們~上期文章中我們講解了如何手動(dòng)在PCB中添加元器件,直接添加的元器件本身是沒有網(wǎng)絡(luò)的,本期我們講述一下如何手動(dòng)的在PCB中去修改網(wǎng)絡(luò)之間的連接關(guān)系,具體的操...

2022-06-13 標(biāo)簽:allegro 11352

Allegro小技巧 | 如何在走線、銅皮、焊盤上顯示網(wǎng)絡(luò)名稱

點(diǎn)擊上方藍(lán)色字關(guān)注我們~在Allegro軟件16.6版本及以上版本,增加了顯示網(wǎng)絡(luò)名稱的功能,方便進(jìn)行布線設(shè)計(jì)。本文向大家講解,如何將網(wǎng)絡(luò)命令進(jìn)行顯示,具體的操作步驟如下所示:01第一步首...

2022-05-24 標(biāo)簽:allegro 25293

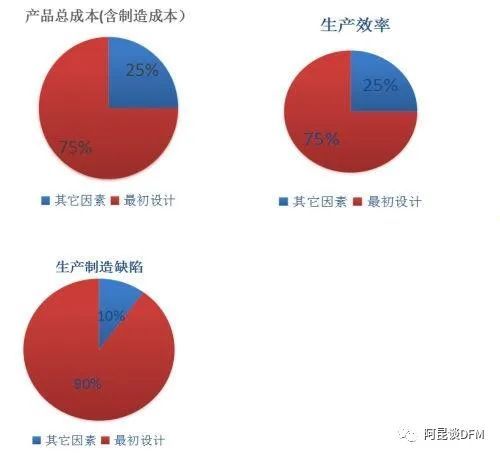

阿昆聊電子制造流行的可生產(chǎn)性設(shè)計(jì)DFM是在什么背景下出現(xiàn)?

我們的硬件電子產(chǎn)品不論是電視機(jī)、電話機(jī)或其它電子產(chǎn)品,傳統(tǒng)上一般是經(jīng)歷產(chǎn)品設(shè)計(jì)、小批量試產(chǎn)、量產(chǎn),銷售各個(gè)階段串行完成,但設(shè)計(jì)階段沒有提前全面甚至沒有考慮制造要求,結(jié)果交...

2021-05-21 標(biāo)簽:pcbPCB設(shè)計(jì)電子制造DFMPCBA 789

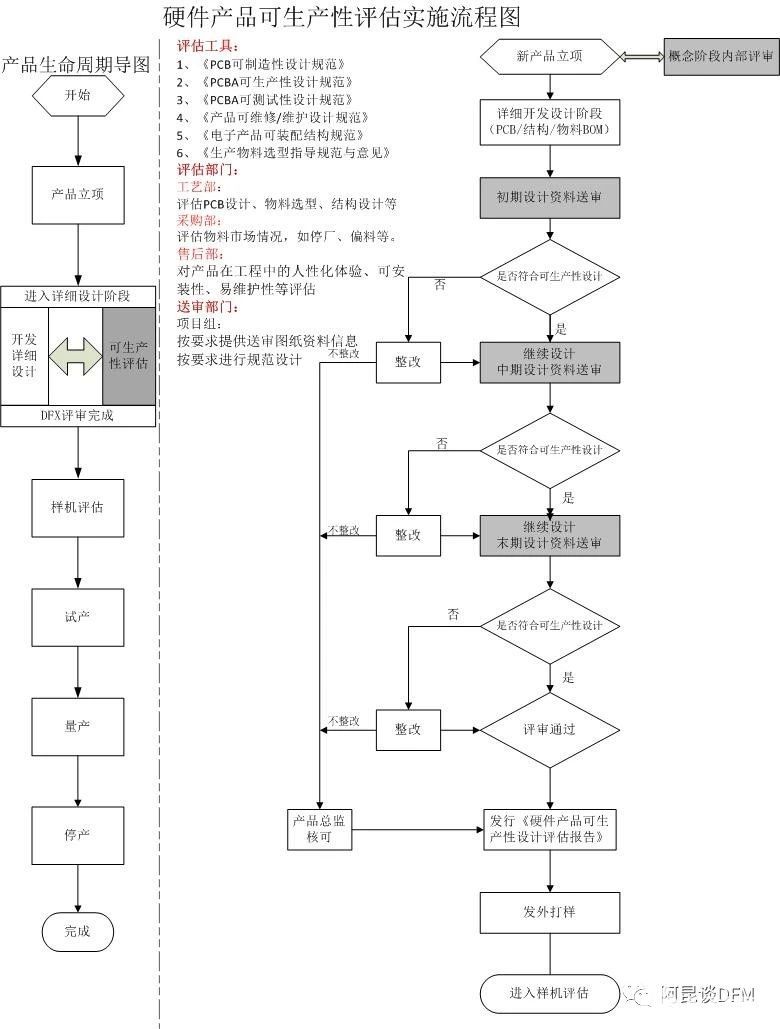

阿昆聊硬件產(chǎn)品DFM可生產(chǎn)性評(píng)估規(guī)范的執(zhí)行方案及思路

現(xiàn)代化的設(shè)計(jì)生產(chǎn)方式早已從原始的獨(dú)立串行設(shè)計(jì)變成了一個(gè)并行設(shè)計(jì)的工程,產(chǎn)品開發(fā)實(shí)際是一個(gè)各種技術(shù)整合的過程。 硬件產(chǎn)品可生產(chǎn)性研究的是將產(chǎn)品制造過程中的各個(gè)環(huán)節(jié)如:物料選...

2021-05-21 標(biāo)簽:pcb硬件DFMDFM檢驗(yàn)華秋DFM 3470

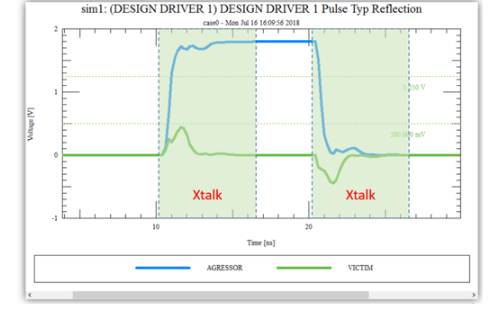

信號(hào)串?dāng)_消除方案之PCB設(shè)計(jì)IDA Crosstalk分析功能

本文將透過設(shè)計(jì)實(shí)例詳解如何使用Allegro? PCB Designer 中的IDA (In-Design Analysis, 設(shè)計(jì)同步分析) Crosstalk分析功能,只要搭配零件模型的掛載,EE/Layout人員就能于設(shè)計(jì)中同步進(jìn)行SI等級(jí)的串?dāng)_分析...

2020-11-12 標(biāo)簽:pcbPCB設(shè)計(jì)allegro串?dāng)_華秋DFM 3728

pcb設(shè)計(jì):Allegro自動(dòng)修改差分線寬方法

在pcb設(shè)計(jì)過程中,有時(shí)候因?yàn)樽杩沟淖兓覀冃枰囊呀?jīng)布好的走線,單根走線非常好更改,直接使用change命令修改線寬即可,對(duì)于差分信號(hào),有線寬、線距,所以我們不能直接用change命令...

2020-10-18 標(biāo)簽:阻抗PCB設(shè)計(jì)走線差分信號(hào) 8355

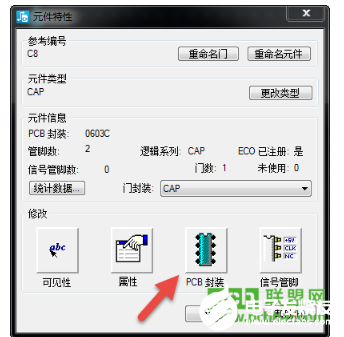

PCB技術(shù):繪制原理圖怎么去進(jìn)行封裝分配

在繪制原理圖時(shí),對(duì)于單個(gè)器件缺少封裝的情況,我們?cè)趺慈ミM(jìn)行封裝分配,操作步驟如下: 第一步,雙擊需要分配封裝的元器件,系統(tǒng)彈出元件特性對(duì)話框,用來編輯改元器件的屬性; 第二...

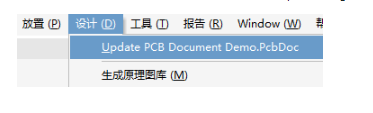

Altium Designer原理圖設(shè)計(jì)導(dǎo)入PCB的兩種方法

PCB原理圖導(dǎo)入的2種方法,小白也能看懂! Altium Designer的原理圖設(shè)計(jì)導(dǎo)入PCB,存在兩種方法:一種是直接導(dǎo)入法,類似于Allegro的第一方導(dǎo)入;另一種是間接法,即網(wǎng)表對(duì)比導(dǎo)入法。 一、直接導(dǎo)...

2020-10-16 標(biāo)簽:pcbAltium DesignerAltium DesignerpcbPCBPCB原理圖 86349

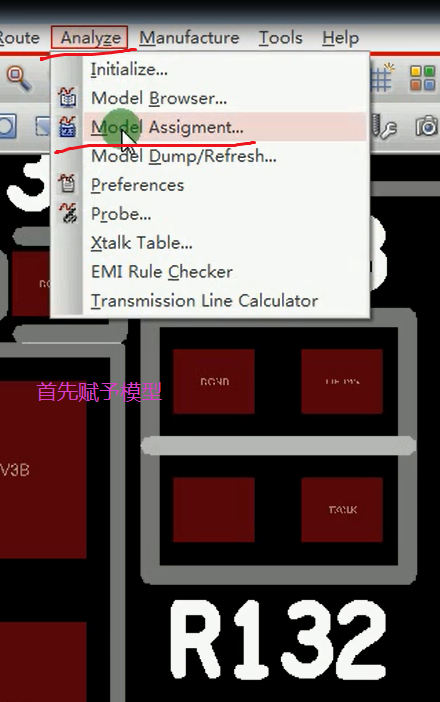

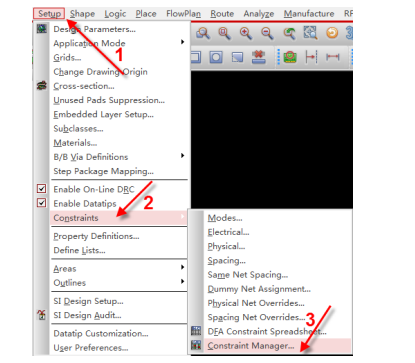

PCB技術(shù):allegro軟件中如何通過模型添加相對(duì)傳輸延遲的等長規(guī)則

講述一下如何使用模型添加法去添加相對(duì)傳輸延遲的等長規(guī)則,...

2020-10-14 標(biāo)簽:pcb拓?fù)浣Y(jié)構(gòu)allegro管理器 5852

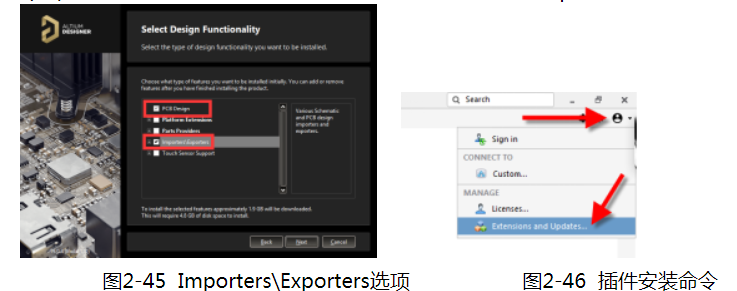

PCB技術(shù):Altium怎么安裝導(dǎo)入導(dǎo)出插件

EDA軟件中Altium Designer的兼容性是最好的,在其他EDA平臺(tái)設(shè)計(jì)的原理圖、PCB等文件,有時(shí)候會(huì)統(tǒng)一到Altium Designer平臺(tái),或者將在Altium Designer平臺(tái)設(shè)計(jì)的文件導(dǎo)入其他平臺(tái),這種時(shí)候需要用到導(dǎo)入導(dǎo)...

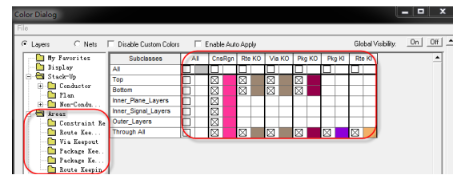

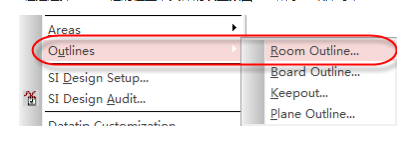

pcb設(shè)計(jì)中各種不同區(qū)域的設(shè)計(jì)

我們?cè)谶M(jìn)行pcb設(shè)計(jì)的時(shí)候,需要根據(jù)不同的PCB板結(jié)構(gòu)以及一些電子產(chǎn)品的需求來進(jìn)行各種不同區(qū)域的設(shè)計(jì),包括允許布局區(qū)域設(shè)計(jì)、禁止布局區(qū)域設(shè)計(jì)。允許布線區(qū)域設(shè)計(jì)等等。在allegro設(shè)計(jì)中...

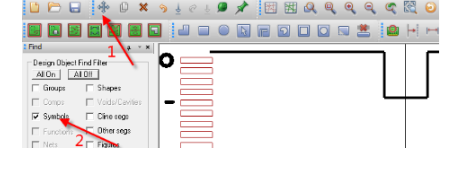

PCB設(shè)計(jì)技術(shù):如何移除創(chuàng)建Groups組的Groups屬性

對(duì)一些做好的模塊進(jìn)行創(chuàng)建Groups組的操作,方便我們進(jìn)行模塊復(fù)用、布局操作。我們創(chuàng)建了Groups組之后呢,這個(gè)屬性會(huì)一直存在,我們是否可以將這個(gè)屬性給去除掉,方便后期的布線操作與規(guī)劃...

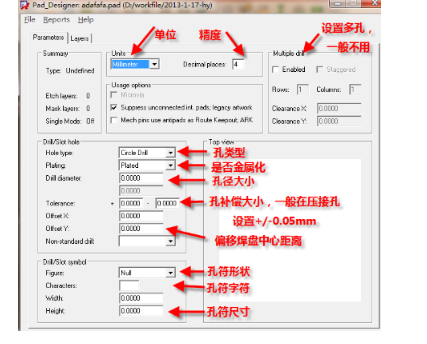

Allegro軟件繪制的PCB封裝詳細(xì)步驟解析

Allegro軟件繪制PCB封裝,比其它EDA軟件相對(duì)于復(fù)雜一些,步驟更多一些,我們這里簡(jiǎn)單的列一下通過Allegro軟件繪制的PCB封裝的步驟,分2類不同封裝,即貼片類型封裝和插件類型封裝,具體的操作...

如何通過ROOM框在PCB板上來放置元器件

這里給大家介紹一些,通過在原理圖添加ROOM屬性,然后通過ROOM框在PCB板上來放置元器件,這樣就可以根據(jù)模塊或者一頁原理圖去發(fā)放置元器件了,具體操作如下: 第一步,需要對(duì)原理圖中的元...

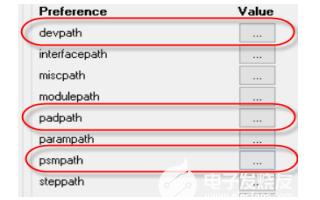

Allegro軟件中怎么指定封裝庫路徑 其中每一個(gè)的代表什么含義

一般我們會(huì)在Allegro軟件中指定這幾個(gè)與封裝庫有關(guān)的路徑。 第一步,點(diǎn)擊Allegro軟件的Setup命令的最后一項(xiàng)User Preferences...,如圖4-25所示; 圖4-25 用戶參數(shù)設(shè)置示意圖 第二步,在彈出的對(duì)話框中,...

2020-04-22 標(biāo)簽:pcbPCB設(shè)計(jì)allegro可制造性設(shè)計(jì)華秋DFM 3520

Cadence如何建立PCB?Cadence建立PCB步驟詳解

Cadence 是一個(gè)大型的EDA 軟件,它幾乎可以完成電子設(shè)計(jì)的方方面面,包括ASIC 設(shè)計(jì)、FPGA 設(shè)計(jì)和PCB 板設(shè)計(jì)。Cadence 在仿真、電路圖設(shè)計(jì)、自動(dòng)布局布線、版圖設(shè)計(jì)及驗(yàn)證等方面有著絕對(duì)的優(yōu)勢(shì)。...

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |