電子發(fā)燒友網(wǎng)>可編程邏輯>FPGA/ASIC技術(shù)>

FPGA/ASIC技術(shù)

電子發(fā)燒友本欄目為FPGA/ASIC技術(shù)專欄,內(nèi)容有fpga培圳資料、FPGA開發(fā)板、FPGA CPLD知識以及FPGA/ASIC技術(shù)的其它應(yīng)用等;是您學(xué)習(xí)FPGA/ASIC技術(shù)的好欄目。什么是數(shù)字中頻?FPGA怎么實現(xiàn)數(shù)字中頻?

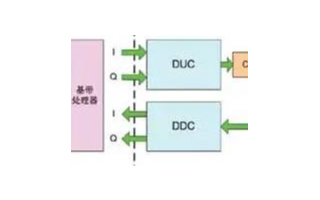

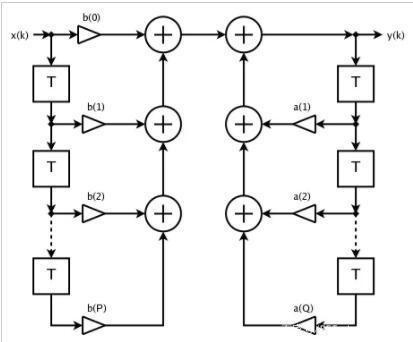

數(shù)字中頻顧名思義,是指一種中間頻率的信號形式。中頻是相對于基帶信號和射頻信號來講的,中頻可以有一級或多級,它是基帶和射頻之間過渡的橋梁。 如圖1所示,中頻部分用數(shù)字方式來實...

2023-10-21 標簽:FPGADDCDUC數(shù)字中頻數(shù)控振蕩器 8467

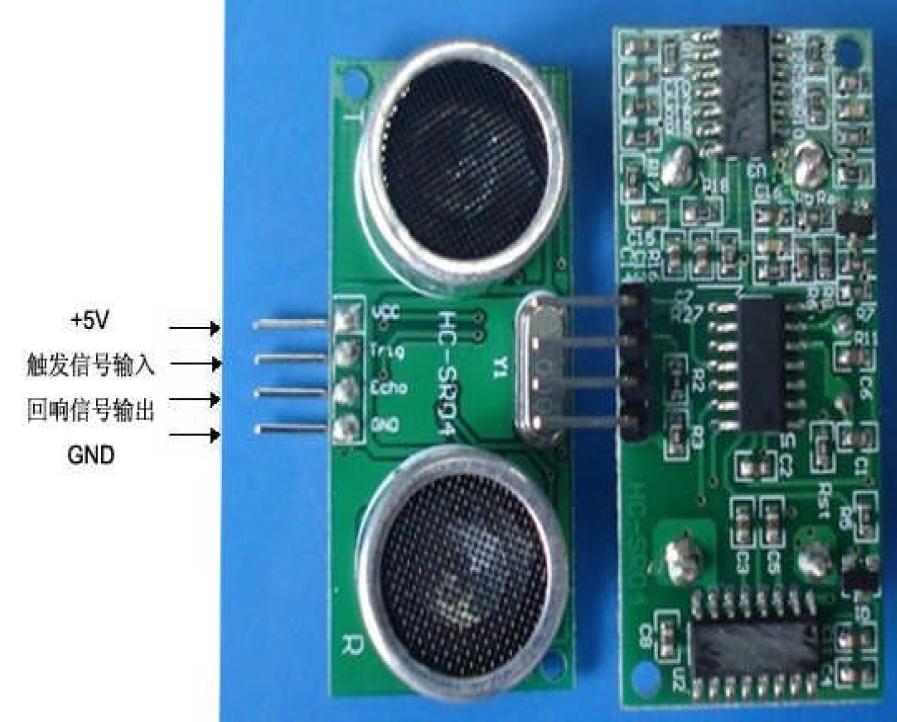

FPGA零基礎(chǔ)之Vivado-超聲波驅(qū)動設(shè)計

聲音是我們?nèi)粘I钪胁豢扇鄙俚囊环N信號,在傳遞信息的同時,也在生活中的各個領(lǐng)域有較多的應(yīng)用。...

2023-10-18 標簽:驅(qū)動器FPGA設(shè)計接收器超聲波Vivado 1624

基于VHDL語言用FPGA制作SPI-ASI接口轉(zhuǎn)換器

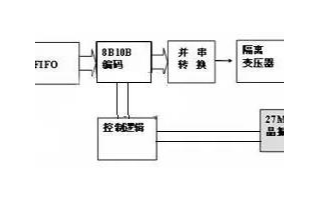

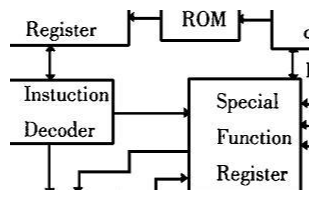

本文在分析ASI發(fā)送系統(tǒng)機理的基礎(chǔ)之上,提出一種使用FPGA完成ASI發(fā)送系統(tǒng)的實現(xiàn)方案,并使用VHDL語言在Altara的FPGA上實現(xiàn)了硬件電路。 1 引言 在目前的廣播電視系統(tǒng)中ASI接口是使用非常廣泛的...

2023-10-18 標簽:FPGASPIASIvhdl接口轉(zhuǎn)換器 3492

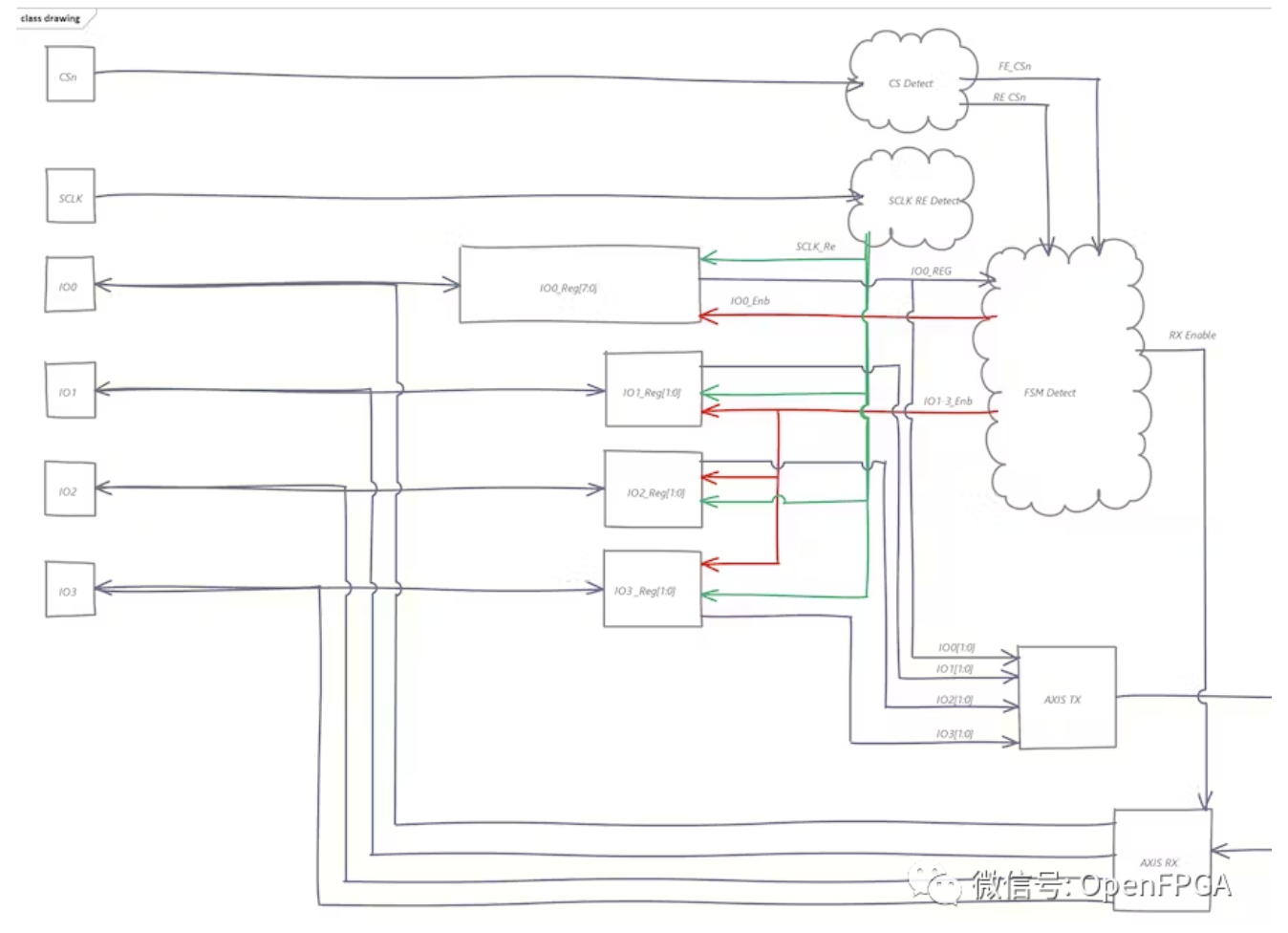

你想自己設(shè)計一個FPGA IP嗎!

開發(fā)和驗證 FPGA IP 不僅僅是編寫 HDL,而是需要更多的思考。讓我們來看看如何做吧!...

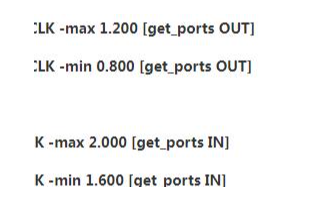

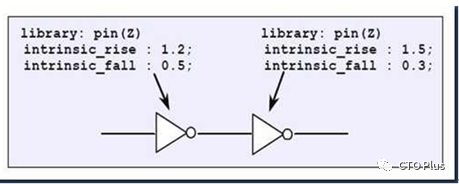

如何在FPGA設(shè)計環(huán)境中加入時序約束?

在給FPGA做邏輯綜合和布局布線時,需要在工具中設(shè)定時序的約束。通常,在FPGA設(shè)計工具中都FPGA中包含有4種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入到輸出的...

2023-10-12 標簽:FPGAFPGA設(shè)計時鐘時序約束 2144

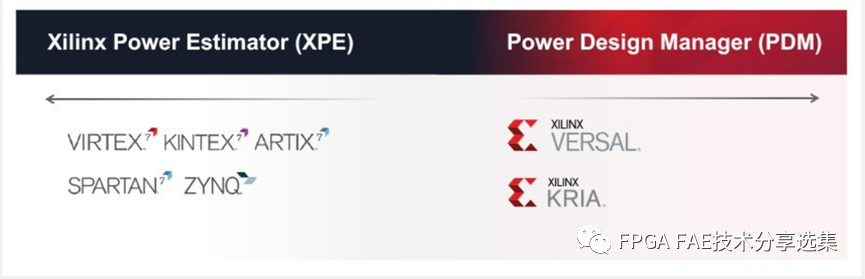

如何使用Power Design Manager(PDM)進行功耗評估?

在基于FPGA和 SoC器件的產(chǎn)品設(shè)計過程中,從器件選擇到系統(tǒng)級電源設(shè)計、散熱設(shè)計,電源功率估算對于設(shè)計方案確定至關(guān)重要;早...

2023-10-08 標簽:電源設(shè)計FPGA設(shè)計PDMVivado 3654

FPGA設(shè)計中的模塊化設(shè)計

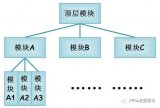

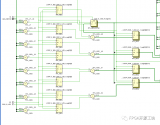

模塊化設(shè)計是FPGA設(shè)計中一個很重要的技巧,它能夠使一個大型設(shè)計的分工協(xié)作、仿真測試更加容易,代碼維護或升級也更加便利。...

2023-10-07 標簽:FPGA設(shè)計CLK 2402

FPGA排序-冒泡排序(Verilog版)介紹

仍然以8個8bit的數(shù)為例來介紹冒泡排序,因此數(shù)據(jù)的輸入和輸出位寬均為64bit(8*8bit),使用valid信號來標識數(shù)據(jù)有效,整個實現(xiàn)采用流水線的方式。...

如何脫離Vivado建立單獨仿真環(huán)境軟件呢?

FPGA項目開發(fā)的過程中,需要完成設(shè)計代碼開發(fā)、驗證環(huán)境搭建、仿真分析、板級驗證等操作,在這個過程中,許多操作雖然必不可少但是步驟是重復(fù)的。...

利用 FPGA 快速路徑構(gòu)建高性能、高能效邊緣 AI 應(yīng)用

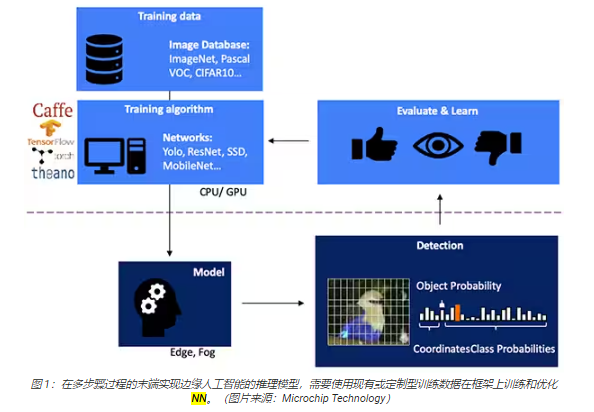

作者:Stephen Evanczuk 對于希望在邊緣的推理處理器上實施人工智能 (AI)算法的設(shè)計人員來說,他們正不斷面臨著降低功耗并縮短開發(fā)時間的壓力,即使在處理需求不斷增加的情況下也是如此。...

2023-10-03 標簽:FPGA嵌入式物聯(lián)網(wǎng)AI 2113

FPGA浮點IP內(nèi)核究竟有哪些優(yōu)勢呢?

最近出現(xiàn)的 FPGA設(shè)計工具和 IP有效減少了計算占用的資源,大大簡化了浮點數(shù)據(jù)通路的實現(xiàn)。而且,與數(shù)字信號處理器不同...

2023-09-25 標簽:dspFPGA設(shè)計乘法器MATLAB仿真數(shù)字信號處理器 1615

基于FPGA做的開源示波器/邏輯分析儀/頻譜儀/波形發(fā)生器設(shè)計

ScopeFun是一款經(jīng)濟實惠、開源、一體化的儀器平臺。...

2023-09-25 標簽:示波器USB接口MSPSFFT任意波形發(fā)生器 2817

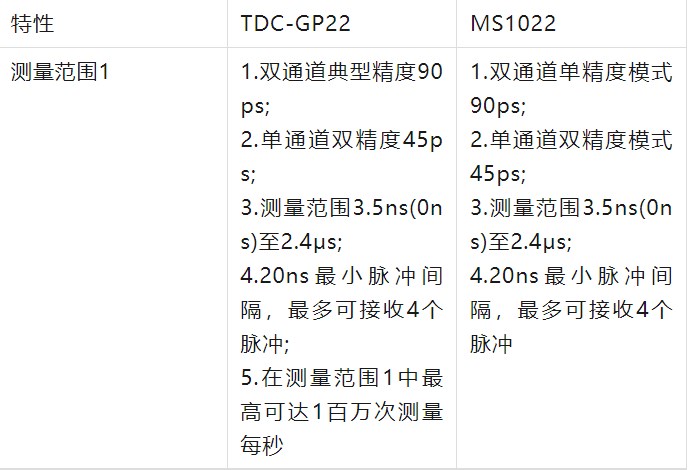

求一種基于FPGA時間數(shù)字轉(zhuǎn)換(TDC)設(shè)計方案

時間數(shù)字轉(zhuǎn)換(Time-to-Digital Converter,TDC)是一種用來測量時間的電路,它將連續(xù)的時間信號轉(zhuǎn)換為數(shù)字信號,從而實現(xiàn)時間測量的數(shù)字化。...

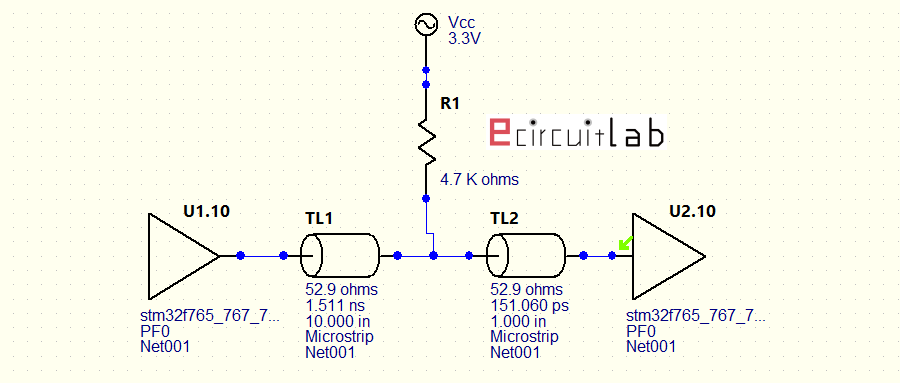

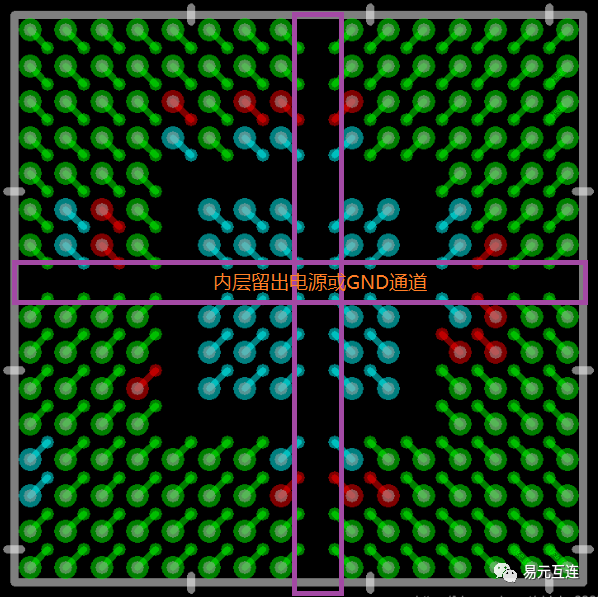

BGA如何快速在4個Ball之間均勻布孔扇出呢?

BGA扇出是EDA工程師的一項基本功,在布局完成后,先將BGA的Ball進行打孔扇出,然后分層和4個方向?qū)GA內(nèi)部信號線引出到外部空間...

2023-09-22 標簽:PCB板FPGA設(shè)計BGA封裝DRCEDA設(shè)計 8025

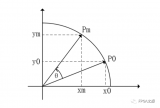

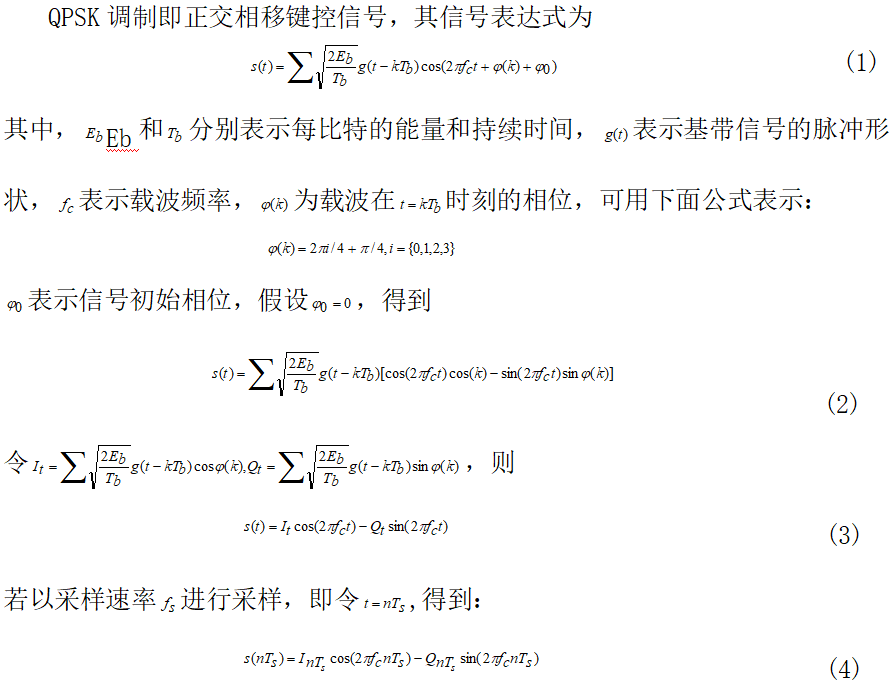

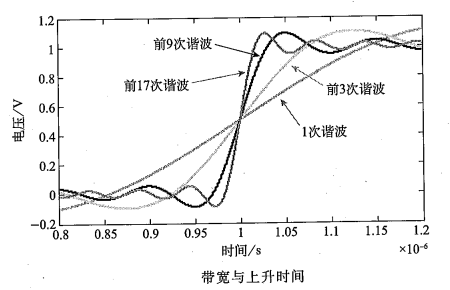

如何實現(xiàn)一種基于FPGA全數(shù)字高碼率QPSK調(diào)制設(shè)計?

調(diào)制信號的符號速率達到500Mbps,根據(jù)奈奎斯特采樣定理,DA的采樣頻率采用2Gbps。...

2023-09-22 標簽:濾波器FPGA設(shè)計調(diào)制解調(diào)器QPSKMATLAB仿真 3441

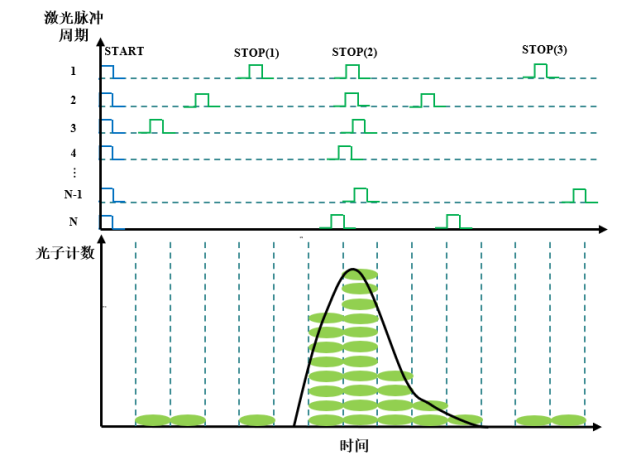

基于單光子探測的時間相關(guān)計數(shù)TCSPC設(shè)計實現(xiàn)

TCSPC時間相關(guān)單光子計數(shù)技術(shù)是一種成熟且通用的單光子計數(shù)技術(shù),是一種功能強大的分析方法,目前廣泛應(yīng)用于熒光壽命測量、時間分辨光譜、熒光壽命成像、飛行時間測量等眾多領(lǐng)域,尤其...

2023-09-22 標簽:FPGA設(shè)計存儲器數(shù)字轉(zhuǎn)換器上位機單光子探測器 9249

什么是DFX技術(shù)?DFX設(shè)計一定要執(zhí)行設(shè)計規(guī)則檢查嗎?

DFX(Dynamic Function eXchange)的前身是PR(部分可重配置,Partial Reconfiguration)。...

2023-09-21 標簽:FPGAVHDL語言RTLDCPdfx設(shè)計 9563

用Verilog在FPGA上實現(xiàn)低通濾波器

在本文中,我們將簡要介紹不同類型的濾波器,然后學(xué)習(xí)如何實現(xiàn)移動平均濾波器并使用CIC架構(gòu)對其進行優(yōu)化。...

2023-10-02 標簽:FPGA設(shè)計低通濾波器加法器fir濾波器FIFO存儲 4233

數(shù)字IC設(shè)計中的異步FIFO簡介

在大規(guī)模ASIC設(shè)計中,**多時鐘系統(tǒng)**通常是不可避免的,這會導(dǎo)致不同時鐘域中的數(shù)據(jù)傳輸問題。...

2023-09-20 標簽:寄存器IC設(shè)計ASIC設(shè)計同步器FIFO存儲 2115

Mojo v3 FPGA板與16x2 LCD模塊是如何進行連接的呢?

在本教程中,我們將使用Verilog HDL設(shè)計一個數(shù)字電路,該電路與基于HD44780 LCD控制器/驅(qū)動芯片的通用LCD模塊連接。Mojo V3 FPGA板將用于實現(xiàn)設(shè)計。本文中使用的LCD模塊是1602A顯示器。...

2023-09-20 標簽:FPGA設(shè)計LCD控制器多路復(fù)用器觸發(fā)器HDL語言 1608

怎樣使用Verilator進行Verilog Lint呢?

FPGA設(shè)計是無情的,所以我們需要利用能獲得的任何軟件進行檢查...

2023-09-20 標簽:FPGA設(shè)計仿真器SDL靜態(tài)分析macOS系統(tǒng) 3381

如何使用Verilog硬件描述語言描述時序邏輯電路?

時序邏輯電路的特點是輸出信號不僅與電路的輸入有關(guān),還與電路原來的狀態(tài)有關(guān)。...

2023-09-17 標簽:FPGA設(shè)計反相器D觸發(fā)器時序邏輯電路CLK 4311

為什么說Vivado是基于IP的設(shè)計?

Vivado是Xilinx公司2012年推出的新一代集成開發(fā)環(huán)境,它強調(diào)系統(tǒng)級的設(shè)計思想及以IP為核心的設(shè)計理念,突出IP核在數(shù)字系統(tǒng)設(shè)計中的作用。...

2023-09-17 標簽:FPGA設(shè)計寄存器C語言RTLVivado 3140

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |