完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

標簽 > lvds

Lvds :Low-Voltage Differential Signaling 低電壓差分信號1994年由美國國家半導(dǎo)體公司提出的一種信號傳輸模式,是一種電平標準,LVDS接口又稱RS-644總線接口,是20世紀90年代才出現(xiàn)的一種數(shù)據(jù)傳輸和接口技術(shù)。

文章:548個 瀏覽:69844次 帖子:437個

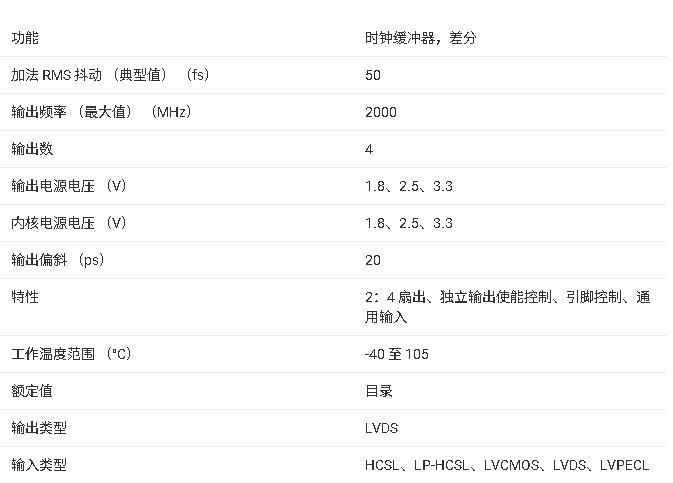

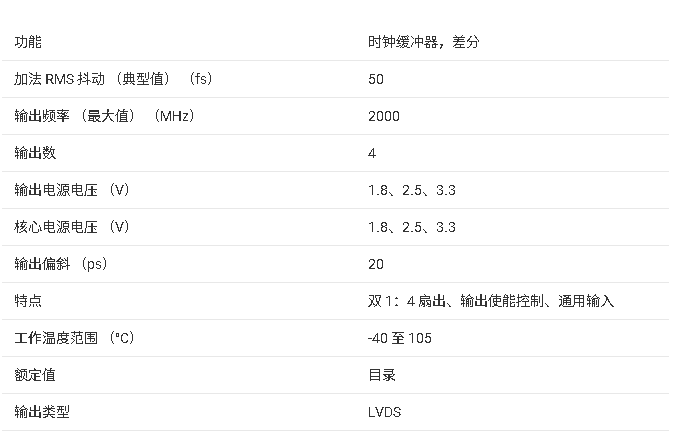

?LMK1D1204P 低附加抖動LVDS緩沖器技術(shù)文檔總結(jié)

LMK1D1204P時鐘緩沖器將兩個可選時鐘輸入(IN0和IN1)中的一個分配給4對差分LVDS時鐘輸出(OUT0至OUT3),時鐘分配的偏斜最小。輸入...

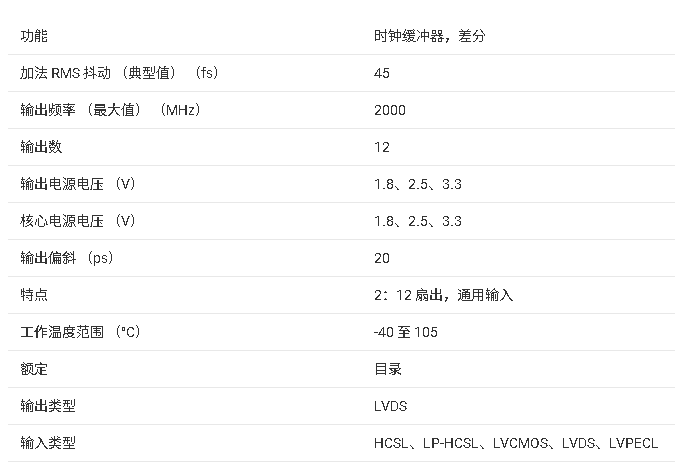

LMK1D1212 12通道輸出1.8V、2.5V和3.3V LVDS緩沖器技術(shù)手冊

LMK1D1212時鐘緩沖器以最小偏斜將兩個可選時鐘輸入(IN0、IN1)中的一個分配到12對差分LVDS時鐘輸出(OUT0至OUT11)。同樣,LMK...

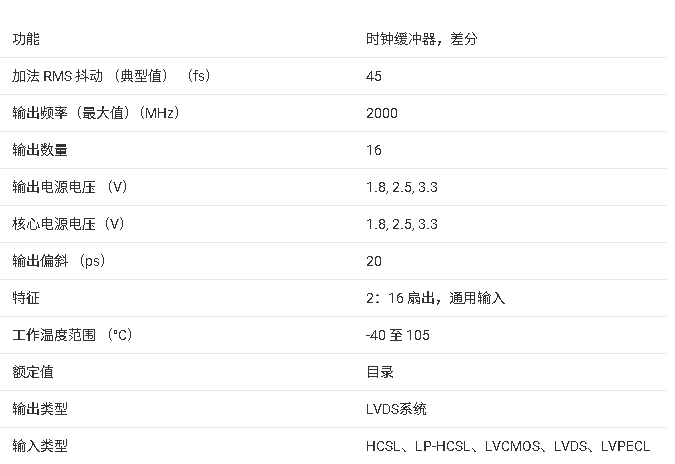

?LMK1D121x系列低附加抖動LVDS緩沖器技術(shù)文檔總結(jié)

LMK1D1212時鐘緩沖器以最小偏斜將兩個可選時鐘輸入(IN0、IN1)中的一個分配到12對差分LVDS時鐘輸出(OUT0至OUT11)。同樣,LMK...

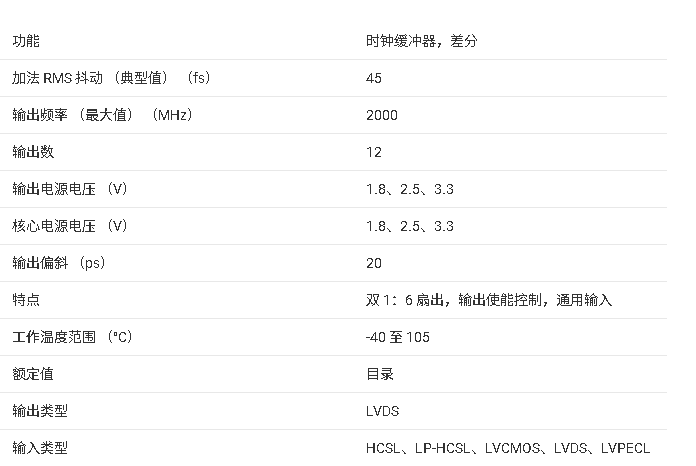

LMK1D2106 雙組 6 通道輸出 1.8V、2.5V 和 3.3V LVDS 緩沖器技術(shù)手冊

LMK1D210x 時鐘緩沖器將兩個時鐘輸入(IN0 和 IN1)分配給LMK1D2108中的總共 16 對差分 LVDS 時鐘輸出(OUT0 至 OU...

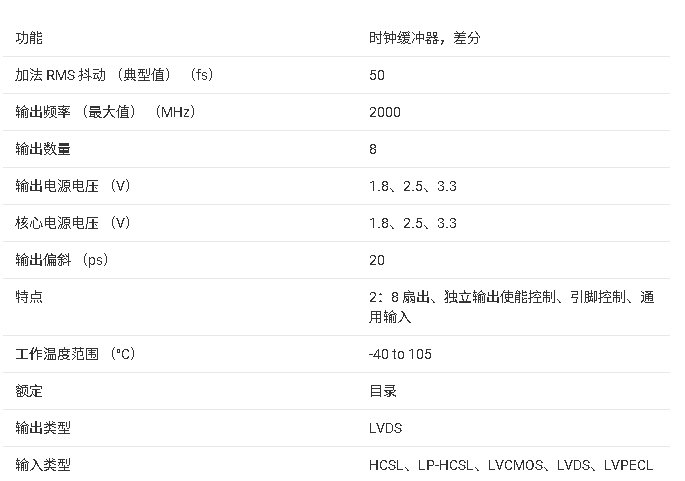

?LMK1D1208P 低附加抖動LVDS緩沖器技術(shù)文檔總結(jié)

LMK1D1208P時鐘緩沖器將兩個可選時鐘輸入(IN0和IN1)中的一個分配給8對差分LVDS時鐘輸出(OUT0至OUT7),時鐘分配的偏斜最小。輸入...

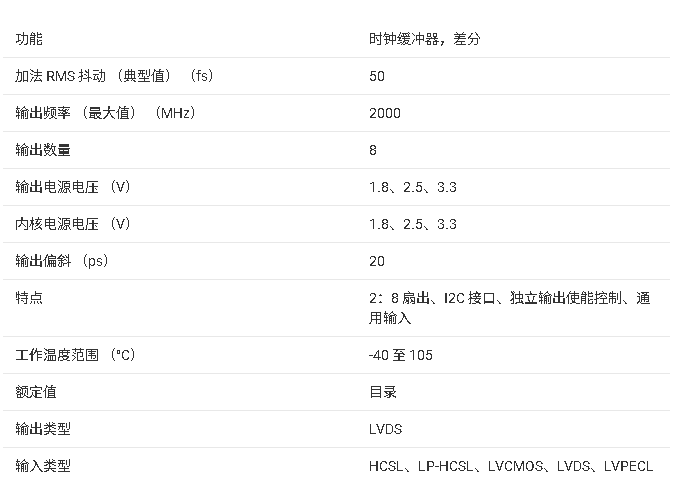

?LMK1D1208I 低附加抖動LVDS緩沖器技術(shù)文檔總結(jié)

LMK1D1208I是一個 I 2C 可編程 LVDS 時鐘緩沖器。該器件具有兩個輸入和八對差分LVDS時鐘輸出(OUT0至OUT7),時鐘分配偏斜最小...

?LMK1D210xL系列超低附加抖動LVDS緩沖器技術(shù)文檔總結(jié)

LMK1D210xL 是一款低噪聲雙時鐘緩沖器,可將一個輸入分配給最多 2 (LMK1D2102L)、4 (LMK1D2104L)、6 (LMK1D21...

LMK1D2104L 系列超低附加抖動LVDS緩沖器技術(shù)文檔總結(jié)

LMK1D210xL 是一款低噪聲雙時鐘緩沖器,可將一個輸入分配給最多 2 (LMK1D2102L)、4 (LMK1D2104L)、6 (LMK1D21...

智多晶LLCR技術(shù)的工作原理和應(yīng)用場景

工程師朋友們注意啦!今天要給大家安利一項FPGA領(lǐng)域的黑科技——西安智多晶微電子推出的LLCR(LVDS Local Clock Receiving)技...

串行RapidIO,高速串行通信協(xié)議,旨在鏈接DSP、FPGA、網(wǎng)絡(luò)處理器等芯片,具有低延遲、高帶寬(支持25Gbps、2.5Gbps、3.125Gbp...

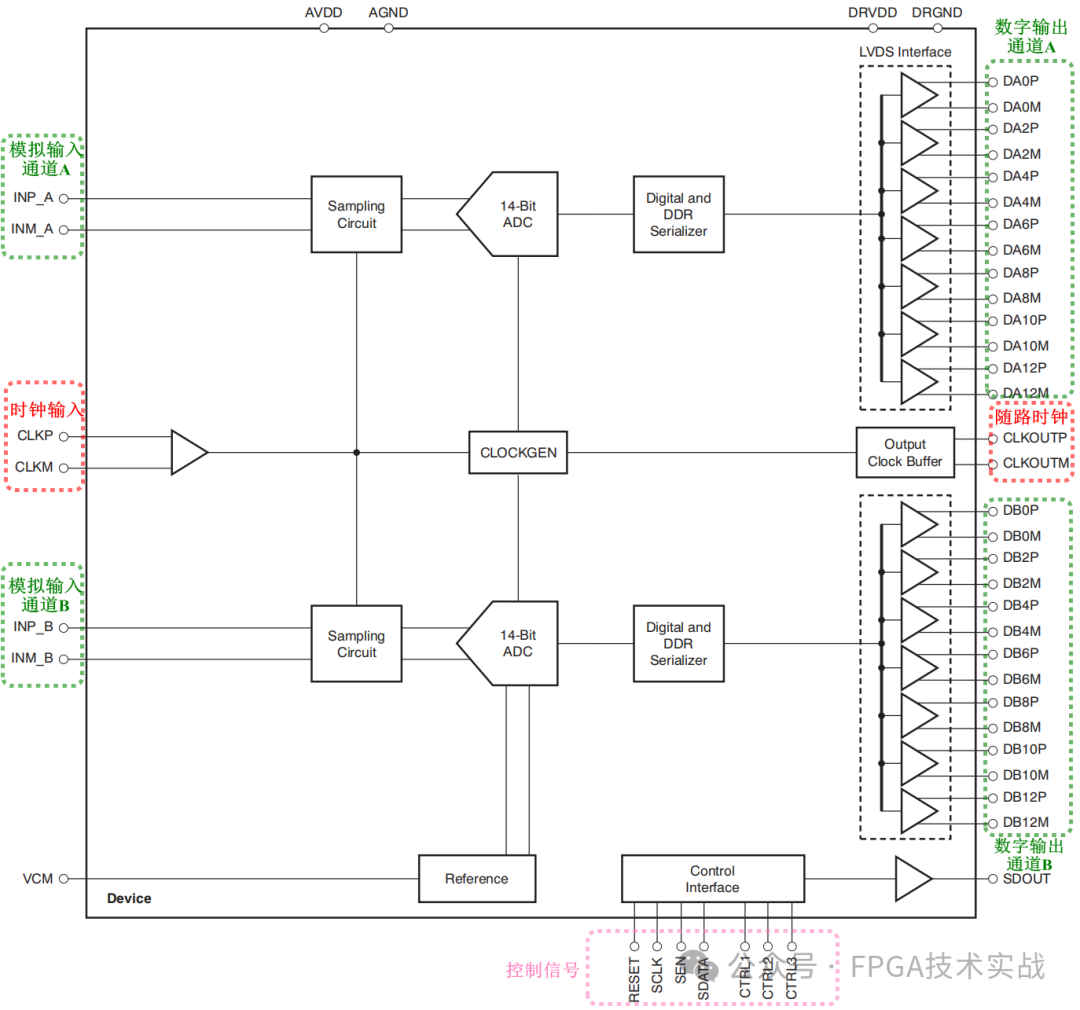

ADC和FPGA之間LVDS接口設(shè)計需要考慮的因素

本文描述了ADC和FPGA之間LVDS接口設(shè)計需要考慮的因素,包括LVDS數(shù)據(jù)標準、LVDS接口數(shù)據(jù)時序違例解決方法以及硬件設(shè)計要點。

LSSD (LVDS Source Synchronous Deserialization),是一種用于解決高速LVDS數(shù)據(jù)接收時鐘與數(shù)據(jù)相位偏移問題的技術(shù)。

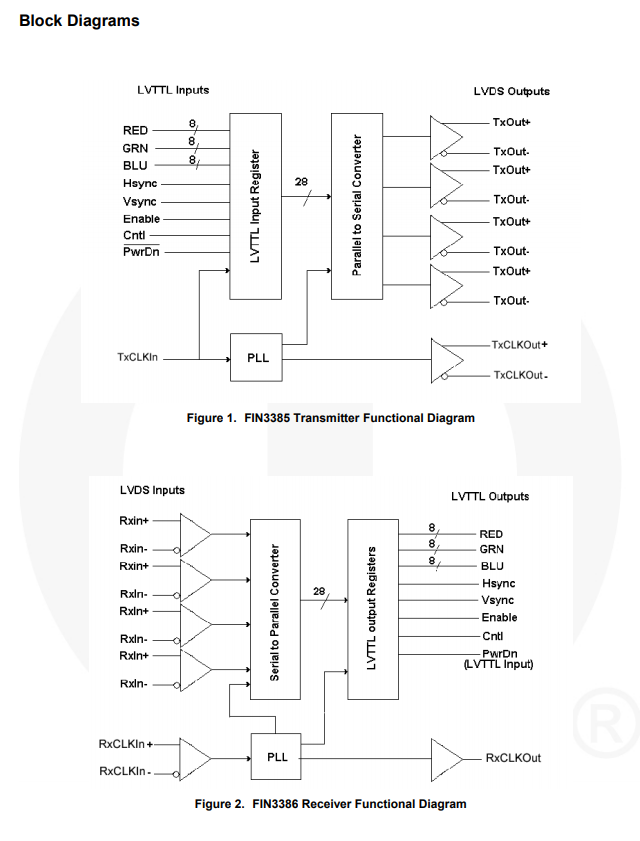

onsemi FIN3386MTDX LVDS串行解串器參數(shù)特性,數(shù)據(jù)手冊與EDA模型下載

onsemi FIN3386MTDX LVDS串行解串器參數(shù)特性,數(shù)據(jù)手冊與EDA模型下載

2025-07-09 標簽:lvdsON Semiconductor串行解串器 770 0

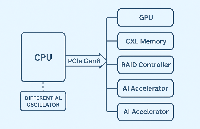

小型數(shù)據(jù)中心典型應(yīng)用平臺與差分晶體振蕩器參數(shù)對照

深入了解小型數(shù)據(jù)中心中常見的交換機、服務(wù)器、存儲設(shè)備與網(wǎng)絡(luò)模塊,如何選擇對應(yīng)的差分晶體振蕩器以確保時鐘同步與高可靠性性能。

2025-07-02 標簽:lvds數(shù)據(jù)中心LVPECL 2.2k 0

PCIe Gen6典型應(yīng)用平臺與差分晶體振蕩器參數(shù)對照

FCom富士晶振差分輸出振蕩器廣泛應(yīng)用于PCIe Gen6平臺,適用于服務(wù)器主板、GPU卡、CXL模塊等,具備超低抖動、寬溫穩(wěn)定、多封裝選擇等優(yōu)勢。

V-by-one線技術(shù):原理、應(yīng)用與未來發(fā)展

V-by-One線技術(shù)作為一種高速、高效的數(shù)字信號傳輸接口,在顯示及視頻傳輸領(lǐng)域發(fā)揮著重要作用。雙品電子專業(yè)生產(chǎn)V-by-One線技術(shù)的原理、特點,深入...

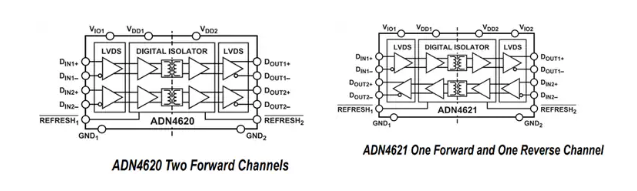

Analog Devices Inc. ADN4620和ADN4621 LVDS 2.5Gb隔離器數(shù)據(jù)手冊

Analog Devices Inc. ADN4620和ADN4621雙通道LVDS 2.5Gb隔離器是信號隔離、低電壓差分信號 (LVDS) 緩沖器,...

Altera FPGA與高速ADS4249和DAC3482的LVDS接口設(shè)計

引言: 本文以TI的ADS4249(ADC)和DAC3482(DAC)之間的接口為例,介紹Altera FPGA與ADC/DAC之間的DDR LVDS接...

ADN4650/ADN4651/ADN4652 5 kV/3.75 kV rms、600 Mbps雙通道LVDS隔離器技術(shù)手冊

ADN4652是一款信號隔離式、低壓差分信號(LVDS)緩沖器,數(shù)據(jù)速率高達600 Mbps,并且具有極低的抖動。 該器件集成 **i**Coup...

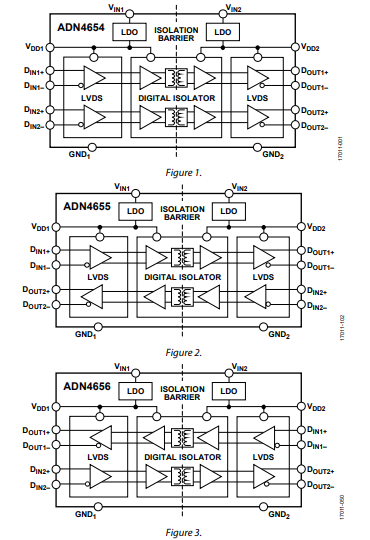

ADN4654/ADN4655/ADN4656 5kV RMS/3.75 kV RMS、雙通道LVDS千兆位隔離器技術(shù)手冊

[ADN4654]/[ADN4655]/ADN4656^1^ 是信號隔離式低電壓差分信號 (LVDS) 緩沖器,能夠以低抖動在高達 1.1 Gbps 的...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |