隨著PCIe Gen6協議的商用推進(64?GT/s,PAM4調制),對系統時鐘的抖動性能、輸出形式、溫度穩定性提出了極高要求。差分輸出晶體振蕩器作為高性能平臺的關鍵時鐘源,需要同時滿足低抖動、差分信號輸出、寬溫度工作、封裝靈活等指標,才能支撐下一代數據中心、AI運算、CXL擴展與高性能存儲等應用。

應用平臺與參數對照表

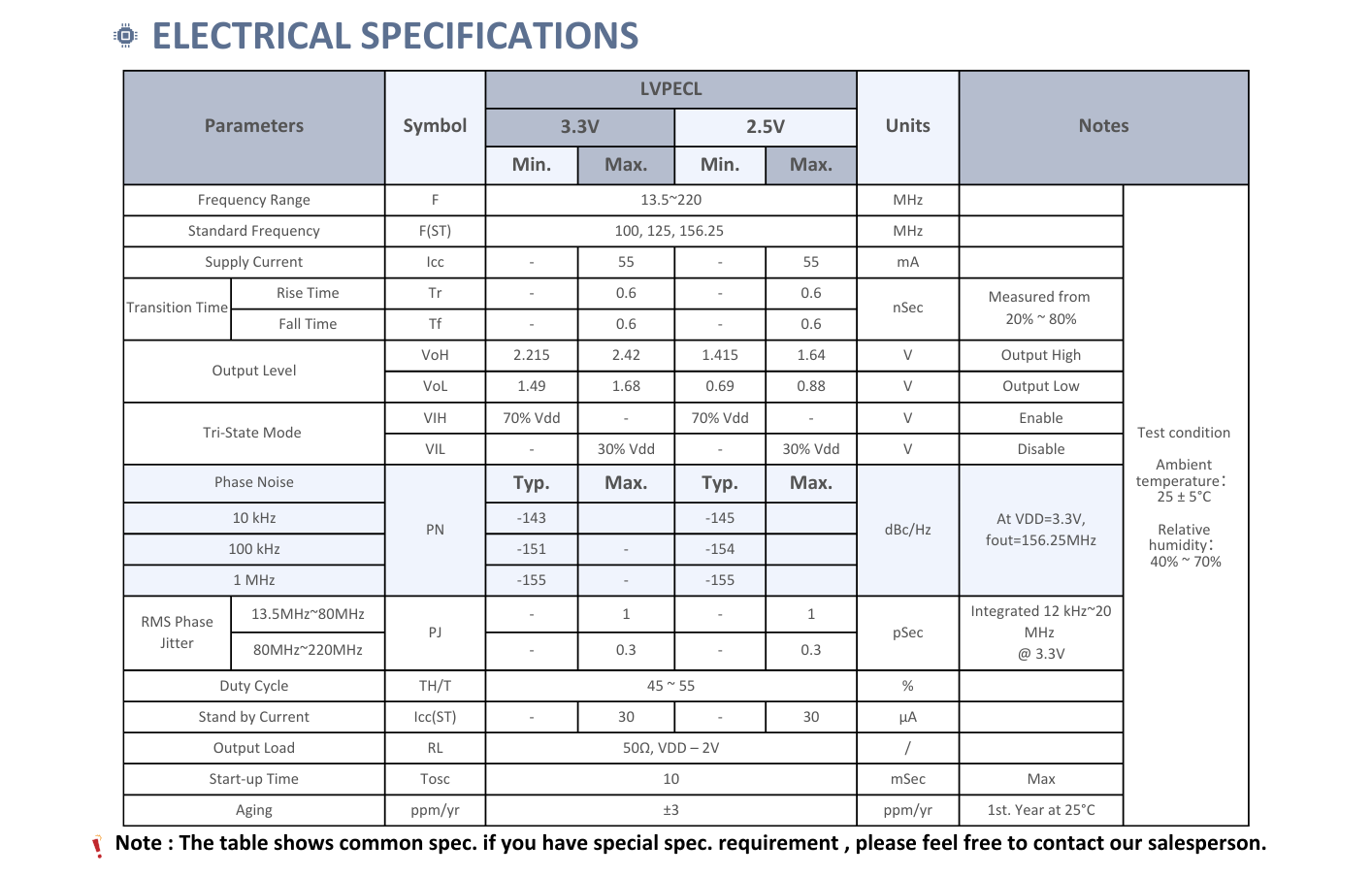

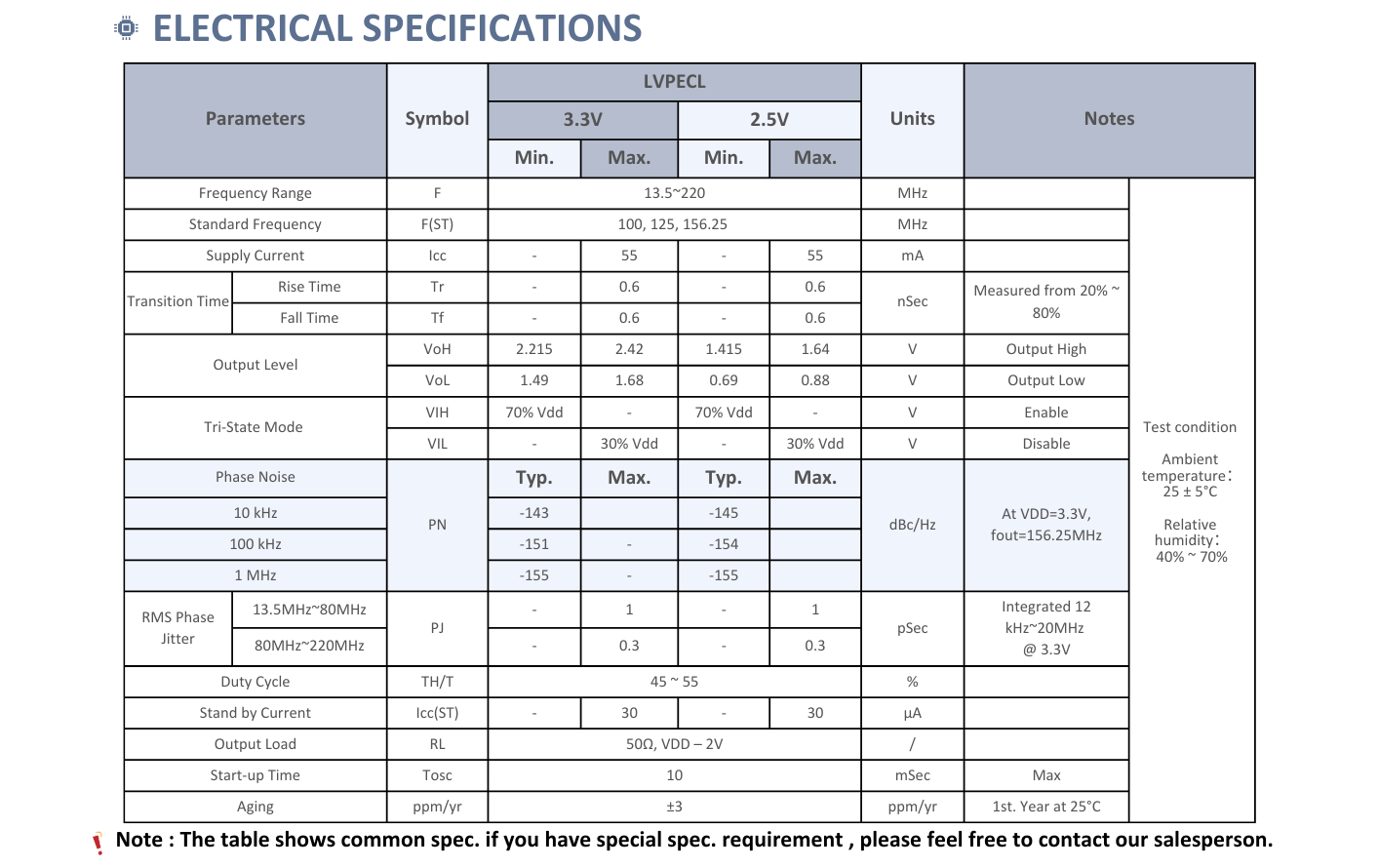

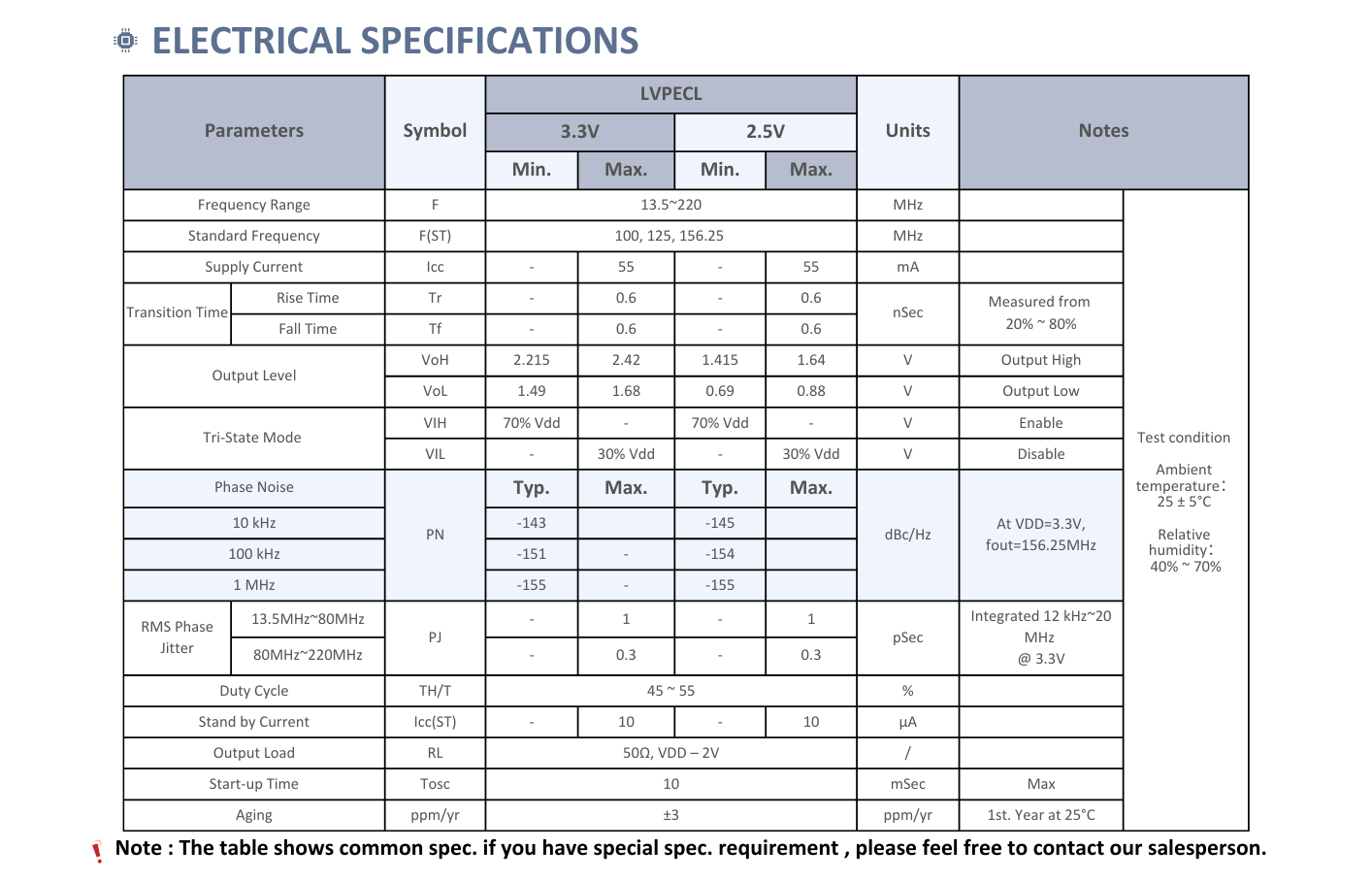

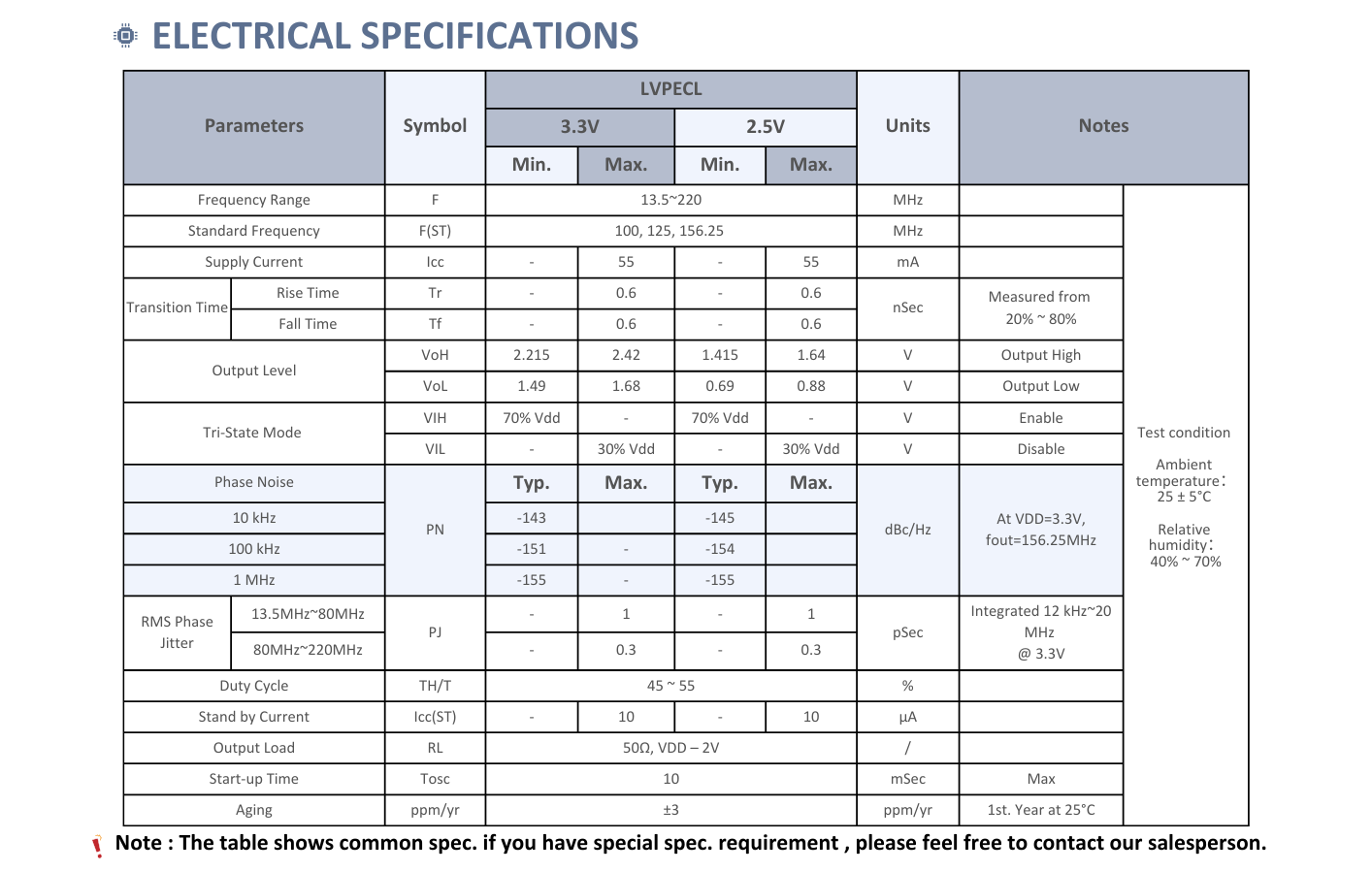

| 模塊類型 | 平臺 / 芯片 | 推薦型號 | 推薦頻率 | 輸出形式 | 抖動性能 | 溫度范圍 | 封裝尺寸 |

|---|---|---|---|---|---|---|---|

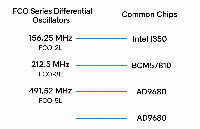

| 主板 / 服務器 | Intel Eagle Stream / AMD SP5 | FCO?5L?HCSL?100M | 100 MHz | HCSL | ≤ 80 fs RMS | ?40°C ~ +85°C | 5.0×3.2 mm |

| 前沿 GPU 顯卡 | NVIDIA H100 / AMD MI300 | FCO?7L?LVDS?100M | 100 MHz | LVDS | ≤ 80 fs RMS | ?40°C ~ +85°C | 7.0×5.0 mm |

| CXL 內存模塊 | CXL Type 3 / Smart NIC | FCO?3L?LVPECL?200M | 200 MHz | LVPECL | ≤ 100 fs RMS | ?40°C ~ +85°C | 3.2×2.5 mm |

| 存儲控制器 / SSD | PCIe Gen5/Gen6 RAID 卡 | FCO?2L?HCSL?100M | 100 MHz | HCSL | ≤ 100 fs RMS | ?40°C ~ +85°C | 2.5×2.0 mm |

| AI 加速模塊 | PCIe Gen6 AI FPGA卡 | FCO?5L?LVDS?100M | 100 MHz | LVDS | ≤ 80 fs RMS | ?40°C ~ +85°C | 5.0×3.2 mm |

選型建議與應用搭配

100 MHz HCSL:適用于PCIe主鏈路(主板、服務器、RAID卡)

100 MHz LVDS:適用于GPU模塊、AI加速卡、FPGA平臺

200 MHz LVPECL:適用于CXL高速數據鏈路與SerDes接口

供電支持:2.5V / 3.3V 兼容主流控制器

抖動控制:建議選用 ≤100 fs RMS 規格,推薦 ≤80 fs

封裝選擇:空間緊湊應用推薦使用2520或3225小型封裝

相關產品

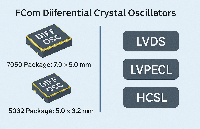

FCO?2L:小尺寸差分晶振,適用于SSD/RAID卡

差分晶振FCO-2L數據表

差分晶振FCO-2L數據表FCO?3L:主流平臺應用,兼容LVPECL/LVDS輸出

差分晶振FCO-3L數據表

差分晶振FCO-3L數據表FCO?5L:高可靠性平臺首要之選,支持高速網絡接口

差分晶振FCO-5L數據表

差分晶振FCO-5L數據表FCO?7L:適配高功耗平臺,如AI GPU服務器

差分晶振FCO-7L數據表

差分晶振FCO-7L數據表推薦典型應用場景

在服務器主板中提供PCIe主時鐘支持

用于GPU加速卡的差分同步鏈路

CXL內存模塊與主控芯片之間的高精度同步

與TI/ADI Jitter Cleaner組合用于RAID存儲系統

為FPGA平臺中的SerDes、PLL等提供穩定時鐘

總結

FCom富士晶振FCO-L系列差分晶體振蕩器,在滿足PCIe Gen6高速傳輸平臺對抖動、輸出、電壓、溫度等多方面嚴苛要求的同時,提供多樣化封裝與接口支持,是高性能系統設計中的關鍵時鐘解決方案。聯系我們

-

振蕩器

+關注

關注

28文章

4180瀏覽量

142993 -

lvds

+關注

關注

2文章

1238瀏覽量

69971 -

PCIe

+關注

關注

16文章

1464瀏覽量

88632 -

差分器件

+關注

關注

0文章

12瀏覽量

6242 -

差分晶振

+關注

關注

0文章

184瀏覽量

2058

發布評論請先 登錄

CS-23系列低相位噪聲恒溫晶體振蕩器

壓控晶體振蕩器參數及選型

XTAL晶體振蕩器是怎么工作的?一文看懂壓電原理與工程應用

FX3晶體振蕩器上電后停止,怎么解決?

中型數據中心應用平臺與差分晶體振蕩器參數對照中型數據中心應用平臺與差分晶體振蕩器參數對照

中型數據中心中的差分晶體振蕩器應用與匹配方案

FCO-L差分振蕩器搭建時鐘架構,全面剖析光模塊與PCIe Gen6的時鐘設計思路

晶體振蕩器如何失效?

愛普生SG5032EEN差分晶體振蕩器的特點

PCIe Gen6典型應用平臺與差分晶體振蕩器參數對照

PCIe Gen6典型應用平臺與差分晶體振蕩器參數對照

評論