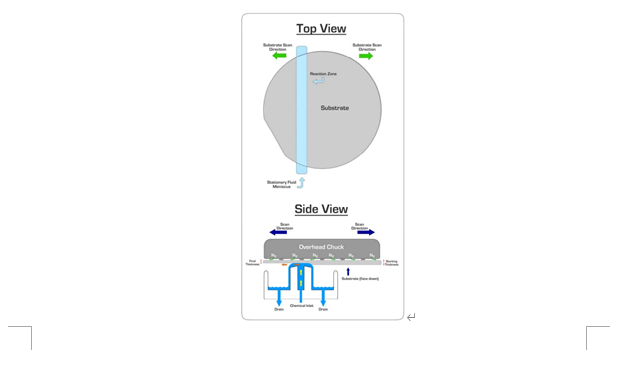

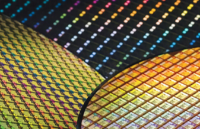

本文主要講述TSV工藝中的硅晶圓減薄與銅平坦化。 硅晶圓減薄與銅平坦化作為 TSV 三維集成技術(shù)的核心環(huán)節(jié),主要應(yīng)用于含銅 TSV 互連的減薄芯片制造流程,為該技術(shù)實(shí)現(xiàn)短互連長度、小尺寸、高集成度等特性提供了重要支撐。

2025-08-12 10:35:00 1546

1546

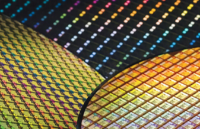

芯片制造主要分為5個(gè)階段:材料制備;晶體生長或晶圓制備;晶圓制造和分揀;封裝;終測。

2022-12-12 09:24:03 5887

5887 隨著5G技術(shù)、物聯(lián)網(wǎng)以及科學(xué)技術(shù)的不斷發(fā)展,半導(dǎo)體晶圓行業(yè)的需求量也在不斷增加。一般的晶圓片厚度有一定的規(guī)格,晶圓厚度對半導(dǎo)體器件的性能和質(zhì)量都有著重要影響。而集成電路制造技術(shù)的不斷發(fā)展,芯片特征尺寸也逐漸減小,帶動晶圓減薄工藝的興起與發(fā)展,晶圓測厚成為了不少晶圓生產(chǎn)廠家的必要需求之一。

2023-08-23 10:45:50 2657

2657

本內(nèi)容詳解了晶圓制造工藝流程,包括表面清洗,初次氧化,熱處理,光刻技術(shù)和離子刻蝕技術(shù)等

2011-11-24 09:32:10 7546

7546 材料用于RFFE的元器件制造,以及用于3D人臉識別的VCSEL和光電探測器。如今,在iPhone X的材料清單(BOM)中列出的約121顆器件中,約15顆器件是在150mm晶圓上制作的。這代表什么呢

2019-05-12 23:04:07

小弟想知道8寸晶圓盒的制造工藝和檢驗(yàn)規(guī)范,還有不知道在大陸有誰在生產(chǎn)?

2010-08-04 14:02:12

安森美半導(dǎo)體全球制造高級副總裁Mark Goranson最近訪問了Mountain Top廠,其8英寸晶圓廠正慶祝制造8英寸晶圓20周年。1997年,Mountain Top點(diǎn)開設(shè)了一個(gè)新建的8英寸

2018-10-25 08:57:58

`晶圓制造總的工藝流程芯片的制造過程可概分為晶圓處理工序(Wafer Fabrication)、晶圓針測工序(Wafer Probe)、構(gòu)裝工序(Packaging)、測試工序(Initial

2011-12-01 15:43:10

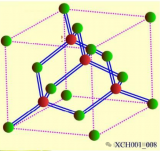

圓比人造鉆石便宜多了,感覺還是很劃算的。硅的純化I——通過化學(xué)反應(yīng)將冶金級硅提純以生成三氯硅烷硅的純化II——利用西門子方法,通過三氯硅烷和氫氣反應(yīng)來生產(chǎn)電子級硅 二、制造晶棒晶體硅經(jīng)過高溫成型,采用

2019-09-17 09:05:06

`微晶片制造的四大基本階段:晶圓制造(材料準(zhǔn)備、長晶與制備晶圓)、積體電路制作,以及封裝。晶圓制造過程簡要分析[hide][/hide]`

2011-12-01 13:40:36

在硅晶圓被蝕刻入的晶體管起不了任何作用,這一切是由于制造技術(shù)限制而造成的,任何一個(gè)存在上面問題的芯片將因不能正常工作而被報(bào)廢。上圖中,一塊硅晶圓中蝕刻了16個(gè)晶體管,但其中4個(gè)晶體管存在缺陷,因此我們

2011-12-01 16:16:40

效率高,它以圓片形式的批量生產(chǎn)工藝進(jìn)行制造,一次完成整個(gè)晶圓芯片的封裝大大提高了封裝效率。 2)具有倒裝芯片封裝的優(yōu)點(diǎn),即輕,薄,短,小。封裝尺寸接近芯片尺寸,同時(shí)也沒有管殼的高度限制。 3)封裝芯片

2021-02-23 16:35:18

本人想了解下晶圓制造會用到哪些生產(chǎn)輔材或生產(chǎn)耗材

2017-08-24 20:40:10

` 硅是由石英沙所精練出來的,晶圓便是硅元素加以純化(99.999%),接著是將些純硅制成硅晶棒,成為制造積體電路的石英半導(dǎo)體的材料,經(jīng)過照相制版,研磨,拋光,切片等程序,將多晶硅融解拉出單晶硅晶棒

2011-09-07 10:42:07

測試晶格:指晶圓表面具有電路元件及特殊裝置的晶格,在晶圓制造期間,這些測試晶格需要通過電流測試,才能被切割下來 4 邊緣晶格:晶圓制造完成后,其邊緣會產(chǎn)生部分尺寸不完整的晶格,此即為邊緣晶格,這些

2011-12-01 15:30:07

晶圓級封裝技術(shù)源自于倒裝芯片。晶圓級封裝的開發(fā)主要是由集成器件制造廠家(IBM)率先啟動。1964年,美國IBM公司在其M360計(jì)算器中最先采用了FCOB焊料凸點(diǎn)倒裝芯片器件。

2020-03-06 09:02:23

不良品,則點(diǎn)上一點(diǎn)紅墨水,作為識別之用。除此之外,另一個(gè)目的是測試產(chǎn)品的良率,依良率的高低來判斷晶圓制造的過程是否有誤。良品率高時(shí)表示晶圓制造過程一切正常, 若良品率過低,表示在晶圓制造的過程中,有

2020-05-11 14:35:33

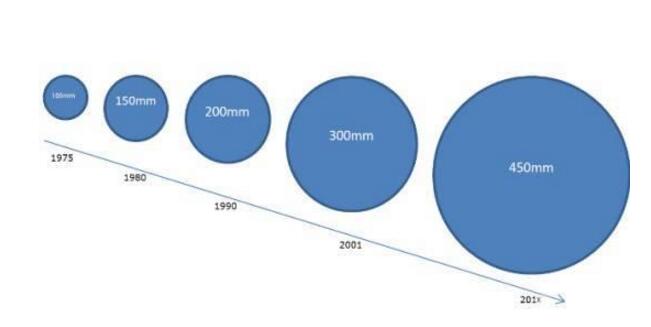

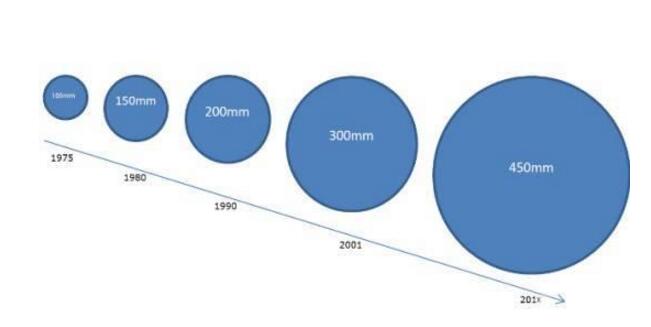

而現(xiàn)在正轉(zhuǎn)向450mm(18英寸)領(lǐng)域。更大直徑的晶圓是由不斷降低芯片成本的要求驅(qū)動的。這對晶體制備的挑戰(zhàn)是巨大的。在晶體生長中,晶體結(jié)構(gòu)和電學(xué)性能的一致性及污染問題是一個(gè)挑戰(zhàn)。在晶圓制備、平坦性

2018-07-04 16:46:41

納米到底有多細(xì)微?什么晶圓?如何制造單晶的晶圓?

2021-06-08 07:06:42

。二氧化硅礦石經(jīng)由電弧爐提煉,鹽酸氯化,并經(jīng)蒸餾后,制成了高純度的多晶硅,其純高達(dá)99.999999999%。晶圓制造廠再把此多晶硅融解,再于融液里種入籽晶,然后將其慢慢拉出,以形成圓柱狀的單晶硅晶棒

2011-12-01 11:40:04

的晶粒時(shí),標(biāo)有記號的不合格晶粒會被洮汰,不再進(jìn)行下一個(gè)制程,以免徒增制造成本。在晶圓制造完成之后,晶圓測試是一步非常重要的測試。這步測試是晶圓生產(chǎn)過程的成績單。在測試過程中,每一個(gè)芯片的電性能力和電路

2011-12-01 13:54:00

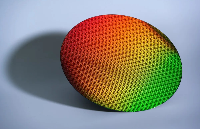

半導(dǎo)體

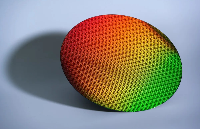

晶圓(晶片)的直徑為4到10英寸(10.16到25.4厘米)的圓盤,在

制造過程

中可承載非本征半導(dǎo)體。它們是正(P)型半導(dǎo)體或負(fù)(N)型半導(dǎo)體的臨時(shí)形式。硅晶片是非常常見的半導(dǎo)體晶片,因?yàn)楣?/div>

2021-07-23 08:11:27

單晶的晶圓制造步驟是什么?

2021-06-08 06:58:26

今日分享晶圓制造過程中的工藝及運(yùn)用到的半導(dǎo)體設(shè)備。晶圓制造過程中有幾大重要的步驟:氧化、沉積、光刻、刻蝕、離子注入/擴(kuò)散等。這幾個(gè)主要步驟都需要若干種半導(dǎo)體設(shè)備,滿足不同的需要。設(shè)備中應(yīng)用較為廣泛

2018-10-15 15:11:22

過處理之后成為光罩 這些就是最后完成的晶圓成品 接下來看晶圓切割 形成成品之后的晶圓還要經(jīng)過切割才能成為應(yīng)用于芯片制造。 這里演示的就是晶圓切割 放大觀看 接下來是演示經(jīng)過切割的晶圓的一些應(yīng)用。 可以應(yīng)用于芯片制造、液晶顯示屏制造或者手機(jī)芯片制造等。 ``

2011-12-01 15:02:42

`什么是硅晶圓呢,硅晶圓就是指硅半導(dǎo)體積體電路制作所用的硅晶片。晶圓是制造IC的基本原料。硅晶圓和晶圓有區(qū)別嗎?其實(shí)二者是一個(gè)概念。集成電路(IC)是指在一半導(dǎo)體基板上,利用氧化、蝕刻、擴(kuò)散等方法

2011-12-02 14:30:44

從硅晶圓的制備到晶圓IC的制造,每一步都對工藝流程的質(zhì)量有著嚴(yán)格的管控要求,作為產(chǎn)品表面質(zhì)量檢測儀器的光學(xué)3D表面輪廓儀,以其高檢測精度和高重復(fù)性,發(fā)揮著重要的作用。 中圖儀器

2022-05-16 16:18:36

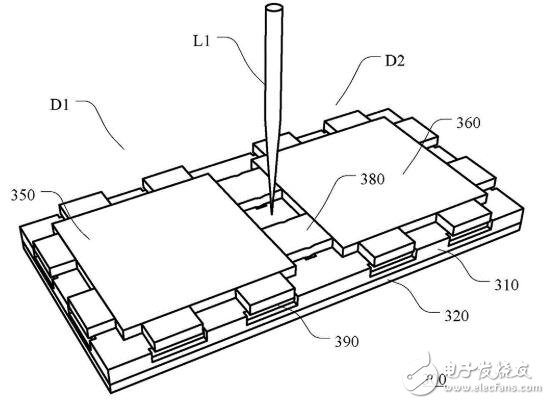

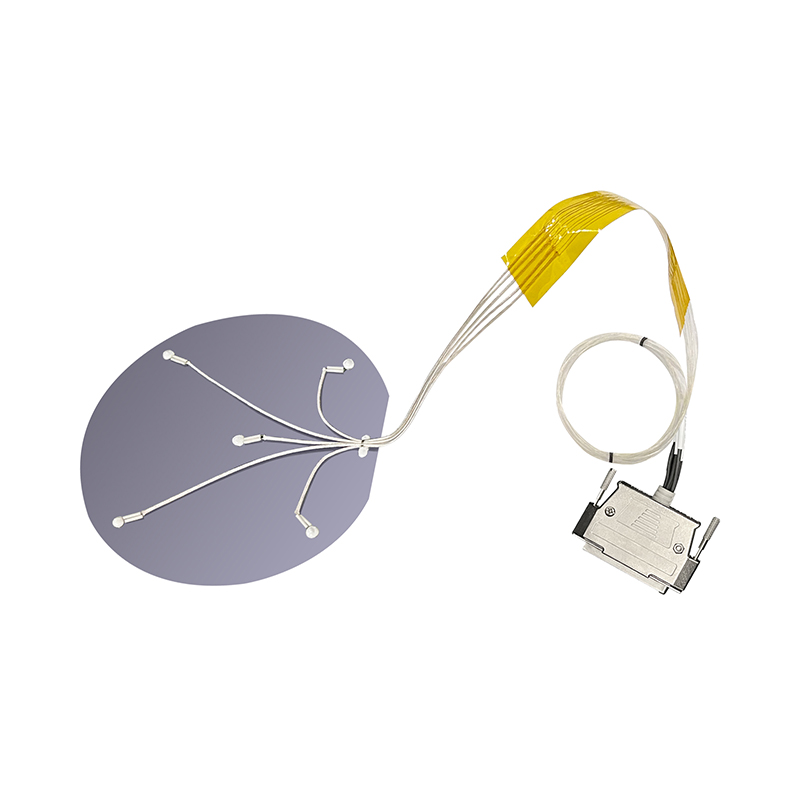

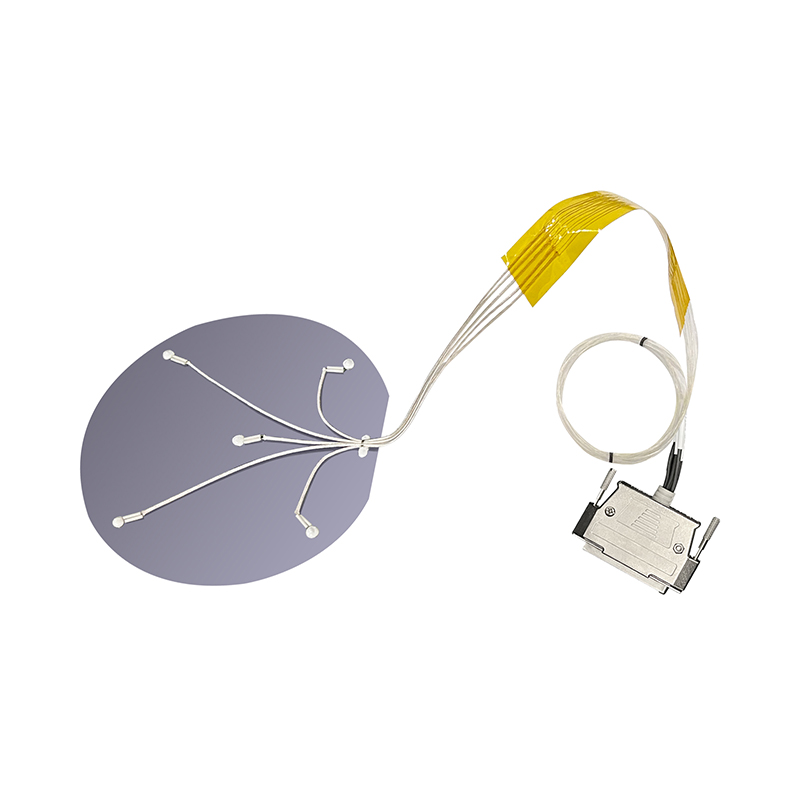

晶圓測溫系統(tǒng),晶圓測溫?zé)犭娕迹?b class="flag-6" style="color: red">晶圓測溫裝置一、引言隨著半導(dǎo)體技術(shù)的不斷發(fā)展,晶圓制造工藝對溫度控制的要求越來越高。熱電偶作為一種常用的溫度測量設(shè)備,在晶圓制造中具有重要的應(yīng)用價(jià)值。本文

2023-06-30 14:57:40

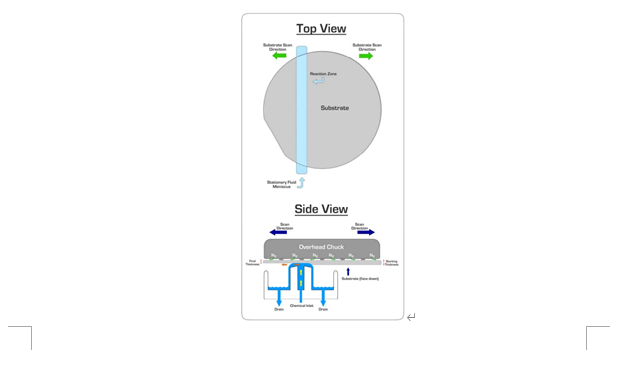

在半導(dǎo)體制造的精密流程中,晶圓濕法清洗設(shè)備扮演著至關(guān)重要的角色。它不僅是芯片生產(chǎn)的基礎(chǔ)工序,更是決定良率、效率和成本的核心環(huán)節(jié)。本文將從技術(shù)原理、設(shè)備分類、行業(yè)應(yīng)用到未來趨勢,全面解析這一關(guān)

2025-06-25 10:26:37

英飛凌科技(Infineon Technologies)宣布已于奧地利菲拉赫(Villach)據(jù)點(diǎn)生產(chǎn)出首款 300mm (12寸)薄晶圓之功率半導(dǎo)體晶片(first silicon),成為全球首家進(jìn)一步成功采用此技術(shù)的公司。采用300mm薄晶圓

2011-10-14 09:51:43 1352

1352 晶圓是微電子產(chǎn)業(yè)的行業(yè)術(shù)語之一。

2017-12-07 15:41:11 41079

41079 晶圓制造總的工藝流程 芯片的制造過程可概分為晶圓處理工序(Wafer Fabrication)、晶圓針測工序(Wafer Probe)、構(gòu)裝工序(Packaging)、測試工序(Initial Test and Final Test)等幾個(gè)步驟。

2018-04-16 11:27:00 15246

15246 本文開始介紹了晶圓的概念和晶圓的制造過程,其次詳細(xì)的闡述了晶圓的基本原料,最后介紹了晶圓尺寸的概念及分析了晶圓的尺寸是否越大越好。

2018-03-16 14:50:23 147635

147635

新型鍵合材料對于在高級半導(dǎo)體制造工藝中保持超薄晶圓的完整性至關(guān)重要。有了新型材料的配合,臨時(shí)鍵合在晶圓減薄工藝中愈發(fā)成為可能。

2018-06-25 16:48:00 10821

10821

本文首先介紹了什么是晶圓,其次詳細(xì)的闡述了晶圓制造的14個(gè)步驟流程。

2018-08-21 17:12:46 51697

51697 根據(jù)芯思想研究院的統(tǒng)計(jì),截止2018年底我國12英寸晶圓制造廠裝機(jī)產(chǎn)能約60萬片;8英寸晶圓制造廠裝機(jī)產(chǎn)能約90萬片;6英寸晶圓制造廠裝機(jī)產(chǎn)能約200萬片;5英寸晶圓制造廠裝機(jī)產(chǎn)能約90萬片;4英寸晶圓制造廠裝機(jī)產(chǎn)能約200萬片。

2019-02-21 17:59:01 26721

26721 本文主要介紹了晶圓的結(jié)構(gòu),其次介紹了晶圓切割工藝,最后介紹了晶圓的制造過程。

2019-05-09 11:15:54 12824

12824

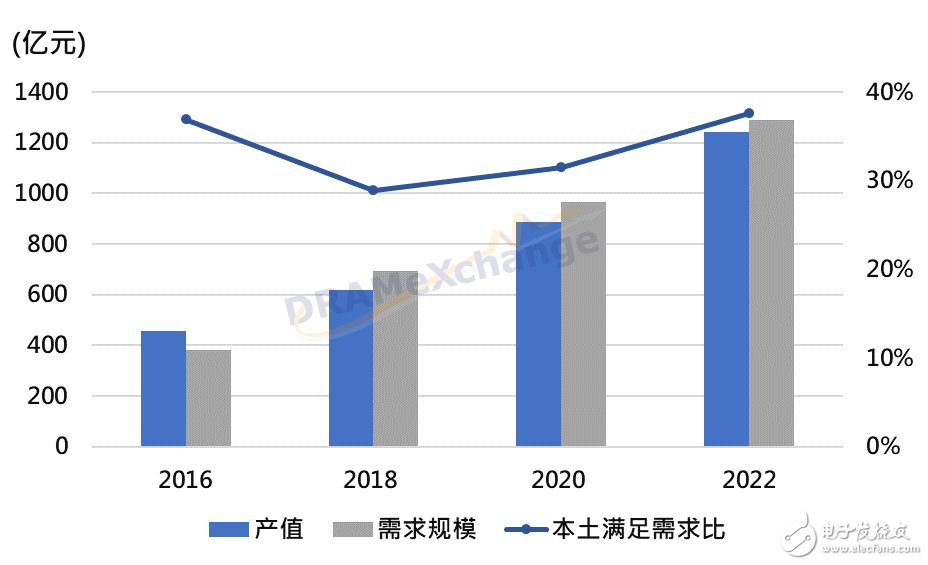

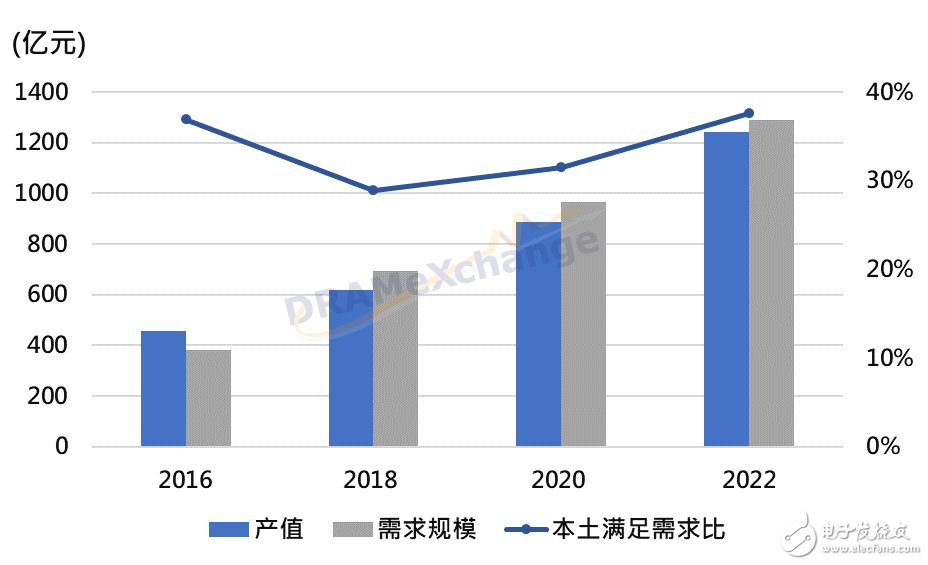

近年來隨著國家集成電路規(guī)劃的持續(xù)推進(jìn),各地紛紛上馬晶圓制造項(xiàng)目,在大量項(xiàng)目不斷落地的同時(shí),對“中國晶圓制造產(chǎn)能過剩”的擔(dān)憂言論也開始出現(xiàn),中國的晶圓制造產(chǎn)能是否會出現(xiàn)產(chǎn)能過剩?或者在進(jìn)行國產(chǎn)替代的大背景下該如何擴(kuò)充晶圓制造產(chǎn)能?從產(chǎn)業(yè)和市場的趨勢去看,或許可以得到一些答案。

2019-07-31 15:36:54 3940

3940

晶圓的制造在半導(dǎo)體領(lǐng)域,科技含量相當(dāng)?shù)母撸夹g(shù)工藝要求非常高。而我們國半導(dǎo)體事業(yè)起步較晚,在晶圓的制造上還處于建設(shè)發(fā)展階段。現(xiàn)在我國主要做的是晶圓的封測。我國的晶圓封測規(guī)模和市場都是全球首屈一指的,約占全球約1/4。

2019-08-12 14:13:00 48168

48168 顆粒體為單位切成單獨(dú)的晶顆粒體時(shí),標(biāo)著標(biāo)記的不過關(guān)晶顆粒體會被淘汰,不會再開展下一個(gè)制造,以減少不比較的制造成本。 在晶圓制造完成以后,晶圓檢測是一步十分關(guān)鍵的檢測。這步檢測是晶圓生產(chǎn)過程的成績表。在檢測全過程中,每

2021-03-24 14:57:59 15755

15755 晶圓的重要性不言而喻,因此我們需要對晶圓具備一定的認(rèn)識。前兩篇文章中,小編對晶圓到CPU的轉(zhuǎn)換過程、晶圓和硅片的區(qū)別有所探討。為增進(jìn)大家對晶圓的了解程度,本文將對晶圓制造業(yè)的特點(diǎn)予以闡述。如果你對晶圓具有興趣,不妨繼續(xù)往下閱讀哦。

2020-12-26 11:25:04 6002

6002 隨5G、物聯(lián)網(wǎng)、電動車蓬勃發(fā)展,對于低功耗要求越來越高,功率半導(dǎo)體成為這些產(chǎn)業(yè)勢不可擋的必備組件。宜特(TWSE: 3289)晶圓后端工藝廠的晶圓減薄能力也隨之精進(jìn)。宜特今(1/6)宣布,晶圓后端

2021-01-07 18:03:20 4433

4433 在本文中,我們?nèi)A林科納半導(dǎo)體將專注于一種新的化學(xué)變薄技術(shù),該技術(shù)允許晶圓變薄到50μm或更少,均勻性更好,比傳統(tǒng)的變薄成本更低。我們還將討論處理無任何類型晶圓載體的薄晶圓的方法。

2022-03-18 14:11:36 1602

1602

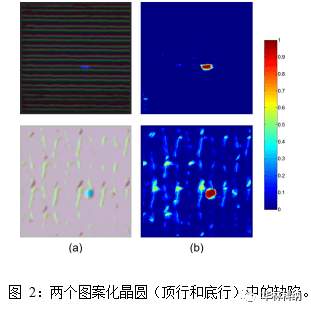

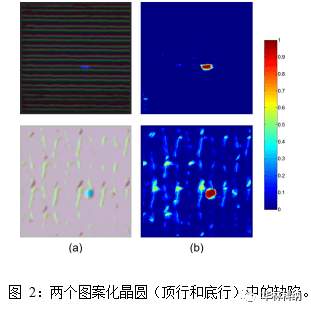

幾何結(jié)構(gòu)引起的背景分離。在本文中,我們將算法擴(kuò)展到多通道晶圓缺陷檢測中的 3D 數(shù)據(jù)。我們在一組半導(dǎo)體晶片上測試了我們的算法,并證明了我們的多尺度多通道算法與單尺度和單通道方法相比具有卓越的性能。

2022-03-22 14:15:22 2416

2416

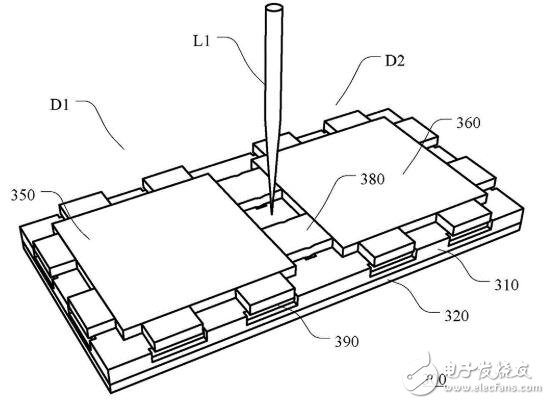

摘要 本文提出了一種用于實(shí)現(xiàn)貫穿芯片互連的包含溝槽和空腔的微機(jī)械晶片的減薄方法。通過研磨和拋光成功地使晶圓變薄,直至達(dá)到之前通過深度反應(yīng)離子蝕刻蝕刻的空腔。研究了腐蝕結(jié)構(gòu)損壞的可能原因。研究了空腔中

2022-03-25 17:03:30 4050

4050

晶圓薄化是實(shí)現(xiàn)集成電路小型化的主要工藝步驟,硅片背面磨至70微米的厚度被認(rèn)為是非常關(guān)鍵的,因?yàn)樗艽嗳酢1疚膶⒂懻撽P(guān)鍵設(shè)備檢查項(xiàng)目的定義和設(shè)置險(xiǎn)。 所涉及的設(shè)備是內(nèi)聯(lián)晶圓背面研磨和晶圓安裝。本研究

2022-03-31 14:58:24 5901

5901

一整大片的晶圓,需要對它進(jìn)行劃片和處理,這時(shí)候晶圓劃片機(jī)的價(jià)值就體現(xiàn)出了。之所以晶圓需要變換尺寸,是為了制作更復(fù)雜的集成電路。

10、晶圓減薄機(jī)

在硅晶圓制造中,對晶片的尺寸精度、幾何精度、表面

2022-04-02 15:47:49 6608

6608 半導(dǎo)體集成電路是在晶圓的薄基板的基礎(chǔ)上,通過制造多個(gè)相同電路而產(chǎn)生的。如同制作披薩時(shí)添加配料之前先做面團(tuán)一樣,晶圓作為半導(dǎo)體的基礎(chǔ),是指將硅(Si)、砷化鎵(GaAs)等生成的單晶柱切成薄片的圓盤。

2022-12-16 10:05:41 5391

5391 半導(dǎo)體集成電路是將許多元件集成到一個(gè)芯片中以處理和存儲各種功能的電子組件。由于半導(dǎo)體集成電路是通過在晶圓的薄基板上制造多個(gè)相同電路而產(chǎn)生的,因此晶圓是半導(dǎo)體的基礎(chǔ),就像制作披薩時(shí)添加配料之前先做面團(tuán)一樣。

2023-01-11 10:28:01 6502

6502 晶圓制造和芯片制造是半導(dǎo)體行業(yè)中兩個(gè)非常重要的環(huán)節(jié),它們雖然緊密相連,但是卻有一些不同之處。下面我們來詳細(xì)介紹晶圓制造和芯片制造的區(qū)別。

2023-06-03 09:30:44 20573

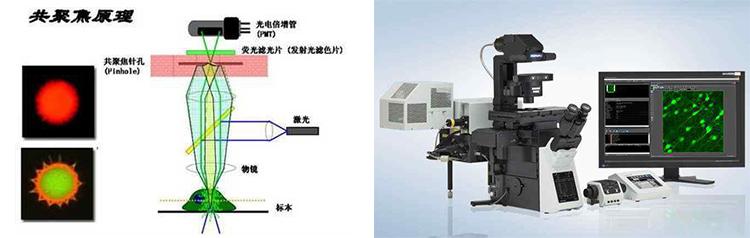

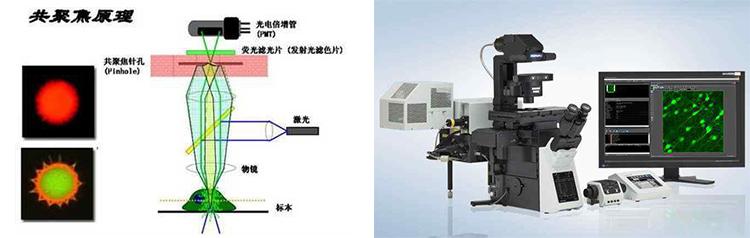

20573 激光共聚焦顯微鏡來實(shí)現(xiàn)晶圓質(zhì)量檢測,幫助改善制造工藝,提高良品率。注:圖片來源于網(wǎng)絡(luò) 激光共聚焦顯微鏡以激光作為光源,采用共軛聚焦裝置,激光束經(jīng)照明針孔,經(jīng)由分光鏡反射至物鏡,并通過壓電物鏡定位器帶載物鏡進(jìn)行精密定位調(diào)

2023-06-15 10:05:11 1593

1593

鍍銀晶圓的材料特性晶圓經(jīng)過背面研磨減薄后,經(jīng)由背面蒸鍍金屬,切片加工而成的芯片將在器件熱阻降低、工作散熱和冷卻、封裝厚度減薄等各個(gè)方面實(shí)現(xiàn)很大的改善。在晶圓背面金屬化過程中,一般選擇鈦、鎳、銀作為

2022-08-19 09:23:32 3175

3175

在封裝前,通常要減薄晶圓,減薄晶圓主要有四種主要方法:機(jī)械磨削、化學(xué)機(jī)械研磨、濕法蝕刻和等離子體干法化學(xué)蝕刻。

2024-01-26 09:59:27 7328

7328

芯片堆疊封裝存在著4項(xiàng)挑戰(zhàn),分別為晶圓級對準(zhǔn)精度、鍵合完整性、晶圓減薄與均勻性控制以及層內(nèi)(層間)互聯(lián)。

2024-02-21 13:58:34 9340

9340

“TC WAFER 晶圓測溫系統(tǒng)”似乎是一種用于測量晶圓(半導(dǎo)體制造中的基礎(chǔ)材料)溫度的系統(tǒng)。在半導(dǎo)體制造過程中,晶圓溫度的控制至關(guān)重要,因?yàn)樗苯佑绊懙?b class="flag-6" style="color: red">制造出的芯片的質(zhì)量和性能。因此,準(zhǔn)確的晶圓

2024-03-08 17:58:26 1964

1964

厚度的增加雖然提高了晶圓的穩(wěn)定性,但同時(shí)也帶來了新的挑戰(zhàn),如熱管理問題和加工難度增加。更厚的晶圓意味著在制造過程中,熱量的分布可能更不均勻,這可能會影響到晶圓上芯片的制造質(zhì)量。

2024-03-25 10:16:17 3707

3707

的容量和功能。在過去的幾十年中,基于薄晶圓 ( 通常厚度小于 100 μm) 的硅穿孔(Through-Silicon Via,TSV) 技術(shù)已經(jīng)實(shí)現(xiàn)了 3D-IC 封裝。但是由于薄晶圓的易碎性和易翹曲的傾向,在對器件晶圓進(jìn)行背部加工過程中,需要利用膠粘劑將其固定在載體上,并使薄晶圓在背部

2024-03-29 08:37:59 2196

2196 以下是關(guān)于碳化硅晶圓和硅晶圓的區(qū)別的分析: 材料特性: 碳化硅(SiC)是一種寬禁帶半導(dǎo)體材料,具有比硅(Si)更高的熱導(dǎo)率、電子遷移率和擊穿電場。這使得碳化硅晶圓在高溫、高壓和高頻應(yīng)用中具有優(yōu)勢

2024-08-08 10:13:17 4711

4711 電子發(fā)燒友網(wǎng)站提供《2.5薄型晶圓組件90°彎曲.pdf》資料免費(fèi)下載

2024-09-03 14:21:52 0

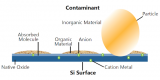

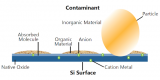

0 晶圓表面潔凈度會極大的影響后續(xù)半導(dǎo)體工藝及產(chǎn)品的合格率。在所有產(chǎn)額損失中,高達(dá)50%是源自于晶圓表面污染。 能夠?qū)е缕骷姎庑阅芑蚱骷?b class="flag-6" style="color: red">制造過程發(fā)生不受控制的變化的物體統(tǒng)稱為污染物。污染物可能來自晶圓

2024-11-21 16:33:47 3024

3024

改善晶圓出刀TTV(Total Thickness Variation,總厚度變化量)異常的加工方法主要包括以下幾種:

一、設(shè)備調(diào)整與優(yōu)化

主軸與承片臺角度調(diào)整

通過設(shè)備自動控制,進(jìn)行工藝角度調(diào)整

2024-12-05 16:51:26 595

595

和基本概念 T/R(Turn Ratio),在晶圓制造領(lǐng)域中,指的是在制品的周轉(zhuǎn)率,即每片晶圓平均每天經(jīng)過的工藝步驟(Stage)的數(shù)量。它是衡量生產(chǎn)線效率、工藝設(shè)計(jì)合理性和生產(chǎn)進(jìn)度的重要指標(biāo)之一。 ? ? 在實(shí)際制造過程中,晶圓需要依次通過多個(gè)工藝步驟,例如光刻、刻

2024-12-17 11:34:56 2617

2617 半導(dǎo)體晶圓制造是現(xiàn)代電子產(chǎn)業(yè)中不可或缺的一環(huán),它是整個(gè)電子行業(yè)的基礎(chǔ)。這項(xiàng)工藝的流程非常復(fù)雜,包含了很多步驟和技術(shù),下面將詳細(xì)介紹其主要的制造工藝流程。第一步:晶圓生長晶圓生長是半導(dǎo)體制造的第一步

2024-12-24 14:30:56 5110

5110

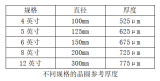

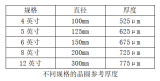

300mm晶圓的厚度為775um,200mm晶圓的度為725um,這個(gè)厚度在實(shí)際封裝時(shí)太厚了。前段制程中晶圓要被處理、要在設(shè)備內(nèi)和設(shè)備間傳送,這時(shí)候上面提到的厚度是合適的,可以滿足機(jī)械強(qiáng)度的要求

2024-12-24 17:58:45 1819

1819 晶圓是集成電路、功率器件及半導(dǎo)體分立器件的核心原材料,超過90%的集成電路均在高純度、高品質(zhì)的晶圓上制造而成。晶圓的質(zhì)量及其產(chǎn)業(yè)鏈供應(yīng)能力,直接關(guān)乎集成電路的整體性能和競爭力。今天我們將詳細(xì)介紹

2025-01-09 09:59:26 2107

2107

晶圓,作為芯片制造的基礎(chǔ)載體,其表面平整度對于后續(xù)芯片制造工藝的成功與否起著決定性作用。

2025-01-24 10:06:02 2192

2192 芯片制造的畫布 芯片制造的畫布:晶圓的奧秘與使命 在芯片制造的宏大舞臺上,晶圓(Wafer)扮演著至關(guān)重要的角色。它如同一張潔白的畫布,承載著無數(shù)工程師的智慧與夢想,見證著從砂礫到智能的奇跡之旅。晶

2025-03-10 17:04:25 1547

1547 本文介紹了半導(dǎo)體集成電路制造中的晶圓制備、晶圓制造和晶圓測試三個(gè)關(guān)鍵環(huán)節(jié)。

2025-04-15 17:14:37 2168

2168

在半導(dǎo)體制造流程中,晶圓在前端工藝階段需保持一定厚度,以確保其在流片過程中的結(jié)構(gòu)穩(wěn)定性,避免彎曲變形,并為芯片制造工藝提供操作便利。不同規(guī)格晶圓的原始厚度存在差異:4英寸晶圓厚度約為520微米,6

2025-05-09 13:55:51 1979

1979 前言在半導(dǎo)體制造的前段制程中,晶圓需要具備足夠的厚度,以確保其在流片過程中的結(jié)構(gòu)穩(wěn)定性。盡管芯片功能層的制備僅涉及晶圓表面幾微米范圍,但完整厚度的晶圓更有利于保障復(fù)雜工藝的順利進(jìn)行,直至芯片前制程

2025-05-16 16:58:44 1110

1110

半導(dǎo)體行業(yè)是現(xiàn)代制造業(yè)的核心基石,被譽(yù)為“工業(yè)的糧食”,而晶圓是半導(dǎo)體制造的核心基板,其質(zhì)量直接決定芯片的性能、良率和可靠性。晶圓隱裂檢測是保障半導(dǎo)體良率和可靠性的關(guān)鍵環(huán)節(jié)。晶圓檢測通過合理搭配工業(yè)

2025-05-23 16:03:17 648

648

“減薄”,也叫 Back Grinding(BG),是將晶圓(Wafer)背面研磨至目標(biāo)厚度的工藝步驟。這個(gè)過程通常發(fā)生在芯片完成前端電路制造、被切割前(即晶圓仍然整體時(shí)),是連接芯片制造和封裝之間的橋梁。

2025-05-30 10:38:52 1661

1661 晶圓檢測是指在晶圓制造完成后,對晶圓進(jìn)行的一系列物理和電學(xué)性能的測試與分析,以確保其質(zhì)量和性能符合設(shè)計(jì)要求。這一過程是半導(dǎo)體制造中的關(guān)鍵環(huán)節(jié),直接影響后續(xù)封裝和芯片的良品率。 隨著圖形化和幾何結(jié)構(gòu)

2025-06-06 17:15:28 718

718

Wafer Acceptance Test (WAT) 是晶圓制造中確保產(chǎn)品質(zhì)量和可靠性的關(guān)鍵步驟。它通過對晶圓上關(guān)鍵參數(shù)的測量和分析,幫助識別工藝中的問題,并為良率提升提供數(shù)據(jù)支持。在芯片項(xiàng)目的量產(chǎn)管理中,WAT是您保持產(chǎn)線穩(wěn)定性和產(chǎn)品質(zhì)量的重要工具。

2025-07-17 11:43:31 2781

2781 尺寸與清洗

挑戰(zhàn)小尺寸

晶圓(2-6英寸)特點(diǎn):面積小、厚度較

薄(如2英寸

晶圓厚度約500μm),機(jī)械強(qiáng)度低,易受流體沖擊損傷。

挑戰(zhàn):清洗槽體積較小,易因流體不均勻?qū)е?/div>

2025-07-22 16:51:19 1332

1332

劃片機(jī)(DicingSaw)在生物晶圓芯片的制造中扮演著至關(guān)重要的角色,尤其是在實(shí)現(xiàn)高精度切割方面。生物晶圓芯片通常指在硅、玻璃、石英、陶瓷或聚合物(如PDMS)等基片上制造的,用于生物檢測、診斷

2025-07-28 16:10:29 713

713

退火工藝是晶圓制造中的關(guān)鍵步驟,通過控制加熱和冷卻過程,退火能夠緩解應(yīng)力、修復(fù)晶格缺陷、激活摻雜原子,并改善材料的電學(xué)和機(jī)械性質(zhì)。這些改進(jìn)對于確保晶圓在后續(xù)加工和最終應(yīng)用中的性能和可靠性至關(guān)重要。退火工藝在晶圓制造過程中扮演著至關(guān)重要的角色。

2025-08-01 09:35:23 2036

2036

在晶圓加工流程中,早期檢測宏觀缺陷是提升良率與推動工藝改進(jìn)的核心環(huán)節(jié),這一需求正驅(qū)動檢測技術(shù)與晶圓測試圖分析領(lǐng)域的創(chuàng)新。宏觀缺陷早期檢測的重要性與挑戰(zhàn)在晶圓層面,一個(gè)宏觀缺陷可能影響多個(gè)芯片,甚至在

2025-08-19 13:48:23 1120

1120

半導(dǎo)體制造工藝中,經(jīng)晶棒切割后的硅晶圓尺寸檢測,是保障后續(xù)制程精度的核心環(huán)節(jié)。共聚焦顯微鏡憑借其高分辨率成像能力與無損檢測特性,成為檢測過程的關(guān)鍵分析工具。下文,光子灣科技將詳解共聚焦顯微鏡檢測硅晶

2025-10-14 18:03:26 448

448

在超高純度晶圓制造過程中,盡管晶圓本身需達(dá)到11個(gè)9(99.999999999%)以上的純度標(biāo)準(zhǔn)以維持基礎(chǔ)半導(dǎo)體特性,但為實(shí)現(xiàn)集成電路的功能化構(gòu)建,必須通過摻雜工藝在硅襯底表面局部引入特定雜質(zhì)。

2025-10-29 14:21:31 623

623

在半導(dǎo)體制造中,晶圓切割是決定芯片良率的關(guān)鍵一步。面對切割道檢測中的重重挑戰(zhàn),如何實(shí)現(xiàn)精準(zhǔn)定位與高效檢測?本文將深入解析高低雙倍率視覺系統(tǒng)的創(chuàng)新解決方案,助您攻克技術(shù)難點(diǎn),切實(shí)提升生產(chǎn)效能。

2025-11-25 16:54:12 703

703

在半導(dǎo)體制造過程中,晶圓檢測是確保芯片質(zhì)量與性能的核心環(huán)節(jié)。隨著工藝精度的不斷提升,晶圓溫度對檢測結(jié)果的影響日益凸顯。熱電偶溫度監(jiān)測技術(shù)因其高靈敏度和實(shí)時(shí)性,被廣泛應(yīng)用于晶圓檢測環(huán)境中,用于實(shí)時(shí)監(jiān)控

2025-11-27 10:07:18 387

387

已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論