隨5G、物聯網、電動車蓬勃發展,對于低功耗要求越來越高,功率半導體成為這些產業勢不可擋的必備組件。宜特(TWSE: 3289)晶圓后端工藝廠的晶圓減薄能力也隨之精進。宜特今(1/6)宣布,晶圓后端工藝廠(竹科二廠),通過客戶肯定,成功開發晶圓減薄達1.5mil(38um)技術,技術門坎大突破。同時,為更專注服務國際客戶,即日起成立宜錦股份有限公司(Prosperity Power Technology Inc)。

使用控片測得2mil、1.5 mil、1.5 mil優化條件后的損壞層厚度及TEM分析宜特指出,功率半導體進行“減薄”,一直都是改善工藝,使得功率組件實現“低功耗、低輸入阻抗”最直接有效的方式。晶圓減薄除了有效減少后續封裝材料體積外,還可因降低RDS(on)(導通阻抗)進而減少熱能累積效應,以增加芯片的使用壽命。

但如何在減薄工藝中降低晶圓厚度,又同時兼顧晶圓強度,避免破片率居高不下之風險自晶圓減薄最大的風險。

為解決此風險,iST宜特領先業界,已完成2mil(50um)、1.5mil(38um),甚至到0.4mil(10um)減薄技術開發,iST宜特更藉由特殊的優化工藝,在降低晶圓厚度的同時,也兼顧晶圓強度,可將研磨損傷層(Damage layer)降到最低。

責任編輯:xj

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

半導體

+關注

關注

339文章

30725瀏覽量

264032 -

晶圓

+關注

關注

53文章

5408瀏覽量

132280 -

宜特科技

+關注

關注

0文章

5瀏覽量

8906

發布評論請先 登錄

相關推薦

熱點推薦

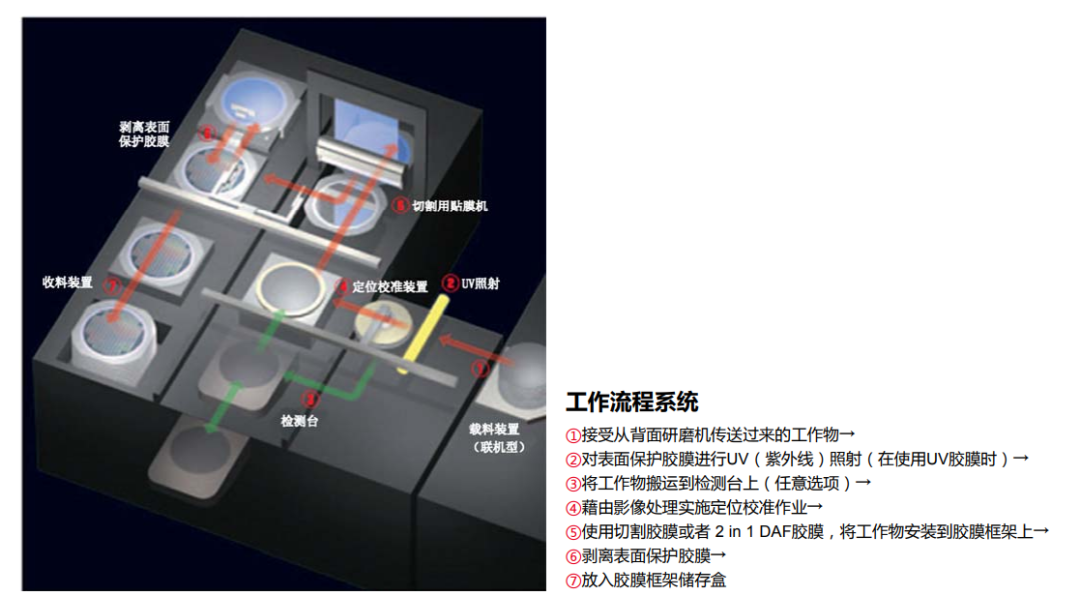

晶圓減薄工藝分為哪幾步

“減薄”,也叫 Back Grinding(BG),是將晶圓(Wafer)背面研磨至目標厚度的工藝步驟。這個過程通常發生在芯片完成前端電路制造、被切割前(即

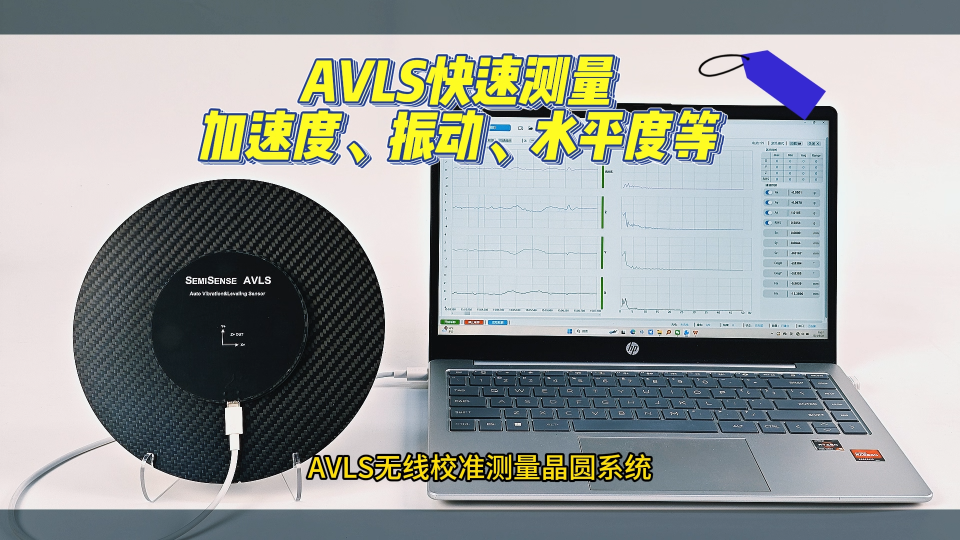

wafer晶圓厚度(THK)翹曲度(Warp)彎曲度(Bow)等數據測量的設備

通過退火優化和應力平衡技術控制。

3、彎曲度(Bow) 源于材料與工藝的對稱性缺陷,對多層堆疊和封裝尤為敏感,需在晶體生長和鍍膜工藝中嚴格調控。

在先進制程中,三者共同決定了晶圓的幾何完整性,是良率提升

發表于 05-28 16:12

宜特晶圓:成功開發晶圓減薄達1.5mil(38um)技術

宜特晶圓:成功開發晶圓減薄達1.5mil(38um)技術

評論