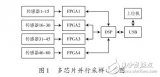

提出一種基于FPGA技術(shù)的多路數(shù)字量采集模塊,利用FPGA的I/O端口數(shù)多且可編程設(shè)置的特點,配以VHDL編寫的 FPGA內(nèi)部邏輯,實現(xiàn)采集多路數(shù)字量信號。

2015-05-15 12:09:29 4721

4721 利用FPGA實現(xiàn)雙口RAM的設(shè)計及應(yīng)用

概述:為了在高速采集時不丟失數(shù)據(jù),在數(shù)據(jù)采集系統(tǒng)和

2010-04-16 14:08:36 11881

11881

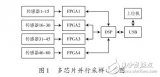

本文提出了一種基于FPGA的多路光柵信號采集方案,該方案使用I/O口相對較少的低端FPGA,配合多路選擇開關(guān),通過內(nèi)部處理,實現(xiàn)了多路光柵信號的采集,結(jié)果表明,該方案成本低廉且能滿足精度的要求。

2013-12-30 13:35:40 3125

3125

如今的移動系統(tǒng)設(shè)計常常包含使用顯示屏串行接口(DSI)的LCD顯示屏和采用攝像頭串行接口(CSI-2)的攝像頭圖像傳感器,利用超低密度(ULD)fpga橋接MIPI DSI和CSI-2接口到大量的傳統(tǒng)總線。這些低成本、低功耗的fpga產(chǎn)品和MIPI參考設(shè)計被設(shè)計用來構(gòu)建一個理想的橋接芯片.

2016-10-27 17:02:15 10071

10071

本文介紹如何利用FPGA和DMA技術(shù)處理來自AD9280和AD9708 ADC的數(shù)據(jù)。首先,探討了這兩種ADC的特點及其與FPGA的接口兼容性。接著,詳細說明了使用Xilinx VIVADO環(huán)境下

2025-07-29 14:12:22 4847

4847 本篇將詳細介紹如何利用Verilog HDL在FPGA上實現(xiàn)SRAM的讀寫測試。SRAM是一種非易失性存儲器,具有高速讀取和寫入的特點。在FPGA中實現(xiàn)SRAM讀寫測試,包括設(shè)計SRAM接口模塊

2025-10-22 17:21:38 4118

4118

DSP技術(shù)廣泛應(yīng)用于各個領(lǐng)域,但傳統(tǒng)的數(shù)字信號處理器由于以順序方式工作使得數(shù)據(jù)處理速度較低,且在功能重構(gòu)及應(yīng)用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現(xiàn)數(shù)字信號處理系統(tǒng),具有很強的實時性和靈活性,因此利用FPGA實現(xiàn)數(shù)字信號處理成為數(shù)字信號處理領(lǐng)域的一種新的趨勢。

2019-10-17 08:12:27

實現(xiàn)多路信號的復用;在接收機中再對其解擴,恢復原傳輸信號。利用擴頻通信的擴頻增益,可大大提高通信系統(tǒng)的信噪比,增加傳輸信號的可靠性改善通信質(zhì)量、提高通信效率。 同時 DSP具有可滿足算法控制復雜結(jié)構(gòu)

2019-07-08 08:28:48

該文檔為基于FPGA的多路模擬數(shù)據(jù)采集接口設(shè)計講解文檔,介紹一種基于 8,RQ 的多路模擬數(shù)據(jù)采集接口的設(shè)計方案。該方案使用Max1281 作為模數(shù)轉(zhuǎn)換芯片,在 APA150 FPGA 中設(shè)計和實現(xiàn)了相關(guān)的接口控制、配置和數(shù)據(jù)存儲模塊;給出了系統(tǒng)設(shè)計框圖、FPGA開發(fā)要點和仿真波形。

2018-09-21 14:37:00

,數(shù)據(jù)收發(fā)時兩根線遵循既定的時序就可以實現(xiàn)數(shù)據(jù)傳輸,如開始時序、停止時序、acquire時序、/acquire時序等等。我的方案是:利用FPGA的狀態(tài)機機制,使指定的兩端口循環(huán)執(zhí)行:開始,讀數(shù)據(jù)/寫

2012-05-16 16:08:36

申請理由:團隊針對燒結(jié)設(shè)備有多路溫度采集需求;學習Python在Linux環(huán)境下的編程、界面設(shè)計與數(shù)據(jù)分析;項目描述:實現(xiàn)功能如下:1、數(shù)據(jù)采集:模擬量采集與溫度控制器通訊2、數(shù)據(jù)傳輸:利用Wifi自組建網(wǎng)絡(luò)3、數(shù)據(jù)分析:基于Python實現(xiàn)數(shù)據(jù)可視化與數(shù)據(jù)分析,利用觸摸屏實現(xiàn)人機交互

2015-06-29 16:34:26

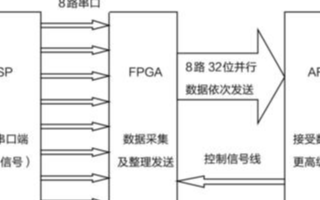

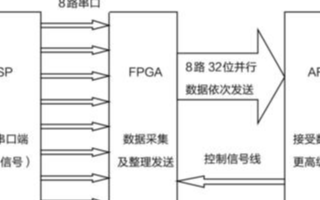

的采集,傳感器分別位于人體的頭、四肢、手、腰上,每路采樣率為200。利用ARM芯片作為系統(tǒng)主控芯片,控制FPGA采集數(shù)據(jù)的速率、啟停,并控制數(shù)據(jù)傳輸方向。為外部設(shè)備提供標準的API,方便外部設(shè)備調(diào)用

2016-08-15 17:13:19

CVSD編譯碼時則需要很多專用芯片,具有局限性;而單片FPGA容易實現(xiàn)多路CVSD編譯碼功能。此外如果專用芯片停產(chǎn)或者買不到,已有的通信設(shè)備維修將會因器件缺乏導致后續(xù)工作無法開展。為了彌補專用CVSD芯片

2019-08-07 07:04:27

在FPGA上實現(xiàn)時鐘信號的多路同步輸出該怎么做呢?好像要用到FPGA內(nèi)部的PLL,將時鐘信號分成多路輸送到其他板塊,求高手解答該怎么做輸入時鐘由一個50M的晶振提供

2023-03-21 14:51:29

時間。針對上述研究現(xiàn)狀和分布式采集場景分析,本文介紹了一種基于FPGA和TOE架構(gòu),實現(xiàn)TCP/IP協(xié)議數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">多路采集與切換系統(tǒng)。該系統(tǒng)涉及并行數(shù)據(jù)采集、多路通道切換、TCP/IP協(xié)議通信等模塊

2021-07-12 08:30:00

字信號處理、硬件數(shù)字濾波器、各種算法等,或者利用FPGA來擴展I/O接口,如實現(xiàn)多路PWM(脈寬調(diào)制)輸出、實現(xiàn)PCI接口擴展等。通過合理的系統(tǒng)軟硬件功能劃分,結(jié)合優(yōu)秀高效的FPGA設(shè)計,整個嵌入式

2019-05-06 09:18:16

1引言在許多嵌入式系統(tǒng)的實際應(yīng)用中,需要擴展FP-GA(現(xiàn)場可編程門陣列)模塊,將CPU實現(xiàn)有困難或實現(xiàn)效率低的部分用FPGA實現(xiàn),如數(shù)字信號處理、硬件數(shù)字濾波器、各種算法等,或者利用FPGA來擴展

2019-04-25 07:00:05

和實測驗證,該算法能有效快速地消除回聲;同時,該算法應(yīng)用靈活,能實現(xiàn)多路的回聲消除,在VOIP終端設(shè)備上具有較強的應(yīng)用價值和應(yīng)用前景。頁 碼:9-11頁主 題 詞:回聲消除VOIPFPGA Echo cancellationVOIPFPGA學科分類:TN91核心收錄:暫無

2018-05-08 10:23:36

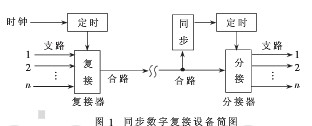

數(shù)字復分接技術(shù)是數(shù)字通信網(wǎng)中的一項重要技術(shù),能將若干路低速信號合并為一路高速信號,以提高帶寬利用率和數(shù)據(jù)傳輸效率。

2019-09-26 07:48:06

電路圖。 現(xiàn)在我們要在FPGA中實現(xiàn),二選一多路選擇命名為“mux2_1”,不要命名為mux21,mux21是quartus中默認器件庫中的名字,命名相同會出現(xiàn)錯誤。 建立工程后,輸入如下設(shè)計代碼

2023-03-01 17:10:10

基于fpga的數(shù)字通信系統(tǒng)數(shù)字復接器建模與設(shè)計

2014-04-15 21:58:57

,所以CORDIC算法的移位、加減法運算和流水線結(jié)構(gòu)更容易在FPGA上實現(xiàn)。本文在Altera公司的QuartusⅡ7.2軟件環(huán)境下使用VHDL,利用上述各種算法設(shè)計了16 bit寬的FFT復乘模塊并在

2011-07-11 21:32:29

的是計算機那種邏輯式、代數(shù)式處理,另外,由于能進行時分復接而降低了處理成本。因此,它趨向于根據(jù)不同的需要進行各種處理。例如數(shù)據(jù)、傳真信號的存儲變換;話音、圖像信號的頻帶壓縮,以及衛(wèi)星通訊中的回波抑制等。這些

2014-09-11 11:27:25

如何利用FPGA實現(xiàn)UART的設(shè)計?UART的結(jié)構(gòu)和幀格式

2021-04-08 06:32:05

如何利用FPGA實現(xiàn)低成本汽車多總線橋接?

2021-04-29 06:51:23

利用FPGA具有擴展靈活實現(xiàn)片上系統(tǒng)(SoC),同時具有多種IP核可供使用等優(yōu)點,設(shè)計了能夠控制多路模擬開關(guān)、A/D轉(zhuǎn)換、快速數(shù)據(jù)處理與傳輸、誤差校正、溫度補償?shù)闹悄軅鞲衅飨到y(tǒng);同時將傳感器與數(shù)據(jù)采集處理控制系統(tǒng)集成在一起,使系統(tǒng)更加緊湊,提高了系統(tǒng)適應(yīng)工業(yè)現(xiàn)場的能力。

2021-05-06 09:36:21

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

求大佬分享利用FPGA技術(shù)實現(xiàn)的數(shù)字式頻分多路副載波解調(diào)器設(shè)計?

2021-04-08 06:52:08

如何利用CPLD實現(xiàn)異步ASI/SDI信號電復接光傳輸設(shè)備的設(shè)計?

2021-04-29 06:29:10

,輸出設(shè)備。FPGA具有實現(xiàn)高速并行運算的能力,因而成為高性能數(shù)字信號處理的理想器件。此外,與專用集成電路(ASIC)相比,FPGA具有可重復編程的優(yōu)點。

2019-11-06 08:11:54

如何利用STM32 CubeMx ADC DMA實現(xiàn)多路采集?

2021-11-26 06:33:39

如何利用STM32實現(xiàn)安卓多路串口?

2022-01-21 06:03:36

如何利用STM32多個定時器實現(xiàn)多路PWM配置?

2021-11-24 07:55:02

如下圖所示:無線接收端需要什么硬件,能夠實現(xiàn)多路無線數(shù)據(jù)的接收?

2019-03-22 17:26:06

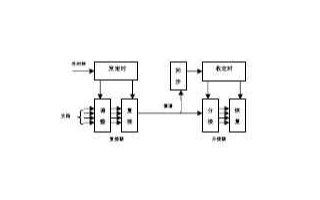

本文基于FPGA的技術(shù)特點,結(jié)合數(shù)字復接技術(shù)的基本原理,實現(xiàn)了基群速率(2048kbps)數(shù)字信號的數(shù)字分接與復接。

2021-04-30 06:27:39

隨著FPGA和大規(guī)模集成電路的發(fā)展,數(shù)據(jù)交換的實現(xiàn)有了新的方法。

2019-08-16 06:11:26

怎樣利用FPGA來實現(xiàn)IPV6數(shù)據(jù)包的拆裝?IPV6數(shù)據(jù)包的包頭和數(shù)據(jù)部分的拆分過程是怎樣進行的?

2021-04-28 06:05:54

畢設(shè)需要用labview軟件進行數(shù)字復接分接實驗的仿真,但是從來沒有接觸過那個軟件。哪位能教教么?我最近也在看視頻學習,但是還是不懂要怎么去用二進制數(shù)去輸出相應(yīng)的方波序列,或者說這個題目不知道怎么下手?哪位能提點一下嗎

2015-03-26 22:00:04

數(shù)字復接芯片有哪幾種?有何不同?復接芯片有哪些應(yīng)用舉例?

2021-05-27 06:08:21

數(shù)據(jù)復接方法有哪些?如何去實現(xiàn)它們?在設(shè)計數(shù)據(jù)復接與分接設(shè)備過程中有哪些難點?怎樣利用FPGA去實現(xiàn)多路話音/數(shù)據(jù)復接設(shè)備?

2021-04-14 06:42:57

數(shù)字復接的基本原理是什么?數(shù)字復接系統(tǒng)是如何構(gòu)成的?怎樣去設(shè)計數(shù)字復接系統(tǒng)?

2021-04-28 07:04:28

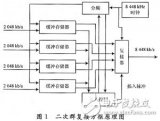

二次群復接的基本原理是什么?基于CPLD的PDH通信二次群復接器的設(shè)計怎樣對PDH通信二次群復接器進行仿真?

2021-04-30 07:01:48

要求是利用FPGA開發(fā)板,設(shè)計一個多路PCM編碼的復接器,已知8路電話信號已經(jīng)過PCM編碼,每路位寬8bit,頻率8KHz,以64比特寬度并行輸入到復接器,要求復接邏輯能夠把8電話路信號順序排隊,以

2014-09-16 21:39:41

多路復用與數(shù)字復接8.1 頻分多路復用(FDM)原理8.2 時分多路復用(TDM)原理8.3 準同步數(shù)字體系(PDH) 8.4 同步數(shù)字體系(SDH)

2008-10-22 13:26:58 0

0 本文概述了數(shù)字復接芯片在光纖通信系統(tǒng)中的作用,對幾種常用于PDH系統(tǒng)中的數(shù)字復接芯片進行了比較,然后重點介紹了GW7680芯片的功能和特點以及應(yīng)用技巧.

2009-04-25 16:04:15 27

27 電力線載波通信是電力系統(tǒng)的一種特殊的通信方式,在對這種通信方式進行充分研究的基礎(chǔ)上設(shè)計了一種雙CPU、低功耗、低成本的數(shù)字復接器,以滿足電力通信傳輸系統(tǒng)的需要。

2009-08-05 08:28:05 28

28 用VHDL 語言在FPGA 內(nèi)部編程實現(xiàn)組播復制。本文介紹其實現(xiàn)方法,并給出了時序仿真波形。通過擴展,該設(shè)計可以支持多位寬、多路復制,因而具有較好的應(yīng)用前景。關(guān)鍵詞:FP

2009-08-26 08:48:25 10

10 本文介紹了在ALTERA 公司的EDA 軟件MAX+plusⅡ平臺下,應(yīng)用VHDL 語言進行基于FPGA 的數(shù)字化光電經(jīng)緯儀中低速數(shù)字信號復接設(shè)計的具體實現(xiàn)方案,并給出部分程序設(shè)計。實驗表明,

2009-09-01 08:34:53 10

10 以太網(wǎng)到多路E1適配電路設(shè)計及FPGA實現(xiàn)

摘要:介紹了一種基于現(xiàn)場可編程門陣列(FPGA)的以太網(wǎng)數(shù)據(jù)-多路E1反向復用器同步電路設(shè)計,分析了FPGA具體實現(xiàn)過程中的一些常

2009-11-13 20:59:00 22

22 本文介紹了一種基于FPGA 的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計方案,描述了系統(tǒng)的主要組成及FPGA 的實現(xiàn)方法。在硬件上FPGA 采用ACEX1K100 器件,用于實現(xiàn)A/D 轉(zhuǎn)換器的控制電路、多路

2009-12-19 16:02:33 50

50 利用 FPGA 實現(xiàn)UART 的設(shè)計引 言隨著計算機技術(shù)的發(fā)展和廣泛應(yīng)用,尤其是在工業(yè)控制領(lǐng)域的應(yīng)用越來越廣泛,計算機通信顯的尤為重要。串行通信雖然使設(shè)備之間的連線大為減

2010-03-24 09:23:40 49

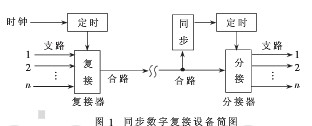

49 在簡要介紹同步數(shù)字復接基本原理的基礎(chǔ)上,采用VHDL語言對同步數(shù)字復接各組成模塊進行了設(shè)計,并在ISE集成環(huán)境下進行了設(shè)計描述、綜合、布局布線及時序仿真,取得了正確的設(shè)

2010-06-25 17:47:25 12

12 利用國際空間數(shù)據(jù)系統(tǒng)咨詢委員會(CCSDS)高級在軌系統(tǒng)(AOS)建議,提出了兩級復用的方案,設(shè)計了一種具有載荷數(shù)據(jù)存儲功能的高速實時/回放分級復接器。該方案采用FPGA技術(shù),對星上載荷

2010-07-28 16:51:47 14

14 本文提出了基于FPGA技術(shù)實現(xiàn)數(shù)字復接系統(tǒng)的設(shè)計方案,并介紹了有代表性的較簡單的四路同步復接器系統(tǒng)總體設(shè)計。硬件電路調(diào)試證明,該方案是行之有效的。

2010-08-06 16:33:16 30

30 為實現(xiàn)設(shè)備中存在的低速數(shù)據(jù)光纖通信的同步復接/ 分接,提出一種基于FPGA 的幀同步頭信號提取檢測方案,其中幀頭由7 位巴克碼1110010 組成,在數(shù)據(jù)的接收端首先從復接數(shù)據(jù)中

2010-10-26 16:56:54 46

46 FPGA的多路可控脈沖延遲系統(tǒng)設(shè)計

采用數(shù)字方法和模擬方法設(shè)計了一種最大分辨率為0.15 ns級的多路脈沖延遲系統(tǒng),可以實現(xiàn)對連續(xù)脈沖信號的高分辨

2009-03-29 15:09:48 2975

2975

摘要: 在反輻射導彈的雷達導引頭中,信號跟蹤器的實時性是影響系統(tǒng)性能的重要因素之一。介紹了利用高性能FPGA豐富的資源實現(xiàn)的多路脈沖重復頻率跟

2009-06-20 15:34:23 745

745

基于FPGA的二次群分接器的結(jié)構(gòu)分析及實現(xiàn)

1.引言

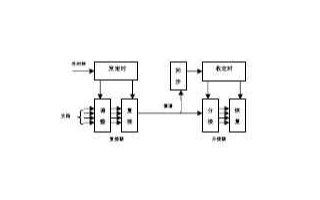

為了提高傳輸速率,擴大通信容量,減少信道數(shù)量,通常把多路信號復用成一路信號進行傳輸。在多種復

2009-12-08 09:54:42 1109

1109 摘要:陸上集群無線電通信(TETRA)系統(tǒng)是歐洲電信標準協(xié)會(ETSI)在專用移動通信(PMR)和公共接入移動通信(PAMR)網(wǎng)絡(luò)領(lǐng)域惟一支持無線數(shù)字集群的開放標準,本文主要介紹了該系統(tǒng)中話音編碼算法,并討論了其在DSP上實現(xiàn)的具體流程。 關(guān)鍵詞:TETRA;話音

2011-02-24 15:06:15 56

56 介紹這種基于FPGA流程設(shè)計的同步數(shù)字信號復接和分解方案,使用EDA仿真設(shè)計工具QuartusⅡ和Verilog HDL硬件描述語言對數(shù)據(jù)復接和分解的關(guān)鍵步驟進行功能仿真和驗證。

2011-08-05 11:52:03 8360

8360

本文將著重介紹運用FPGA技術(shù)實現(xiàn)基群與二次群之間復接與分接系統(tǒng)的總體設(shè)計方案。

2011-08-15 17:00:27 1858

1858 本課題基于關(guān)節(jié)臂式坐標測量機的研制需要,研究了 光柵傳感器 輸出信號的特點和FPGA開發(fā)技術(shù),以FPGA為載體,設(shè)計了一個基于FPGA的多路光柵數(shù)據(jù)采集系統(tǒng)。 本文主要介紹了光柵傳感

2011-08-18 16:34:55 78

78 基于USB2.0 的FIFO 方式, 利用FPGA 同步實現(xiàn)三個通道, 不同傳輸率的數(shù)據(jù)的發(fā)送和采集, 詳細說明多路數(shù)據(jù)發(fā)送與采集時,對不同數(shù)據(jù)傳輸速率的實現(xiàn)方法以及部分硬件和軟件設(shè)計, 最后, 簡要

2011-09-13 17:22:34 66

66 多路交換開關(guān)是高性能交換部件的核心,本文描述了基于Xilinx公司Virtex-11系列FPGA的特點設(shè)計和實現(xiàn)的一種高速多路交換開關(guān),它由輸入信道組織、內(nèi)部無阻塞crossbar交換和仲裁調(diào)度器三

2011-12-27 16:45:04 46

46 為了實現(xiàn)對多路視頻和數(shù)據(jù)信號的同步傳輸,提出了一種基于FPGA的視頻數(shù)據(jù)綜合傳輸系統(tǒng)設(shè)計方案,并完成系統(tǒng)的軟硬件設(shè)計。該系統(tǒng)的硬件部分主要由FPGA、CPLD芯片及光模塊等設(shè)備組成,軟件部分采用

2015-12-31 09:26:25 12

12 于FPGA的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計。

2016-05-10 13:45:28 41

41 在復雜的現(xiàn)代數(shù)字通信系統(tǒng)中,所需傳輸?shù)臄?shù)字信源往往有很多個。為了提高傳輸?shù)男剩瑪U大傳輸?shù)娜萘浚罁?jù)時分復用原理實現(xiàn)的數(shù)字信號復接與分接已經(jīng)廣泛應(yīng)用于很多系統(tǒng)中。數(shù)字復接器(Digital

2017-11-07 10:29:37 8

8 基于PCIE通信總線的FPGA開發(fā)板與多路AD采集卡設(shè)計并實現(xiàn)了滿足系統(tǒng)要求的數(shù)據(jù)采集平臺。首先簡要介紹了該采集平臺的結(jié)構(gòu)及PCIE通信鏈路的搭建,然后設(shè)計實現(xiàn)了一種數(shù)據(jù)連續(xù)存儲的方法,最后通過實驗驗證了該方法的可行性及采集平臺的整體性能。

2017-11-15 14:21:02 12246

12246

設(shè)計方案。該方案能夠實現(xiàn)高速載荷數(shù)據(jù)接收合路、NAND flash大容量數(shù)據(jù)存儲控制、數(shù)據(jù)復接,數(shù)據(jù)信道低密度奇偶校驗編碼(LDPC)等功能。設(shè)計過程中對電路進行優(yōu)化,實現(xiàn)了高速并行數(shù)據(jù)處理和高可靠性目標。通過FPGA的原型驗證,本方案設(shè)計

2018-04-03 15:23:30 0

0 為了提高傳輸速率,擴大通信容量,減少信道數(shù)量,通常把多路信號復用成一路信號進行傳輸。在多種復用方式中,時分復用是一種常用的方式。時分復用是多路信號按照時間間隔共享一路信道進行傳輸。復接是把多路速率

2018-12-30 10:24:00 2048

2048

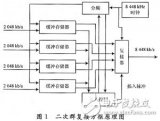

復接器由緩沖存儲器、插入控制電路、時鐘發(fā)生器、分頻器和復接器組成。時鐘產(chǎn)生器提供8 448 kHz時鐘;分頻器對8 448 kHz進行4分頻,以獲得2 112 kHz的讀出時鐘;緩沖存儲器和插入

2019-06-28 08:07:00 4864

4864

在數(shù)字通信網(wǎng)中,為了擴大傳輸容量和傳輸效率,常常需要把若干個低速數(shù)字信號合并成為一個高速數(shù)字信號,然后通過高速信道傳輸;而在接收端又按照需要分解成低速數(shù)字信號。數(shù)字復接技術(shù)就是實現(xiàn)這種數(shù)字信號合并(復接)和分解(分接)的專門技術(shù)。

2019-06-10 08:12:00 4820

4820

介紹了一種基于FPGA的高速多路數(shù)據(jù)采集系統(tǒng)的設(shè)計方案,描述了系統(tǒng)的主要組成及FPGA的實現(xiàn)方法,并用v∞L語言設(shè)計的狀態(tài)杌在Qmr嚙Ⅱ開發(fā)軟件中進行仿真。該系統(tǒng)在通用數(shù)據(jù)采集系統(tǒng)的基礎(chǔ)上,增加數(shù)據(jù)

2018-10-12 16:15:09 14

14 介紹一~種基于FPGA的多路模擬數(shù)據(jù)采集接口的設(shè)計方案。該方案使用Max1281作為模數(shù)轉(zhuǎn)換芯片,在APA150 FPGA中設(shè)計和實現(xiàn)了相關(guān)的接口控制、配置和數(shù)據(jù)存儲模塊;給出了系統(tǒng)設(shè)計框圖、FPGA開發(fā)要點和仿真波形。

2018-10-16 16:18:00 18

18 提出了一種基于FPGA+ARM的多路視頻采集系統(tǒng)的設(shè)計與實現(xiàn)方法。該視頻采集系統(tǒng)不僅能對多路快速變化的視頻信號進行采集和處理,而且能應(yīng)用為系統(tǒng)信號發(fā)生設(shè)備.系統(tǒng)采用FPGA為核心高速時序邏輯控制

2019-11-19 15:51:42 21

21 在數(shù)字通信中,為了擴大傳輸容量和提高傳輸效率,通常需要將若干個低速數(shù)字碼流按一定格式合并成一個高速數(shù)據(jù)碼流流,以便在高速寬帶信道中傳輸。數(shù)字復接就是依據(jù)時分復用基本原理完成數(shù)碼合并的一種技術(shù),并且是數(shù)字通信中的一項基礎(chǔ)技術(shù)。

2020-08-07 16:55:11 2231

2231

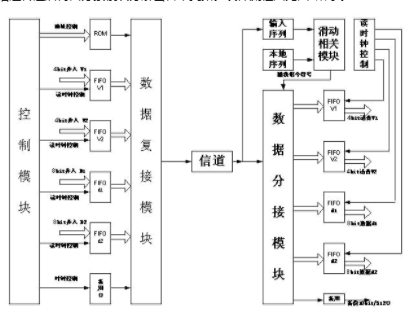

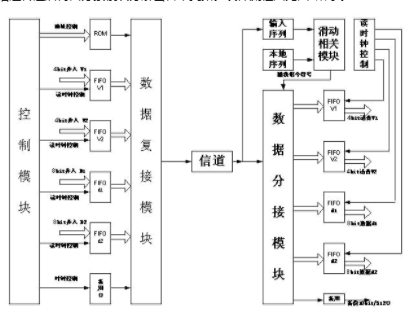

隨著現(xiàn)代通信向著多業(yè)務(wù)方向發(fā)展,為了節(jié)省信道資源、降低調(diào)制解調(diào)設(shè)備的復雜度,數(shù)據(jù)復接設(shè)備得到了更充分的利用。它能將多路不同類型的數(shù)據(jù)流復接成一路高速數(shù)據(jù)流,通過信道傳輸,在收端分接出發(fā)端對應(yīng)的數(shù)據(jù)流,以實現(xiàn)多業(yè)務(wù)雙向通信。

2020-08-26 17:21:15 925

925

主要介紹基于FPGA實現(xiàn)多路模擬信號自適應(yīng)采集系統(tǒng)的設(shè)計。該系統(tǒng)主要包括軟件和硬件兩部分:硬件主要采用FPGA芯片,AD7982—1,ADG406和運放AD824來搭建硬件平臺;軟件包括FPGA程序

2021-02-02 15:52:34 5

5 無人機等空中平臺的下行鏈路中包含了眾多的信息,如遙測信息,測距信息,實時圖像信息等,為利用同一信道將這些信息有效地傳輸?shù)降孛婵刂葡到y(tǒng),必須進行數(shù)據(jù)打包(復接)處理。本文針對遙測數(shù)據(jù)和圖像數(shù)據(jù)復接的情況,給出了一種基于FPGA的設(shè)計方案。

2021-04-02 09:33:15 24

24 隨著集成電路技術(shù)的發(fā)展,FPGA和DSP以及ARM以其體積小、速度快、功耗低、設(shè)計靈活、利于系統(tǒng)集成、擴展升級等優(yōu)點,被廣泛地應(yīng)用于高速數(shù)字信號傳輸及數(shù)據(jù)處理,以DSP+FPGA+ARM的架構(gòu)組成滿足實時性要求的高速數(shù)字處理系統(tǒng)已成為一種趨勢,本文主要研究FPGA在高速多路數(shù)據(jù)傳輸中的應(yīng)用。

2021-04-24 09:04:49 7109

7109

引言:上一篇文章我們介紹了通過添加電阻器、場效應(yīng)晶體管(FET)開關(guān)、電平轉(zhuǎn)換器甚至其他Xilinx FPGA等選項實現(xiàn)HP Bank IO與2.5V/3.3V外設(shè)對接的方法。本文介紹利用TI公司TXS0108實現(xiàn)FPGA IO Bank接不同外設(shè)IO接口電壓轉(zhuǎn)換。

2023-05-16 09:02:50 5020

5020

作為一名在工業(yè)自動化領(lǐng)域摸爬滾打多年的工程師,我深知企業(yè)通信網(wǎng)絡(luò)的痛點——設(shè)備接口雜亂、線路成本高、維護難度大。直到去年為某化工廠升級通信系統(tǒng)時,接觸到了廣州郵科的PCM復接綜合設(shè)備,才真正

2025-11-03 09:45:27 225

225

電子發(fā)燒友App

電子發(fā)燒友App

評論