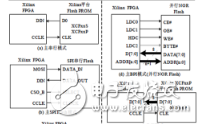

廣義的來說,FPGA的配置包括直接使用下載電纜對FPGA器件進行編程、對外部EEPROM和FLASH進行編程、使用MPU對FPGA器件進行編程、外部EEPROM和FLASH對器件進行編程等。

2016-10-26 10:58:27 12458

12458 在需要多個FPGA芯片的應(yīng)用中,如果JTAG鏈上所有FPGA采用相同配置,可以通過“成組”加載方式同時加載;

2023-02-20 10:18:27 8049

8049

自中高端FPGA技術(shù)成熟以來,FPGA+DSP/ARM架構(gòu)的硬件設(shè)計在眾多工業(yè)領(lǐng)域得到廣泛應(yīng)用。例如無線通信、圖像處理、工業(yè)控制、儀器測量等。

2025-10-15 10:39:02 3929

3929

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進行視頻處理的方案,實現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。

2014-10-23 15:35:49 6823

6823

DSP+FPGA架構(gòu)的最大特點是結(jié)構(gòu)靈活、有較強的通用性、適合于模塊化設(shè)計,從而能夠提高算法效率,同時其開發(fā)周期短、系統(tǒng)易于維護和升級,適合于實時視頻圖像處理。

2015-02-03 15:20:47 1660

1660

FPGA配置方式靈活多樣,根據(jù)芯片是否能夠自己主動加載配置數(shù)據(jù)分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為

2022-09-22 09:13:59 4864

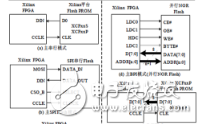

4864 的方法彌補單DSP核心的缺陷。DSP+FPGA的結(jié)構(gòu)能將DSP從繁瑣的外部接口管理中解放出來,充分發(fā)揮DSP的運算優(yōu)勢,提高運算效率的同時易于維護和擴展。DSP通過XINTF接口與FPGA通信。DSP

2016-09-24 10:41:18

現(xiàn)狀是:1.信號處理板的架構(gòu)是FPGA+DSP,DSP上掛網(wǎng)口,與電腦可正常通信2.數(shù)據(jù)處理板的架構(gòu)是FPGA掛網(wǎng)口,與電腦可正常通信現(xiàn)在問題:兩塊板子網(wǎng)口無法正常通信,且拔插網(wǎng)口后不能自啟動。聯(lián)系方式:shang_lg2011@163.com/***尚

2020-05-27 08:28:44

本帖最后由 mr.pengyongche 于 2013-4-30 02:57 編輯

FPGA+DSP 在空中背景下運動目標實時跟蹤系統(tǒng)中的應(yīng)用 摘要:針對電視跟蹤系統(tǒng)對飛行目標的檢測與跟蹤受到速度瓶頸

2012-12-28 11:19:07

本人剛?cè)腴TFPGA,不知道如何實現(xiàn)FPGA+DSP,FPGA+ARM接口設(shè)計,網(wǎng)上查詢有的說FPGA+DSP可以通過EMIF,IP核實現(xiàn),FPGA+ARM可以通過SPI,有沒有具體硬件參考的?

2016-08-27 11:30:26

本文檔關(guān)于FPGA與DSP組成的一個強大的開發(fā)系統(tǒng)

2014-07-22 16:10:56

.FPGA+DSP的導(dǎo)引頭信號處理結(jié)構(gòu)成為當前以及未來一段時間的主流。FPGA和DSP處理器具有截然不同的架構(gòu),在一種器件上非常有效的算法.在另一種器件上可能效率會非常低。如果目標要求大量的并行處理或者最大

2019-08-30 06:31:29

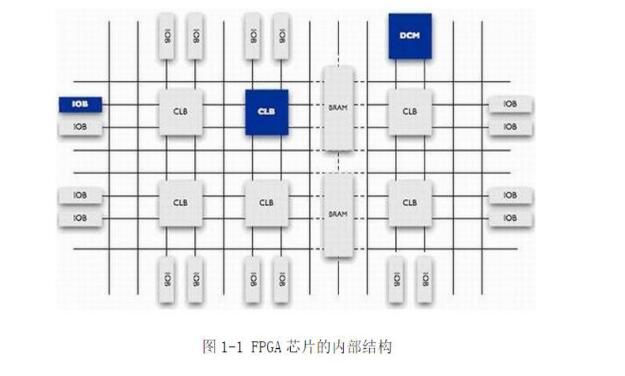

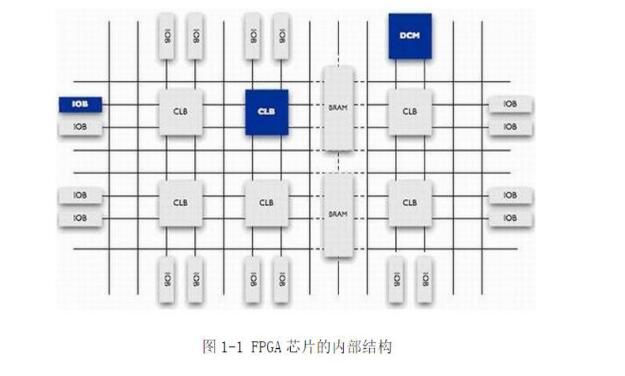

、功能多個角度解析兩者的不同。1、FPGA與DSP的特點FPAG的結(jié)構(gòu)特點片內(nèi)有大量的邏輯門和觸發(fā)器,多為查找表結(jié)構(gòu),實現(xiàn)工藝多為SRAM。規(guī)模大,集成度高,處理速度快,執(zhí)行效率高。能完成復(fù)雜的時序

2019-05-07 01:28:40

。FPGA的邏輯是通過向內(nèi)部靜態(tài)存儲器單元加載配置數(shù)據(jù)來實現(xiàn)的。存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及模塊間或與I/O間的連接,并最終決定了FPGA實現(xiàn)的功能。FPGA的這種結(jié)構(gòu)允許無限次的重新

2011-02-17 11:21:37

,影響系統(tǒng)實時性。動態(tài)重構(gòu)在系統(tǒng)運行中能實時全部或部分重構(gòu),且不中斷正常邏輯輸出,因而更有靈活性和高速度。 大多數(shù)FPGA都是基于LUT查找表結(jié)構(gòu),它們只適用于靜態(tài)重構(gòu),通過向LUT一次下載全部配置數(shù)據(jù)

2011-05-27 10:22:59

最近在調(diào)試FPGA+DSP c6748,用upp來進行數(shù)據(jù)交換,現(xiàn)在遇到一個問題,想請教一下大家,dsp通過upp發(fā)送數(shù)據(jù)到FPGA,能正常發(fā)送,但是在dsp通過upp接收數(shù)據(jù)時遇到了一些問題

2020-05-22 09:52:19

fpga+dsp 4路ad采集系統(tǒng),you嘗,rapidio pcieddr3 各種高速外圍接口 代碼有償。qq2715957785

2018-02-24 08:34:21

本帖最后由 全都被注冊過 于 2015-8-14 23:15 編輯

fpga為主機向dsp傳數(shù),fpga的port initial會高低跳變,導(dǎo)致傳輸速度很慢(我認為傳輸速度慢是因為其跳變導(dǎo)致的)是什么導(dǎo)致的port initial不停跳變?有人遇到過這種情況嗎?求教!

2015-08-14 18:47:58

ARM、DSP及FPGA的技術(shù)特點和區(qū)別

2019-10-12 07:13:50

方式。加電時,FPGA芯片將EPROM中數(shù)據(jù)讀入片內(nèi)編程RAM中,配置完成后,FPGA進入工作狀態(tài)。掉電后,FPGA恢復(fù)成白片,內(nèi)部邏輯關(guān)系消失,因此,FPGA能夠反復(fù)使用。FPGA的編程無須專用

2021-09-08 17:49:20

大家好,最近剛接觸FPGA不久 現(xiàn)在手上有一塊xilinx SP3E開發(fā)板,簡單的設(shè)計了一個流水燈的程序 通過JTAG下載方式 直接下到FPGA里 板子可以運行 因為想實現(xiàn)斷電后重啟板子自動

2014-10-11 11:16:08

FPGA進行硬件實現(xiàn),這樣能兼顧速度及靈活性。高層的處理算法結(jié)構(gòu)復(fù)雜,適用于運算速度高、尋址方式靈活、通信機制強的DSP芯片宋實現(xiàn)。DSP+FPGA架構(gòu)的最大特點是結(jié)構(gòu)靈活、有較強的通用性、適合于模塊化

2019-07-01 07:38:06

```勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載51:Altera FPGA配置方式概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD

2018-03-04 22:12:49

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載52:Altera FPGA配置方式之AS/PS/JTAG配置方式特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com

2018-03-05 16:30:35

,數(shù)字信號處理與數(shù)字圖像處理沒有太大區(qū)別),就意味著可以用FPGA做硬件設(shè)計來實現(xiàn)DSP芯片的功能,當然,相比較專業(yè)的DSP芯片 成本太高,因此你也沒必要選擇FPGA+DSP,就選擇DSP芯片,算法...

2021-07-28 09:16:02

基于DSP的圖像處理系統(tǒng)的應(yīng)用研究摘要 本文介紹了一種基于FPGA+DSP結(jié)構(gòu)的具有通用性、可擴充性的高速數(shù)字圖像處理系統(tǒng)硬件平臺。重點介紹了以高速數(shù)字信號處理器TMS320DM642

2012-12-19 11:05:08

用FPGA進行硬件實現(xiàn),這樣能兼顧速度及靈活性。高層的處理算法結(jié)構(gòu)復(fù)雜,適用于運算速度高、尋址方式靈活、通信機制強的DSP芯片宋實現(xiàn)。 DSP+FPGA架構(gòu)的最大特點是結(jié)構(gòu)靈活、有較強的通用性

2019-06-28 08:10:26

數(shù)據(jù)量特別大、運算復(fù)雜,單純依靠通用PC很難達到實時性要求,不能滿足現(xiàn)行高速三維圖像處理應(yīng)用。 本系統(tǒng)中,采用FPGA實現(xiàn)底層的信號預(yù)處理算法,其處理數(shù)據(jù)量很大,處理速度高,但算法結(jié)構(gòu)相對

2019-06-24 06:11:03

圖像數(shù)據(jù)處理的工作原理是什么?基于FPGA+DSP的圖像處理系統(tǒng)待如何去設(shè)計?

2021-06-02 06:54:28

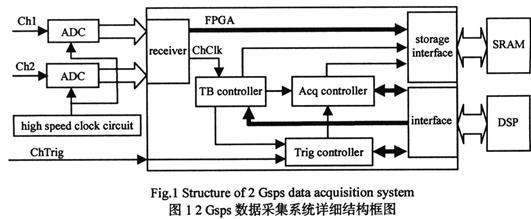

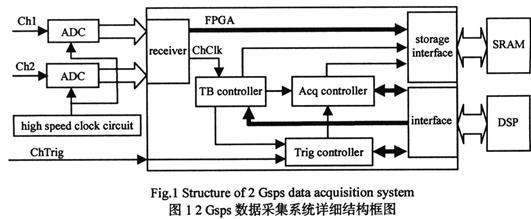

基于FPGA+DSP的高速數(shù)據(jù)采集系統(tǒng)設(shè)計

2012-06-27 17:23:53

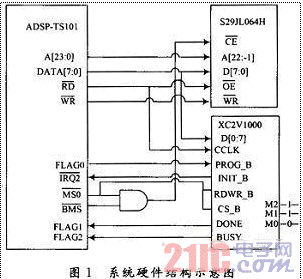

的接口不斷掃描,將數(shù)據(jù)送到顯示屏顯示。同時FPGA連接鍵盤接口,通過掃描法掃描鍵值,之后通過中斷方式送到DSP,使DSP對各種輸入進行控制。整個系統(tǒng)的結(jié)構(gòu)圖如圖1所示。

2019-07-03 08:08:33

。目前想要選擇單一FPGA進行設(shè)計,但是又擔心片太貴預(yù)算超標,大家是否有合適的片子推薦?或者還是繼續(xù)采用FPGA+DSP的結(jié)構(gòu),大家有啥看法呢?

2018-05-11 11:54:50

,生命周期縮短。實現(xiàn)功能強、性能指標高、抗干擾能力強、工作穩(wěn)定可靠、體積小、功耗低、結(jié)構(gòu)緊湊合理符合彈載要求的導(dǎo)引頭信號處理器已經(jīng)勢在必行。過去單一采用DSP處理器搭建信號處理器已經(jīng)不能滿足要求.FPGA+DSP的導(dǎo)引頭信號處理結(jié)構(gòu)成為當前以及未來一段時間的主流。

2019-11-06 08:34:27

,生命周期縮短。實現(xiàn)功能強、性能指標高、抗干擾能力強、工作穩(wěn)定可靠、體積小、功耗低、結(jié)構(gòu)緊湊合理符合彈載要求的導(dǎo)引頭信號處理器已經(jīng)勢在必行。過去單一采用DSP處理器搭建信號處理器已經(jīng)不能滿足要求.FPGA+DSP的導(dǎo)引頭信號處理結(jié)構(gòu)成為當前以及未來一段時間的主流。

2019-08-19 06:38:12

雖說FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點,但有什么方法去證明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)是存在的呢?

2021-04-08 06:54:33

我想用FPGA+DSP做個聲相儀,有感興趣的小伙伴嗎?一起開發(fā),在上海最好啦。先做原型機出來,然后再考慮產(chǎn)品化。私聊:QQ 4010087

2017-04-25 14:53:48

:48MB/s);向FPGA讀數(shù)據(jù):41.62MB/s(按當前配置最大理論值為:48MB/s)。2,綜上所述,選擇DSP與FPGA的接口方式時,應(yīng)該考慮實際的需求,如果做圖像處理之類FPGA采集大量數(shù)據(jù)需實時

2018-08-01 08:04:26

FPGA通過GPIO口發(fā)送中斷給DSP讓DSP讀取數(shù)據(jù),那么DSP怎么通知FPGA已經(jīng)讀完了呢???

2018-07-30 09:37:02

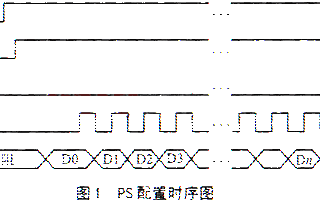

介紹一種在嵌入式系統(tǒng)中使用微處理器被動串行配置方式實現(xiàn)對FPGA配置的方案,將系統(tǒng)程序及配置文件存在系統(tǒng)Flash 中,利用微處理器的I/O 口產(chǎn)生配置時序,省去配置器件;討論FPG

2009-04-15 11:02:53 13

13 闡述了一種數(shù)字接收系統(tǒng)的設(shè)計,由ADC器件AD6640和DSP. FPGA組成,具有結(jié)構(gòu)靈活、擴展能力強等特點。本文詳細介紹了該系統(tǒng)的結(jié)構(gòu)和接口設(shè)計。

2009-05-08 16:43:12 27

27 本文介紹了DSP 和FPGA 在數(shù)字電子設(shè)計中的優(yōu)勢,并結(jié)合雷達模擬系統(tǒng)的硬件設(shè)計實例,重點闡述了相應(yīng)的硬件與軟件實現(xiàn)方法。關(guān)鍵詞:DSP FPGA 數(shù)字電路設(shè)計雷達模擬系統(tǒng)

2009-08-25 14:33:01 15

15 通過說明FPGA 的各種配置方式及各種配置文件的使用,重點探討了在嵌入式系統(tǒng)中使用FPGA 的軟硬件設(shè)計。使用微處理器在線配置FPGA 時,需要將存儲在Flash 中的配置文件,通過微處

2009-09-16 10:52:02 10

10 介紹了一種基于FPGA+DSP 的數(shù)據(jù)采集與處理平臺,給出了系統(tǒng)實現(xiàn)的總體方案,并闡述了各部分硬件電路的設(shè)計。重點對FPGA 內(nèi)部各主要功能模塊做了詳細闡述,對各個模塊的設(shè)計方法

2009-12-19 15:59:16 34

34 簡要分析了DSP+FPGA 系統(tǒng)的特點和優(yōu)越性,結(jié)合導(dǎo)引頭信號處理板的開發(fā),提出了在此系統(tǒng)中,FPGA 設(shè)計的幾個關(guān)鍵技術(shù),并且給出了詳實的分析和解決方案。

2009-12-23 14:53:54 20

20 用可再配置FPGA實現(xiàn)DSP功能

2010-07-16 17:56:43 10

10 本文舉例分析了DSP的引導(dǎo)裝載過程和FPGA的配置流程,并據(jù)此提出了一種使用單個FLASH存儲器實現(xiàn)上述兩個功能的方法。

2010-07-21 17:14:42 13

13 簡要分析了DSP+FPGA系統(tǒng)的特點和優(yōu)越性,結(jié)合導(dǎo)引頭信號處理板的開發(fā),提出了在此系統(tǒng)中,FPGA設(shè)計的幾個關(guān)鍵技術(shù),并且給出了詳實的分析和解決方案。

2010-07-21 17:28:04 18

18 摘要: 介紹基于SRAM LUT結(jié)構(gòu)的FPGA器件的上電配置方式;著重介紹采用計算機串口下載配置數(shù)據(jù)的方法和AT89C2051單片機、串行EEPROM組成的串行配置系統(tǒng)的設(shè)計方法及

2009-06-20 10:57:26 1326

1326

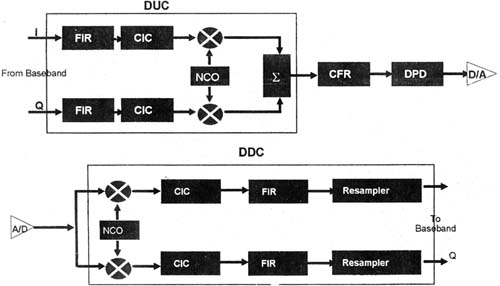

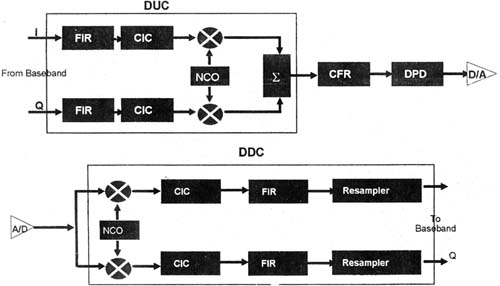

FPGA和DSP組合在無線基站中的應(yīng)用

在自動控制產(chǎn)品中,CPD+DSP+MCU的構(gòu)架是目前最為流行的成熟方案,而在通訊產(chǎn)品中,大量使用FPGA設(shè)計,合理使用FPGA

2009-10-12 11:20:11 1340

1340

摘要:為了實現(xiàn)高速HDLC通訊協(xié)議,設(shè)計了DSP+FPGA結(jié)構(gòu)的485通訊接口,接口包括DSP、FPGA、485轉(zhuǎn)換等硬件電路,以及DSP與FPGA之間的數(shù)據(jù)交換程序和FPGA內(nèi)部狀態(tài)機;其中DSP用于實現(xiàn)數(shù)據(jù)控制,FPGA用于實現(xiàn)HDLC通訊協(xié)議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 摘要:在FPGA+DSP構(gòu)建的便件平臺上,以鏈路口(LINKPORT)通信協(xié)議為根據(jù),實現(xiàn)紅外圖像數(shù)據(jù)采集與顯示。重點描述紅外圖像數(shù)據(jù)采集與經(jīng)過LINKPORT傳入DSP,圖像壓縮與經(jīng)過LINKPORT傳出DSP以及圖像數(shù)據(jù)緩存與顯示,最后介紹了程序高度過程中的方法。樣機在實

2011-03-01 00:11:12 89

89 SPI方式FPGA配置和SPI flash編程

2011-05-16 18:01:02 166

166 在雷達信號處理、數(shù)字圖像處理等領(lǐng)域中,信號處理的實時性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢及DSP芯片在復(fù)雜算法處理上的優(yōu)勢,DSP+FPGA的實時信號處理系統(tǒng)

2012-07-05 15:01:40 8211

8211

基于FPGA+DSP實時圖像采集處理系統(tǒng)設(shè)計

2017-01-03 11:41:35 9

9 基于DSP的FPGA配置方法研究與實現(xiàn)

2017-10-19 16:15:19 36

36 在自動控制產(chǎn)品中,CPD+DSP+MCU的構(gòu)架是目前最為流行的成熟方案,而在通訊產(chǎn)品中,大量使用FPGA設(shè)計,合理使用FPGA和DSP的組合,FPGA和DSP之間的智能配分可使無線系統(tǒng)設(shè)計師獲得最佳

2017-10-25 11:41:07 1

1 所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運算速度快,尋址靈活的DSP數(shù)字信號處理器進行處理。這里提出了一種FPGA+DSP相結(jié)合的實時圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-26 15:44:56 3

3 所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運算速度快,尋址靈活的DSP數(shù)字信號處理器進行處理。這里提出了一種FPGA+DSP相結(jié)合的實時圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-31 17:00:34 14

14 視頻、影像和電信市場的標準推動了異構(gòu)可重配置DSP硬件平臺的使用。在本文中這些平臺包括DSP處理器和FPGA,它們提供的現(xiàn)成硬件解決方案可以解決視頻、影像和電信設(shè)計中的重大難題,同時又不失差異化

2017-11-06 13:59:42 3

3 在現(xiàn)代工業(yè)控制系統(tǒng)中,對電機的控制是其重要組成部分。編碼器作為電機角位移的檢測裝置,為系統(tǒng)提供重要反饋信號。本文介紹了一個適合嵌入式系統(tǒng)的基于DSP和FPGA的海德漢光電編碼器信號處理通用模塊,能夠

2017-11-18 03:39:01 4476

4476

高速率跳頻、高帶寬技術(shù)是提高跳頻發(fā)射機性能的關(guān)鍵,本文結(jié)合軟件無線電思想和架構(gòu),提出一種基于FPGA+DSP的跳頻電臺傳輸系統(tǒng)的設(shè)計方案,該系統(tǒng)兼容多種調(diào)制方式和跳頻速率及數(shù)碼率。系統(tǒng)采用上下變頻器作為系統(tǒng)基帶信號與中頻信號之間的頻率轉(zhuǎn)換器,還給出了系統(tǒng)電路原理圖和程序流程圖。

2017-11-22 08:02:36 3115

3115

FPGA配置方式靈活多樣,根據(jù)芯片是否能夠自己主動加載配置數(shù)據(jù)分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失(斷電不丟數(shù)據(jù))性存儲器中的配置比特流,配置所需的時鐘信號(稱為

2017-11-22 09:24:02 7490

7490 FPGA配置方式靈活多樣,根據(jù)芯片是否能夠自己主動加載配置數(shù)據(jù)分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為

2017-11-26 08:12:51 8993

8993

本文主要介紹了一種基于FPGA+DSP的視頻控制的智能交通燈設(shè)計。該交通燈由視頻采集、圖像處理和控制模塊組成,使用FPGA核心搭建專用高速視頻采集模塊,使用DSP處理器進行實時圖像運算,通過圖像算法提取車流量信息,最終結(jié)合模糊算法實現(xiàn)智能控制。

2018-01-09 14:15:41 2686

2686

本文首先分析了FPGA是否會取代DSP,其次介紹了FPAG結(jié)構(gòu)特點與優(yōu)勢及DSP的基本結(jié)構(gòu)和特征,最后闡述了FPGA與DSP兩者之間的區(qū)別。

2018-05-31 09:51:25 37403

37403

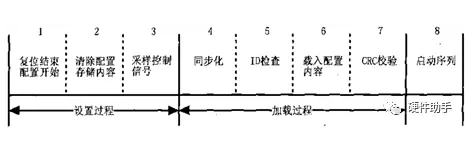

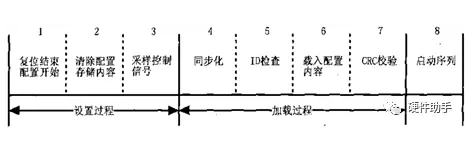

盡管FPGA的配置模式各不相同,但整個配置過程中FPGA的工作流程是一致的,分為三個部分:設(shè)置、加載、啟動。

2018-08-01 15:32:54 5330

5330

本文采用ADC+高頻時鐘電路+FPGA+DSP的結(jié)構(gòu)模式,設(shè)計了一種實時采樣率為2 Gsps的數(shù)字存儲示波器數(shù)據(jù)采集系統(tǒng),為國內(nèi)高速高分辨率的數(shù)據(jù)采集系統(tǒng)的研制提供了一個參考方案。

2019-05-03 09:19:00 7263

7263

FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點,兼顧了速度和靈活性。本文以導(dǎo)引頭信號處理系統(tǒng)為例說明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)。

2019-01-08 08:36:00 3785

3785

FPGA有多種配置/加載方式。粗略可以分為主動和被動兩種。主動加載是指由FPGA控制配置流程,被動加載是指FPGA僅僅被動接收配置數(shù)據(jù)。

2018-10-05 10:12:00 19146

19146 高速中頻采樣信號處理平臺在實際應(yīng)用中有很大的前景,提出采用FPGA+DSP的處理結(jié)構(gòu),結(jié)合高性能A/D和D/A處理芯片,設(shè)計了一個通用處理平臺,并對其主要性能進行了測試。

2018-10-18 16:36:48 5708

5708

大,運算簡單,但是要求運算速率高,可以用FPGA硬件來處理,上層所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運算速度快,尋址靈活的DSP數(shù)字信號處理器進行處理。這里提出了一種FPGA+DSP相結(jié)合的實時圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實際采集的是光線束

2018-10-22 22:00:01 891

891 滿足導(dǎo)航系統(tǒng)設(shè)計的小型化、實時性要求,本文提出了一種基于FPGA+DSP的實現(xiàn)方案。該方案的設(shè)計思路是:將FPGA映射到DSP EMIF的一段地址空間,并用FPGA來完成多通道信號的采集;DSP根據(jù)

2018-11-07 17:18:23 10

10 提出了一種新的基于FPGA+DSP的高精度數(shù)字化電源的數(shù)據(jù)采集方案。詳細闡述了FPGA與DSP之.間vXSPI接口進行同步通信,以及用DSP作為控制器并通過PI調(diào)節(jié)產(chǎn)生PWM波形來控制數(shù)字化電源穩(wěn)定性的具體方法。

2018-11-07 17:18:30 23

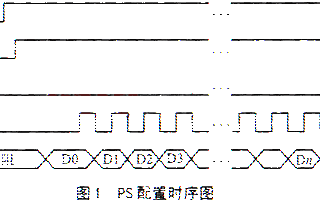

23 Altera FPGA支持AS,PS,JTAG等幾種較常見的配置方法。 當為AS配置模式時,FPGA為主設(shè)備,加載外部FLASH中的數(shù)據(jù)至內(nèi)部RAM中運行。當為PS配置模式時,FPGA為從設(shè)備,外部

2018-11-18 18:05:01 831

831 FPGA的配置方式有以下幾種,JTAG,AS,PS,AP,F(xiàn)PP等幾種。

2019-11-25 07:02:00 5893

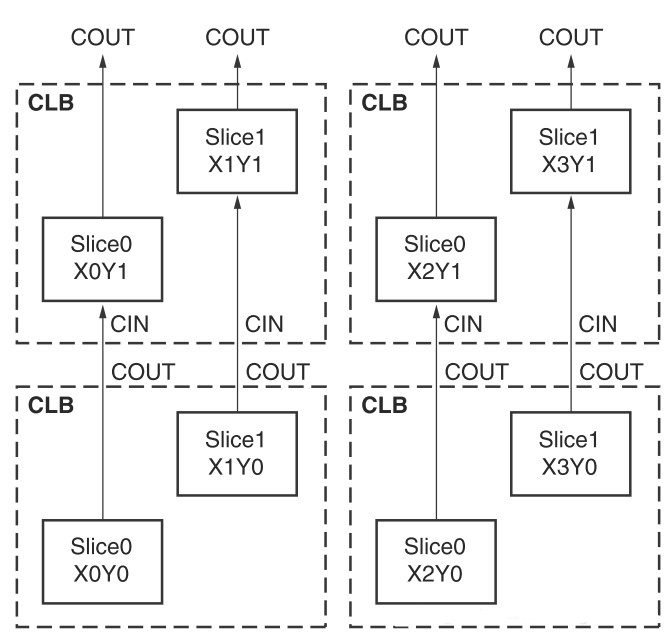

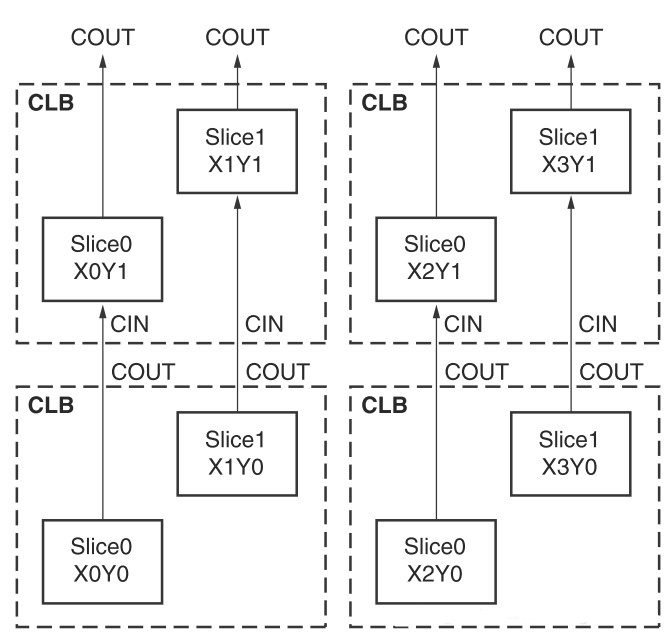

5893 目前市場上90%以上的FPGA來自于xilinx和altera這兩家巨頭,而這兩家FPGA的實現(xiàn)技術(shù)都是基于SRAM的可編程技術(shù),FPGA內(nèi)部結(jié)構(gòu)基本一致,所以本文僅以xilinx的7系列FPGA介紹。

2019-10-20 09:03:00 3074

3074

FPGA器件有三類配置下載方式:主動配置方式(AS)和被動配置方式(PS)和最常用的(JTAG)配置方式。AS由FPGA器件引導(dǎo)配置操作過程,它控制著外部存儲器和初始化過程,EPCS系列:如

2020-07-09 10:53:09 8918

8918 介紹一種在嵌放式系統(tǒng)中使用微處理器被動串行配置方式實現(xiàn)對FPGA配置的方案,將系統(tǒng)程序及配置文件存在系統(tǒng)Flash中,利用微處理器的I/O口產(chǎn)生配置時序,省去配置器件;討論FPGA的各種配置方式

2020-09-29 17:05:59 1490

1490

最近完成了Arria10的原理圖設(shè)計,想做一些記錄,下面是關(guān)于FPGA配置的一些方式。 MSEL 將 MSEL 管腳直接連接到VCCPGM 或 GND,不需使用任何的上拉或下拉電阻,即可選擇出所需

2021-03-12 16:26:58 14350

14350

FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法(哪些專業(yè)適合嵌入式開發(fā))-該文檔為FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 11:16:55 22

22 。 FPGA器件配置方式分三大類:主動配置、被動配置和JTAG配置。 主動配置:由FPGA器件引導(dǎo)配置操作過程。 被動配置:由計算機或控制器控制配置過程。上電后,控制器件或主控器把存儲在外部存儲器中的數(shù)據(jù)送入FPGA器件內(nèi),配置完成之后將對器件I/O和寄存器進行初始化。初始化完成后,進入用戶

2021-09-06 09:41:56 7483

7483 基于FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計(開關(guān)電源技術(shù)發(fā)展綜述)-該文檔為基于FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計講解文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-24 11:32:01 36

36 FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計(電源技術(shù)是什么檔次的期刊)-為基于FPGADSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計講解文檔摘 要:提出了一種新的基于FPGA+DSP的高精度數(shù)字化電源

2021-09-27 11:16:45 19

19 基于FPGA+DSP彈載SAR信號處理系統(tǒng)設(shè)計

2021-12-27 18:58:51 21

21 FPGA 可編程的特性決定了其實現(xiàn)數(shù)字邏輯的結(jié)構(gòu)不能像專用 ASIC 那樣通過固定的邏輯門電路來完成,而只能采用一種可以重復(fù)配置的結(jié)構(gòu)來實現(xiàn), 而查找表(LUT)可以很好地滿足這一要求,目前主流的 FPGA 芯片仍是基于 SRAM 工藝的查找表結(jié)構(gòu)。

2022-11-29 10:10:57 5648

5648 電子發(fā)燒友網(wǎng)站提供《基于FPGA+DSP模式的智能相機設(shè)計.pdf》資料免費下載

2023-10-08 10:37:16 3

3 FPGA可以反復(fù)的重新配置,這就意味著設(shè)計者可以不斷的反復(fù)的下載設(shè)計的邏輯做驗證。如果出現(xiàn)錯誤或者需要升級,只需要修改設(shè)計,重新下載設(shè)計邏輯電路即可。FPGA雖然有重新配置的優(yōu)勢,帶來的不利就是它

2024-10-24 18:13:41 1988

1988

FPGA+DSP核心板是基于中科億海微EQ6HL130型FPGA芯片搭配國產(chǎn)DSP開發(fā)的高性能核心板卡。對外接口采取郵票孔連接方式,可以極大提高信號傳輸質(zhì)量和焊接后的機械強度。核心板卡的系統(tǒng)框圖如下

2025-06-20 14:12:22 912

912

電子發(fā)燒友App

電子發(fā)燒友App

評論