作為賽靈思的現(xiàn)場工程師,我常常問這樣的問題:我們是否能夠提供一款其功能可滿足客戶所有獨特設(shè)計要求的DSP內(nèi)核。有時候內(nèi)核會太大,太小或者不夠快。有時,我們會開發(fā)一款能確切滿足客戶需求的內(nèi)核,并迅速以CORE GeneratorTM商標(biāo)推出。不過即便在這種情況下,客戶仍然想要一套特定的DSP功能,而且刻不容緩。在這些情況下,我常常建議他們使用我們器件中的插值查找表來定制他們的DSP功能。

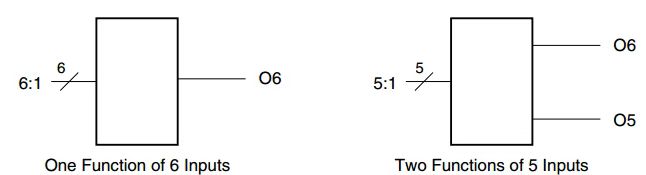

查找表 (LUT) 實質(zhì)上是一個存儲元件,能夠根據(jù)任何給定的輸入狀態(tài)組合,“查找”輸出,以確保每個輸入都有確切的輸出。采用LUT來實現(xiàn) DSP功能具有一些重大優(yōu)勢:

您可用諸如MATLAB?或Simulink?等高抽象層編程語言改變LUT內(nèi)容。

您可以設(shè)計一項DSP功能來運行那些采用離散邏輯運算將極度困難的數(shù)學(xué)函數(shù),比如 y=log(x)、y=exp(x)、y=1/x、y=sin(x) 等。

LUT還可輕松執(zhí)行在可配置邏輯塊 (CLB) 芯片,以及嵌入式乘法單元或DSP48可編程乘法累加 (MAC) 單元方面可能要求過多FPGA資源的復(fù)雜數(shù)學(xué)函數(shù)。

不過,以這種方式使用LUT當(dāng)然也會存在一些弊端。當(dāng)您使用LUT來實現(xiàn)DSP功能時,您必須使用塊RAM (BRAM) 元件。若執(zhí)行函數(shù) y=sqrt(x)(其中x 表示16位輸入,y 表示18位輸出),每個變量則需要約64個18KB BRAM單元。如果,比如說,您的目標(biāo)是實現(xiàn)小型化Spartan?器件,或者您有太多的運算需要執(zhí)行,無法為每個變量省出64個BRAM單元,建議您放棄這種需要如此大量BRAM單元的方法,從系統(tǒng)架構(gòu)的角度來看,這種方法代價太大。

插值LUT方法不僅具有LUT方法在實現(xiàn)DSP功能時所帶來的各種優(yōu)勢,而且無需使用太多BRAM單元。采用這種方法,您可以使用來自容量較小的LUT (比如,1000字 LUT)的連續(xù)輸出,線性地對其內(nèi)插,以模擬更大容量的LUT。這樣,您就可以實現(xiàn)比1000 字 LUT 更高的數(shù)值分辨率。此外,通過這種方法,僅需 1 個 BRAM、1 個嵌入式乘法器(或DSP48),以及少數(shù)幾個CLB芯片便可實施控制邏輯,因此LUT的使用成本變得更加合理化。而且,從信噪比的角度來看,其數(shù)值精度也是非常讓人滿意。

當(dāng)然,應(yīng)用插值LUT (ILUT) 方法需要一定的技巧。舉例來說,采用該方法執(zhí)行y=sqrt(x) 函數(shù)時,可以清楚地顯示ILUT在面積占用、時序和數(shù)值精度方面的性能。我們先大致看一下這個示例,然后我再講解部分實例,說明如何使用這種方法來滿足客戶截然不同的需求,比如讓傳遞函數(shù)呈非線性的傳感器實現(xiàn)線性化,以及實施自適應(yīng)有限脈沖響應(yīng)(FIR) 濾波器以消除合成孔徑雷達(dá) (SAR) 圖像上的斑點噪聲。

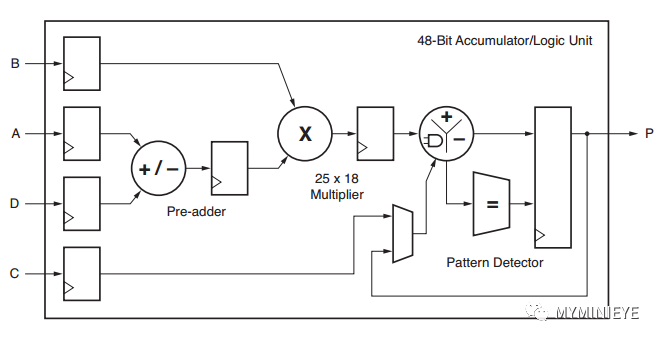

圖 1. System Generator for DSP中插值查找表頂層方框圖

使用System Generator for DSP進(jìn)行設(shè)計

為在賽靈思FPGA上實施DPS算法,我借助了采用MathWorks Simulink基于模型設(shè)計方法的System Generator for DSP設(shè)計與綜合工具。System Generator得益于賽靈思在Simulink 環(huán)境中的DSP模塊組,可自動調(diào)用CORE Generator為DSP構(gòu)建塊生成高度優(yōu)化的網(wǎng)表。Simulink是一種雙精度浮點設(shè)計工具,而System Generator則是一款定點運算工具。不管怎樣,您只要將這兩種工具協(xié)同使用,就可以定義每個信號的總位數(shù)以及每個信號的二進(jìn)制位置,從而在定點運算中巧妙處理分?jǐn)?shù)。仿真結(jié)果周期精確、位真,因此您可以方便地將它們與MATLAB腳本或Simulink模塊生成的浮點參考值相比較,以檢查量化誤差。

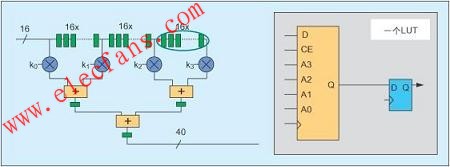

圖1顯示了System Generator中ILUT方案的頂層結(jié)構(gòu)圖。為讓這個方法盡可能一般化,假設(shè)nx=16位中的輸入變量 x 的取值范圍為0≤x<1,因此其格式為“無符號16位加上二進(jìn)制點右邊的16 位”,也稱為Ufix_16_16格式。最高有效位 (MSB) 和最低有效位 (LSB) 模塊分別對應(yīng)輸入數(shù)據(jù)nb=10的最高位和nx-nb=6的最低位。這些信號被命名為x0和dx。y=sqrt(x) 輸出則以ny=17位二進(jìn)制數(shù)表示,格式為:Ufix_17_17。

圖2顯示了1000字小容量LUT通過雙端口RAM模塊的部署步驟。由于該模塊系只讀存儲器,布爾常數(shù)模塊We_const強(qiáng)制將寫入歸零。信號X0和X0+1則用作ROM表上后續(xù)的兩個地址。Data_const模塊的零常數(shù)定義了任何ROM字的大小(即本例中的ny)。

下面的公式顯示了以x0為x的最高有效位的情況下,如何在兩個已知點(x0,y0)和(x1,y1)之間插入坐標(biāo)為(x,y)的點:

注意X1和X0是這個小容量LUT的相鄰地址,它們之間只隔了一個最低有效位。由于這個小容量LUT的地址空間為nb 位,那么該LSB的值為2-nb。

圖2 System Generator for DSP中的小容量LUT圖

圖3 System Generator for DSP的線性內(nèi)插圖

內(nèi)插步驟見圖3。“Reinterpret”模塊在不改變二進(jìn)制表示法的情況下,可改變dx=x-x0信號。其重置了二進(jìn)制小數(shù)點(從UFix_6_0到UFix_6_6格式),并輸出nx-nb位二進(jìn)制數(shù)的一個分?jǐn)?shù),從而計算出 (x-x0)/2-nb 的值。

從硬件角度來看,這些模塊什么都不占用。總的來說(且根據(jù)我們通過ILUT方法應(yīng)用的函數(shù)類型),如果y1=0且y0=0,我們可以強(qiáng)制y1-y0=1,這樣我們就可以得到1/2-nb而不是0。我們采用Mux、Rational、Constant和Constant1模塊來執(zhí)行這項工作。剩下的Mult、Add和Sub模塊則執(zhí)行線性內(nèi)插公式。在本例中,我強(qiáng)制Mult模塊的輸出信號為17位分辨率,而非理論上要求的23位,因為總體數(shù)值精度對本試驗來說已經(jīng)足夠。此外,由于y-sqrt(x) 函數(shù)呈單調(diào)遞增,因此所有結(jié)果都無符號。換句話說,不同的函數(shù)需要對數(shù)據(jù)類型進(jìn)行不同的精心調(diào)整,但不會與圖3所示的原理相去甚遠(yuǎn)。

假定我們以Spartan-3E 1200(fg320-4)為目標(biāo)器件,現(xiàn)使用ISE設(shè)計套件和System Generator for DSP 10.1 SP3版工具對其進(jìn)行布局和布線,結(jié)果其所占用的FPGA資源的總體情況如下:

該設(shè)計完全流水線作業(yè),可以在任何一個時鐘周期提供新的輸出。時延為10個時鐘周期,最大數(shù)據(jù)速率達(dá)194.70MSPS(每秒百萬采樣數(shù))。從數(shù)值精度來說,對1000或2000字ILUT而言,參考浮點結(jié)果與System Generator for DSP定點輸出的量化誤差之間的比值,即信噪比分別為 71.94dB或77.95dB。

除ILUT外,我們還可應(yīng)用賽靈思System Generator for DSP提供的Reference Math Blockset(參考數(shù)學(xué)模塊組)中的CORDIC SQRT模塊。在本例中,總時延為37個時鐘周期,最大數(shù)據(jù)速率達(dá)115.18 MSPS,區(qū)域資源占用為940片觸發(fā)器,總共有885個四輸入LUT,560個占用的芯片以及兩個MULT 18x18嵌入式乘法器。信噪比為40.64dB。這些結(jié)果顯示CORDIC是實施定點數(shù)學(xué)運算的理想方法,但I(xiàn)LUT在許多方面更加出色。

線性化非線性傳感器

目前許多企業(yè)在工業(yè)控制系統(tǒng)中使用“智能傳感器”,以滿足低占用面積、低功耗、高性能、最低成本以及最短開發(fā)時間等要求。通用智能傳感器可視為一個由傳感器及其信號控制線路、模數(shù)轉(zhuǎn)換器 (ADC) 、帶或不帶嵌入式處理器的相關(guān)DSP子系統(tǒng)組成的功能組件,所有這些功能塊都集成在的同一器件上,如圖4所示。

智能傳感器的目的是將物理量(如電機(jī)中的電流)轉(zhuǎn)化為數(shù)字電路能夠處理的數(shù)字信號。構(gòu)建這類傳感器所采用的技術(shù)及組件的某些特性通常會導(dǎo)致諸如失調(diào)、增益和非線性等誤差,進(jìn)而導(dǎo)致總體傳遞函數(shù)呈非線性。

一般來說,客戶會校正他們產(chǎn)品中運行的DSP子系統(tǒng)所出現(xiàn)的上述誤差。如果 y=f(x) 是來自傳感器和ADC級聯(lián)的數(shù)字輸出信號,那么DSP必須執(zhí)行其反函數(shù)g(y)=f-1(y) 來補(bǔ)償非線性函數(shù),這樣總體輸出z即為:

這是直線方程,其斜率為m,縱截距為b。

圖4. 智能傳感器的方框圖

最簡單的線性化方法是LUT法,采用存儲在ROM中的傳感器校準(zhǔn)點。不過,對16位的ADC來說,ROM顯得過大了,且需要64個BRAM單元。而內(nèi)插LUT則不然,是一個良好的解決方案。

舉例來說,我們假定非線性傳遞函數(shù)是一條拋物線。下一 MATLAB分段碼說明了如何生成最終直線的m和b參數(shù),以及如何計算 g(y)(即 f(x) 的反函數(shù))。圖5用三種顏色顯示了三條不同曲線。請注意在計算 f(x) 的反函數(shù) g(y) 過程中會丟失一些值。這是因為有幾個y值相同的點對應(yīng)著不同的x點。因此,需要對 g(y) 進(jìn)行平滑化,填補(bǔ)所有缺失的點。(為精確起見,我沒有把這部分運算包括在MATLAB分段碼中)

圖5.黑色拋物線表示非線性傳感器傳遞函數(shù)f(x) 的曲線;綠色直線表示線性化DSP子系統(tǒng)獲得的最終線性傳感器傳遞函數(shù)曲線;藍(lán)色拋物線則表示反函數(shù)g(y) 的曲線。

我采用非常類似于圖1-3的設(shè)計,在System Generator for DSP中運行基于定點周期的仿真,在非線性傳感器的總體輸出范圍內(nèi)得到了92.48dB的信噪比。

斑點噪聲消除

跟蹤高速運動系統(tǒng)的目標(biāo)物體(比如導(dǎo)彈)是一項極富挑戰(zhàn)性的工作,需要非常復(fù)雜的DSP算法以及諸如合成孔徑雷達(dá) (SAR) 等各種不同類型的探測介質(zhì)。作為典型的相干電磁源(如激光),SAR成像器件也受斑點噪聲的影響。因此,任何基于SAR的DSP鏈的第一級都是二維 (2D) 自適應(yīng)FIR濾波器,用以降低這種噪聲(但不可能完全消除)。圖6顯示了斑點噪聲的MATLAB仿真。該噪音對左邊圖像的畫質(zhì)造成了綜合性的不良影響。右邊的圖像是2D FIR濾波器黃金模型的輸出結(jié)果。

圖 6. 斑點噪聲對左邊圖像畫質(zhì)造成了影響,右邊的是濾波后的圖像

斑點噪聲是一種倍增噪聲,呈指數(shù)分布,完全由其方差值σ決定。因此,廣泛使用的抗斑點噪聲的方法就是Frost濾波器(由發(fā)明者 V.S.Frost的名字命名而來)。V.S.Frost 在1981年發(fā)表的論文對這個現(xiàn)象進(jìn)行了探討。在一個3x3的矩陣中,可以用下列公式進(jìn)行建模:

其中xij和yij分別代表Frost濾波器的輸入和輸出采樣。K 是控制濾波強(qiáng)度的增益系數(shù)(為方便起見,我在下面假定K=1),μ1和σ分別是2D內(nèi)核的平均值和方差值,Tij是中心輸出像素(系數(shù)ij=22)及所有周邊像素的距離矩陣。下面的等式說明實施這個濾波器的關(guān)鍵因素是R1,即3x3矩陣中的一階μ1和二階μ2之間的比值:

R1的取值范圍在0和1之間。根據(jù)實驗發(fā)現(xiàn)要取得良好的數(shù)值精度,R1可以使用16位至20位二進(jìn)制數(shù)來表示。

我在system Generator for DSP中設(shè)計R1計算步驟后,我決定通過內(nèi)插LUT來實施濾波系數(shù)的歸一化。LUT的內(nèi)容以下列MATLAB代碼表示:

圖7顯示的是歸一化后的系數(shù)沿R1輸入信號分布的曲線。這里只有三條曲線,因為 Tij矩陣在系數(shù) ij=22的中心像素周圍呈對稱分布。根據(jù)曲線,與純浮點參考模型相比,數(shù)值結(jié)果顯示信噪比介于81.28至83.38dB之間。對有興趣的讀者,下面的MATLAB分段碼說明了2D濾波器的處理過程(為簡便起見,沒有包括ILUT函數(shù))。

圖7 沿斑點噪聲降噪濾波參數(shù) R1 分布的歸一化系數(shù)

簡言之,這些例子說明插值查找表是實施賽靈思FPGA的DSP功能的簡便而強(qiáng)大的方法。插值查找表可幫助您在保持面積占用相對較低的情況下實現(xiàn)極高數(shù)值精度 (SNR) 和高數(shù)據(jù)速率。

電子發(fā)燒友App

電子發(fā)燒友App

評論