我們知道FPGA由LUT、IO接口、時鐘管理單元、存儲器、DSP等構成,我覺得最能代表FPGA特點的就是LUT了。當然不同廠家、同一廠家不同階段FPGA的LUT輸入數量是不同的,隨著技術的發展,LUT的輸入數量也在增加。

作為FPGA最基本的電路單元,承擔著各種電路功能的實現,如果能夠理解LUT對電路的實現及影響,對我們進行FPGA開發及優化有著至關重要的作用。如果電路的輸入數量遠大于LUT的輸入數量,LUT在實現電路時必然采用級聯方式,級聯數量必定會造成電路的延時,有時候會嚴重制約系統的最高運行頻率。

如果我們能夠理解好這一點,那么我們在設計電路的時候就要盡量避免級聯級數太多,對電路進行優化,比如插入寄存器等方式來減少電路的延時,保證系統的正常運行。

附XILINX 7Series基本邏輯單元框圖

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636205 -

存儲器

+關注

關注

39文章

7738瀏覽量

171650 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131115 -

時鐘

+關注

關注

11文章

1971瀏覽量

134982 -

LUT

+關注

關注

0文章

52瀏覽量

13142

原文標題:關于FPGA四輸入、六輸入基本邏輯單元LUT的一點理解

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

請教ALTERA的FPGA什么時候開始使用6輸入LUT?

`Xilinx片子一般從65nm工藝以上就使用6輸入LUT,新器件的Slice包含4個6輸入LUT和8個寄存器等。Cyclone V的片子是

發表于 10-26 10:58

FPGA基礎知識0(查找表LUT和編程方式)

Flash或者熔絲與反熔絲工藝的查找表結 構。通過燒寫文件改變查找表內容的方法來實現對FPGA的重復配置。 根據數字電路的基本知識可以知道,對于一個n輸入的邏輯運算,不管是與或非運算還

發表于 05-09 15:04

如何在LUT和邏輯元件之間以及邏輯元件和邏輯單元之間進行交換

嗨,我目前正在對設計進行初步分析。我正在研究關于實現不同功能所需資源的不同FPGA。我找不到一種方法來將設計使用的LUT數量相關聯,并將其轉換為virtex和spartan范圍的

發表于 01-08 10:18

Spartan 6 FPGA LUT中是否有pmos和nmos transisors?

transisors?Spartan 6有6個輸入LUT,所以如果我想實現一個簡單的兩個輸入“和”門,那么其他四個

發表于 08-09 09:16

解析數字電路的與、或、非等邏輯是通過 6 輸入的查找表實現

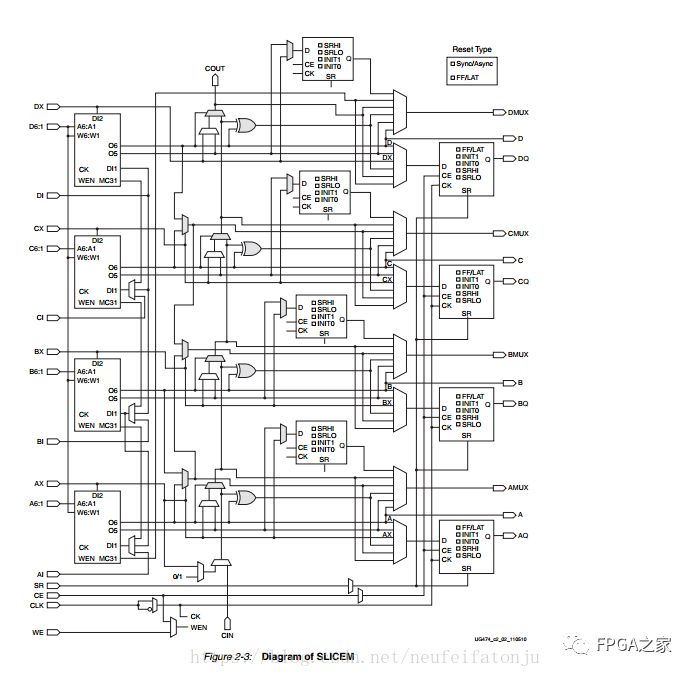

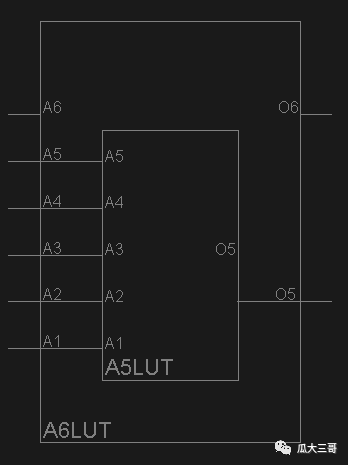

在 7 系列中實現數字電路的與、或、非等邏輯是通過 6 輸入的查找表實現的。LUT 有 6 個輸入(A1~A6)和 2 個輸出(O5~O6)。在一

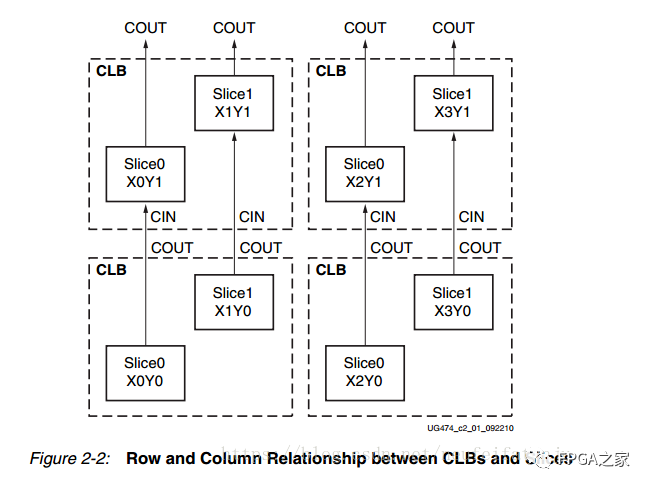

一文詳解xilinx CLB基本邏輯單元

CLB是xilinx基本邏輯單元,每個CLB包含兩個slices,每個slices由4個(A,B,C,D)6輸入LUT和8個寄存器組成。

關于FPGA四輸入、六輸入基本邏輯單元LUT的一點理解

關于FPGA四輸入、六輸入基本邏輯單元LUT的一點理解

評論