在 FPGA 開發(fā)過程中,燒寫bit文件和使用ILA進行調(diào)試是再常見不過的操作。但如果 FPGA 板卡被放在機房,或者通過PCIe插在服務(wù)器上,那么每次調(diào)試時我們都不得不帶著筆記本電腦跑去機房或服務(wù)器旁,接上 JTAG 線后才能進行調(diào)試,非常不便。

2025-06-05 16:41:28 2215

2215

在Vivado中,VIO(Virtual Input/Output)是一種用于調(diào)試和測試FPGA設(shè)計的IP核,它允許設(shè)計者通過JTAG接口實時讀取和寫入FPGA內(nèi)部的寄存器,從而檢查設(shè)計的運行狀態(tài)并修改其行為。VIO IP核提供了一個簡單易用的接口,使得用戶可以輕松地與FPGA內(nèi)部寄存器進行交互。

2025-06-09 09:32:06 3372

3372

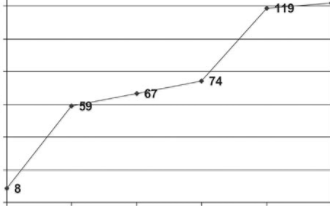

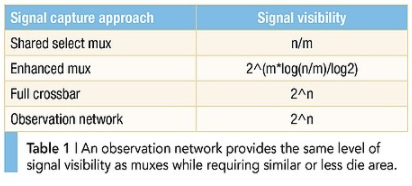

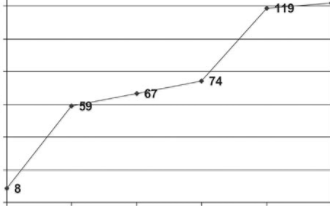

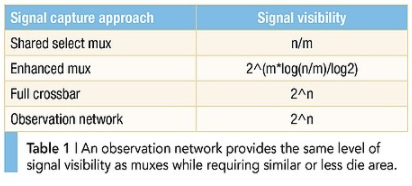

隨著FPGA融入越來越多的能力,對有效調(diào)試工具的需求將變得至關(guān)重要。對內(nèi)部可視能力的事前周密計劃將能使研制組采用正確的調(diào)試戰(zhàn)略,以更快完成他們的設(shè)計任務(wù)。

2011-01-23 10:13:17 1176

1176

FPGA調(diào)試時硬件設(shè)計中及其重要的一步,本文就在FPGA調(diào)試過程中存在3種常見的誤解,進行一些討論....

2018-09-19 09:27:50 4748

4748 在某FPGA系統(tǒng)中,對電源系統(tǒng)進行調(diào)試,在同樣的測試條件下,發(fā)現(xiàn)其中有一塊板相對其它的板功耗總偏大,進而對其進行調(diào)試分析。

2022-10-20 09:13:11 4748

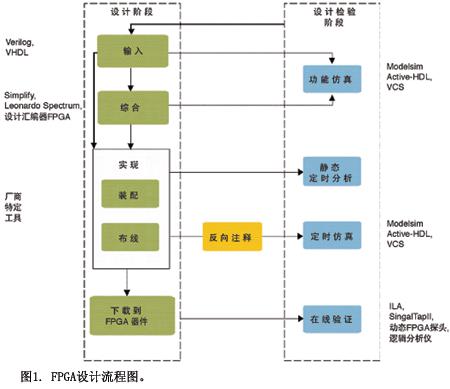

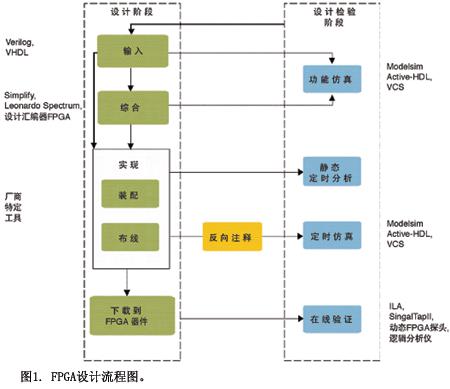

4748 FPGA設(shè)計流程是利用EDA開發(fā)軟件和編程工具對FPGA芯片進行開發(fā)的過程。FPGA的設(shè)計流程如上圖所示:包括設(shè)計定義、代碼實現(xiàn)、功能仿真、邏輯綜合、前仿真、布局布線、后仿真和板級調(diào)試等步驟!

2023-04-04 10:29:51 3088

3088 日常的FPGA開發(fā)常常會遇到“編碼與上機調(diào)試使用各自的電腦”的場景,解決方法一般如下。

2023-05-25 14:36:44 4304

4304

上篇主要是分享了Vivado編譯軟件遠(yuǎn)程調(diào)試的方法。杰克使用Vivado軟件進行遠(yuǎn)程連接,主要是用于固化程序以及FPGA(PL端)的異常排查。而本篇主要內(nèi)容是對使用Vitis軟件遠(yuǎn)程調(diào)試的方法進行總結(jié)和分享。

2023-05-25 14:36:58 4231

4231

今天跟大家分享的內(nèi)容很重要,也是調(diào)試FPGA經(jīng)驗的總結(jié)。隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設(shè)計越來越多。在調(diào)試這些FPGA樣機時,需要從寫代碼時就要小心謹(jǐn)慎,否則寫出來的代碼

2023-08-01 09:18:34 3075

3075

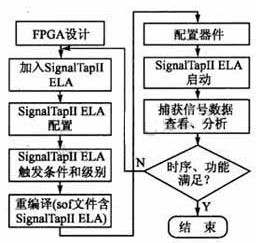

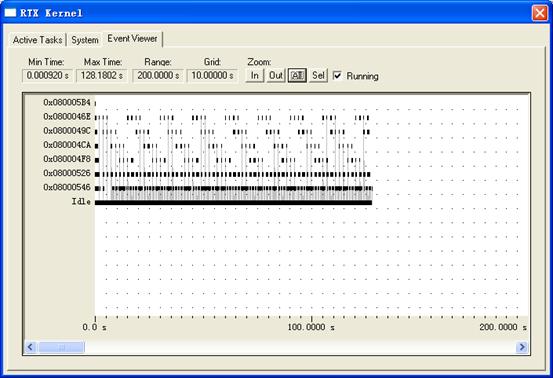

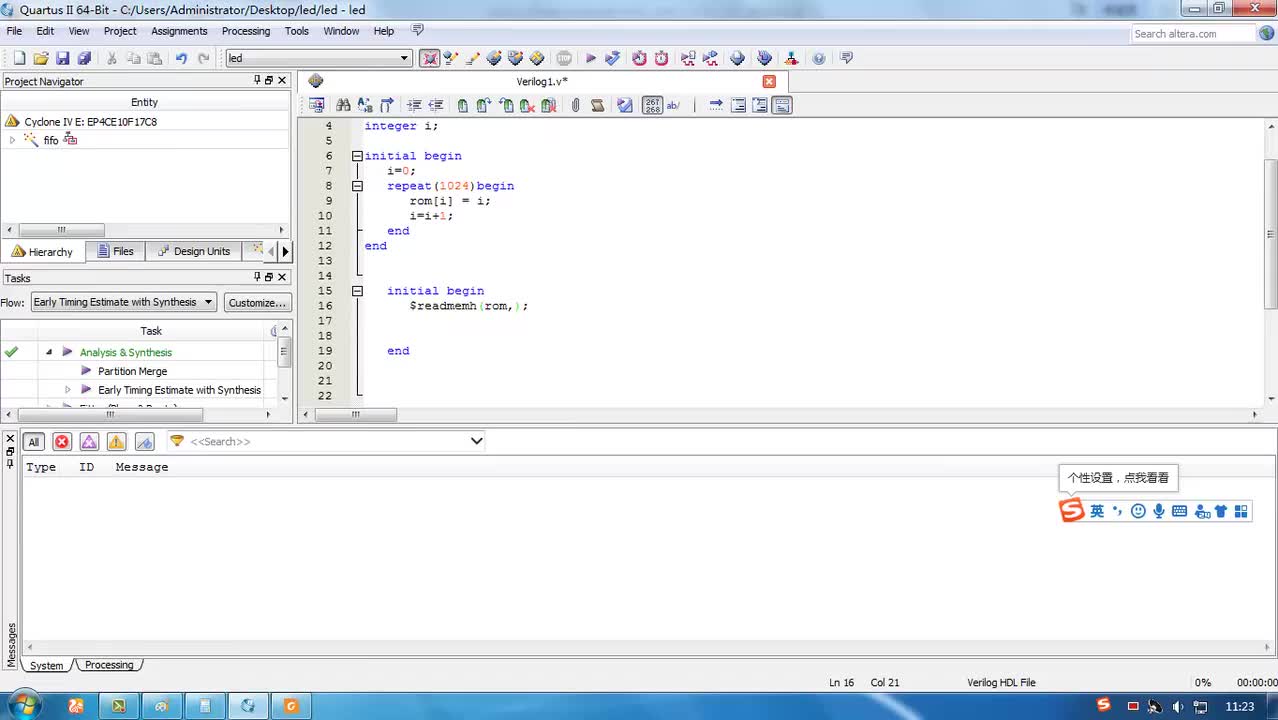

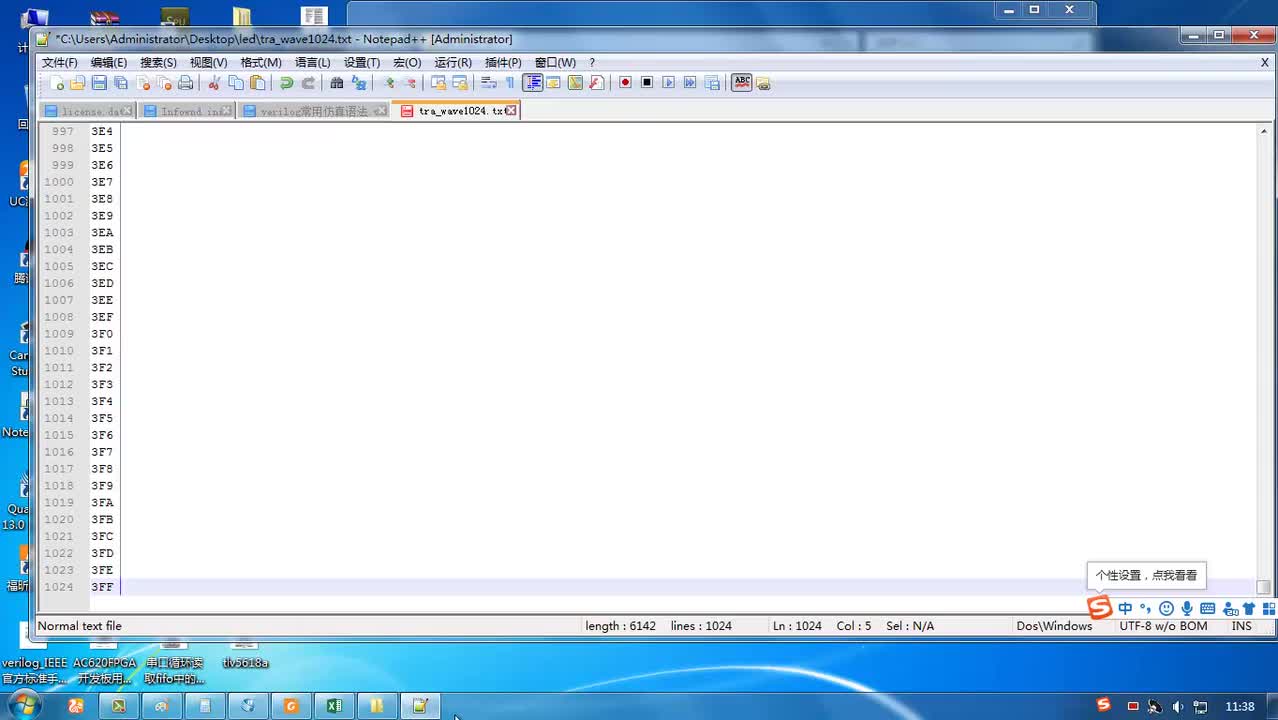

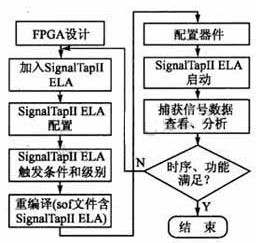

對于FPGA調(diào)試,主要以Intel FPGA為例,在win10 Quartus ii 17.0環(huán)境下進行仿真和調(diào)試,開發(fā)板類型EP4CE15F17。

2024-01-12 09:34:14 4177

4177

調(diào)試,即Debug,有一定開發(fā)經(jīng)驗的人一定會明確這是設(shè)計中最復(fù)雜最磨人的部分。對于一個龐大復(fù)雜的FPGA工程而言,出現(xiàn)問題的概率極大,這時如果沒有一個清晰的Debug思路,調(diào)試過程只能是像無頭蒼蠅一樣四處亂撞。

2025-03-04 11:02:19 1758

1758

。由于一般的集成電路自動測試儀ATE為通用IC測試設(shè)計,但FPGA測試有上述特殊性,在芯片功能測試之前必須對其進行特定的配置,否則芯片是不具備內(nèi)部電路結(jié)構(gòu)的,內(nèi)部資源將無法測試,而通用的ATE要完成

2020-05-14 07:00:00

的板級調(diào)試方法有很多,借助于常規(guī)的示波器和邏輯分析儀的調(diào)試方法是最典型的手段。如圖10.1所示,基于傳統(tǒng)的臺式示波器或邏輯分析儀進行板級調(diào)試有著諸多的不便,相對于設(shè)計電路深藏在芯片內(nèi)部的FPGA

2015-09-02 18:39:49

的代碼有更深刻體會;FPGA調(diào)試,解決bug問題和軟件調(diào)試過程一樣嗎,還是和硬件一樣完全黑盒調(diào)試(很多情況都是摸索,看看是不是電阻電容問題,干擾問題.....),解決bug的方式區(qū)別是什么???據(jù)說

2012-11-25 02:10:05

電源部分。使用萬用表進行測試,排除電源短路等情況后,上電測量電壓是否正確。(2)然后焊接FPGA及相關(guān)的下載電路。再次測量電源地之間是否有短路現(xiàn)象,上電測試電壓是否正確,然后將手排除靜電后觸摸FPGA

2012-08-12 11:52:54

最近一直在忙期末考試的事情,現(xiàn)在終于閑下來了,已經(jīng)把相應(yīng)的芯片期間買來了,正在進行FPGA與TFT彩屏通訊的測試

2012-07-06 17:55:39

我使用fpga跑一個arm的軟核,測試點亮一個led燈的程序。仿真結(jié)果與自己想要的結(jié)果是吻合的(頂層led的port是有輸出的),但是下載到fpga開發(fā)板上后,運行就沒有結(jié)果(連接頂層led的port測試沒有輸出)。請問如何去調(diào)試找出問題出在哪里?

2017-06-13 17:06:52

其切換到 FX3 SDK 1.3.4,則一切正常。

看來 SDK 1.3.5 中的預(yù)置庫出了問題,因為這是唯一真正發(fā)生變化的地方。

有辦法讓 SDK 1.3.5 與 JTAG 調(diào)試器配合使用嗎?

2025-05-23 07:32:08

需要各個儀表之間的配合(如同步等),此外還要照顧到由于衰減器和耦合器等周邊器件的引入導(dǎo)致的測試精度和準(zhǔn)確度的損失。雖然這種方式將導(dǎo)致很多麻煩,但由于這種測試解決方案便于白箱測試的擴展,比較適合于基站的研究開發(fā)領(lǐng)域,所以還是被基站研究開發(fā)領(lǐng)域所采用。那有什么辦法,可以進行WCDMA基站的綜合測試嗎?

2019-08-08 07:35:05

大家好,

我們現(xiàn)在用STM32H743ZIT6,在調(diào)試FreeRTOS + LWIP,發(fā)現(xiàn)SOCKET為堵塞方式,有什么辦法能將socket設(shè)置為非堵塞方式?用setsockopt函數(shù)設(shè)置,已經(jīng)測試過了,不起作用;大神們幫看下,多謝

2024-04-26 08:14:30

我采用TLV3501將混頻后的50Hz正弦波變成方波,然后送入FPGA,對方波信號進行檢測,發(fā)現(xiàn)方波信號有有毛刺導(dǎo)致FPGA誤觸發(fā),有什么辦法減少方波的毛刺呀

2025-05-28 10:31:52

在設(shè)計基于FPGA的電子系統(tǒng)時,一般需要用示波器、邏輯分析儀等外部測試設(shè)備進行輸入輸出信號的測試,借助測試探頭把信號送到測試設(shè)備上進行觀察分析。當(dāng)然,前提是需要保留足夠多的引腳,以便能選擇信號來驅(qū)動

2019-08-19 08:03:56

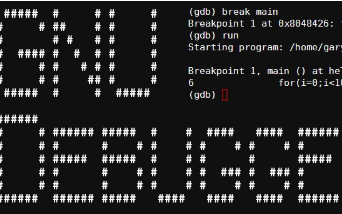

因為有很多的小伙伴是從單片機轉(zhuǎn)過來的,用慣了單片機上的JLINK調(diào)試程序,換到Linux上非常的不習(xí)慣。確實,如果能設(shè)置斷點,單步調(diào)試,查看變量,那確實是太爽了,那么在我們的Linux可以做到

2020-12-28 06:59:24

FPGA所需的.bit文件,并在DSP端執(zhí)行命令進行測試。(1)測試步驟?部署TFTP服務(wù)器打開TFTP服務(wù)器,路徑:"光盤資料/Demo/Hostapp

2018-10-31 14:27:30

嗨,我想測試一個芯片,并想知道Virtex 5評估板是否可行。芯片在晶圓上,我有探針探測它,然后我將探針卡連接到FPGA。我需要數(shù)字I / O(芯片上用于數(shù)字I / O的48個焊盤),模擬輸入(芯片上的14個模擬輸入焊盤)以及電源引腳。如果Virtex 5可以用于此目的,請告訴我嗎?謝謝

2020-06-17 11:00:29

我的設(shè)計完全在Verilog中,并且已經(jīng)使用Spartan FPGA進行了測試。我將源代碼提供給ASIC工廠,以實現(xiàn)作為ASIC使用他們(我認(rèn)為)的概要工具。我的問題是,有沒有辦法使用任何

2019-07-25 13:44:31

請問各位,開放式FPGA的常見測試應(yīng)用有哪些?

2021-05-06 09:53:50

,以便在較大的FPGA中達(dá)到高的系統(tǒng)吞吐量。如果懷疑內(nèi)部的32位總線里有壞的數(shù)據(jù),則難以用幾個I/O引腳來確定問題所在。 第三,通常需要在系統(tǒng)中測試復(fù)雜的功能。在這種情況下,在系統(tǒng)中調(diào)試時訪問一些I

2010-01-08 15:05:27

嗨,我使用的是spartan6 FPFA板,我已經(jīng)使用iMPACT將mcs文件配置到FPGA板中。有沒有辦法從FPGA讀回mcs文件?如果有辦法從fpga板讀回mcs文件,請告訴我。謝謝,拉胡爾庫

2019-07-11 07:28:53

`請問各路大神LTC3850GN有辦法測試好壞嗎`

2020-05-25 16:33:38

我閱讀過AN84868,了解到fx3可以對連接的FPGA芯片進行串行配置;但是我的項目中,希望能盡量縮短FPGA配置的時間,因此希望能夠了解是否有辦法使用fx3芯片對外接的FPGA芯片進行并行配置? 具體使用什么接口,例如gpio或者spi等?或者,是否有相關(guān)的文檔可以作為參考,謝謝!...

2024-05-28 08:30:33

潤和Hi3861V100芯片迷你無線仿真USB Open OCD調(diào)試板多功能調(diào)試器

2023-03-28 13:07:10

FPGA調(diào)試工具chipscope,學(xué)習(xí)與使用FPGA必用的工具。。

2009-03-23 09:45:00 86

86 USB-Blaster的特性: 支持USB Blaster下載仿真調(diào)試,通過計算機的USB接口可對Altera的FPGA/CPLD以及配置芯片進行編程、調(diào)試等操作

2022-07-27 10:31:29

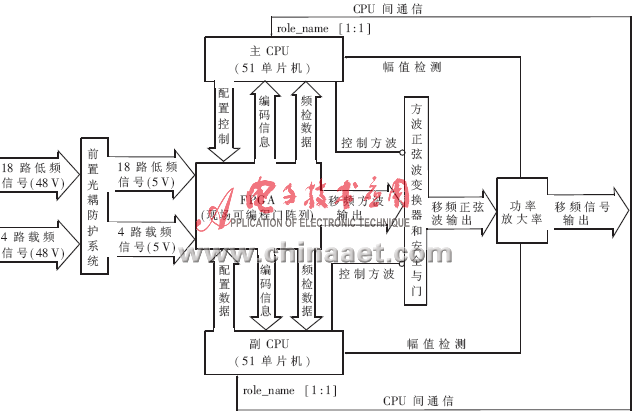

混合CPU_FPGA系統(tǒng)的調(diào)試方法:

2009-07-23 10:44:07 7

7 本文運用黑盒測試的基本理論,提出了FPGA邏輯設(shè)計的測試模型,分析了FPGA邏輯設(shè)計的基本方法和步驟,最后結(jié)合一個實際項目說明了FPGA邏輯設(shè)計的測試驗證過程。關(guān)鍵詞:黑盒

2009-08-19 09:12:41 9

9 簡化Xilinx和Altera FPGA調(diào)試過程:通過FPGAViewTM 解決方案,如混合信號示波器(MSO)和邏輯分析儀,您可以在Xilinx 和Altera FPGA 內(nèi)部迅速移動探點,而無需重新編譯設(shè)計方案。能夠把內(nèi)部FPGA

2009-11-20 17:46:26 27

27 實用FPGA的調(diào)試工具—ChipScope Pro

ChipScope Pro應(yīng)用于FPGA調(diào)試階段,它具有傳統(tǒng)邏輯分析儀的功能,可以觀察FPGA內(nèi)部的任何信號,觸發(fā)條件,數(shù)據(jù)寬度和深度等的設(shè)

2010-02-09 15:10:46 95

95 目錄•FPGA調(diào)試的挑戰(zhàn)•傳統(tǒng)的FPGA調(diào)試方案•Agilent FPGA動態(tài)探頭的調(diào)試方案•總結(jié)

2010-10-11 11:04:36 26

26 使用RealView MDK進行SW調(diào)試和實時跟蹤

STM32有兩個調(diào)試端口,即JTAG和SW。Keil 的ULINK2 USB

2008-08-02 09:27:50 4838

4838

FPGA 重復(fù)配置和測試的實現(xiàn)

從制造的角度來講,FPGA測試是指對FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測。完整的FPGA測試包括

2009-09-03 11:17:08 725

725

FPGA重復(fù)配置和測試的實現(xiàn)

從制造的角度來講,FPGA測試是指對FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA

2010-01-26 09:39:56 690

690

FPGA硬件系統(tǒng)的調(diào)試方法

在調(diào)試FPGA電路時要遵循一定的原則和技巧,才能減少調(diào)試時間,避免誤操作損壞電路。一般情況下,可以參考以下步驟進行

2010-02-08 14:44:42 3102

3102 在設(shè)計基于FPGA的電子系統(tǒng)時,一般需要用示波器、邏輯分析儀等外部測試設(shè)備進行輸入輸出信號的測試,借助測試探頭把信號送到測試設(shè)備上進行觀察分析。當(dāng)然,前提是需要保

2010-05-28 16:27:51 1007

1007

隨著 FPGA 的設(shè)計速度、尺寸和復(fù)雜度明顯增長,使得整個設(shè)計流程中的實時驗證和調(diào)試成為當(dāng)前FPGA 系統(tǒng)的關(guān)鍵部分。獲得FPGA 內(nèi)部信號有限、FPGA 封裝和印刷電路板(PCB)電氣噪聲,這一

2011-06-10 15:42:28 28

28 縱觀數(shù)字集成電路的發(fā)展歷史,電子產(chǎn)品的市場正在逐漸細(xì)分。本書主要重點介紹相關(guān)問題和技巧,幫助您在調(diào)試 FPGA 系統(tǒng)是提高您的工作效率。希望對您的工作學(xué)習(xí)有所幫助!

2011-07-11 16:49:37 406

406 本文就調(diào)試FPGA系統(tǒng)時遇到的問題及有助于提高調(diào)試效率的方法,針對Altera和Xilinx的FPGA調(diào)試提供了最新的方法和工具。

2011-09-27 14:28:39 1197

1197

基于對FPGA系統(tǒng)失效機理的深入分析, 提出了軟件測試技術(shù)在FPGA測試中的應(yīng)用, 并分析了其可行性; 通過對比FPGA與軟件系統(tǒng)的異同, 歸納出FPGA特有的測試要求,從而在軟件測試技術(shù)的基礎(chǔ)

2011-09-29 17:41:21 65

65 AS下載和調(diào)試接口電路(Altera FPGA開發(fā)板)如下圖所示:

2012-08-15 14:29:23 6161

6161

在調(diào)試FPGA電路時要遵循必須的原則和技巧,才能降低調(diào)試時間,防止誤操作損壞電路。通常情況下,參考以下步驟執(zhí)行 FPGA硬件系統(tǒng)的調(diào)試。 1、在焊接硬件電路前,首先要測試電路板

2013-01-16 11:59:58 6120

6120 在軟硬件的開發(fā)階段中,測試結(jié)果直接關(guān)系到這個軟硬件能否順利進行調(diào)試應(yīng)用。其中,硬件的測試往往容易受外界因素的影響,如環(huán)境、計算機設(shè)備等,可以通過一些仿真軟件來避免外界環(huán)境的影響,但是其測試速度比較慢

2017-11-18 05:46:28 2320

2320 部分組成。對FPGA進行測試要對FPGA內(nèi)部可能包含的資源進行結(jié)構(gòu)分析,經(jīng)過一個測試配置(TC)和向量實施(TS)的過程,把FPGA配置為具有特定功能的電路,再從應(yīng)用級別上對電路進行測試,完成電路的功能及參數(shù)測試。 2 FPGA的配置方法 對FPGA進行配置有多種方法可以選擇,包括邊界掃描配置方法等。

2017-11-18 10:44:37 3307

3307

針對FPGA的特點進行改進,形成了一套實用的FPGA測試方法。 現(xiàn)場可編程門陣列(FPGA)的出現(xiàn)大大壓縮了電子產(chǎn)品研發(fā)的周期和成本,由于FPGA器件具有高密度、低功耗、高速、高可靠性等優(yōu)點,在航空、航天、通信、工業(yè)控制等方面得到了大量應(yīng)用。隨著FPG

2018-01-19 22:34:59 3023

3023 在設(shè)計基于FPGA的電子系統(tǒng)時,一般需要用示波器、邏輯分析儀等外部測試設(shè)備進行輸入輸出信號的測試,借助測試探頭把信號送到測試設(shè)備上進行觀察分析。當(dāng)然,前提是需要保留足夠多的引腳,以便能選擇信號來驅(qū)動

2018-02-14 09:19:00 1054

1054 本文檔內(nèi)容介紹了基于chipscope使用教程以及FPGA在線調(diào)試的方法,供參考

2018-03-02 14:09:49 9

9 電路調(diào)試與測試原因有哪些?

2018-04-09 15:43:49 42

42 對MAX10 FPGA 開發(fā)套件進行以太網(wǎng) Ping 測試

2018-06-20 01:00:00 5655

5655

本文重點介紹在調(diào)試FPGA系統(tǒng)時遇到的問題及有助于提高調(diào)試效率的技術(shù),針對Altera和Xilinx的FPGA調(diào)試提供了最新的方法和工具。

2018-11-28 08:43:00 3254

3254

在設(shè)計基于FPGA的電子系統(tǒng)時,一般需要用示波器、邏輯分析儀等外部測試設(shè)備進行輸入輸出信號的測試,借助測試探頭把信號送到測試設(shè)備上進行觀察分析。當(dāng)然,前提是需要保留足夠多的引腳,以便能選擇信號來驅(qū)動

2019-01-08 08:29:00 2292

2292

EP2C5Q208 上,進行在線編程調(diào)試,實現(xiàn)了串行通信控制功能。基于FPGA 的系統(tǒng)設(shè)計調(diào)試維護方便、可靠性高,而且設(shè)計具有靈活性,可以方便地進行擴展和移植。

2018-11-07 11:18:23 6

6 在SDAccel中進行調(diào)試

2018-11-29 06:20:00 2282

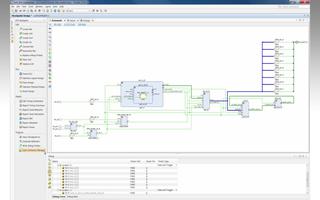

2282 了解使用Vivado 2016.1中引入的ECO流程進行調(diào)試的好處,以及在ECO布局中替換ILA調(diào)試探針?biāo)璧牟襟E。

2018-11-29 06:01:00 4313

4313

這十年來我做過小的嵌入式系統(tǒng),大的電信系統(tǒng)以及基于web的系統(tǒng)。使用過C ++,Ruby,Java和Python等。這篇文章中的經(jīng)驗教訓(xùn)旨在幫助減少編碼、測試和調(diào)試三個階段的bug。

2019-02-11 16:52:45 3575

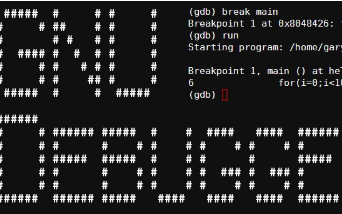

3575 無論多么有經(jīng)驗的程序員,開發(fā)的任何軟件都不可能完全沒有 bug。因此,排查及修復(fù) bug 成為軟件開發(fā)周期中最重要的任務(wù)之一。有許多辦法可以排查 bug(測試、代碼自審等等),但是還有一些專用軟件(稱為調(diào)試器)可以幫助準(zhǔn)確定位問題的所在,以便進行修復(fù)。

2019-05-15 16:39:51 933

933

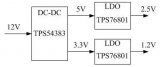

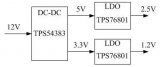

在某FPGA系統(tǒng)中,對電源系統(tǒng)進行調(diào)試,在同樣的測試條件下,發(fā)現(xiàn)其中有一塊板相對其它的板功耗總偏大,進而對其進行調(diào)試分析。在該系統(tǒng)中,輸入電壓為DC12V,輸出電壓有:5V、3.3V、2.5V和1.2V,綜合考慮電源紋波和轉(zhuǎn)換效率,在該系統(tǒng)中采用了DC-DC和LDO。

2019-07-27 09:19:36 3686

3686

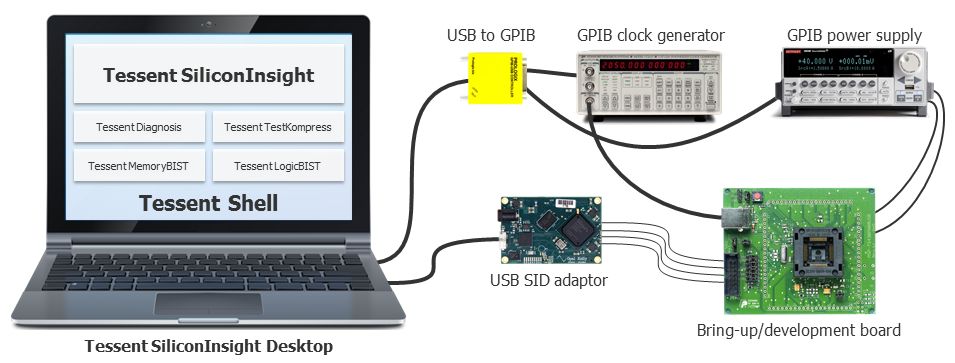

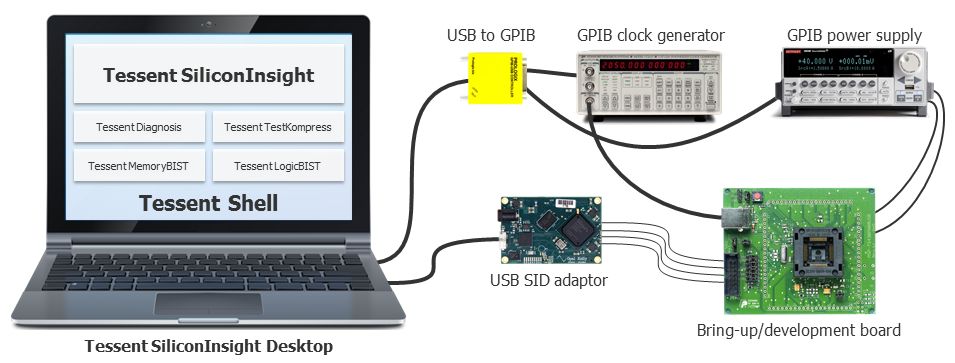

盡管業(yè)界廣泛采用IJTAG(IEEE 1687)測試架構(gòu)進行芯片級測試,但很多公司在芯片級測試向量轉(zhuǎn)換,以及自動測試設(shè)備 (ATE) 調(diào)試測試保留了非常不同的方法。因此,每個特定芯片必須由 DFT 工程師編寫測試向量,然后由測試工程師進行轉(zhuǎn)換,以便在每種測試儀類型上調(diào)試每個場景。

2019-10-11 15:36:23 4952

4952

對于FPGA調(diào)試,主要以Intel FPGA為例,在win10 Quartus ii 17.0環(huán)境下進行仿真和調(diào)試,開發(fā)板類型EP4CE15F17。

2020-03-29 11:37:00 1630

1630 進行硬件設(shè)計的功能調(diào)試時,FPGA的再編程能力是關(guān)鍵的優(yōu)點。CPLD和FPGA早期使用時,如果發(fā)現(xiàn)設(shè)計不能正常工作,工程師就使用“調(diào)試鉤”的方法。先將要觀察的FPGA內(nèi)部信號引到引腳,然后用外部的邏輯分析儀捕獲數(shù)據(jù)。

2020-09-14 15:08:00 909

909

FPGA概述FPGA調(diào)試介紹調(diào)試挑戰(zhàn)設(shè)計流程概述■FPGA調(diào)試方法概述嵌入式邏輯分析儀外部測試設(shè)備■使用 FPGAVIEW改善外部測試設(shè)備方法■FPGA中高速O的信號完整性測試和分析

2020-09-22 17:43:21 12

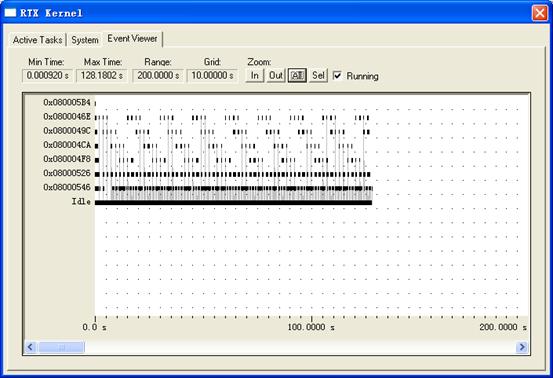

12 在線調(diào)試也稱作板級調(diào)試,它是將工程下載到FPGA芯片上后分析代碼運行的情況。

2020-11-01 10:00:49 5441

5441

焊接變位機如何進行調(diào)試?在正式使用焊接變位機進行焊接之前,要注意對設(shè)備的調(diào)試方法,并注意使用,從而保證焊接精度,我們需要根據(jù)合理的調(diào)試流程進行,可以幫助焊接變位機穩(wěn)定發(fā)揮,青島賽邦小編帶您了解焊接

2021-11-02 16:57:26 3551

3551 FPGA與STM32等嵌入式開發(fā)最大的一個優(yōu)點就是,可以在時序仿真階段驗證超過90%的功能,發(fā)現(xiàn)90%的問題。當(dāng)所有的仿真沒問題了,才能進行最...

2022-01-25 17:28:09 1

1 使用Jtag Master調(diào)試FPGA程序時用到tcl語言,通過編寫tcl腳本,可以實現(xiàn)對FPGA的讀寫,為調(diào)試FPGA程序帶來極大的便利,下面對FPGA調(diào)試過程中常用的tcl語法進行介紹,并通過tcl讀FIFO的例子,說明tcl在實際工程中的應(yīng)用。

2022-02-19 19:44:34 3645

3645 對FPGA進行上板調(diào)試時,使用最多的是SignalTap,但SignalTap主要用來抓取信號時序,當(dāng)需要發(fā)送信號到FPGA時,Jtag Master可以發(fā)揮很好的作用,可以通過Jtag Master對FPGA進行讀寫測試

2022-02-16 16:21:36 3151

3151

在某FPGA系統(tǒng)中,對電源系統(tǒng)進行調(diào)試,在同樣的測試條件下,發(fā)現(xiàn)其中有一塊板相對其它的板功耗總偏大,進而對其進行調(diào)試分析。

2022-04-26 13:45:38 7122

7122 隨著復(fù)雜性的增加和對探測點的訪問受限,ASIC 和 FPGA 驗證和調(diào)試變得乏味且耗時。隨著越來越多的功能集成到每個芯片中,對探測點的物理訪問變得不可能。接下來的挑戰(zhàn)是整合足夠的片上觀察點,不僅可以處理預(yù)期的調(diào)試場景,還可以處理意外的調(diào)試場景。

2022-07-09 06:54:00 843

843

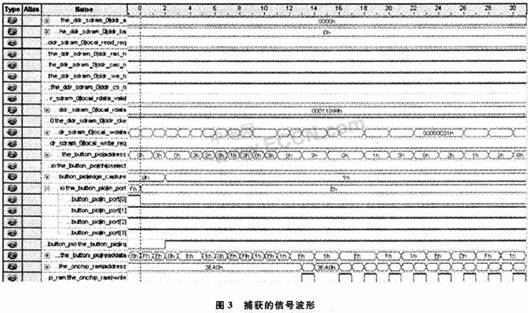

本設(shè)計對系統(tǒng)的性能和系統(tǒng)的功能分別進行了測試,性能測試是對FPGA的資源利用情況和運行速度情況進行測試,功能測試有腐蝕算法測試,幀差算法測試,定位功能調(diào)試等。

2023-02-07 10:47:19 679

679 Xilinx LabTools工具是Xilinx FPGA單獨的編程和調(diào)試工具,是從ISE或Vivado中獨立出來的實驗室工具,只能用來下載FPGA程序和進行ILA調(diào)試,支持所有的FPGA系列,無需

2023-03-28 10:46:56 9161

9161 之前介紹過一種遠(yuǎn)程(無線)更新的方式,詳見《起飛!通過無線WIFI下載調(diào)試FPGA》,這種方式缺點有兩個:一是速度較慢;二是我們的設(shè)備中需要增加一個無線設(shè)備,增加成本的同時增加了暴露的風(fēng)險。這兩點即無法在調(diào)試的時候使用也沒辦法在實際設(shè)備中使用。今天我們再介紹另一種簡單方式。

2023-05-25 09:23:03 4492

4492

剖析》分析了用戶在進行大規(guī)模原型驗證過程中的多FPGA聯(lián)合調(diào)試難題,并介紹了一種新型FPGA原型驗證深度跟蹤調(diào)試解決方案,用于幫助客戶在SoC開發(fā)過程中解決調(diào)試問

2022-06-16 10:16:48 1693

1693

調(diào)試和測試方法主要還是結(jié)合開發(fā)人員,比如軟件工程師在代碼中通過CLI增加【調(diào)試接口】,讓調(diào)試人員可以通過CLI發(fā)送指令進行調(diào)試。

2023-10-18 11:04:48 1537

1537

點擊上方 藍(lán)字 關(guān)注我們 大容量、高速率和低功耗已成為FPGA的發(fā)展重點。 嵌入式邏輯分析工具無法滿足通用性要求,外部測試工具可以把FPGA內(nèi)部信號與實際電路聯(lián)合起來觀察系統(tǒng)真實運行情況。 隨著

2023-10-23 15:20:01 1956

1956

前言本指導(dǎo)文檔適用的開發(fā)環(huán)境為Windows764bit和Windows1064bit。本文檔主要提供開發(fā)板FPGA端案例測試方法,所有工程均位于產(chǎn)品資料Demo1目錄下。進行本文檔操作前,請先

2022-08-25 15:08:54 1

1 USB調(diào)試模式是什么意思?USB調(diào)試模式有什么用? USB調(diào)試模式是一種在Android設(shè)備上進行開發(fā)、測試和調(diào)試的模式。當(dāng)設(shè)備處于USB調(diào)試模式下,開發(fā)人員可以通過USB連接設(shè)備和計算機,在計算機上進行

2023-12-11 11:06:10 16307

16307 1 推動FPGA調(diào)試技術(shù)改變的原因 進行硬件設(shè)計的功能調(diào)試時,FPGA的再編程能力是關(guān)鍵的優(yōu)點。CPLD和FPGA早期使用時,如果發(fā)現(xiàn)設(shè)計不能正常工作,工程師就使用“調(diào)試鉤”的方法。先將要觀察

2023-12-20 13:35:01 1207

1207

在調(diào)試FPGA電路時要遵循必須的原則和技巧,才能降低調(diào)試時間,防止誤操作損壞電路。通常情況下,參考以下步驟執(zhí)行 FPGA硬件系統(tǒng)的調(diào)試。 1、在焊接硬件電路前,首先要測試電路板的各個電源之間,各電源

2023-12-22 16:40:01 1607

1607

FPGA軟件包含進行設(shè)計而產(chǎn)生的程序、文檔和數(shù)據(jù),同時包含與之相關(guān)的軟件特性和硬件特性。FPGA軟件測試需要考慮軟件代碼正確性、軟硬件接口協(xié)調(diào)性、時序性等方面的全面覆蓋。

2024-03-06 11:39:36 1509

1509 FPGA開發(fā)板是一種基于FPGA(現(xiàn)場可編程門陣列)技術(shù)的開發(fā)平臺,它允許工程師通過編程來定義和配置FPGA芯片上的邏輯電路,以實現(xiàn)各種數(shù)字電路和邏輯功能。FPGA開發(fā)板通常包括FPGA芯片、時鐘模塊、電源模塊、輸入輸出接口等組件,并提供相應(yīng)的編程軟件和開發(fā)工具,方便工程師進行電路設(shè)計和調(diào)試。

2024-03-14 18:20:29 4535

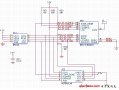

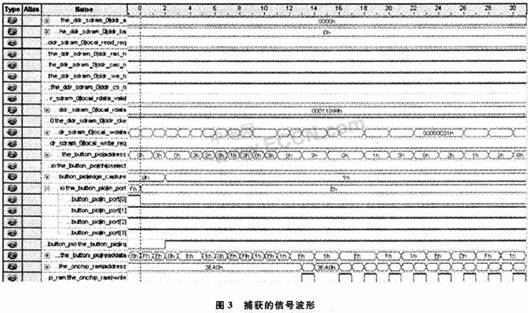

4535 FPGA(現(xiàn)場可編程門陣列)和DSP(數(shù)字信號處理器)之間通過SRIO接口進行調(diào)試通常需要以下步驟。

2024-04-19 11:48:46 2569

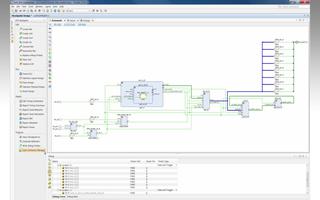

2569 聯(lián)合開發(fā)或者跑多策略工程的時候,一般都使用多核的服務(wù)器進行FPGA設(shè)計。這個時候如果板卡在本地電腦上應(yīng)該怎么進行調(diào)試呢?

2024-10-24 18:05:00 1317

1317

Verilog測試平臺設(shè)計方法是Verilog FPGA開發(fā)中的重要環(huán)節(jié),它用于驗證Verilog設(shè)計的正確性和性能。以下是一個詳細(xì)的Verilog測試平臺設(shè)計方法及Verilog FPGA開發(fā)

2024-12-17 09:50:06 1630

1630

電子發(fā)燒友App

電子發(fā)燒友App

評論