本文將對源同步定時如何優化高速接口時序裕量進行討論。時序預算是對系統正常工作所需時序參數或時序要求的計算。

2012-03-20 10:46:32 6290

6290

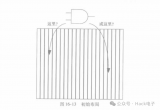

表。 這4類路徑中,我們最為關心是②的同步時序路徑,也就是FPGA內部的時序邏輯。 時序模型 典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數據路徑和目的時鐘路徑,也可以表示為觸發器+組合邏輯+觸發器的模型。 該

2020-11-17 16:41:52 3687

3687

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2392

2392 引言:本文分享一篇技術PPT,該PPT主要介紹如何將算法映射到FPGA或ASIC硬件架構。

2023-01-30 17:37:11 2860

2860 FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-06 17:53:07 1938

1938

在FPGA設計中,時序約束的設置對于電路性能和可靠性都至關重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的基礎知識。

2023-06-06 18:27:13 12757

12757

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 4234

4234 今天跟大家分享的內容很重要,也是調試FPGA經驗的總結。隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設計越來越多。在調試這些FPGA樣機時,需要從寫代碼時就要小心謹慎,否則寫出來的代碼

2023-08-01 09:18:34 3075

3075

前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 3030

3030

這篇文章是探討對接收端進行時序優化(即ready打拍,或稱backward打拍)的方式。

2023-12-04 10:20:55 1207

1207

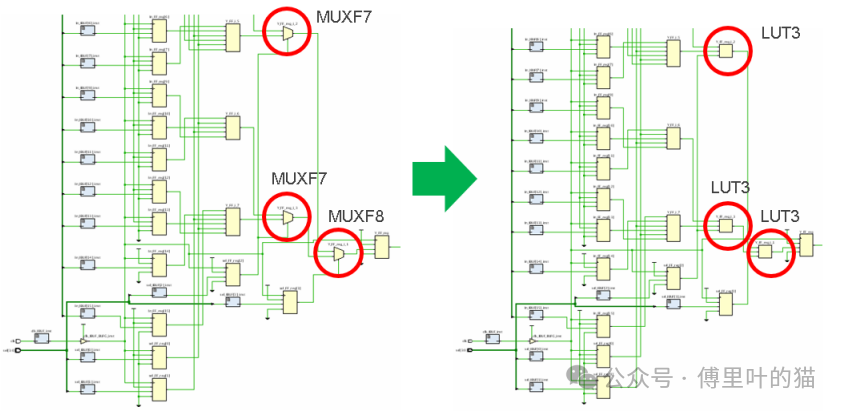

在數字IC/FPGA設計的過程中,對PPA的優化是無處不在的,也是芯片設計工程師的使命所在。此節主要將介紹performance性能的優化,如何對時序路徑進行優化,提高工作時鐘頻率。

2025-12-09 10:33:20 2961

2961

FPGA系統設計實質上是一個同步時序系統的設計,理解時序概念,掌握代碼優化與綜合技術,正確完整地進行時序約束和分析是實現高性能系統的重要保證。很多同學在設計中都會碰到時序方面的問題,如何解決時序難題

2018-06-07 15:52:07

的綜合、映射、布局和布線,以減小邏輯和布線延時,從而提高 工作頻率。

2、獲得正確的時序分析報告

幾乎所有的 FPGA 設計平臺都包含靜態時序分析工具,利用這類工具可以獲得映射或 布局布線后的時序

2024-06-17 17:07:28

時間,降低了制造成本。直觀的邏輯合成環境包括先進的優化技術、屢獲殊榮的時序分析和先進的推論技術,適用于與供應商無關的設計中,可加快產品上市時間、消除設計缺陷以及提供極佳的結果質量 (QoR)。 FPGA

2018-09-20 11:11:16

如今,FPGA 功能強大且管腳數目極大,可為工程師提供大量機會來提升特性和功能,同時還能降低產品成本。隨著復雜度增加,將這些器件集成到印刷電路板也成為了一項嚴峻的挑戰。數百個邏輯信號需映射到器件

2019-10-09 07:15:30

,所以測不出來2 時序頻率太高了,FPGA已經Hold不住了,應該降低頻率請有經驗的同志們幫我看看可能是什么原因。在此獻出我的積分了。。。

2016-09-14 17:36:45

起點(即時鐘觸發器輸入端口)

(2)路徑終點(即輸出端口的寄存器或查找表單元)

(3)邏輯電路和邏輯器件

有了這些元素,就可以構建完整的時序路徑。在實踐中,我們可以使用FPGA工具來分析、優化

2023-11-15 17:41:10

FPGA中的I_O時序優化設計在數字系統的同步接口設計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優化設計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

同步復位,可以降低資源的使用和功耗,有助于時序收斂。由于FPGA的初始狀態是確定的(可以在定義說明中指定),為了更快地時序收斂,官方文檔認為,能不用復位是最好的,尤其數據路徑和移位寄存器的設計中。不過

2020-12-23 17:42:10

VGA驅動接口時序設計之7優化本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt最后,再次編譯系統,查看時序

2015-08-10 15:03:08

FPGA的時序優化高級研修班通知通過設立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優化的方法。1.FPGA靜態時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優化方法

2013-03-27 15:20:27

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-09-21 07:45:57

FPGA 設計優化主要分為編碼風格、設計規劃和時序收斂三大部分,這 些因素直接決定了 FPGA 設計的成敗。 編碼風格直接影響 FPGA 設計的實現并最終影響設計的性能。盡管綜合 工具集成

2022-09-29 06:12:02

EDA技術具有什么特征?FPGA是什么原理?FPGA設計應用及優化策略基于VHDL的FPGA系統行為級設計

2021-04-15 06:33:58

“hotstart_1”策略。然而,它仍然缺少-90ps 的時序。

我們對“HotStart_1”的結果應用了名為“Extra Opt Exploration”的第二個秘訣。這側重于優化關鍵路徑。這是

2024-08-16 19:56:07

速度優化是指在充分掌握軟硬件特性的基礎上, 通過應用程序結構調整等手段來降低完成指定任務所需執行的指令數。在同一個處理器上, 經過速度優化的程序比未經優化的程序在完成指定任務時所需的時間更短,即前者比

2011-07-07 11:06:42

人工智能大熱之前,Cloud或Data Center已經開始使用FPGA做各種加速了。而隨著Deep Learning的爆發,這種需求越來越強勁。本文主要討論Cloud巨頭Amazon和Microsoft的FPGA策略。

2019-08-13 08:37:24

近年來,世界上許多大軟件公司紛紛推出各種Linux服務器系統及Linux下的應用軟件。目前,Linux 已可以與各種傳統的商業操作系統分庭抗禮,在服務器市場,占據了相當大的份額。本文分別從磁盤調優,文件系統,內存管理以及編譯優化等方面來論述 Linux系統的優化調優策略。

2019-07-16 06:23:35

上次我發過一個帖子已經得到解決,目前的情況是FPGA的時序有問題。板子是VGA轉HDMI的,經過CAT9883C芯片下游到Sil9134,出來的高清圖像一直有水波紋。查資料說是FPGA,有的說要改代碼。有的說改板子上東西。有沒有大佬看一下我的板子幫個忙。。。

2017-10-31 16:54:41

InTime 利用大數據分析和人工智能,建立時序數據庫,無需修改源代碼即可優化設計,為工程師推薦最佳工具參數組合。了解更多>>

2017-04-18 14:53:40

轉自:VIVADO時序分析練習時序分析在FPGA設計中是分析工程很重要的手段,時序分析的原理和相關的公式小編在這里不再介紹,這篇文章是小編在練習VIVADO軟件時序分析的筆記,小編這里

2018-08-22 11:45:54

整體對這軟件評價是,優化功耗的時候不能有很大提升,但優化時序還是不錯的,這款軟件不僅可以優化時序,還可以對工程進行工作頻率的適當提升。很感興趣他們的private cloud編譯方式。收到

2017-06-30 15:28:28

解決FPGA時序優化問題的軟件。InTime 內嵌學習引擎,可以智能分析FPGA設計,為綜合和布局布線提供更優的策略組合。同時,根據對器件、設計和工具特點的了解,以及獨有的算法,InTime 可以生成最能滿足

2017-07-05 11:00:48

當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2019-08-11 08:30:00

提出有效的PPA優化方案。其實這一條經驗是并不特指高頻設計,是做好設計的基本功,缺陷率高同學往往問題就出現在這里。2.建立把代碼通過人腦轉化成電路的能力。verilog描述的就是電路,時序優化也是在電路

2022-06-23 15:43:18

特定模塊劃分到不同的時鐘域里;但異步時鐘域不宜太多。綜合時使用retiming,duplication;physical synthesis優化,現在的綜合器這方面已經足夠聰明了。預算允許可使用速度更快的芯片;這個也許是實現 “不修改RTL又時序收斂” 的最可能的方式。

2018-06-07 17:55:37

當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2021-05-18 15:55:00

本帖最后由 mingzhezhang 于 2012-5-23 20:05 編輯

大型設計中FPGA的多時鐘設計策略 利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重

2012-05-23 19:59:34

。掌握分析和確定關鍵路徑時序的方法,并通過分析找出關鍵路徑的時序問題,再對關鍵路徑進行優化,通過RTL層面的不斷優化,不斷修煉自己的設計能力,讓設計出來的電路更為靠譜有效!本資料屬大西瓜FPGA開發團隊,在此開源,與大家一起學習FPGA!

2017-02-26 09:42:48

您好,如果我想為我的設計獲得最佳時序收斂,我應該使用什么實施策略?例如,如果我想改善設置和保持的松弛度,我應該選擇哪種最佳策略?以上來自于谷歌翻譯以下為原文Hello,If i want

2018-11-05 11:40:14

虛擬同步發電機雙機并聯系統的參數自調節優化控制策略有哪些?

2021-11-04 07:20:27

觸摸屏知識及軟件優化策略

2012-08-20 10:04:54

新手,需要對一個工程時序優化,現在只能到110MHZ, 需要到150MHZ以上,跪求時序優化資料或例程。。

2015-12-05 11:22:54

變則通,通則久。事物都有其運行的規律,把握好規律,就能更好的實現人的目的。在數字后端設計中,時序優化一直是關鍵問題,尤其追求高頻高性能的設計中,時許問題常常貫穿始終。大大小小二十幾個項目模塊后端工作

2020-12-10 07:37:31

在基于相似度計算的本體映射中,相似度計算量大的主要原因是待映射概念和待計算屬性過多。該文采用過濾策略,利用候選映射策略和信息增益策略減少待映射概念和待計算屬性

2009-04-14 09:15:23 29

29 如何有效的管理FPGA設計中的時序問題

當FPGA設計面臨到高級接口的設計問題時,EMA的TimingDesigner可以簡化這些設計問題,并提供對幾乎所有接口的預先精確控制。從簡單

2009-04-15 14:19:31 947

947

介紹了采用STA (靜態時序分析)對FPGA (現場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1476

1476 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 很好的FPGA資料,基礎的資料,快來下載吧

2016-09-01 16:40:07 34

34 基于時序路徑的FPGA時序分析技術研究_周珊

2017-01-03 17:41:58 2

2 低成本BIST映射電路的設計與優化_張玲

2017-01-07 21:39:44 2

2 如何有效地管理FPGA設計中的時序問題

2017-01-14 12:49:02 14

14 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2017-02-09 01:59:11 510

510 參加 ?FPGA? 功率優化班,將幫助您創建更高電源效率的 ?FPGA? 設計。通過本課程的學習,將有助于您的設計滿足更小型化的 ?FPGA? 器件,降低 ?FPGA? 功耗,或在更低的溫度下運行

2017-02-09 06:24:11 320

320 fpga時序收斂

2017-03-01 13:13:34 23

23 一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2967

2967

和底層工具Planahead實現高速串并轉換中數據建立時間和保持時間的要求,實現并行數據的正確輸出。最后通過功能測試和時序測試,驗證了設計的正確性。此方法可適用于高端和低端FPGA,提高了系統設計的靈活性,降低了系統的成本。

2017-11-17 12:27:01 7352

7352

現有的工具和技術可幫助您有效地實現時序性能目標。當您的FPGA 設計無法滿足時序性能目標時,其原因可能并不明顯。解決方案不僅取決于FPGA 實現工具為滿足時序要求而優化設計的能力,還取決于設計人員指定前方目標,診斷并隔離下游時序問題的能力。

2017-11-18 04:32:34 3842

3842 作為賽靈思用戶論壇的定期訪客(見 ),我注意到新用戶往往對時序收斂以及如何使用時序約束來達到時序收斂感到困惑。為幫助 FPGA設計新手實現時序收斂,讓我們來深入了解時序約束以及如何利用時序約束實現

2017-11-24 19:37:55 5955

5955

在給FPGA做邏輯綜合和布局布線時,需要在工具中設定時序的約束。通常,在FPGA設計工具中都FPGA中包含有4種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入到輸出的純組合邏輯

2017-11-24 20:12:54 2067

2067 合理的電力網架恢復策略對大停電后電力系統的快速恢復具有重要意義。采用時序恢復策略進行電力網架恢復,分步進行機組啟動順序優化和路徑恢復順序優化。第一步以網架恢復時間內系統發電能力最大為目標優化機組啟動

2018-01-14 11:10:57 17

17 傳統的基于模擬退火的現場可編程門陣列( FPGA)時序驅動布局算法在時延代價的計算上存在一定誤差,已有的時序優化算法能夠改善布局質量,但增加了時耗。針對上述問題,提出一種基于事務內存( TM)的并行

2018-02-26 10:09:04 0

0 FPGA時序收斂讓你的產品達到最佳性能!

2018-04-10 11:38:48 19

19 FPGA設計一個很重要的設計是時序設計,而時序設計的實質就是滿足每一個觸發器的建立(Setup)/保持(Hold)時間的要求。

2018-06-05 01:43:00 4865

4865

如今,FPGA 功能強大且管腳數目極大,可為工程師提供大量機會來提升特性和功能,同時還能降低產品成本。隨著復雜度增加,將這些器件集成到印刷電路板也成為了一項嚴峻的挑戰。數百個邏輯信號需映射到器件

2018-10-26 11:54:01 544

544 FPGA設計中,層次結構設計和復位策略影響著FPGA的時序。在高速設計時,合理的層次結構設計與正確的復位策略可以優化時序,提高運行頻率。

2019-02-15 15:15:53 1270

1270 關鍵詞:FPGA , 國產 , 國產FPGA , 試用 作者在:特權同學 關于時序工具的一些FAE解答: 問:你們的工具是否只提供所有輸入輸出管腳完全一致的時序約束?如tsu,th,tco,tpd

2019-02-25 18:24:01 740

740

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-05 07:08:00 3476

3476

萬幸的是,當今FPGA工具(比如Xilinx的 Vivado)都有很多開關和設置選項來幫助時序收斂。InTime的方法,就是通過調整FPGA工具的編譯過程來解決用戶的時序問題和其他性能問題。

2019-07-26 15:56:23 4237

4237

時序分析結果,并根據設計者的修復使設計完全滿足時序約束的要求。本章包括以下幾個部分: 1.1 靜態時序分析簡介 1.2 FPGA 設計流程 1.3 TimeQuest 的使用 1.4 常用時序約束 1.5 時序分析的基本概念

2020-11-11 08:00:00 67

67 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束利序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 本文檔的主要內容詳細介紹的是FPGA的時序分析的優化策略詳細說明。

2021-01-14 16:03:59 17

17 本文檔的主要內容詳細介紹的是FPGA的時序分析的優化策略詳細說明。

2021-01-14 16:03:59 19

19 ,分別設計 Simple、 Multiple(k)、M(u)和 Relation算法,以此構建任務映射虛擬機選擇的數學模型基于 Cloudsim模擬器的實驗結果表明,通過該策略優化虛擬機選擇與放置過程,可減少云數據中心的能量消耗和虛擬機遷移次數,節省云服務提

2021-05-25 14:29:18 17

17 求出目標函數總帶寬消耗(TBC)的最優解,尋找可組合的VNF,并利用NF決策樹檢查所有組合策略,通過迭代和優化降低TBC。仿真結果表明,A-VNFC算法可在不同場景下有效降低帶寬消耗,其TBC數值接近ILP模型獲得的最小帶寬消耗值。

2021-05-28 14:17:04 5

5 A 時序約束的概念和基本策略 時序約束主要包括周期約束(FFS到FFS,即觸發器到觸發器)和偏移約束(IPAD到FFS、FFS到OPAD)以及靜態路徑約束(IPAD到OPAD)等3種。通過附加

2021-09-30 15:17:46 5927

5927 A 時序約束的概念和基本策略 時序約束主要包括周期約束(FFS到FFS,即觸發器到觸發器)和偏移約束(IPAD到FFS、FFS到OPAD)以及靜態路徑約束(IPAD到OPAD)等3種。通過附加

2021-10-11 10:23:09 6573

6573

索引使用策略及優化 MySQL的優化主要分為結構優化(Scheme optimization)和查詢優化(Query optimization)。本章討論的高性能索引策略主要屬于結構優化范疇。本章

2021-11-02 15:13:42 2297

2297

1、如何降低功耗?

(1) 優化方向:

組合邏輯+時序邏輯+存儲

(2) 組合邏輯:

??(a)通過算法優化的方式減少門電路

??(b)模塊復用、資源共享

(3) 時序邏輯:

??(a)盡量減少無用

2022-02-11 15:30:36 2

2 上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 2166

2166

時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 3922

3922 本文章探討一下FPGA的時序input delay約束,本文章內容,來源于配置的明德揚時序約束專題課視頻。

2022-05-11 10:07:56 4989

4989

明德揚有完整的時序約束課程與理論,接下來我們會一章一章以圖文結合的形式與大家分享時序約束的知識。要掌握FPGA時序約束,了解D觸發器以及FPGA運行原理是必備的前提。今天第一章,我們就從D觸發器開始講起。

2022-07-11 11:33:10 6143

6143

本文章探討一下FPGA的時序input delay約束,本文章內容,來源于明德揚時序約束專題課視頻。

2022-07-25 15:37:07 3757

3757

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-04-27 10:08:22 2404

2404 STA(Static Timing Analysis,即靜態時序分析)在實際FPGA設計過程中的重要性是不言而喻的

2023-06-26 09:01:53 1276

1276

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-26 14:42:10 1252

1252

FPGA時序不收斂,會出現很多隨機性問題,上板測試大概率各種跑飛,而且不好調試定位原因,所以在上板測試前,先優化時序,再上板。

2023-06-26 15:41:31 3800

3800

FPGA高級時序綜合教程

2023-08-07 16:07:55 9

9 FPGA的BRAM和LUT等資源都是有限的,在FPGA開發過程中,可能經常遇到BRAM或者LUT資源不夠用的情況。

2023-08-30 16:12:04 5313

5313

對設計者很通常的情況是花費幾天或幾周的時間圍繞一個設計來滿足時序,甚至多半利用上面描述的自動種子變化,只面對可以起伏通過已有布局的小改變和時序特性完全改變。

2024-04-01 12:35:10 1571

1571

建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2024-08-06 11:40:18 2366

2366

電子發燒友網站提供《FPGA電源時序控制.pdf》資料免費下載

2024-08-26 09:25:41 1

1 優化FPGA(現場可編程門陣列)設計的性能是一個復雜而多維的任務,涉及多個方面和步驟。以下是一些關鍵的優化策略: 一、明確性能指標 確定需求 :首先,需要明確FPGA設計的性能指標,包括時鐘頻率

2024-10-25 09:23:38 1454

1454

電子發燒友App

電子發燒友App

評論