三態電路有什么特點,什么是上拉電阻、下拉電阻以及高阻態?

2019-05-21 07:28:00 7701

7701

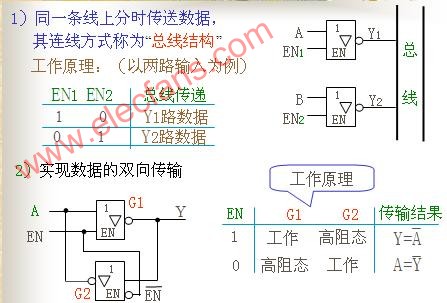

大學計算機教學中的計算機硬件實驗。在計算機硬件實驗中,三態電路有著廣泛的應用,例如構建一個具有分時共享功能的總線電路就需要用到多個三態電路。

2020-08-07 17:14:32 2614

2614

TTL三態門輸出電路是一種重要的接口元件,它能夠提供三種輸出狀態:高電平、低電平和高阻態。這種電路在實現數字系統之間的連接和數據傳輸時起著至關重要的作用。

2024-02-18 15:41:19 6464

6464

上才都有顯示,這時測出的電壓是5V上面的是用proteus仿真的情況,在實際中,我看jtag模塊上都有一個74HC244這種芯片,我上網搜了一下,說244是三態8同相緩沖/驅動器,說是增加什么驅動

2014-07-20 11:49:56

一、三態單片機IO的三態是指:高電平(1)、低電平(0)、高組態(Z)。二、高阻態高阻i是一種電路狀態.既不是高電平,也不是低電平,以高阻態對下級電路輸出,下級電路什么影響也沒有.高阻態的IO電平

2021-11-25 06:42:28

如圖是一個三態反相緩沖器,我想把它和一個自偏電阻連起來做一個放大器。

2019-01-28 16:40:28

如果我在其中一個存儲器上使用32位三態輸出,則合成器會添加一個切片。有人能告訴我內部三態緩沖器在FPGA架構中的位置(我得到了kintex 7)嗎?我在CLB指南中找了它,但沒找到

2019-03-04 13:17:18

。看起來微處理器正在寫入FPGA而不是從FPGA讀取。但情況應該不是這樣,而應該恰恰相反!在推斷三態緩沖區時,我是否設置了錯誤?當我在planAhead中打開設計時,我可以看到“io_data”被認為是

2019-03-08 14:01:02

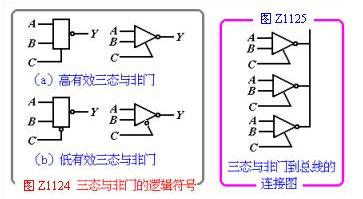

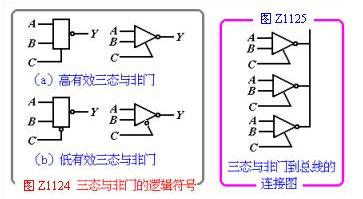

三態輸出門的電路圖和圖形符號

2019-10-25 07:17:31

三態門的工作原理是什么?

2021-05-20 06:55:47

三態門輸入信號和輸出信號之間接電阻是什么用法?

2017-04-09 19:36:20

- 2.5VVCCO_35 - 2.5V連接到I / O bank的一些外部電路在2.5V FPGA電源軌之前上電(這超出了我的控制范圍)。這會以奇怪的方式導致2.5V FPGA電源軌斜坡,請參考附圖。基本上2.5VFPGA

2020-07-30 09:51:29

1、AD5420的SDO是否是三態輸出腳

2、MCU的SPI接口配置CPOL=0、CPAH=0,是否正確

2023-12-20 08:08:51

AD9280三態引腳是否只是控制數據輸出端的,和轉換過程沒有關系?

現在問題是FPGA引腳不夠用了,能否將兩片AD9280數據D0-D7接在一起,時鐘是共用的,兩片AD同步輸出,在數據開始輸出后用三態引腳控制取數?

2023-12-14 06:49:33

not directly control the tri-state conditionof the SDOUT or SDIO output,尊敬的專家,如果CS沒被選中,SDOUT是否是三態狀態?在CS拉高后,SDOUT是否會立馬變為三態?

2019-05-23 08:07:10

SN74AVC2T244的使能引腳OE到底是OE=低電平時輸出三態,還是OE=高電平時輸出三態?

TI的手冊也能漏洞百出?

2024-12-04 07:48:02

大家好: 請教一下大家,STM8單片機的IO口是否可實現三態:輸出高電平、低電平、高阻態。

2024-05-07 07:07:28

inout Key_inout;wire Key_input;//輸入reg Key_output;//輸出reg Key_Ctr;//三態控制assign Key_inout=Key_Ctr

2014-09-23 15:34:43

如果:紅色-0,綠色-1,藍色-2

輸入:數組

輸出:布爾數組或簇

例如:輸入數組為〔0 1 2 1 0〕

希望輸出顯示為紅色,綠色,藍色,綠色,紅色的一組三態燈。

網上給的子vi是利用bool引用句柄實現一個燈的三態顯示,如果數組元素少的話用枚舉可以實現,但是如果數組元素很多,有什么簡便的方法嗎?

2015-12-09 14:32:54

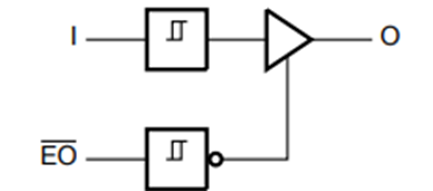

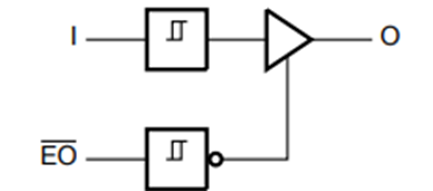

等,要求信號為三態類型,也就是我們所說的輸入輸出(inout)類型。那么,本節夢翼師兄將和大家一起來探討三態門的用法。項目需求設計一個三態門電路,可以實現數據的輸出和總線“掛起”。系統架構 模塊功能

2019-12-12 16:11:51

AD9280三態引腳是否只是控制數據輸出端的,和轉換過程沒有關系?現在問題是FPGA引腳不夠用了,能否將兩片AD9280數據D0-D7接在一起,時鐘是共用的,兩片AD同步輸出,在數據開始輸出后用三態引腳控制取數?

2019-01-09 09:30:29

在輸入時讀入外部電平用.1. 三態門的特點三態輸出門又稱三態電路。它與一般門電路不同,它的輸出端除了出現高電平、低電平外,還可以出現第三個狀態,即高阻態,亦稱禁止態,但并不是3個邏輯值電路。 2.

2008-05-26 13:01:37

晶振的高阻態在電路起什么作用,為什么有的晶振需要三態腳有的不需要,晶振的三態是靠什么去控制的?

2025-05-15 11:08:06

三態LED 子vi

2017-01-13 10:39:39

如何才能制作一個三態指示燈?需要什么材料等等

2014-10-28 19:51:17

反相器的速度與哪些因素有關?什么是轉換時間和傳播延遲呢?怎樣去設計一種CMOS三態緩沖器的電路呢?

2021-10-20 06:24:39

我有一個使用MCLR作為輸入的項目。用PICTIT2 MCLR放在編程后的三態,但是用皮卡4,似乎PIN保持高。這有什么設置嗎? 以上來自于百度翻譯 以下為原文 I have a project

2018-10-26 16:11:59

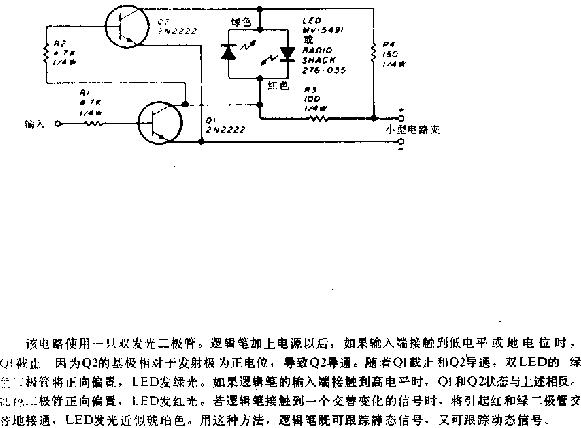

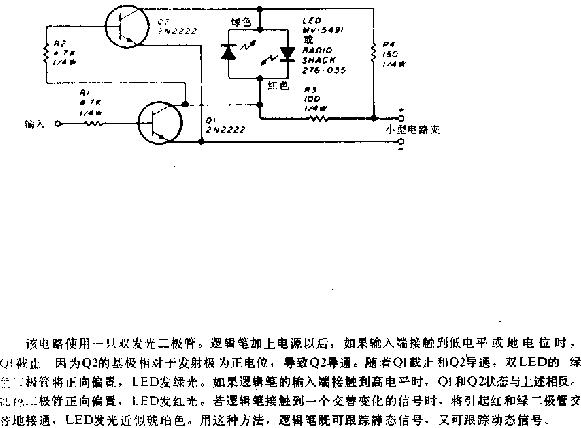

描述PCB_三態極性指示器使用 1K 電阻 (x2) 和任何硅二極管。頂部的綠色 LED 底部的紅色。使用厚二極管腿作為探針和帶有鱷魚夾的接地線。

2022-08-30 07:31:27

新人在工作中經常碰到三態門與高阻態;請教技術大佬,這兩個到底是什么東西 ?

2021-04-07 06:59:01

1、AD5420的SDO是否是三態輸出腳2、MCU的SPI接口配置CPOL=0、CPAH=0,是否正確

2018-12-20 09:26:31

ISIM不能處理1Mb信號)。我也測試了它,用邏輯分析儀我可以看到信號,地址和寫入數據是正確的,時間也很好,但讀數不對。我的猜測是它與雙向數據總線有關,我知道內部三態在spartan-3上不再可用,但我

2019-06-26 10:24:04

請問這個三態門為什么不能實現非功能?它的邏輯表達式不應該是A非嗎?

2023-04-26 11:49:06

集電極開路 漏極開路 推挽 上拉電阻 弱上拉 三態門 準雙向口

2016-06-02 16:22:21

高阻態和三態門高阻態 高阻態的實質:電路分析時高阻態可做開路理解。你可以把它看作輸出(輸入)電阻非常大。他的極限可以認為懸空。也就是說理論上高阻態不是懸空,它是對地或對電源電阻極大的狀態。而實際

2019-01-08 11:03:07

數字電路常見術語:高阻態,三態門高阻態常用的表示方法

2021-03-01 11:09:49

如何用正確的使用VHDL描述三態電路Tri-State Bus Implementation

library ieee;use ieee.std_logic_1164.all;library

2008-09-09 16:18:54 14

14 如何處理內部三態電路—PLD設計技巧 Tri-State vsMUX

Tri-State Buffer

There are two application area

2008-09-11 09:27:21 29

29 集電極開路門和三態輸出門的應用

一、 實訓目的1.熟悉集電極開路門(OC門)和三態輸出門(TSL門)的邏輯功能;2.熟悉用OC門構成線與功能;3.熟悉用TSL門

2009-04-07 23:23:53 59

59 具有三態輸出的集成電路其輸出具有可控的高阻抗狀態,廣泛應用于總線結構中。凡是輸出連接到總線的邏輯部件,例如:存儲器、總線控制器、總線接口等等。無論是TTL電路,還

2010-05-05 10:15:13 16

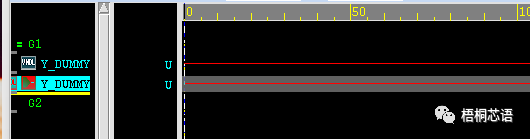

16 本文就三態電路在FPGA中的應用作了詳細的說明。文章首先描述了一個調用lpm中三態電路模塊的VHDL程序,這個程序會出現編譯不能通過的問題。然后從這個問題出發,通過嘗試三態電

2010-08-06 16:56:22 27

27 什么是三態門?

三態門,是指邏輯門的輸出除有高、低電平兩種狀態外,還有第三種狀態——高阻狀態的門電路 高阻態相當于隔斷狀態。

2008-05-26 12:48:24 49852

49852

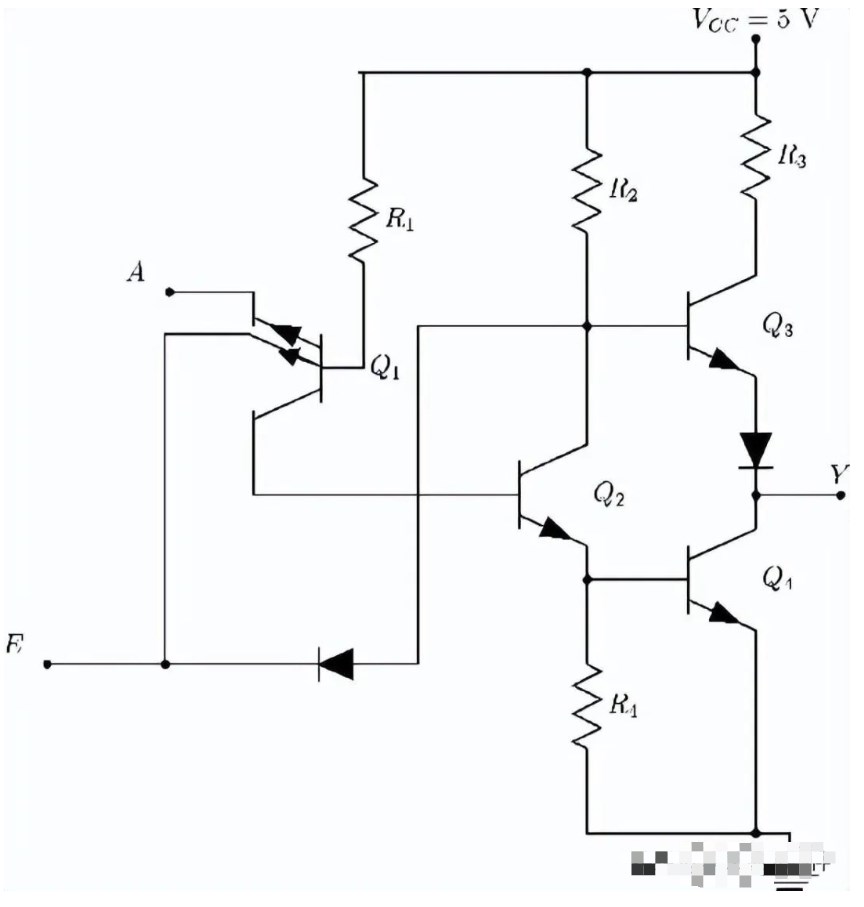

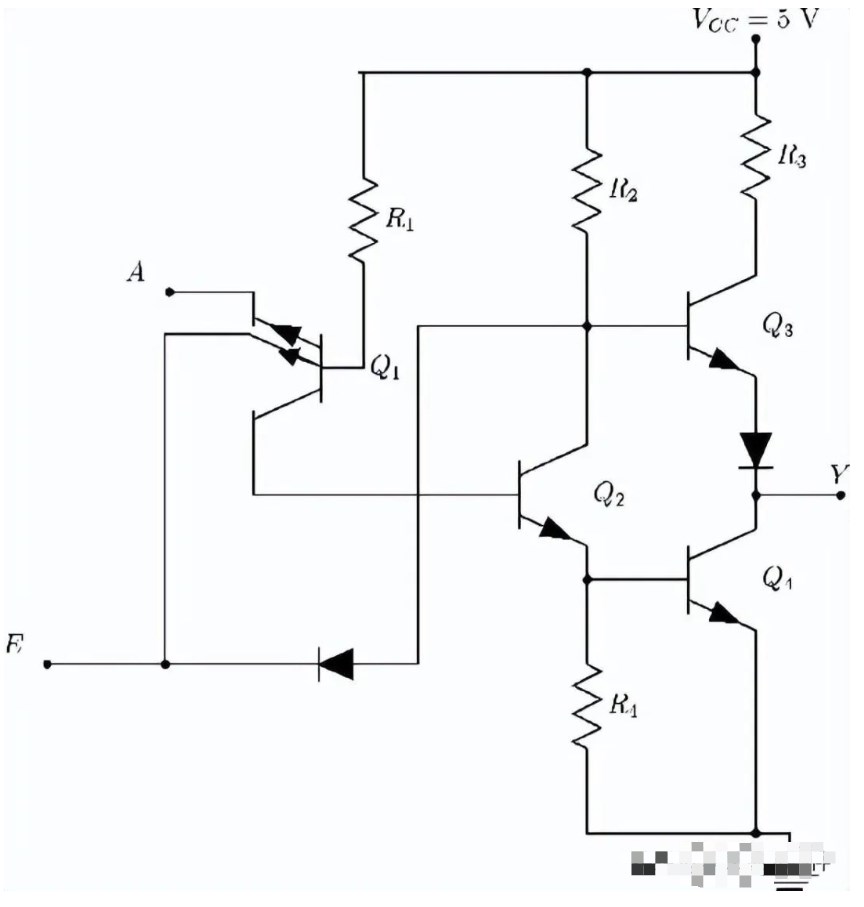

TTL或非門、集電極開路門和三態門電路

1.TTL或非門

下圖為TTL或非門的邏輯電路及其代表符號。

2009-04-07 00:11:59 17424

17424

三態邏輯筆電路圖

2009-04-07 09:16:34 2408

2408

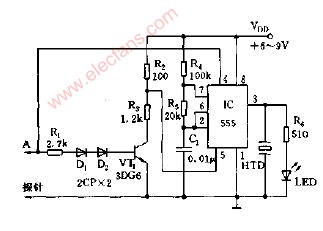

三態聲光邏輯筆電路圖

2009-05-19 13:42:17 885

885

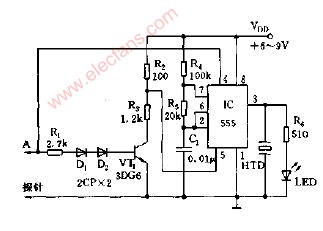

五用途三態聲頻邏輯比電路圖

2009-05-19 13:45:31 678

678

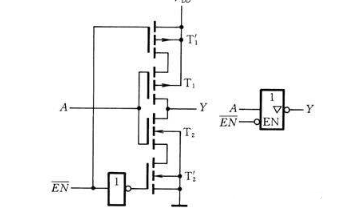

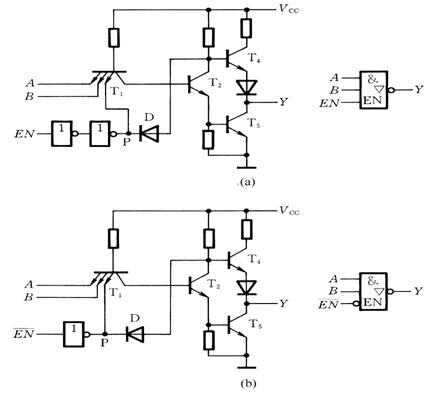

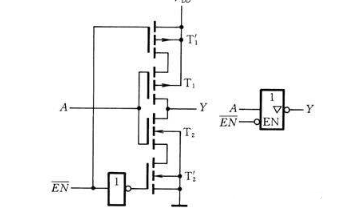

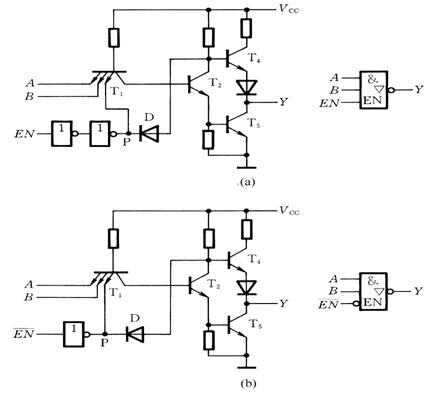

三態輸出門的電路圖和圖形符號

2009-07-15 19:03:57 3527

3527

CMOS三態門電路結構

(a)用或非門控制 (b)用與非門控制

2009-07-15 19:09:10 13373

13373

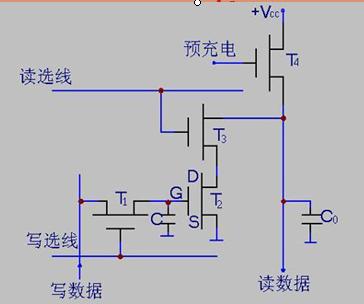

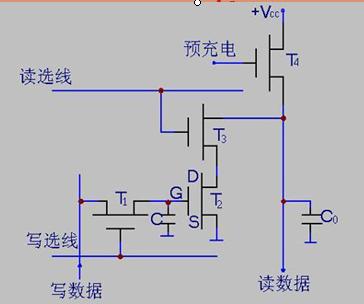

三態MOS動態存儲單元電路

2009-10-10 18:45:49 1445

1445

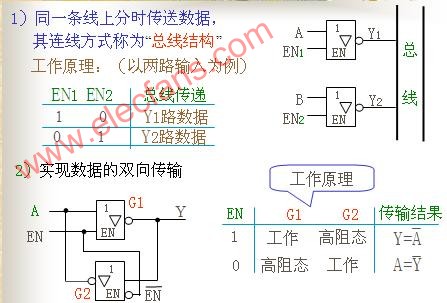

三態門的組成及工作原理

2010-02-28 19:13:26 26690

26690

圖中所示用555時基電路集成三態聲光邏輯筆電路.555時基集成電路接成多諧振蕩器.

控

2010-10-03 16:56:03 1711

1711 介紹了用Multisim仿真軟件分析三態門工作過程的方法,目的是探索三態門工作波形的仿真實驗技術,即用Multisim仿真軟件中的字組產生器產生三態門的控制信號及輸入信號,用Multisim中示

2011-05-06 15:59:38 0

0 提出了一種基于FPGA 實現嵌入式三態(10MB/100MB/1 000MB)以太網的設計方案,分別從硬件和軟件方面介紹了使用FPGA 進行嵌入式系統設計的方法,編寫了一個控制系統進行10MB/100MB/1 000MB 自切換

2011-05-13 18:52:40 64

64 基于探索仿真三態門總線傳輸電路的目的,采用Multisim10仿真軟件對總線連接的三態門分時輪流工作時的波形進行了仿真實驗測試,給出了仿真實驗方案,即用Multisim仿真軟件構成環形計

2013-06-08 17:58:44 48

48 三態緩沖器三態緩沖器三態緩沖器三態緩沖器三態緩沖器三態緩沖器三態緩沖器

2015-11-16 11:59:30 0

0 三態門在數字電路上可以說是應用的非常廣泛,特別是一些總線上的應用,因而,隨著數字電路的發展,就避免不了用硬件描述語言在FPGA上來設計實現三態門。

2017-02-08 11:37:06 9478

9478 PSoC 4 三態緩沖器 Bufoe

2017-10-10 08:39:49 13

13 低電平,隨它后面接的東西定。三態門,是指邏輯門的輸出除有高、低電平兩種狀態外,還有第三種狀態——高阻狀態的門電路。高阻態相當于隔斷狀態(電阻很大,相當于開路)。 三態門都有一個EN控制使能端,來控制門電路的通斷。 可以具備這三種狀態的器件就叫做三態(門,總線,......)。

2017-12-25 11:27:11 27795

27795

三態數據緩沖器是數據輸入/輸出的通道,數據傳輸的方向取決于控制邏輯對三態門的控制。本文介紹三態緩沖器的邏輯符號。

2018-01-11 10:42:36 16307

16307

三態指其輸出既可以是一般二值邏輯電路,即正常的高電平(邏輯1)或低電平(邏輯0),又可以保持特有的高阻抗狀態。本文開始介紹了三態門的定義,其次介紹了三態門的邏輯符號,最后介紹了三款三態門邏輯電路。

2018-03-01 14:03:10 81602

81602

本文開始介紹了三態門的定義與三態門的應用,其次對三態門的三態及特點進行了介紹,最后闡述了三態輸出門電路與三態門電路的圖形符號與真值表。

2018-03-01 14:47:41 131514

131514

三態門,是指邏輯門的輸出除有高、低電平兩種狀態外,還有第三種狀態——高阻狀態的門電路 高阻態相當于隔斷狀態。

2018-07-26 10:53:43 45501

45501

三態緩沖器(Three-state buffer),又稱為三態門、三態驅動器,其三態輸出受到使能輸出端的控制,當使能輸出有效時,器件實現正常邏輯狀態輸出(邏輯0、邏輯1),當使能輸入無效時,輸出處于高阻狀態,即等效于與所連的電路斷開。

2018-10-24 16:09:36 35791

35791 三態指其輸出既可以是一般二值邏輯電路,即正常的高電平(邏輯1)或低電平(邏輯0),又可以保持特有的高阻抗狀態,那么三態門輸出的三種狀態是什么呢?

2019-02-21 16:45:59 73743

73743 三態門主要是用于總線的連接,因為總線只允許同時只有一個使用者。通常在數據總線上接有多個器件,每個器件通過OE/CE之類的信號選通。如器件沒有選通的話它就處于高阻態,相當于沒有接在總線上,不影響其它器件的工作。

2019-03-08 16:49:37 27350

27350 三態門亦稱“三態輸出門”、“三態門輸出電路”。是一種重要的總線接口電路。具有高電平、低電平和高阻抗三種輸出狀態的門電路。

2019-03-10 09:29:25 19309

19309 三態電路可提供三種不同的輸出值:邏輯“0”,邏輯“1”和高阻態。高阻態主要用來將邏輯門同系統的其他部分加以隔離。例如雙向I/O電路和共用總線結構中廣泛應用三態特性。

2019-11-29 07:09:00 5188

5188 三態電路可提供三種不同的輸出值:邏輯“0”,邏輯“1”和高阻態。高阻態主要用來將邏輯門同系統的其他部分加以隔離。例如雙向I/O電路和共用總線結構中廣泛應用三態特性。

2019-11-21 07:05:00 9571

9571 常規的硬件實驗測試三態總線電路邏輯功能的方法是,將三態輸出門的控制端、輸入端分別接邏輯電平開關,改變邏輯電平開關為邏輯1、邏輯0觀測輸出函數的邏輯狀態。存在的問題是,總線分時傳輸關系不直觀。用

2020-04-18 12:50:00 8930

8930 本文檔的主要內容詳細介紹的是三態RS觸發器的Multisim仿真實例電路圖免費下載。

2020-09-03 18:30:06 29

29 本文檔的主要內容詳細介紹的是三態門應用的Multisim仿真實例電路圖免費下載。

2020-09-23 17:32:00 41

41 電子發燒友網為你提供數字電路常見術語:高阻態,三態門資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-27 08:45:27 13

13 三態輸出門電路的輸出端除了出現高、低電平外,還會出現第三種狀態——高阻態,所以叫做三態輸出門電路。 ? ?三態門的工作原理: 當控制端a為“1”時,b型管3導通,同時a端電平通過反向器成為低電平,讓

2021-08-12 11:39:49 14601

14601 由上圖看出,在單相三態門中,當EN=1時,對原電路無影響,電路的輸出符合原來電路的所有邏輯關系,即A可以輸出到B。當EN= 0時,電路內部的所有輸出與外部將處于一種關斷狀態。

2022-10-20 11:01:02 3227

3227 八進制透明鎖存器(三態);八進制 D 觸發器(三態)-74F373_374

2023-03-03 20:05:16 1

1 本文著重探討 HDIO OBUFT 和 IOBUF 用例。如果含三態控制 (OBUFT/IOBUF) 的 HDIO 輸出緩沖器的上電電壓為 3.3 V 或 2.5 V 并且 Data(數據)控制信號與 Tristate(三態)控制信號的切換時間彼此相近,則可能會受到三態數據爭用條件的影響。

2023-07-12 09:50:32 1853

1853

三態輸出的緩沖器有哪些用途? 三態輸出緩沖器是一種電子元件,其主要作用是將一個輸入信號轉換成一個可以控制多個輸出設備的信號。這種緩沖器可以被用于一系列的應用,包括數碼電路、計算機、消費電子設備、通信

2023-09-21 15:55:36 4939

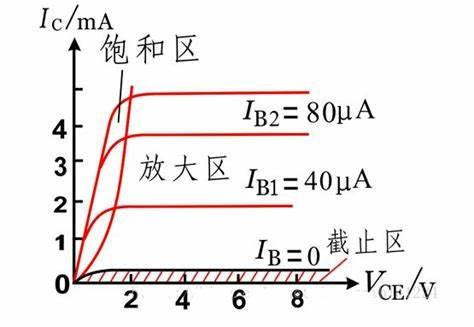

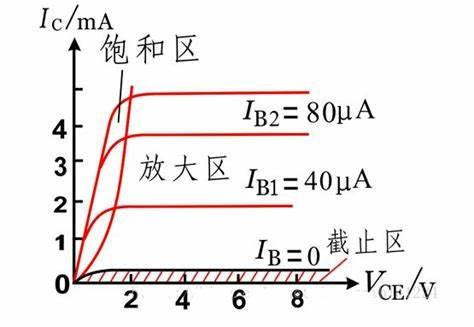

4939 三極管三態分析

2023-12-05 11:49:20 2005

2005

TTL(晶體管-晶體管邏輯)三態門是一種特殊類型的邏輯門,它具有三個狀態:高電平、低電平和高阻抗狀態(也稱為“三態”或“浮動”狀態)。

2024-05-28 15:58:53 6442

6442 TTL(晶體管-晶體管邏輯)三態門是一種特殊類型的數字邏輯門,它具有三種輸出狀態:高電平、低電平和高阻抗狀態(也稱為三態或高阻態)。

2024-05-28 16:04:03 4169

4169 TTL三態輸出門是一種特殊的數字邏輯門,它具有高電平、低電平和高阻抗(三態)三種輸出狀態。

2024-05-28 16:14:59 7654

7654 TTL三態門是一種特殊的邏輯門,它具有三個狀態:高電平、低電平和高阻抗狀態(也稱為“三態”或“浮動”狀態)。

2024-05-28 17:18:14 5097

5097 在電子設計的廣闊領域中,三態緩沖器以其獨特的三態輸出特性,成為了不可或缺的關鍵組件。今天我們就來一起揭秘三態緩沖器的神秘面紗,探討它在電子設計中的重要作用和獨特優勢。 一、三態緩沖器的三態奧秘

2024-06-27 16:01:46 2510

2510 三態門電路是一種特殊的數字邏輯電路,其輸出可以有三種狀態:高電平、低電平和高阻抗狀態。這種電路在數字系統中有著廣泛的應用,如數據總線、地址總線等。 一、三態門電路的工作原理 三態門電路的基本組

2024-07-30 15:17:05 9711

9711 三態邏輯作為一種數字電子技術中的邏輯類型,允許信號線在三種狀態之間切換。本文介紹了三態邏輯電路原理并介紹了四種基本類型的三態緩沖器。如果你對三態邏輯感興趣,相信這篇內容會讓你對其有基礎的認識。

2024-08-01 09:59:32 5263

5263

三態緩沖器(Three-state buffer),又稱為三態門、三態驅動器,是一種特殊的邏輯門電路,其工作原理主要基于三態輸出控制。三態緩沖器對輸入值不執行任何運算,其輸出值和輸入值一樣,但它在計算機的設計中有著重要作用。

2024-08-02 17:47:05 9970

9970 電路在不影響其他電路和總線的前提下,能夠靈活地控制其輸出狀態。以下將詳細探討三態緩沖器在計算機中的具體應用,內容將涵蓋其定義、優勢以及在不同計算機子系統中的具體作用。

2024-08-02 17:48:12 2328

2328 三態緩沖器在總線控制中的應用是計算機系統設計中的一個關鍵環節,其獨特的三態輸出特性使得它在實現多設備間數據共享和傳輸時顯得尤為重要。以下將詳細探討三態緩沖器在總線控制中的應用,包括其基本原理、功能優勢、具體實現方式以及在實際系統中的應用案例。

2024-08-02 17:49:13 4316

4316

電子發燒友App

電子發燒友App

評論