在FPGA設計中,雙向IO(輸入輸出引腳)是一個比較麻煩的東西,但是信號線用作總線等雙向數據傳輸時就要用到inout類型。

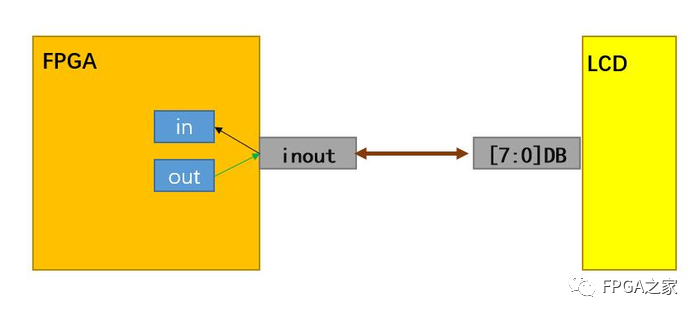

以下用液晶的的數據線用作雙向IO示例:

說是雙向IO端口,其實輸入和輸出不是同時進行的,需要有一個控制信號out_en來控制端口什么時候為輸出,什么時候為輸入。

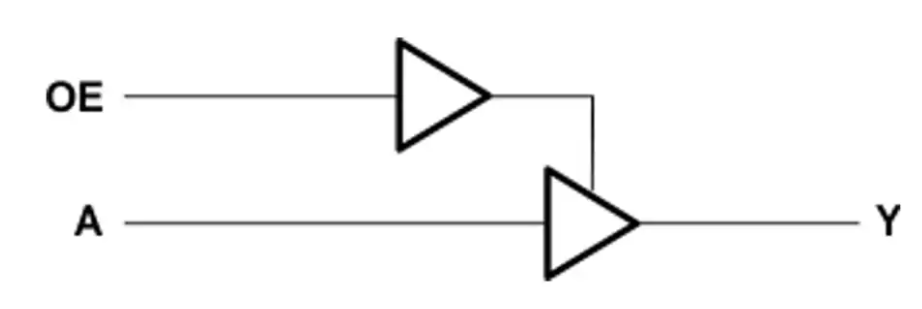

那這里就需要引入一個三態門結構電路。

三態門結構

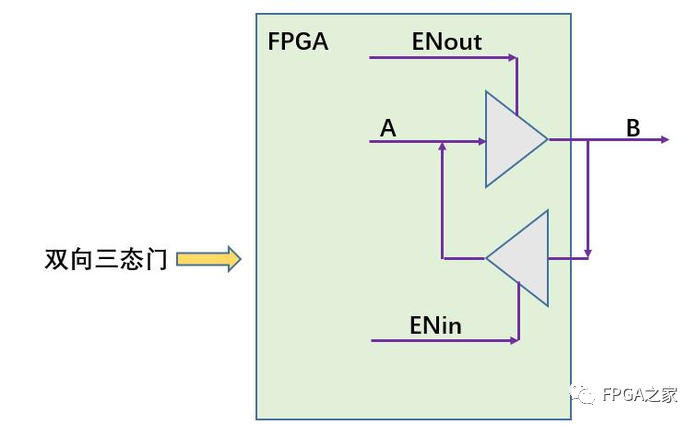

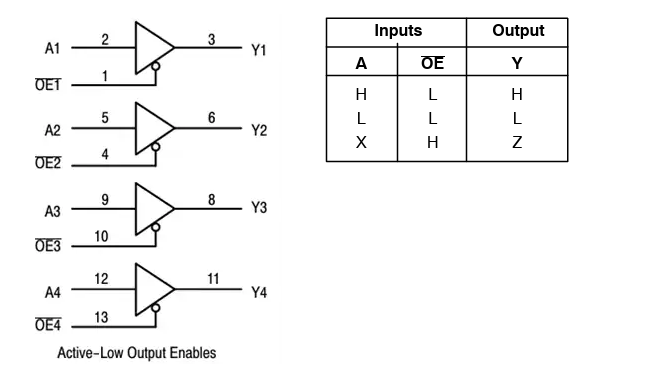

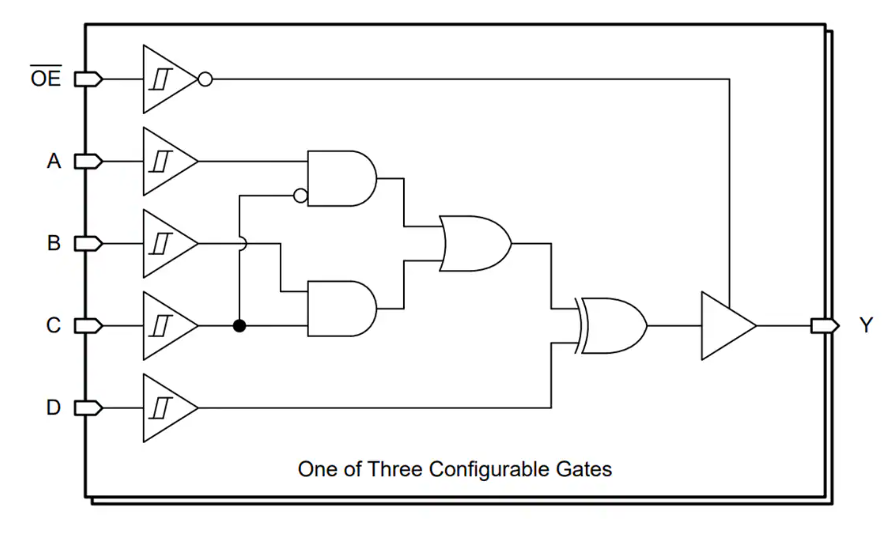

那么三態門的結構是怎樣的呢?

三態門電路的輸出結構和普通門電路的輸出結構有很大的不同,因為它在電路中增加了一個輸出控制端EN。

由上圖看出,在單相三態門中,當EN=1時,對原電路無影響,電路的輸出符合原來電路的所有邏輯關系,即A可以輸出到B。當EN= 0時,電路內部的所有輸出與外部將處于一種關斷狀態。

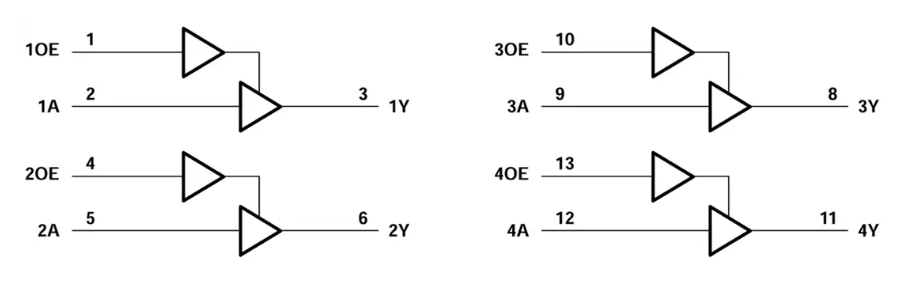

因此,當FPGA的信號線存在雙向IO時,可以有兩個三態門來控制,一個控制輸出,一個控制輸入,結構如下:

當ENout=1,ENin=0時,雙向三態門的電路傳輸方向是A->B;

當ENout=0,ENin=1時,雙向三態門的電路傳輸方向是B->A;

模型分析

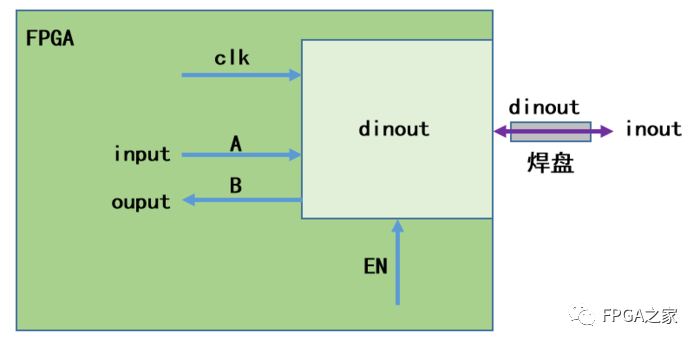

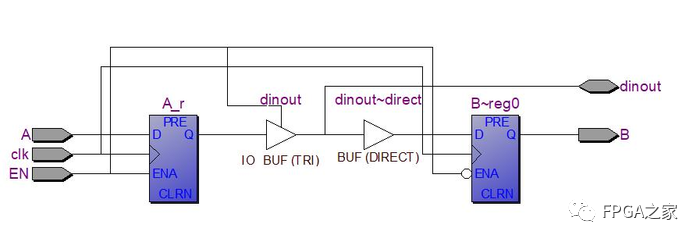

下面簡單做個簡易模型來說明雙向IO如何分別實現作為輸入端口和輸出端口的功能,模塊圖如下:

模型引腳定義

(1)輸入口A定義:當雙向端口dinout作為輸出口時,我們將A端口輸入數據傳到模塊中,讓數據從dinout口出來。

(2)輸出端口B定義:當當雙向端口dinout作為輸入口時,我們將dinout端口輸入數據傳到模塊中,讓數據從B口出來。

(3)EN控制信號定義:當EN=1時,開通三態門,將dinout作為輸出口使用,當EN=0時,把三態門置為高阻態,這時dinout作為輸入口用。

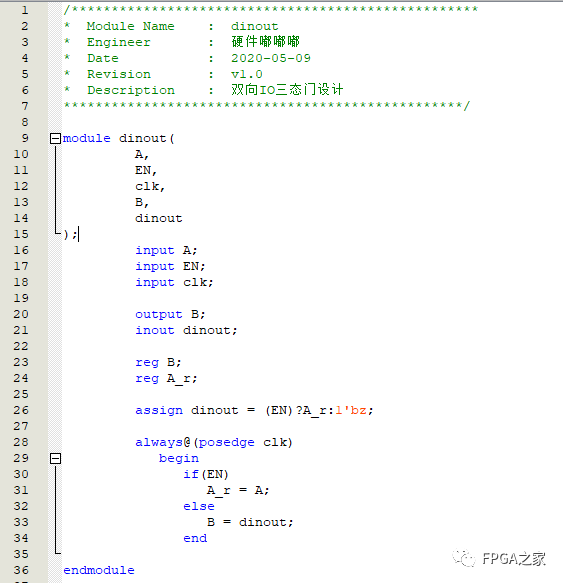

代碼展示

編譯分析后查看RTL視角邏輯電路,符合原有模型設計。

總結說明

(1)FPGA內部不允許傳遞雙向IO信號,只有FPGA對外部才能定義為雙向IO端口,即只有在頂層輸出的信號才可以被賦值為高阻態。

(2)在結構化建模的過程中,一個模塊一個功能的建模,當涉及到內部模塊的端口是雙向IO端口時,然后根據一個雙向IO對應一個輸入,一個輸出和一個使能控制,把模塊中雙向IO的輸出用輸出端口代替,雙向IO的輸入用輸入端口代替,引出使能信號,并把對應assign中賦值的高阻態z根據實際情況給出0或1,來解決FPGA內部雙向IO連接問題。

審核編輯 :李倩

-

FPGA

+關注

關注

1663文章

22483瀏覽量

638628 -

電路

+關注

關注

173文章

6084瀏覽量

178776 -

信號線

+關注

關注

2文章

187瀏覽量

22273

原文標題:FPGA雙向IO使用之三態門說明

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

74LVC126A:適用于多場景的四通道三態緩沖器探析

74LVC125A:一款實用的三態輸出四緩沖器

SGM7SZ245S:八進制三態輸出總線收發器的深度剖析

SGM7SZ126:三態輸出小邏輯緩沖器的技術解析

74HC541:八通道三態緩沖/線驅動器的深度解析

SN74ABT16245ADGGR 具有三態輸出的 16 位總線收發器

SN74HC245NSR 具有三態輸出的八通道總線收發器

MC74VHCT125A三態總線緩沖器技術深度解析與應用指南

SN74AHC126四路三態總線緩沖門技術解析與應用指南

SN74AHCT1G126 單總線緩沖門技術解析與應用指南

Texas Instruments SN74AC3G99/SN74AC3G99-Q1多功能門特性/應用/框圖

FPGA三態門的結構是怎樣的呢?

FPGA三態門的結構是怎樣的呢?

評論