本文將對(duì)源同步定時(shí)如何優(yōu)化高速接口時(shí)序裕量進(jìn)行討論。時(shí)序預(yù)算是對(duì)系統(tǒng)正常工作所需時(shí)序參數(shù)或時(shí)序要求的計(jì)算。

2012-03-20 10:46:32 6290

6290

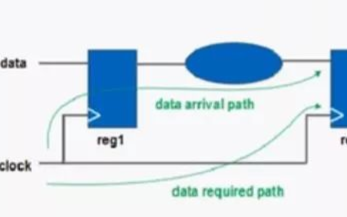

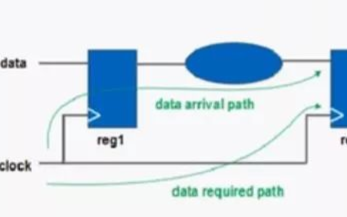

表。 這4類(lèi)路徑中,我們最為關(guān)心是②的同步時(shí)序路徑,也就是FPGA內(nèi)部的時(shí)序邏輯。 時(shí)序模型 典型的時(shí)序模型如下圖所示,一個(gè)完整的時(shí)序路徑包括源時(shí)鐘路徑、數(shù)據(jù)路徑和目的時(shí)鐘路徑,也可以表示為觸發(fā)器+組合邏輯+觸發(fā)器的模型。 該

2020-11-17 16:41:52 3687

3687

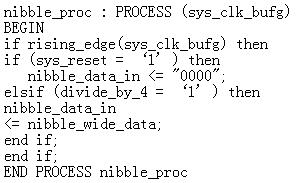

更快,而一個(gè)壞的代碼風(fēng)格則給后續(xù)時(shí)序收斂造成很大負(fù)擔(dān)。你可能要花費(fèi)很長(zhǎng)時(shí)間去優(yōu)化時(shí)序,保證時(shí)序收斂。拆解你的代碼,添加寄存器,修改走線(xiàn),最后讓你原來(lái)的代碼遍體鱗傷。這一篇基于賽靈思的器件來(lái)介紹一下如何在開(kāi)始碼代碼的時(shí)候就考慮時(shí)序收斂的問(wèn)題,寫(xiě)出

2020-11-20 15:51:41 4814

4814

《UltraFast 設(shè)計(jì)方法時(shí)序收斂快捷參考指南》提供了以下分步驟流程, 用于根據(jù)《UltraFast設(shè)計(jì)方法指南》( UG949 )中的建議快速完成時(shí)序收斂: 1初始設(shè)計(jì)檢查:在實(shí)現(xiàn)設(shè)計(jì)前審核

2021-11-05 15:10:26 5891

5891

在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束和時(shí)序例外約束才能實(shí)現(xiàn)PCB板級(jí)的時(shí)序收斂。因此,FPGA時(shí)序約束中IO口時(shí)序約束也是一個(gè)重點(diǎn)。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2392

2392 FPGA開(kāi)發(fā)過(guò)程中,離不開(kāi)時(shí)序約束,那么時(shí)序約束是什么?簡(jiǎn)單點(diǎn)說(shuō),FPGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿(mǎn)足建立和保持時(shí)間。

2023-06-06 17:53:07 1938

1938

在FPGA設(shè)計(jì)中,時(shí)序約束對(duì)于電路性能和可靠性非常重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的主時(shí)鐘約束。

2023-06-12 17:29:21 4234

4234 今天跟大家分享的內(nèi)容很重要,也是調(diào)試FPGA經(jīng)驗(yàn)的總結(jié)。隨著FPGA對(duì)時(shí)序和性能的要求越來(lái)越高,高頻率、大位寬的設(shè)計(jì)越來(lái)越多。在調(diào)試這些FPGA樣機(jī)時(shí),需要從寫(xiě)代碼時(shí)就要小心謹(jǐn)慎,否則寫(xiě)出來(lái)的代碼

2023-08-01 09:18:34 3075

3075

FPGA設(shè)計(jì)中的絕大部分電路為同步時(shí)序電路,其基本模型為“寄存器+組合邏輯+寄存器”。同步意味著時(shí)序路徑上的所有寄存器在時(shí)鐘信號(hào)的驅(qū)動(dòng)下步調(diào)一致地運(yùn)作。

2023-08-03 09:27:25 2201

2201

前面講解了時(shí)序約束的理論知識(shí)FPGA時(shí)序約束理論篇,本章講解時(shí)序約束實(shí)際使用。

2023-08-14 18:22:14 3030

3030

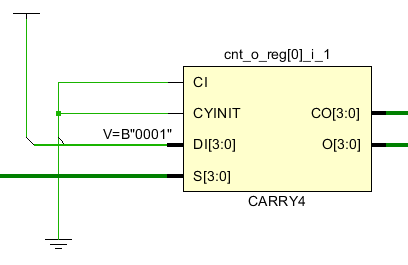

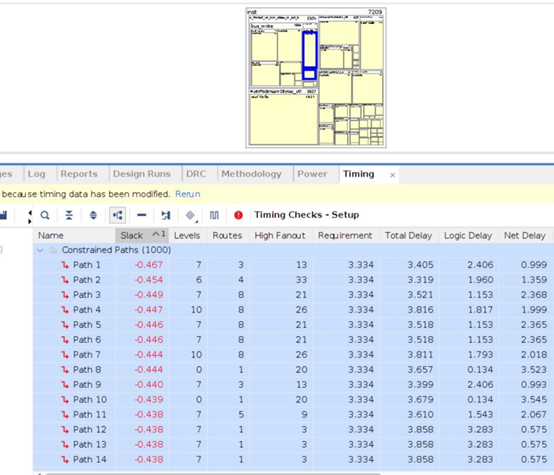

在之前的文章里面介紹了Canny算法的原理和基于Python的參考模型,之后呢在FPGA上完成了Canny算法的實(shí)現(xiàn),可是遇到了時(shí)序不收斂的問(wèn)題,記錄一下。

2023-11-18 16:38:28 1783

1783

在輸入信號(hào)到輸出信號(hào)中,因?yàn)榻?jīng)過(guò)的傳輸路徑、寄存器、門(mén)電路等器件的時(shí)間,這個(gè)時(shí)間就是時(shí)序。開(kāi)發(fā)工具不知道我們路徑上的要求,我們通過(guò)時(shí)序約束來(lái)告訴開(kāi)發(fā)工具,根據(jù)要求,重新規(guī)劃,從而實(shí)現(xiàn)我們的時(shí)序要求,達(dá)到時(shí)序的收斂。

2019-07-31 14:50:41 7018

7018

今天給大俠帶來(lái)FPGA 高級(jí)設(shè)計(jì):時(shí)序分析和收斂,話(huà)不多說(shuō),上貨。

這里超鏈接一篇之前的STA的文章,僅供各位大俠參考。

FPGA STA(靜態(tài)時(shí)序分析)

什么是靜態(tài)時(shí)序分析?靜態(tài)時(shí)序分析就是

2024-06-17 17:07:28

經(jīng)過(guò)兩天的惡補(bǔ),特別是學(xué)習(xí)了《第五章_FPGA時(shí) 序收斂》及其相關(guān)的視頻后,我基本上明白了時(shí)序分析的概念和用法。之后的幾天,我會(huì)根據(jù)一些官方的文件對(duì)時(shí)序分析進(jìn)行更系統(tǒng)、深入的學(xué)習(xí)。先總結(jié)一下之前

2011-09-23 10:26:01

你好: 現(xiàn)在我使用xilinx FPGA進(jìn)行設(shè)計(jì)。遇到問(wèn)題。我不知道FPGA設(shè)計(jì)是否符合時(shí)序要求。我在設(shè)計(jì)中添加了“時(shí)鐘”時(shí)序約束。我不知道如何添加其他約束。一句話(huà),我不知道哪條路徑應(yīng)該被禁止。我

2019-03-18 13:37:27

的時(shí)序約束。FPGA作為PCB上的一個(gè)器件,是整個(gè)PCB系統(tǒng)時(shí)序收斂的一部分。FPGA作為PCB設(shè)計(jì)的一部分,是需要PCB設(shè)計(jì)工程師像對(duì)待所有COTS器件一樣,閱讀并分析其I/O Timing

2016-06-02 15:54:04

(InputDelay、OutputDelay)、上下拉電阻、驅(qū)動(dòng)電流強(qiáng)度等。加入I/O約束后的時(shí)序約束,才是完整的時(shí)序約束。FPGA作為PCB上的一個(gè)器件,是整個(gè)PCB系統(tǒng)時(shí)序收斂的一部分。FPGA作為

2017-12-27 09:15:17

FPGA畢竟不是ASIC,對(duì)時(shí)序收斂的要求更加嚴(yán)格,本文主要介紹本人在工程中學(xué)習(xí)到的各種時(shí)序約束技巧。 首先強(qiáng)烈推薦閱讀官方文檔UG903和UG949,這是最重要的參考資料,沒(méi)有之一。它提倡

2020-12-23 17:42:10

基本的時(shí)序分析理論2本文節(jié)選自特權(quán)同學(xué)的圖書(shū)《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 下面我們?cè)賮?lái)看一個(gè)例子,如圖8.2所示

2015-07-14 11:06:10

FPGA 設(shè)計(jì)優(yōu)化主要分為編碼風(fēng)格、設(shè)計(jì)規(guī)劃和時(shí)序收斂三大部分,這 些因素直接決定了 FPGA 設(shè)計(jì)的成敗。 編碼風(fēng)格直接影響 FPGA 設(shè)計(jì)的實(shí)現(xiàn)并最終影響設(shè)計(jì)的性能。盡管綜合 工具集成

2022-09-29 06:12:02

《FPGA設(shè)計(jì)時(shí)序收斂》,很好的PPT!推薦給大家[hide][/hide]

2011-07-26 11:24:49

當(dāng)你的FPGA設(shè)計(jì)不能滿(mǎn)足時(shí)序要求時(shí),原因也許并不明顯。解決方案不僅僅依賴(lài)于使用FPGA的實(shí)現(xiàn)工具來(lái)優(yōu)化設(shè)計(jì)從而滿(mǎn)足時(shí)序要求,也需要設(shè)計(jì)者具有明確目標(biāo)和診斷/隔離時(shí)序問(wèn)題的能力。設(shè)計(jì)者現(xiàn)在有一些

2019-08-11 08:30:00

個(gè)器件,是整個(gè)PCB系統(tǒng)時(shí)序收斂的一部分。FPGA作為PCB設(shè)計(jì)的一部分,是需要PCB設(shè)計(jì)工程師像對(duì)待所有COTS器件一樣,閱讀并分析其I/O Timing Diagram的。FPGA不同于COTS

2017-10-20 13:26:35

特定模塊劃分到不同的時(shí)鐘域里;但異步時(shí)鐘域不宜太多。綜合時(shí)使用retiming,duplication;physical synthesis優(yōu)化,現(xiàn)在的綜合器這方面已經(jīng)足夠聰明了。預(yù)算允許可使用速度更快的芯片;這個(gè)也許是實(shí)現(xiàn) “不修改RTL又時(shí)序收斂” 的最可能的方式。

2018-06-07 17:55:37

當(dāng)你的FPGA設(shè)計(jì)不能滿(mǎn)足時(shí)序要求時(shí),原因也許并不明顯。解決方案不僅僅依賴(lài)于使用FPGA的實(shí)現(xiàn)工具來(lái)優(yōu)化設(shè)計(jì)從而滿(mǎn)足時(shí)序要求,也需要設(shè)計(jì)者具有明確目標(biāo)和診斷/隔離時(shí)序問(wèn)題的能力。設(shè)計(jì)者現(xiàn)在有一些

2021-05-18 15:55:00

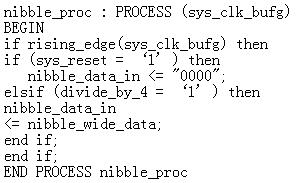

摘要:RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術(shù)的高速發(fā)展,一些常見(jiàn)的接口電路的時(shí)序電路可以通過(guò)FPGA實(shí)現(xiàn),通過(guò)這種設(shè)計(jì)可減少電路系統(tǒng)元件的數(shù)量,提高系統(tǒng)集成度和可靠性。詳細(xì)闡述

2019-06-19 07:42:37

時(shí)序分析是FPGA設(shè)計(jì)的必備技能之一,特別是對(duì)于高速邏輯設(shè)計(jì)更需要時(shí)序分析,經(jīng)過(guò)基礎(chǔ)的FPGA是基于時(shí)序的邏輯器件,每一個(gè)時(shí)鐘周期對(duì)于FPGA內(nèi)部的寄存器都有特殊的意義,不同的時(shí)鐘周期執(zhí)行不同的操作

2017-02-26 09:42:48

如何解決功耗影響時(shí)序的問(wèn)題?工程師在解決功耗問(wèn)題的時(shí)候,有哪些準(zhǔn)則?

2021-04-08 06:11:51

如何使用基于圖形的物理綜合加快FPGA設(shè)計(jì)時(shí)序收斂?

2021-05-06 09:19:08

如何有效的管理FPGA設(shè)計(jì)中的時(shí)序問(wèn)題當(dāng)FPGA設(shè)計(jì)面臨到高級(jí)接口的設(shè)計(jì)問(wèn)題時(shí),EMA的TimingDesigner可以簡(jiǎn)化這些設(shè)計(jì)問(wèn)題,并提供對(duì)幾乎所有接口的預(yù)先精確控制。從簡(jiǎn)單SRAM接口到高速

2009-04-14 17:03:52

您好,如果我想為我的設(shè)計(jì)獲得最佳時(shí)序收斂,我應(yīng)該使用什么實(shí)施策略?例如,如果我想改善設(shè)置和保持的松弛度,我應(yīng)該選擇哪種最佳策略?以上來(lái)自于谷歌翻譯以下為原文Hello,If i want

2018-11-05 11:40:14

什么是時(shí)序收斂?如何去解決物理設(shè)計(jì)中時(shí)序收斂的問(wèn)題?

2021-04-26 06:38:50

總結(jié)時(shí)序收斂的目的是讓FPGA design 按預(yù)設(shè)的邏輯正常的工作。為了使其正常工作,需要考慮至少三處:FPGA內(nèi)部的寄存器-寄存器時(shí)序要求,FPGA輸入數(shù)據(jù)的時(shí)序要求,FPGA輸出信號(hào)的要求。

2019-07-09 09:14:48

如何收斂高速ADC時(shí)序?有哪種辦法可以最大化ADC的建立和保持時(shí)間?

2021-04-14 06:06:09

如何在開(kāi)始碼代碼的時(shí)候就考慮時(shí)序收斂的問(wèn)題?

2021-06-18 06:29:47

時(shí)鐘,到我們FPGA的工作時(shí)鐘clk1再執(zhí)行一次全編譯,所有的路徑達(dá)到時(shí)序收斂當(dāng)然,除了這些,我們還需要一些時(shí)序上的優(yōu)化,以及一些微調(diào),要想達(dá)到系統(tǒng)的真正穩(wěn)定,光做這些還是不夠的,小墨也是在學(xué)習(xí)當(dāng)中

2015-03-31 10:35:18

FPGA內(nèi)部的走線(xiàn)延遲,時(shí)鐘延遲等等,這里我們添加的時(shí)序約束,就相當(dāng)于我們?cè)跊](méi)有下板之前,通過(guò)計(jì)算,來(lái)模擬仿真下板后的延遲情況,并通過(guò)時(shí)序報(bào)告查看有哪些違規(guī)路徑,以及建立保持時(shí)間不平衡的情況,通過(guò)時(shí)序

2015-03-31 10:20:00

Cadence高速PCB的時(shí)序分析:列位看觀,在上一次的連載中,我們介紹了什么是時(shí)序電路,時(shí)序分析的兩種分類(lèi)(同步和異步),并講述了一些關(guān)于SDRAM 的基本概念。這一次的連載中,

2009-07-01 17:23:27 0

0 如何有效的管理FPGA設(shè)計(jì)中的時(shí)序問(wèn)題

當(dāng)FPGA設(shè)計(jì)面臨到高級(jí)接口的設(shè)計(jì)問(wèn)題時(shí),EMA的TimingDesigner可以簡(jiǎn)化這些設(shè)計(jì)問(wèn)題,并提供對(duì)幾乎所有接口的預(yù)先精確控制。從簡(jiǎn)單

2009-04-15 14:19:31 947

947

更高速的 ADC 在轉(zhuǎn)換器輸出和接收機(jī)輸入之間有嚴(yán)格的時(shí)序要求;知道如何利用產(chǎn)品說(shuō)明書(shū)數(shù)字來(lái)保證無(wú)錯(cuò)誤數(shù)字傳輸。

最近幾年,高速、高精度的模數(shù)轉(zhuǎn)換器 (ADC)

2010-07-13 09:59:10 969

969 您編寫(xiě)的代碼是不是雖然在仿真器中表現(xiàn)正常,但是在現(xiàn)場(chǎng)卻斷斷續(xù)續(xù)出錯(cuò)?要不然就是有可能在您使用更高版本的工具鏈進(jìn)行編譯時(shí),它開(kāi)始出錯(cuò)。您檢查自

2010-09-30 10:56:37 1505

1505

一、摘要 從簡(jiǎn)單SRAM接口到高速同步接口,TimingDesigner軟件允許設(shè)計(jì)者在設(shè)計(jì)流程的初期就判斷出潛在的時(shí)序問(wèn)題,盡最大可能在第一時(shí)間解決時(shí)序問(wèn)題。在設(shè)計(jì)過(guò)程的早期檢測(cè)到時(shí)序問(wèn)題,不僅節(jié)省時(shí)間,而且可以更容易的實(shí)施設(shè)計(jì)方案。美國(guó)EMA公司的設(shè)計(jì)自動(dòng)

2011-01-13 16:25:00 103

103 介紹了采用STA (靜態(tài)時(shí)序分析)對(duì)FPGA (現(xiàn)場(chǎng)可編程門(mén)陣列)設(shè)計(jì)進(jìn)行時(shí)序驗(yàn)證的基本原理,并介紹了幾種與STA相關(guān)聯(lián)的時(shí)序約束。針對(duì)時(shí)序不滿(mǎn)足的情況,提出了幾種常用的促進(jìn) 時(shí)序收斂的方

2011-05-27 08:58:50 70

70 當(dāng)你的FPGA設(shè)計(jì)不能滿(mǎn)足時(shí)序要求時(shí),原因也許并不明顯。解決方案不僅僅依賴(lài)于使用FPGA的實(shí)現(xiàn)工具來(lái)優(yōu)化設(shè)計(jì)從而滿(mǎn)足時(shí)序要求,也需要設(shè)計(jì)者具有明確目標(biāo)和診斷/隔離時(shí)序問(wèn)題的能力。

2014-08-15 14:22:10 1476

1476 FPGA時(shí)序約束方法很好地資料,兩大主流的時(shí)序約束都講了!

2015-12-14 14:21:25 19

19 基于時(shí)序路徑的FPGA時(shí)序分析技術(shù)研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA設(shè)計(jì)中的時(shí)序問(wèn)題

2017-01-14 12:49:02 14

14 當(dāng)你的FPGA設(shè)計(jì)不能滿(mǎn)足時(shí)序要求時(shí),原因也許并不明顯。解決方案不僅僅依賴(lài)于使用FPGA的實(shí)現(xiàn)工具來(lái)優(yōu)化設(shè)計(jì)從而滿(mǎn)足時(shí)序要求,也需要設(shè)計(jì)者具有明確目標(biāo)和診斷/隔離時(shí)序問(wèn)題的能力。設(shè)計(jì)者現(xiàn)在有一些

2017-02-09 01:59:11 510

510 fpga時(shí)序收斂

2017-03-01 13:13:34 23

23 這是特權(quán)同學(xué)的關(guān)于fpga時(shí)序分析方面的極好資料

2017-08-28 11:19:14 20

20 如今的集成電路(Integrated Circuit,IC)設(shè)計(jì)往往要求芯片包含多個(gè)工作模式,并且在不同工藝角(corner)下能正常工作。工藝角和工作模式的增加,無(wú)疑使時(shí)序收斂面臨極大挑戰(zhàn)。本文

2017-10-20 15:21:11 3

3 一個(gè)好的FPGA設(shè)計(jì)一定是包含兩個(gè)層面:良好的代碼風(fēng)格和合理的約束。時(shí)序約束作為FPGA設(shè)計(jì)中不可或缺的一部分,已發(fā)揮著越來(lái)越重要的作用。毋庸置疑,時(shí)序約束的最終目的是實(shí)現(xiàn)時(shí)序收斂。時(shí)序收斂作為

2017-11-17 07:54:36 2967

2967

針對(duì)八通道采樣器AD9252的高速串行數(shù)據(jù)接口的特點(diǎn),提出了一種基于FPGA時(shí)序約束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行數(shù)據(jù),利用FPGA內(nèi)部的時(shí)鐘管理模塊DCM、位置約束

2017-11-17 12:27:01 7352

7352

現(xiàn)有的工具和技術(shù)可幫助您有效地實(shí)現(xiàn)時(shí)序性能目標(biāo)。當(dāng)您的FPGA 設(shè)計(jì)無(wú)法滿(mǎn)足時(shí)序性能目標(biāo)時(shí),其原因可能并不明顯。解決方案不僅取決于FPGA 實(shí)現(xiàn)工具為滿(mǎn)足時(shí)序要求而優(yōu)化設(shè)計(jì)的能力,還取決于設(shè)計(jì)人員指定前方目標(biāo),診斷并隔離下游時(shí)序問(wèn)題的能力。

2017-11-18 04:32:34 3842

3842 與賽靈思FPGA連接的數(shù)據(jù)轉(zhuǎn)換器正迅速采用全新JESD204B高速串行鏈路。要使用該接口格式及協(xié)議,設(shè)計(jì)必須考慮一些基本硬件及時(shí)序問(wèn)題。

2018-07-19 13:51:00 6518

6518

作為賽靈思用戶(hù)論壇的定期訪(fǎng)客(見(jiàn) ),我注意到新用戶(hù)往往對(duì)時(shí)序收斂以及如何使用時(shí)序約束來(lái)達(dá)到時(shí)序收斂感到困惑。為幫助 FPGA設(shè)計(jì)新手實(shí)現(xiàn)時(shí)序收斂,讓我們來(lái)深入了解時(shí)序約束以及如何利用時(shí)序約束實(shí)現(xiàn)

2017-11-24 19:37:55 5955

5955

FPGA的設(shè)計(jì)與高速接口技術(shù)可以幫助你滿(mǎn)足今天的市場(chǎng)要求,但也提出了一些有趣的設(shè)計(jì)挑戰(zhàn)。為了確保存儲(chǔ)器接口的數(shù)據(jù)傳輸準(zhǔn)確,在超過(guò)200兆赫茲以上,進(jìn)行時(shí)序分析將發(fā)揮更突出的作用,以識(shí)別和解決系統(tǒng)運(yùn)行

2017-11-25 01:06:01 1541

1541

FPGA器件的需求取決于系統(tǒng)和上下游(upstream and downstrem)設(shè)備。我們的設(shè)計(jì)需要和其他的devices進(jìn)行數(shù)據(jù)的交互,其他的devices可能是FPGA外部的芯片,可能是FPGA內(nèi)部的硬核。

2018-07-11 09:37:00 10018

10018

FPGA時(shí)序收斂讓你的產(chǎn)品達(dá)到最佳性能!

2018-04-10 11:38:48 19

19 FPGA設(shè)計(jì)一個(gè)很重要的設(shè)計(jì)是時(shí)序設(shè)計(jì),而時(shí)序設(shè)計(jì)的實(shí)質(zhì)就是滿(mǎn)足每一個(gè)觸發(fā)器的建立(Setup)/保持(Hold)時(shí)間的要求。

2018-06-05 01:43:00 4865

4865

UFDM建議正確的HDL coding風(fēng)格來(lái)滿(mǎn)足目標(biāo)器件,討論時(shí)序約束和時(shí)序收斂。正確的IO約束,IO管腳分配和布局,物理約束,并提供了滿(mǎn)足時(shí)序收斂的技巧和讓FPGA工作快速穩(wěn)定的方法。

2018-06-27 09:50:00 2491

2491

如今的集成電路(Integrated Circuit,IC)設(shè)計(jì)往往要求芯片包含多個(gè)工作模式,并且在不同工藝角(corner)下能正常工作。工藝角和工作模式的增加,無(wú)疑使時(shí)序收斂面臨極大挑戰(zhàn)。本文

2018-08-05 10:26:16 6787

6787

多片A/D器件流水轉(zhuǎn)換,并將數(shù)據(jù)采樣結(jié)果儲(chǔ)存到由Block RAM構(gòu)建的高速緩沖RAM陣列中,采樣時(shí)序由FPGA生成,保證了多路并行采樣的高同步性。

2018-08-28 10:16:07 14862

14862

由于FPGA的高速和并行處理特性,使其廣泛應(yīng)用在高速信息處理系統(tǒng)中.以X射線(xiàn)能譜的前端數(shù)據(jù)處理為對(duì)象,提出了基于FPGA實(shí)現(xiàn)對(duì)高速數(shù)據(jù)的采集與處理的方法.同時(shí)討論了電子測(cè)量系統(tǒng)中的補(bǔ)償措施.

2018-09-21 15:50:58 13

13 1.考慮器件的資源,包括LE,ram資源,硬件乘法器,PLL,全局時(shí)鐘網(wǎng)絡(luò)等。 總體來(lái)說(shuō),對(duì)于FPGA設(shè)計(jì),資源一定要留有余量,否則最后的時(shí)序收斂會(huì)比較困難。我認(rèn)為使用80%左右是比較合適的。對(duì)于資源使用量在95%以上的設(shè)計(jì),除了時(shí)序收斂,可能還會(huì)遇到一些你想不到的問(wèn)題。

2018-11-02 17:18:03 8

8 FPGA設(shè)計(jì)中,層次結(jié)構(gòu)設(shè)計(jì)和復(fù)位策略影響著FPGA的時(shí)序。在高速設(shè)計(jì)時(shí),合理的層次結(jié)構(gòu)設(shè)計(jì)與正確的復(fù)位策略可以?xún)?yōu)化時(shí)序,提高運(yùn)行頻率。

2019-02-15 15:15:53 1270

1270 本課程以目前流行的Xilinx 7系列FPGA的開(kāi)發(fā)為主線(xiàn),全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語(yǔ)言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開(kāi)發(fā)開(kāi)始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-05 07:08:00 3476

3476

萬(wàn)幸的是,當(dāng)今FPGA工具(比如Xilinx的 Vivado)都有很多開(kāi)關(guān)和設(shè)置選項(xiàng)來(lái)幫助時(shí)序收斂。InTime的方法,就是通過(guò)調(diào)整FPGA工具的編譯過(guò)程來(lái)解決用戶(hù)的時(shí)序問(wèn)題和其他性能問(wèn)題。

2019-07-26 15:56:23 4237

4237

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA經(jīng)常有哪些常見(jiàn)警告應(yīng)該如何解決。

2020-10-14 16:00:03 9

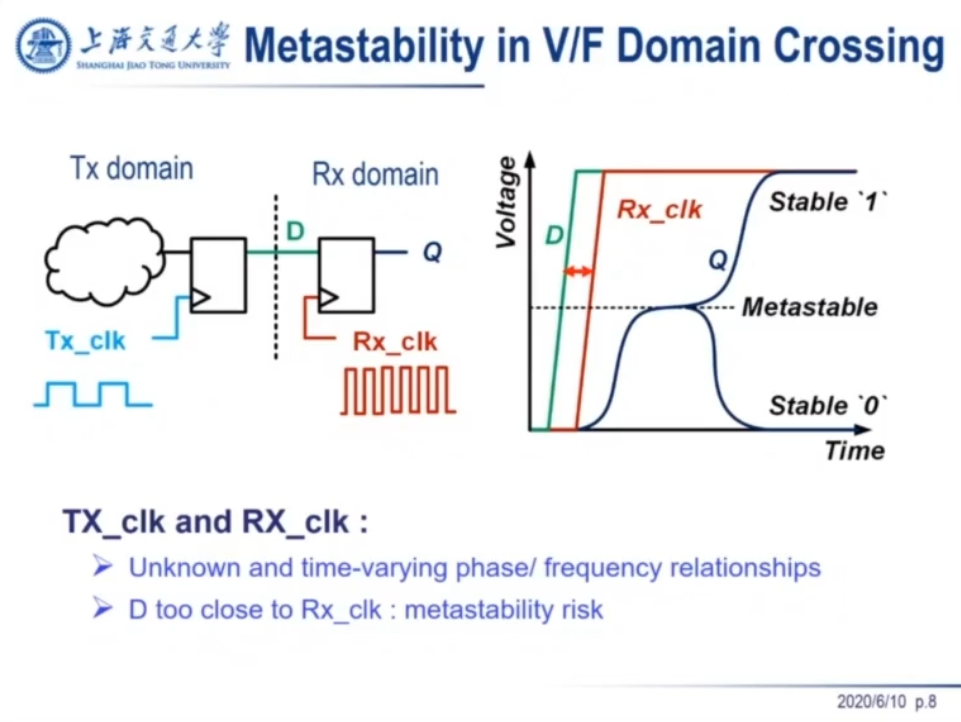

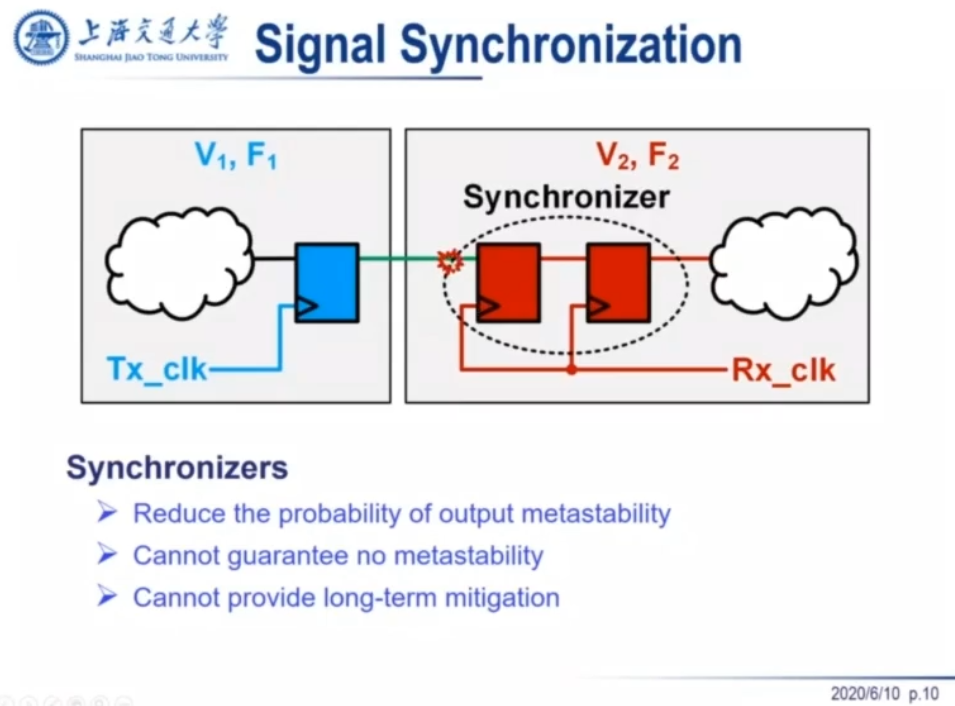

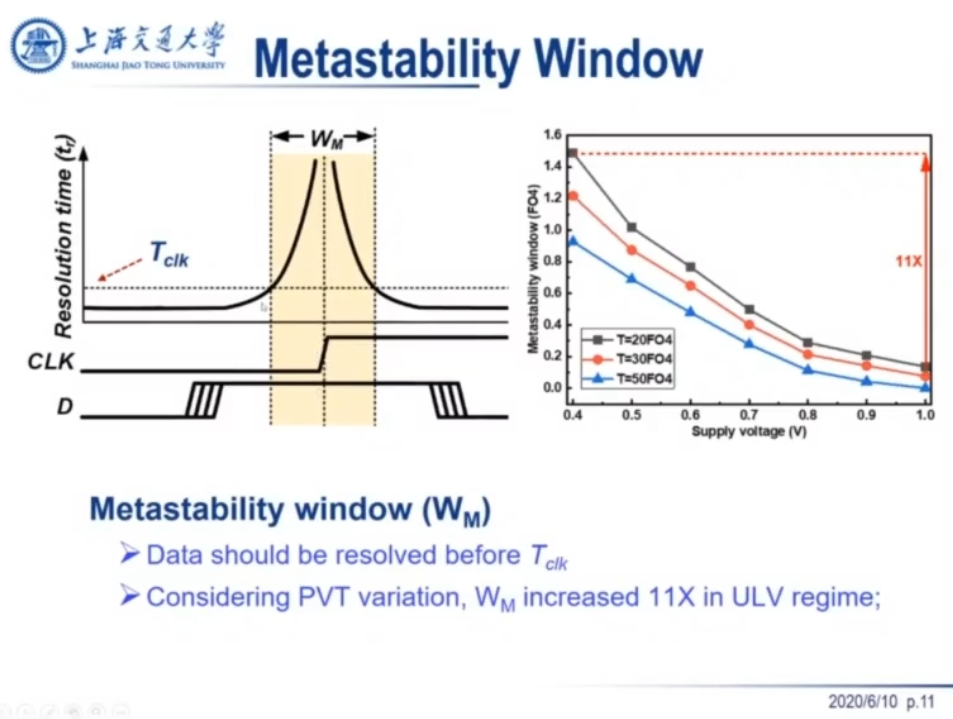

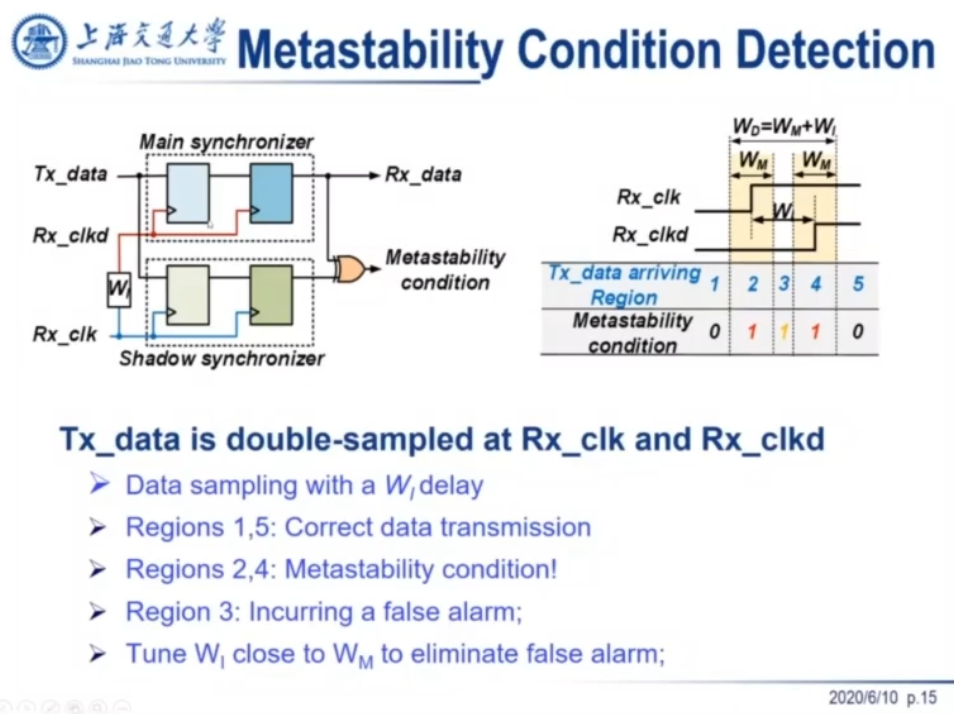

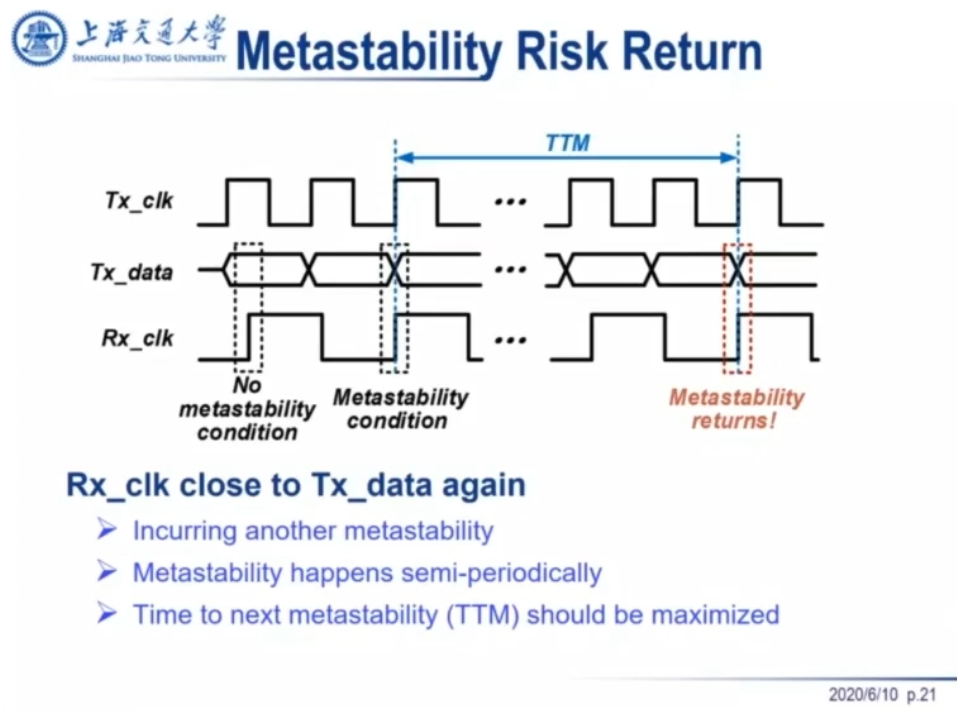

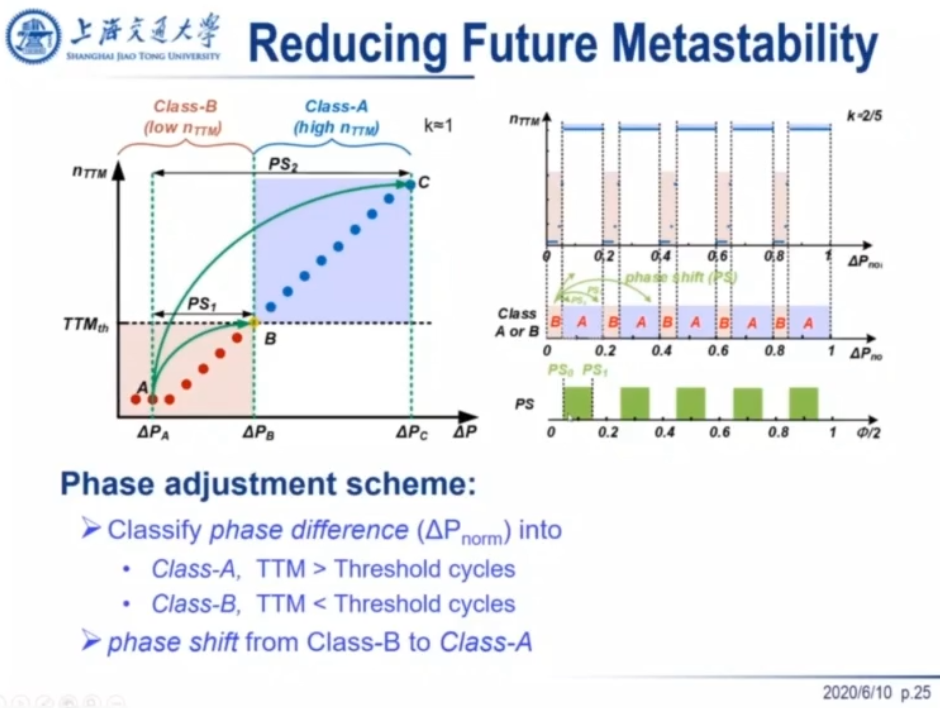

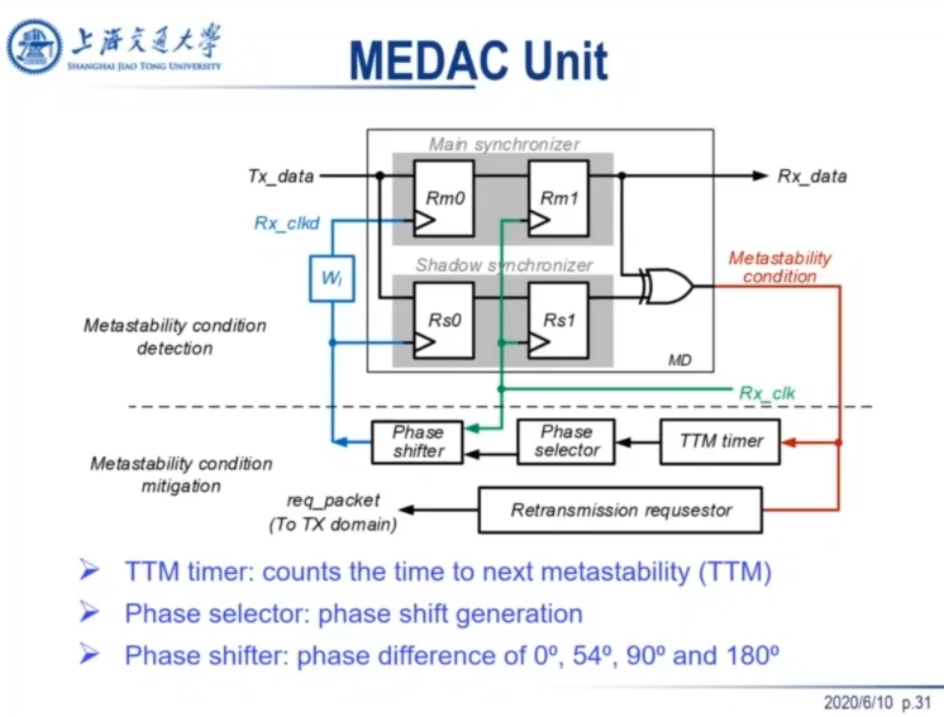

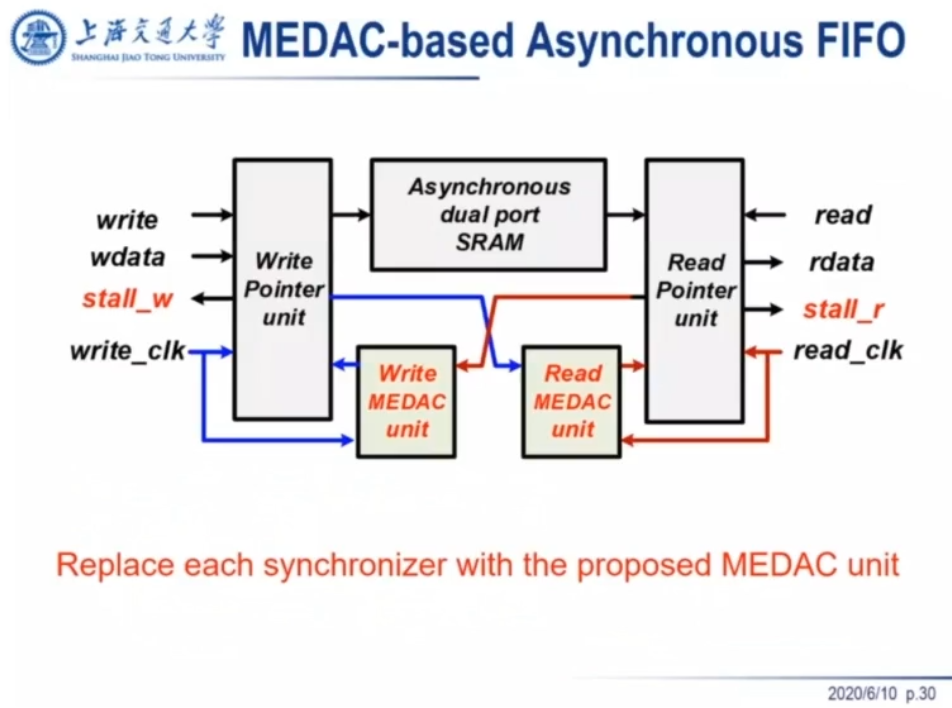

9 本文是一篇詳細(xì)介紹ISSCC2020會(huì)議上一篇有關(guān)亞穩(wěn)態(tài)解決方案的文章,該技術(shù)也使得FPGA在較高頻率下的時(shí)序收斂成為了可能。亞穩(wěn)態(tài)問(wèn)題是芯片設(shè)計(jì)和FPGA設(shè)計(jì)中常見(jiàn)的問(wèn)題,隨著FPGA的發(fā)展,時(shí)序

2020-10-22 18:00:22 5277

5277

本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA經(jīng)常會(huì)碰到哪些問(wèn)題應(yīng)該如何解決。

2020-10-30 16:54:49 14

14 時(shí)序分析結(jié)果,并根據(jù)設(shè)計(jì)者的修復(fù)使設(shè)計(jì)完全滿(mǎn)足時(shí)序約束的要求。本章包括以下幾個(gè)部分: 1.1 靜態(tài)時(shí)序分析簡(jiǎn)介 1.2 FPGA 設(shè)計(jì)流程 1.3 TimeQuest 的使用 1.4 常用時(shí)序約束 1.5 時(shí)序分析的基本概念

2020-11-11 08:00:00 67

67 對(duì)自己的設(shè)計(jì)的實(shí)現(xiàn)方式越了解,對(duì)自己的設(shè)計(jì)的時(shí)序要求越了解,對(duì)目標(biāo)器件的資源分布和結(jié)構(gòu)越了解,對(duì)EDA工具執(zhí)行約束的效果越了解,那么對(duì)設(shè)計(jì)的時(shí)序約束目標(biāo)就會(huì)越清晰,相應(yīng)地,設(shè)計(jì)的時(shí)序收斂過(guò)程就會(huì)更可控。

2021-01-11 17:44:44 8

8 在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束利序例外約束才能實(shí)現(xiàn)PCB板級(jí)的時(shí)序收斂。因此,FPGA時(shí)序約束中IO口時(shí)序約束也是重點(diǎn)。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 在 FPGA 設(shè)計(jì)進(jìn)程中,時(shí)序收斂無(wú)疑是一項(xiàng)艱巨的任務(wù)。低估這項(xiàng)任務(wù)的復(fù)雜性常常導(dǎo)致工作規(guī)劃面臨無(wú)休止的壓力。賽靈思提供了諸多工具,用于幫助縮短時(shí)序收斂所需時(shí)間,從而加速產(chǎn)品上市。本篇博文描述了一種

2021-05-19 11:25:47 3922

3922

上一篇《FPGA時(shí)序約束分享01_約束四大步驟》一文中,介紹了時(shí)序約束的四大步驟。

2022-03-18 10:29:28 2166

2166

時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話(huà)題,也是FPGA開(kāi)發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來(lái),先介紹時(shí)序分析中的一些基本概念。

2022-03-18 11:07:13 3922

3922 本文章探討一下FPGA的時(shí)序input delay約束,本文章內(nèi)容,來(lái)源于配置的明德?lián)P時(shí)序約束專(zhuān)題課視頻。

2022-05-11 10:07:56 4989

4989

本文章探討一下FPGA的時(shí)序input delay約束,本文章內(nèi)容,來(lái)源于明德?lián)P時(shí)序約束專(zhuān)題課視頻。

2022-07-25 15:37:07 3757

3757

本文旨在提供一種方法,以幫助設(shè)計(jì)師判斷給定模塊是否能夠在空裸片上達(dá)成時(shí)序收斂。 如果目標(biāo)模塊無(wú)法在空裸片上達(dá)成非關(guān)聯(lián) (OOC) 時(shí)序收斂,則恐難以與設(shè)計(jì)其余部分達(dá)成關(guān)聯(lián)性時(shí)序收斂。設(shè)計(jì)師可從完整

2022-08-02 11:37:35 989

989

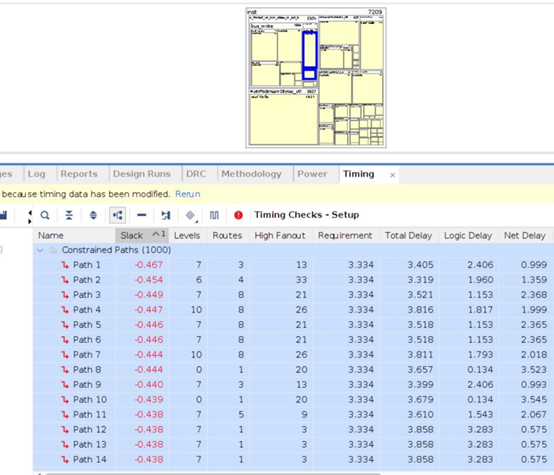

在 FPGA 設(shè)計(jì)進(jìn)程中,時(shí)序收斂無(wú)疑是一項(xiàng)艱巨的任務(wù)。低估這項(xiàng)任務(wù)的復(fù)雜性常常導(dǎo)致工作規(guī)劃面臨無(wú)休止的壓力。賽靈思提供了諸多工具,用于幫助縮短時(shí)序收斂所需時(shí)間,從而加速產(chǎn)品上市。本篇博文描述了一種方法,能夠有效減少時(shí)序路徑問(wèn)題分析所需工作量

2022-08-02 09:25:06 1049

1049

對(duì)于建立時(shí)間和保持時(shí)間本文就不再過(guò)多敘述,可參考【FPGA】幾種時(shí)序問(wèn)題的常見(jiàn)解決方法-------3,可以說(shuō)在數(shù)字高速信號(hào)處理中最基本的概念就是建立時(shí)間和保持時(shí)間,而我們要做的就是解決亞穩(wěn)態(tài)問(wèn)題和傳輸穩(wěn)定問(wèn)題。

2022-12-13 11:03:58 707

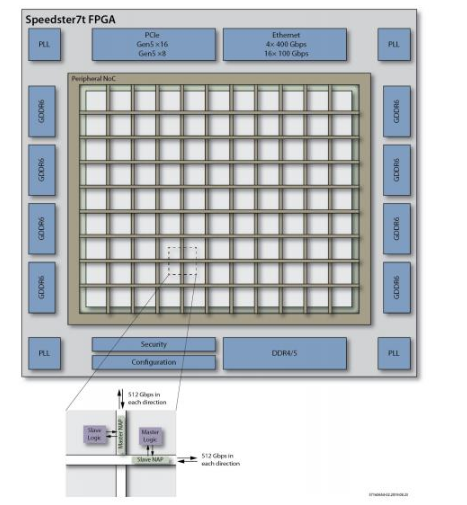

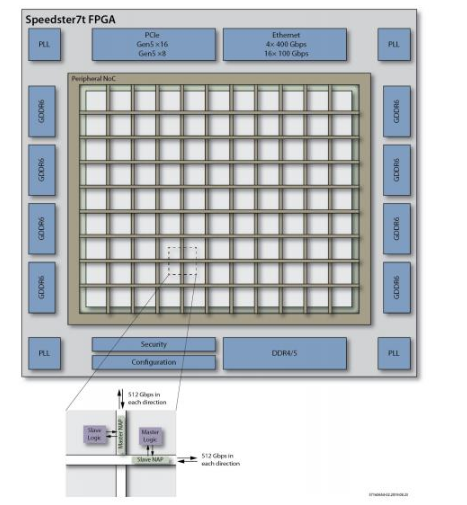

707 自從幾十年前首次推出FPGA 以來(lái),每種新架構(gòu)都繼續(xù)在采用按位(bit-wise)的布線(xiàn) 結(jié)構(gòu)。 雖然這種方法一直是成功的,但是隨著高速通信標(biāo)準(zhǔn)的興起,總是要求不斷增加片上總線(xiàn)位寬,以支持這些

2023-04-03 14:57:57 1149

1149

FPGA開(kāi)發(fā)過(guò)程中,離不開(kāi)時(shí)序約束,那么時(shí)序約束是什么?簡(jiǎn)單點(diǎn)說(shuō),FPGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿(mǎn)足建立和保持時(shí)間。

2023-06-26 14:42:10 1252

1252

FPGA時(shí)序不收斂,會(huì)出現(xiàn)很多隨機(jī)性問(wèn)題,上板測(cè)試大概率各種跑飛,而且不好調(diào)試定位原因,所以在上板測(cè)試前,先優(yōu)化時(shí)序,再上板。

2023-06-26 15:41:31 3800

3800

本文聊聊“RQS_CLOCK-12”時(shí)鐘設(shè)置建議以及它如何幫助達(dá)成時(shí)序收斂

2023-07-12 15:44:19 1194

1194

FPGA高級(jí)時(shí)序綜合教程

2023-08-07 16:07:55 9

9 電子發(fā)燒友網(wǎng)站提供《UltraFast設(shè)計(jì)方法時(shí)序收斂快捷參考指南(UG1292).pdf》資料免費(fèi)下載

2023-09-15 10:38:51 0

0 如何解決高速信號(hào)的手工布線(xiàn)和自動(dòng)布線(xiàn)之間的矛盾? 高速信號(hào)的手工布線(xiàn)和自動(dòng)布線(xiàn)之間存在矛盾主要是因?yàn)?b class="flag-6" style="color: red">高速信號(hào)傳輸需要考慮到許多影響因素,包括信號(hào)完整性、時(shí)序約束、電磁干擾等。手工布線(xiàn)和自動(dòng)布線(xiàn)在

2023-11-24 14:38:18 1340

1340 建立時(shí)間和保持時(shí)間是FPGA時(shí)序約束中兩個(gè)最基本的概念,同樣在芯片電路時(shí)序分析中也存在。

2024-08-06 11:40:18 2366

2366

電子發(fā)燒友網(wǎng)站提供《FPGA電源時(shí)序控制.pdf》資料免費(fèi)下載

2024-08-26 09:25:41 1

1 電子發(fā)燒友網(wǎng)站提供《高速ADC與FPGA的LVDS數(shù)據(jù)接口中避免時(shí)序誤差的設(shè)計(jì)考慮.pdf》資料免費(fèi)下載

2024-10-15 09:50:32 8

8

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論