本文通過對OpenCV中圖像類型和函數(shù)處理方法的介紹,通過設(shè)計實例描述在vivadoHLS中調(diào)用OpenCV庫函數(shù)實現(xiàn)圖像處理的幾個基本步驟,完成從OpenCV設(shè)計到RTL轉(zhuǎn)換綜合的開發(fā)流程。

開源計算機視覺 (OpenCV) 被廣泛用于開發(fā)計算機視覺應(yīng)用,它包含2500多個優(yōu)化的視頻函數(shù)的函數(shù)庫并且專門針對臺式機處理器和GPU進行優(yōu)化。OpenCV的用戶成千上萬,OpenCV的設(shè)計無需修改即可在 Zynq器件的ARM處理器上運行。但是利用OpenCV實現(xiàn)的高清處理經(jīng)常受外部存儲器的限制,尤其是存儲帶寬會成為性能瓶頸,存儲訪問也會限制功耗效率。使用VivadoHLS高級語言綜合工具,可以輕松實現(xiàn)OpenCV C++視頻處理設(shè)計到RTL代碼的轉(zhuǎn)換,輸出硬件加速器或者直接在FPGA上實現(xiàn)實時視頻處理功能。同時,Zynq All-programmable SOC是實現(xiàn)嵌入式計算機視覺應(yīng)用的極好方法,很好解決了在單一處理器上實現(xiàn)視頻處理性能低功耗高的限制,Zynq高性能可編程邏輯和嵌入式ARM內(nèi)核,是一款功耗優(yōu)化的集成式解決方案。

1 OpenCV中圖像IplImage, CvMat, Mat 類型的關(guān)系和VivadoHLS中圖像hls::Mat類型介紹

OpenCv中常見的與圖像操作有關(guān)的數(shù)據(jù)容器有Mat,cvMat和IplImage,這三種類型都可以代表和顯示圖像,但是,Mat類型側(cè)重于計算,數(shù)學性較高,openCV對Mat類型的計算也進行了優(yōu)化。而CvMat和IplImage類型更側(cè)重于“圖像”,opencv對其中的圖像操作(縮放、單通道提取、圖像閾值操作等)進行了優(yōu)化。在opencv2.0之前,opencv是完全用C實現(xiàn)的,但是,IplImage類型與CvMat類型的關(guān)系類似于面向?qū)ο笾械睦^承關(guān)系。實際上,CvMat之上還有一個更抽象的基類----CvArr,這在源代碼中會常見。

1.1 OpenCV中Mat類型:矩陣類型(Matrix)。

在openCV中,Mat是一個多維的密集數(shù)據(jù)數(shù)組。可以用來處理向量和矩陣、圖像、直方圖等等常見的多維數(shù)據(jù)。

Mat有3個重要的方法:

1、Mat mat = imread(const String* filename); 讀取圖像

2、imshow(const string frameName, InputArray mat); 顯示圖像

3、imwrite (const string& filename, InputArray img); 儲存圖像

Mat類型較CvMat與IplImage類型來說,有更強的矩陣運算能力,支持常見的矩陣運算。在計算密集型的應(yīng)用當中,將CvMat與IplImage類型轉(zhuǎn)化為Mat類型將大大減少計算時間花費。

1.2 OpenCV中CvMat類型與IplImage類型:“圖像”類型

在openCV中,Mat類型與CvMat和IplImage類型都可以代表和顯示圖像,但是,Mat類型側(cè)重于計算,數(shù)學性較高,openCV對Mat類型的計算也進行了優(yōu)化。而CvMat和IplImage類型更側(cè)重于“圖像”,openCV對其中的圖像操作(縮放、單通道提取、圖像閾值操作等)進行了優(yōu)化。

補充:IplImage由CvMat派生,而CvMat由CvArr派生即CvArr -》 CvMat -》 IplImage

CvArr用作函數(shù)的參數(shù),無論傳入的是CvMat或IplImage,內(nèi)部都是按CvMat處理。

在openCV中,沒有向量(vector)的數(shù)據(jù)結(jié)構(gòu)。任何時候,但我們要表示向量時,用矩陣數(shù)據(jù)表示即可。

但是,CvMat類型與我們在線性代數(shù)課程上學的向量概念相比,更抽象,比如CvMat的元素數(shù)據(jù)類型并不僅限于基礎(chǔ)數(shù)據(jù)類型,比如,下面創(chuàng)建一個二維數(shù)據(jù)矩陣:

CvMat* cvCreatMat(int rows ,int cols , int type);

這里的type可以是任意的預(yù)定義數(shù)據(jù)類型,比如RGB或者別的多通道數(shù)據(jù)。這樣我們便可以在一個CvMat矩陣上表示豐富多彩的圖像了。

1.3 OpenCV中IplImage類型

在OpenCV類型關(guān)系上,我們可以說IplImage類型繼承自CvMat類型,當然還包括其他的變量將之解析成圖像數(shù)據(jù)。

IplImage類型較之CvMat多了很多參數(shù),比如depth和nChannels。在普通的矩陣類型當中,通常深度和通道數(shù)被同時表示,如用32位表示RGB+Alpha.但是,在圖像處理中,我們往往將深度與通道數(shù)分開處理,這樣做是OpenCV對圖像表示的一種優(yōu)化方案。

IplImage的對圖像的另一種優(yōu)化是變量origin----原點。在計算機視覺處理上,一個重要的不便是對原點的定義不清楚,圖像來源,編碼格式,甚至操作系統(tǒng)都會對原地的選取產(chǎn)生影響。為了彌補這一點,openCV允許用戶定義自己的原點設(shè)置。取值0表示原點位于圖片左上角,1表示左下角。

1.4 VivadoHLS中圖像數(shù)據(jù)類型hls::Mat《》

VivadoHLS視頻處理函數(shù)庫使用hls::Mat《》數(shù)據(jù)類型,這種類型用于模型化視頻像素流處理,實質(zhì)等同于hls::steam《》流的類型,而不是OpenCV中在外部memory中存儲的matrix矩陣類型。因此,在HLS實現(xiàn)OpenCV的設(shè)計中,需要將輸入和輸出HLS可綜合的視頻設(shè)計接口,修改為Video stream接口,也就是采用HLS提供的video接口可綜合函數(shù),實現(xiàn)AXI4 video stream到VivadoHLS中hls::Mat《》類型的轉(zhuǎn)換。

2 使用VivadoHLS實現(xiàn)OpenCV到RTL代碼轉(zhuǎn)換的流程

2.1 OpenCV設(shè)計中的權(quán)衡

OpenCV圖像處理是基于存儲器幀緩存而構(gòu)建的,它總是假設(shè)視頻frame數(shù)據(jù)存放在外部DDR 存儲器中,因此,OpenCV對于訪問局部圖像性能較差,因為處理器的小容量高速緩存性能不足以完成這個任務(wù)。而且出于性能考慮,基于OpenCV設(shè)計的架構(gòu)比較復雜,功耗更高。在對分辨率或幀速率要求低,或者在更大的圖像中對需要的特征或區(qū)域進行處理是,OpenCV似乎足以滿足很多應(yīng)用的要求,但對于高分辨率高幀率實時處理的場景下,OpenCV很難滿足高性能和低功耗的需求。

基于視頻流的架構(gòu)能提供高性能和低功耗,鏈條化的圖像處理函數(shù)能減少外部存儲器訪問,針對視頻優(yōu)化的行緩存和窗口緩存比處理器高速緩存更簡單,更易于用FPGA部件,使用VivadoHLS中的數(shù)據(jù)流優(yōu)化來實現(xiàn)。

VivadoHLS對OpenCV的支持,不是指可以將OpenCV的函數(shù)庫直接綜合成RTL代碼,而是需要將代碼轉(zhuǎn)換為可綜合的代碼,這些可綜合的視頻庫稱為HLS視頻庫,由VivadoHLS提供。

OpenCV函數(shù)不能直接通過HLS進行綜合,因為OpenCV函數(shù)一般都包含動態(tài)的內(nèi)存分配、浮點以及假設(shè)圖像在外部存儲器中存放或者修改。

VivadoHLS視頻庫用于替換很多基本的 OpenCV函數(shù),它與OpenCV具有相似的接口和算法,主要針對在FPGA架構(gòu)中實現(xiàn)的圖像處理函數(shù),包含了專門面向FPGA的優(yōu)化,比如定點運算而非浮點運算(不必精確到比特位),片上的行緩存(line buffer)和窗口緩存(window buffer)。

2.2 VivadoHLS實現(xiàn)OpenCV設(shè)計流程介紹

使用VivadoHLS實現(xiàn)OpenCV的開發(fā),主要的三個步驟如下:

在計算機上開發(fā)OpenCV應(yīng)用,由于是開源的設(shè)計,采用C++的編譯器對其進行編譯,仿真和debug,最后產(chǎn)生可執(zhí)行文件。這些設(shè)計無需修改即可在 ARM內(nèi)核上運行OpenCV應(yīng)用。

使用I/O函數(shù)抽取FPGA實現(xiàn)的部分,并且使用可綜合的VivadoHLS Video庫函數(shù)代碼代替OpenCV函數(shù)的調(diào)用。

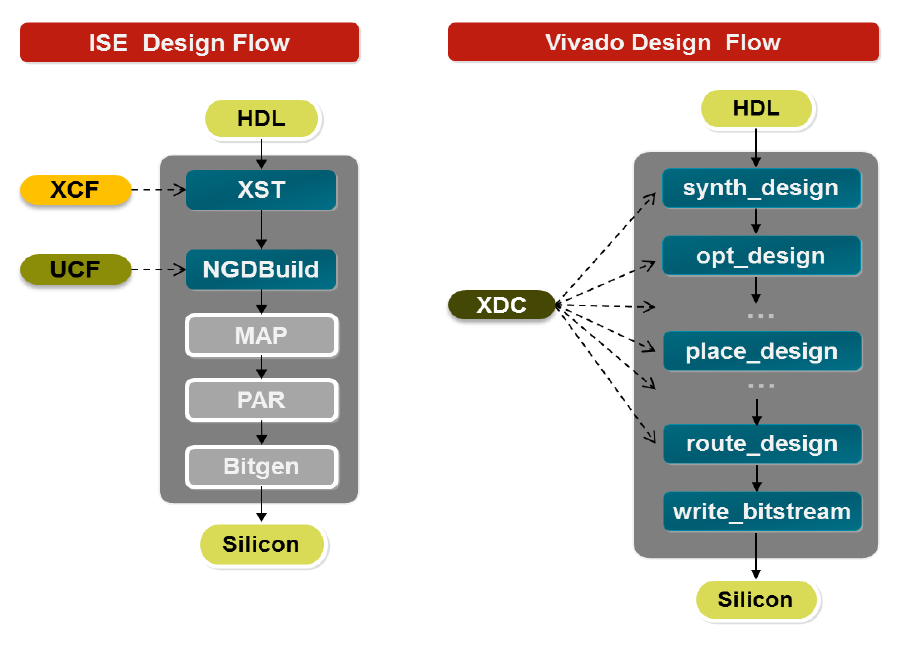

運行HLS生成RTL代碼,在vivadoHLS工程中啟動co-sim,重用openCV的測試激勵驗證產(chǎn)生的RTL代碼。在ISE或者Vivado開發(fā)環(huán)境中做RTL的集成和SOC/FPGA實現(xiàn)。

2.2.1 VivadoHLS視頻庫函數(shù)

HLS視頻庫是包含在hls命名空間內(nèi)的C++代碼。#include “hls_video.h”

與OpenCV等具有相似的接口和等效的行為,例如:

OpenCV庫:cvScale(src, dst, scale, shift);

HLS視頻庫:hls:cale《。。。》(src, dst, scale, shift);

一些構(gòu)造函數(shù)具有類似的或替代性的模板參數(shù),例如:

OpenCV庫:cv::Mat mat(rows, cols, CV_8UC3);

HLS視頻庫:hls::Mat mat(rows, cols);

ROWS和COLS指定處理的最大圖像尺寸

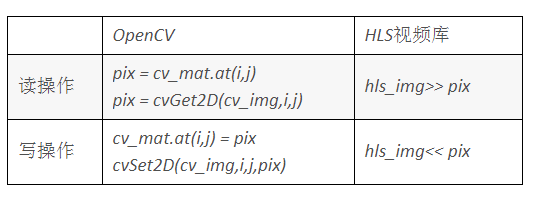

表2.2.1 VivadoHLS視頻處理函數(shù)庫

2.2.2 VivadHLS實現(xiàn)OpenCV設(shè)計的局限性

首先,必須用HLS視頻庫函數(shù)代替OpenCV調(diào)用。

其次,不支持OpenCV通過指針訪問幀緩存,可以在HLS中使用VDMA和 AXI Stream adpater函數(shù)代替。

再者,不支持OpenCV的隨機訪問。HLS對于讀取超過一次的數(shù)據(jù)必須進行復制,更多的例子可以參見見hls:uplicate()函數(shù)。

最后,不支持OpenCVS的In-place更新,比如 cvRectangle (img, point1, point2)。

下面表格2.2.2列舉了OpenCV中隨機訪問一幀圖像處理對應(yīng)HLS視頻庫的實現(xiàn)方法。

OpenCVHLS視頻庫

讀操作pix = cv_mat.at(i,j)

pix = cvGet2D(cv_img,i,j)hls_img 》》 pix

寫操作cv_mat.at(i,j) = pix

cvSet2D(cv_img,i,j,pix)hls_img 《《 pix

表 2.2.2 OpenCV和HLS中對一幀圖像像素訪問對應(yīng)方法

2.3 用HLS實現(xiàn)OpenCV應(yīng)用的實例(快速角點濾波器image_filter)

我們通過快速角點的例子,說明通常用VivadoHLS實現(xiàn)OpenCV的流程。首先,開發(fā)基于OpenCV的快速角點算法設(shè)計,并使用基于OpenCV的測試激勵仿真驗證這個算法。接著,建立基于視頻數(shù)據(jù)流鏈的OpenCV處理算法,改寫前面直覺的OpenCV的通常設(shè)計,這樣的改寫是為了與HLS視頻庫處理機制相同,方便后面步驟的函數(shù)替換。最后,將改寫的OpenCV設(shè)計中的函數(shù),替換為HLS提供的相應(yīng)功能的視頻函數(shù),并用VivadoHLS綜合,最后在Xilinx開發(fā)環(huán)境下實現(xiàn)。當然,這些可綜合代碼也可在處理器或ARM上運行。

2.3.1 設(shè)計基于OpenCV的視頻濾波器設(shè)計和測試激勵

在這個例子中,首先設(shè)計開發(fā)完全調(diào)用OpenCV庫函數(shù)的快速角點濾波器設(shè)計opencv_image_filter.cpp和這個濾波器的測試激勵opencv_image_filter_tb.cpp,測試激勵用于仿真驗證opencv_image_filter算法功能。算法和測試激勵設(shè)計代碼如下:

void opencv_image_filter(IplImage* src, IplImage* dst)

{

IplImage* gray = cvCreateImage( cvGetSize(src), 8, 1 );

std::vector keypoints;

cv::Mat gray_mat(gray,0);

cvCvtColor( src, gray, CV_BGR2GRAY );

cv::FAST( gray_mat, keypoints, 20, true);

cvCopy( src,dst);

for (int i=0;i

{

cvRectangle(dst, cvPoint(keypoints[i].pt.x-1,keypoints[i].pt.y-1),

cvPoint(keypoints[i].pt.x+1,keypoints[i].pt.y+1), cvScalar(255,0,0),CV_FILLED);

}

cvReleaseImage( &gray );

}

例子2.3.1.1 通常的OpenCV視頻處理代碼opencv_image_filter.cpp

int main (int argc, char** argv) {

IplImage* src=cvLoadImage(INPUT_IMAGE);

IplImage* dst = cvCreateImage(cvGetSize(src), src-》depth, src-》nChannels);

opencv_image_filter(src, dst);

cvSaveImage(OUTPUT_IMAGE_GOLDEN, dst);

cvReleaseImage(&src);

cvReleaseImage(&dst);

return 0;

}

例子2.3.1.2 OpenCV視頻處理測試激勵代碼opencv_image_filter_tb.cpp

上面的例子是直接調(diào)用OpenCV在處理器上軟件應(yīng)用實現(xiàn)的例子,可以看到在算法設(shè)計中直接調(diào)用opencV庫函數(shù),測試激勵讀入圖像,經(jīng)過濾波器處理輸出的圖像保存分析。可以看到,算法的處理基于IPIimage類型,輸入和輸出圖像都使用此類型。

2.3.2 使用IO函數(shù)和Vivado HLS視頻庫替換OpenCV函數(shù)庫

需要特別說明的是,xilinx通常使用的視頻處理模塊都是基于axi4 streaming協(xié)議進行不同模式見像素數(shù)據(jù)的交互,也就是我們所說的AXI4 video接口協(xié)議格式。為了和xilinx視頻庫接口協(xié)議統(tǒng)一,VivadoHLS提供了視頻接口函數(shù)庫,用于從OpenCV程序中抽取需要進行RTL綜合轉(zhuǎn)換的頂層函數(shù),并把這些可綜合的代碼和OpenCV不可綜合轉(zhuǎn)換的代碼進行隔離。然后,對需要綜合轉(zhuǎn)換為RTL代碼的OpenCV函數(shù),用xilinx VivadoHLS提供相應(yīng)功能的可綜合video函數(shù)進行替換。最后在C/C++編譯環(huán)境下仿真驗證OpenCV代碼和替換video函數(shù)后功能的一致,并在VivadoHLS開發(fā)環(huán)境中做代碼綜合和產(chǎn)生RTL代碼的co-sim混合仿真驗證。

VivadoHLS可綜合的視頻接口函數(shù):

Hls::AXIvideo2Mat 轉(zhuǎn)換AXI4 video stream到hls::Mat表示格式

Hls::Mat2AXIvideo 轉(zhuǎn)換hls::Mat數(shù)據(jù)格式到AXI4 video stream

首先,我們對2.3.1中OpenCV的設(shè)計進行改寫,改寫的代碼還是完全基于OpenCV的函數(shù),目的是為了對視頻的處理機制基于視頻流的方式,與VivadoHLS視頻庫提供函數(shù)的處理機制一致。下面是OpenCV設(shè)計的另一種寫法:

void opencv_image_filter(IplImage* src, IplImage* dst)

{

IplImage* gray = cvCreateImage( cvGetSize(src), 8, 1 );

IplImage* mask = cvCreateImage( cvGetSize(src), 8, 1 );

IplImage* dmask = cvCreateImage( cvGetSize(src), 8, 1 );

std::vector keypoints;

cv::Mat gray_mat(gray,0);

cvCvtColor(src, gray, CV_BGR2GRAY );

cv::FAST(gray_mat, keypoints, 20, true);

GenMask(mask, keypoints);

cvDilate(mask,dmask);

cvCopy(src,dst);

PrintMask(dst,dmask,cvScalar(255,0,0));

cvReleaseImage( &mask );

cvReleaseImage( &dmask );

cvReleaseImage( &gray );

}

例子2.3.2.1另一種OpenCV設(shè)計應(yīng)用opencv_image_filter.cpp

其次,使用Vivado HLS視頻庫替代標準OpenCV函數(shù),并使用可綜合的視頻接口函數(shù),采用video stream的方式交互視頻數(shù)據(jù)。用于FPGA的硬件可綜合模塊由VivadoHLS視頻庫函數(shù)與接口組成,我們用hls命名空間中的相似函數(shù)代替OpenCV函數(shù),增加接口函數(shù)構(gòu)建AXI4 stream類型的接口。

void image_filter(AXI_STREAM& input, AXI_STREAM& output, int rows, int cols)

{

//Create AXI streaming interfaces for the core

#pragma HLS RESOURCE variable=input core=AXIS metadata=“-bus_bundle INPUT_STREAM”

#pragma HLS RESOURCE variable=output core=AXIS metadata=“-bus_bundle OUTPUT_STREAM”

#pragma HLS RESOURCE core=AXI_SLAVE variable=rows metadata=“-bus_bundle CONTROL_BUS”

#pragma HLS RESOURCE core=AXI_SLAVE variable=cols metadata=“-bus_bundle CONTROL_BUS”

#pragma HLS RESOURCE core=AXI_SLAVE variable=return metadata=“-bus_bundle CONTROL_BUS”

#pragma HLS interface ap_stable port=rows

#pragma HLS interface ap_stable port=cols

hls::Mat _src(rows,cols);

hls::Mat _dst(rows,cols);

#pragma HLS dataflow

hls::AXIvideo2Mat(input, _src);

hls::Mat src0(rows,cols);

hls::Mat src1(rows,cols);

#pragma HLS stream depth=20000 variable=src1.data_stream

hls::Mat mask(rows,cols);

hls::Mat dmask(rows,cols);

hls:calar《3,unsigned char》 color(255,0,0);

hls:uplicate(_src,src0,src1);

hls::Mat gray(rows,cols);

hls::CvtColor(src0,gray);

hls::FASTX(gray,mask,20,true);

hls:ilate(mask,dmask);

hls:aintMask(src1,dmask,_dst,color);

hls::Mat2AXIvideo(_dst, output);

}

例子2.3.2.2 采用VivadoHLS視頻庫替換后可綜合的設(shè)計opencv_image_filter.cpp

最后,在vivadoHLS開發(fā)環(huán)境下綜合例子2.3.2.2的設(shè)計,產(chǎn)生RTL代碼并重用OpenCV的測試激勵驗證RTL代碼功能。

3 VHLS實現(xiàn)OpenCV設(shè)計流程總結(jié)

通過上面章節(jié)介紹以及在vivadoHLS工具中實現(xiàn)opencV設(shè)計的例子可以看出,OpenCV函數(shù)可實現(xiàn)計算機視覺算法的快速原型設(shè)計,并使用VivadoHLS工具轉(zhuǎn)換為RTL代碼在FPGA或者Zynq SOC上實現(xiàn)高分辨率高幀率的實時視頻處理。計算機視覺應(yīng)用與生俱來的異構(gòu)特性,使其需要軟硬件相結(jié)合的實現(xiàn)方案。Vivado HLS視頻庫能加快OpenCV函數(shù)向FPGA可編程架構(gòu)的映射。

電子發(fā)燒友App

電子發(fā)燒友App

評論