目前大多數(shù)儀器采用封閉式FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)和固定的固件實(shí)現(xiàn)儀器的功能。如果你曾見(jiàn)過(guò)示波器的拆解,你也許見(jiàn)過(guò)里面的FPGA。FPGA可以增加測(cè)試儀器的處理能力,如果你曾使用過(guò)儀器的開(kāi)放式FPGA,你就會(huì)知道可以將自定義的測(cè)試功能編程進(jìn)儀器中。

儀器供應(yīng)商早就了解FPGA的好處,并且一直在充分發(fā)揮FPGA獨(dú)特的處理能力優(yōu)勢(shì)來(lái)豐富的功能,比如:儀器

● 能夠在示波器上完成預(yù)觸發(fā)捕獲

● 能夠利用信號(hào)處理功能在矢量信號(hào)分析儀上產(chǎn)生I和Q數(shù)據(jù)

● 能夠在高速數(shù)字儀器上實(shí)時(shí)進(jìn)行圖案發(fā)生和矢量比較

測(cè)試設(shè)備制造商現(xiàn)在開(kāi)始向用戶開(kāi)放FPGA以提供更多特殊應(yīng)用的優(yōu)化。為了幫助理解為何這是一個(gè)好的轉(zhuǎn)變,下面列出了在測(cè)試應(yīng)用中使用FPGA的一些關(guān)鍵特性:

● 確定性,實(shí)時(shí)處理

● 真正并行的執(zhí)行

● 可重配置

● 低延時(shí)

更進(jìn)一步講,利用開(kāi)放式FPGA可以實(shí)現(xiàn)哪些以前不能實(shí)現(xiàn)的功能呢?為了描述這些可能性,下面將介紹一些利用開(kāi)放式FPGA的常見(jiàn)測(cè)試應(yīng)用。

測(cè)試系統(tǒng)加速

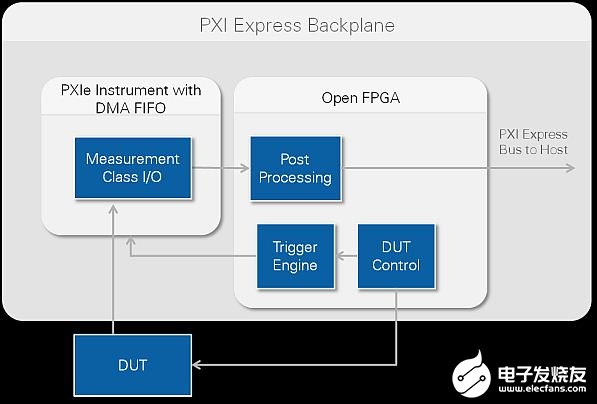

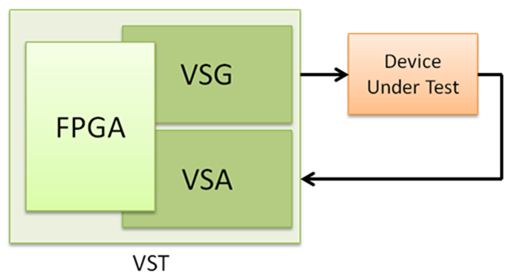

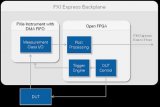

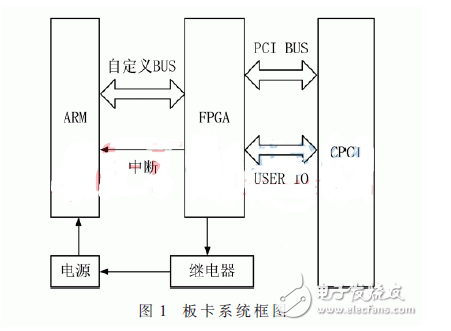

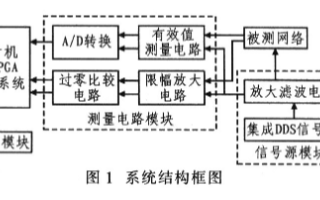

在大批量生產(chǎn)線的最終產(chǎn)品測(cè)試中,每一秒的測(cè)試時(shí)間都很寶貴。當(dāng)產(chǎn)品測(cè)試速度與生產(chǎn)速度相匹配時(shí),生產(chǎn)線的效率就是最高的。當(dāng)兩者速度不匹配時(shí),就必須采用創(chuàng)新的技術(shù)來(lái)縮短測(cè)試時(shí)間。傳統(tǒng)方法需要使用多臺(tái)分開(kāi)的臺(tái)式儀器,它們通過(guò)以太網(wǎng)、USB或GPIB連接到一臺(tái)PC主機(jī)。這種測(cè)試的速度相對(duì)較慢,因?yàn)榇郎y(cè)設(shè)備的控制、測(cè)量以及通過(guò)數(shù)據(jù)總線的處理是分開(kāi)進(jìn)行的。另外一種方法是使用開(kāi)放式FPGA來(lái)加速這個(gè)過(guò)程,如圖1所示。

圖1:在測(cè)試儀器中,開(kāi)放式FPGA可以增加諸如觸發(fā)和后處理等功能。

與使用外部通信總線不同,F(xiàn)PGA可以使用高速總線(如PXIe)連接儀器,并通過(guò)其配置端口(如I2C、SPI或另外的控制總線)連接待測(cè)設(shè)備(DUT)。這種應(yīng)用中的FPGA可以控制待測(cè)設(shè)備,觸發(fā)其它儀器開(kāi)始捕獲樣本,甚至將這些樣本處理成對(duì)主機(jī)來(lái)說(shuō)有意義的結(jié)果。

低時(shí)延是加速這類(lèi)應(yīng)用的一個(gè)關(guān)鍵因素。FPGA沒(méi)有操作系統(tǒng),但所有的邏輯都是用硬件實(shí)現(xiàn),并且這些硬件工作的時(shí)鐘速率很高。這意味著響應(yīng)只需花一個(gè)時(shí)鐘周期捕獲、一個(gè)時(shí)鐘周期處理和一個(gè)時(shí)鐘周期輸出結(jié)果。當(dāng)時(shí)鐘速率為200MHz(時(shí)鐘周期為4ns)時(shí),完整的響應(yīng)時(shí)間只需12ns。由于FPGA的確定性特點(diǎn),12ns的響應(yīng)時(shí)間不是只有一次,而是每次都是。因此FPGA不僅可以避免與使用主機(jī)有關(guān)的延時(shí),而且能夠最大限度地減小主機(jī)處理時(shí)的非確定性延時(shí)。

協(xié)議的處理

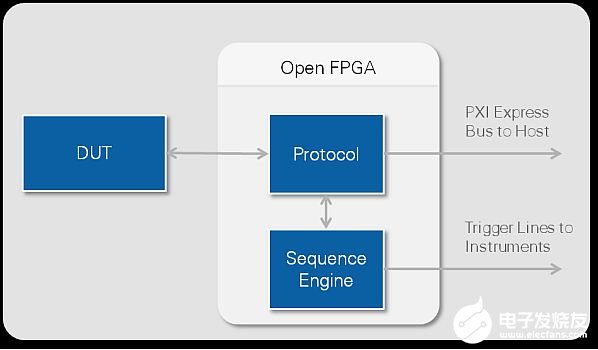

今天,并不是所有數(shù)字和MEMS設(shè)備都能用已知結(jié)果矢量進(jìn)行測(cè)試。就拿脈沖密度麥克風(fēng)(PDM)來(lái)說(shuō),如果給它一個(gè)激勵(lì)信號(hào),你不能期望每次測(cè)試得到的比特流是完全相同的,這是因?yàn)镻DM是模擬設(shè)備。為了從這些類(lèi)型的待測(cè)設(shè)備獲得有意義的結(jié)果,在比較結(jié)果之前你首先需要用其特定的協(xié)議對(duì)數(shù)字流進(jìn)行解碼。借助開(kāi)放式FPGA,你可以在FPGA上配置你的測(cè)試系統(tǒng)來(lái)實(shí)現(xiàn)PDM協(xié)議,不必再傳至CPU進(jìn)行解釋。進(jìn)一步拓展這個(gè)概念,今天你可以配置這個(gè)FPGA實(shí)現(xiàn)PDM協(xié)議,明天你又可以重新配置同樣這個(gè)FPGA實(shí)現(xiàn)不同的協(xié)議,比如用于測(cè)試數(shù)字溫度傳感器、加速度計(jì)或MEMS設(shè)備的協(xié)議。

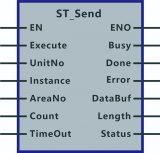

在圖2中,協(xié)議不是在CPU上實(shí)現(xiàn),而是在FPGA上實(shí)現(xiàn)。正因?yàn)榇耍瑴y(cè)試系統(tǒng)現(xiàn)在自身就可以支持快速握手腳本,適應(yīng)精確等待周期等協(xié)議行為,并根據(jù)通信內(nèi)容做出決策。這種方法不僅能讓你從待測(cè)設(shè)備接收更高層數(shù)據(jù),比如在PDM麥克風(fēng)場(chǎng)合中解碼的模擬數(shù)據(jù),而且允許你用更高層命令編寫(xiě)測(cè)試腳本。

圖2:FPGA可以用來(lái)處理協(xié)議,知曉總線使用的協(xié)議內(nèi)容。

閉環(huán)測(cè)試:功放

在無(wú)線通信系統(tǒng)中,信號(hào)在發(fā)往天線之前需要用功放IC增加信號(hào)的強(qiáng)度。功放的性能規(guī)格通常是在特定的輸出功率電平點(diǎn)定義的。因此當(dāng)功放工作在這個(gè)輸出功率電平時(shí)對(duì)它們進(jìn)行測(cè)試就顯得非常重要。然而,功放的增益一般只是粗略的知道(比如±3dB),而且在器件工作范圍內(nèi)是非線性的。你越接近最大輸出功率,增益就越低。基于這些理由,在開(kāi)展任何性能測(cè)試之間你必須首先“調(diào)測(cè)”放大器的輸出。調(diào)測(cè)輸出經(jīng)常被稱(chēng)為功率電平調(diào)整或功率伺服調(diào)整。基本原理是調(diào)整放大器的輸入功率,直到你測(cè)得正確的輸出功率。

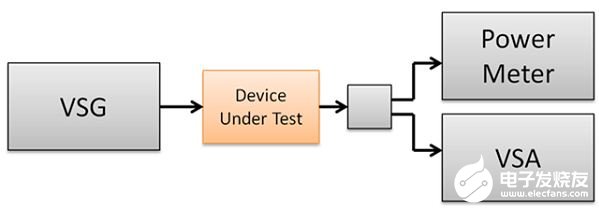

測(cè)量功放的傳統(tǒng)測(cè)試裝置見(jiàn)圖3所示。矢量信號(hào)發(fā)生器(VSG)產(chǎn)生一個(gè)激勵(lì)波形給待測(cè)設(shè)備。功率計(jì)確保待測(cè)設(shè)備輸出正確的功率電平。最后由矢量信號(hào)分析義(VSA)測(cè)量待測(cè)設(shè)備的性能——如誤差矢量幅度(EVM)或相鄰?fù)ǖ拦β剩?a target="_blank">ACP)。實(shí)際操作中需要針對(duì)各種中心頻率和功率電平重復(fù)這些測(cè)量。

圖3:用于測(cè)量功放輸出的傳統(tǒng)測(cè)試裝置包含有矢量信號(hào)發(fā)生器、矢量信號(hào)分析儀和功率計(jì)。

必須針對(duì)每個(gè)想要測(cè)試的中心頻率和功率電平調(diào)測(cè)功放的輸出功率。調(diào)測(cè)過(guò)程一般遵循以下這些步驟:

● 根據(jù)估計(jì)的待測(cè)設(shè)備增益選取一個(gè)起始的矢量信號(hào)發(fā)生器功率電平

● 設(shè)置矢量信號(hào)發(fā)生器的功率電平

● 等待矢量信號(hào)發(fā)生器穩(wěn)定工作

● 等待待測(cè)設(shè)備穩(wěn)定工作

● 用功率計(jì)進(jìn)行測(cè)量

如果功率在正確的范圍內(nèi),退出。如果不在范圍內(nèi),計(jì)算新的矢量信號(hào)發(fā)生器功率電平,回到步驟2重新開(kāi)始

整個(gè)調(diào)測(cè)過(guò)程可能要花幾百毫秒到幾秒的時(shí)間,具體取決于待測(cè)設(shè)備類(lèi)型、要求的精度以及使用的儀器。調(diào)測(cè)過(guò)程完成后就可以用矢量信號(hào)分析儀開(kāi)展性能測(cè)量了。

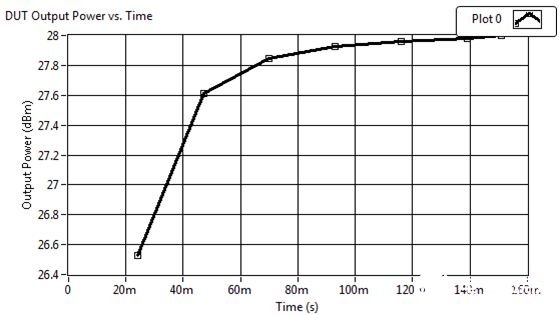

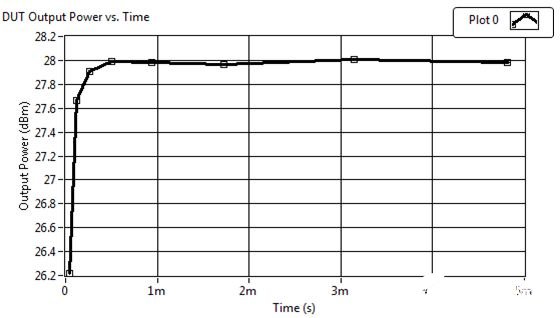

圖4顯示了使用傳統(tǒng)方法將待測(cè)設(shè)備樣品輸出調(diào)整到平均輸出功率為28dBm的過(guò)程。如果功率放大器的增益是線性的,并且符合數(shù)據(jù)手冊(cè)中規(guī)定的典型增益,那么矢量信號(hào)發(fā)生器產(chǎn)生的第一個(gè)點(diǎn)就將產(chǎn)生28dBm的輸出功率。然而放大器的實(shí)測(cè)輸出功率只有26.5dBm,這就表明了功放典型增益指標(biāo)的不精確性。隨后調(diào)整矢量信號(hào)發(fā)生器的輸出功率,由矢量信號(hào)分析儀捕獲另外一個(gè)輸出功率點(diǎn)。這次平均功率是27.6dBm,從中可以看出放大器增益響應(yīng)的壓縮過(guò)程。總之花了7步、大約150ms的時(shí)間才使放大器的輸出達(dá)到想要的功率值。在這個(gè)例子中,待測(cè)設(shè)備的穩(wěn)定時(shí)間是每步10ms。但不同待測(cè)設(shè)備的穩(wěn)定時(shí)間是不同的,它將顯著影響總的調(diào)測(cè)時(shí)間。

圖4:傳統(tǒng)的功放輸出調(diào)測(cè)方法表明功率電平是漸次增加的。

矢量信號(hào)收發(fā)器(VST)是將矢量信號(hào)發(fā)生器、矢量信號(hào)分析儀和FPGA整合在一起的一種儀器。這種組合可以讓你將功率調(diào)測(cè)算法轉(zhuǎn)移到硬件中實(shí)現(xiàn)。即使沒(méi)有圖5中的功率計(jì),你通常也可以執(zhí)行系統(tǒng)校準(zhǔn)步驟將功率計(jì)精度轉(zhuǎn)嫁給矢量信號(hào)分析儀。

圖5:矢量信號(hào)收發(fā)器將信號(hào)發(fā)生器、信號(hào)分析儀和FPGA整合在一起。

調(diào)測(cè)功放輸出功率的步驟與傳統(tǒng)方法是類(lèi)似的,只不過(guò)調(diào)測(cè)環(huán)路在開(kāi)放式FPGA中執(zhí)行。在FPGA中執(zhí)行環(huán)路可以顯著縮短每次調(diào)整所需的時(shí)間。

通過(guò)使用開(kāi)放式FPGA和硬件并在FPGA上實(shí)現(xiàn)控制環(huán)路,調(diào)測(cè)待測(cè)設(shè)備輸出功率的時(shí)間將遠(yuǎn)遠(yuǎn)小于在主機(jī)電腦上執(zhí)行控制環(huán)路的時(shí)間。對(duì)于本例中的待測(cè)設(shè)備來(lái)說(shuō),調(diào)測(cè)過(guò)程只用了5ms,而傳統(tǒng)方法需要150ms。需要注意的是,基于硬件的方法所需的步驟數(shù)比傳統(tǒng)方法多一步。但調(diào)測(cè)過(guò)程所需的總時(shí)間卻明顯減少。與圖4相比,圖6中的前幾個(gè)步驟完成得很快(平均時(shí)間較短),然后點(diǎn)的間隔越來(lái)越大,因?yàn)檎{(diào)測(cè)環(huán)路正在收斂。

圖6:使用基于硬件的調(diào)測(cè)方法后,功率電平上升的時(shí)間要短于傳統(tǒng)方法。

信號(hào)處理

用戶可編程FPGA最有用的應(yīng)用之一是在儀器上減少必須傳回主機(jī)進(jìn)行后處理的數(shù)據(jù)量,從而釋放通信總線用于其它數(shù)據(jù)傳輸,同時(shí)減少CPU的負(fù)擔(dān)。用于這方面的常見(jiàn)方法包括復(fù)雜觸發(fā)、濾波、峰值檢測(cè)或?qū)Σ东@的數(shù)據(jù)集執(zhí)行快速傅里葉變換(FFT)。

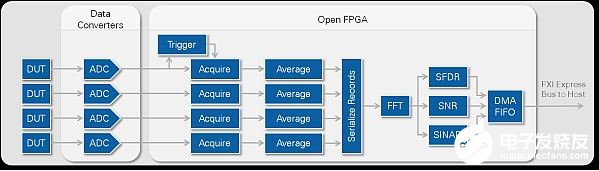

例如在圖7中你可以看到有4個(gè)待測(cè)設(shè)備需要并行測(cè)試的應(yīng)用。模數(shù)轉(zhuǎn)換器(ADC)將樣本傳送給FPGA,但直到定制觸發(fā)器啟動(dòng)捕獲命令后數(shù)據(jù)才被捕獲。在捕獲數(shù)據(jù)時(shí),F(xiàn)PGA會(huì)實(shí)時(shí)平均測(cè)量結(jié)果,然后將它們連續(xù)進(jìn)行記錄。然后在測(cè)量無(wú)雜散動(dòng)態(tài)范圍(SFDR)、信噪比(SNR)和信號(hào)噪聲與失真比(SINAD)之前對(duì)記錄進(jìn)行快速傅里葉變換。這些結(jié)果只是來(lái)自ADC的的輸入信號(hào)數(shù)據(jù)的一部分,接下來(lái)將通過(guò)直接存儲(chǔ)器訪問(wèn)先入先出緩沖機(jī)制(DMA FIFO)上傳給主機(jī)。

圖7:開(kāi)放式FPGA可以幫助你捕獲數(shù)據(jù)、平均數(shù)據(jù)以消除噪聲、將并行數(shù)據(jù)變?yōu)榇袛?shù)據(jù),然后執(zhí)行數(shù)學(xué)、FFT和濾波器算法。

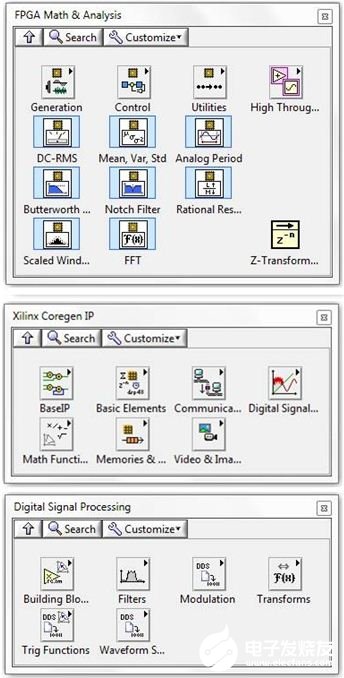

作為DSP中的一種基本功能,快速傅里葉變換被廣泛用于許多測(cè)試應(yīng)用。由FPGA實(shí)現(xiàn)這個(gè)功能可以為許多測(cè)試應(yīng)用增添許多功能,比如頻域觸發(fā)器、數(shù)據(jù)精簡(jiǎn)、基于頻率的閉環(huán)控制和圖像處理等。圖8顯示了如何在上例中使用LabVIEW FPGA實(shí)現(xiàn)快速傅里葉變換。

圖8:前述例子中的這個(gè)代碼顯示了快速傅里葉變換是在開(kāi)放式FPGA的何處執(zhí)行的。

雖然本文只是提及了很少幾個(gè)可以FPGA上實(shí)現(xiàn)的令人激動(dòng)的數(shù)字信號(hào)處理功能,但實(shí)際上還有許多其它功能可以用來(lái)擴(kuò)展FPGA在測(cè)試應(yīng)用中可以實(shí)現(xiàn)的能力。這類(lèi)處理功能可以在許多開(kāi)放式FPGA上實(shí)現(xiàn),圖9顯示了在國(guó)家儀器(NI)公司的硬件上可以通過(guò)LabVIEW FPGA實(shí)現(xiàn)的一些功能類(lèi)型。

圖9:在FPGA上可以實(shí)現(xiàn)的數(shù)字信號(hào)處理功能包括數(shù)學(xué)、濾波、三角函數(shù)和視頻處理等。

隨著開(kāi)放式FPGA在整個(gè)測(cè)試與測(cè)量行業(yè)內(nèi)逐漸流行起來(lái),你將看到只有固定功能的儀器越來(lái)越少。相反,更多的儀器將變得可軟件定義,與移動(dòng)設(shè)備行業(yè)中引入“應(yīng)用(app)”所經(jīng)歷的變革一樣。測(cè)試應(yīng)用不再受制于測(cè)試供應(yīng)商開(kāi)發(fā)的軟件能力。它們將只受限于當(dāng)時(shí)的硬件水平以及使用儀器的工程師的想像力。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論