本方案利用FPGA實(shí)現(xiàn)了巴特沃茲IIR數(shù)字帶通濾波器,并給出較為詳細(xì)的方案設(shè)計過程。實(shí)驗(yàn)結(jié)果證明了所設(shè)計的濾波器完全滿足預(yù)定設(shè)計要求,從而也證實(shí)了本方案的有效性、可行性。

2014-02-13 10:58:32 7689

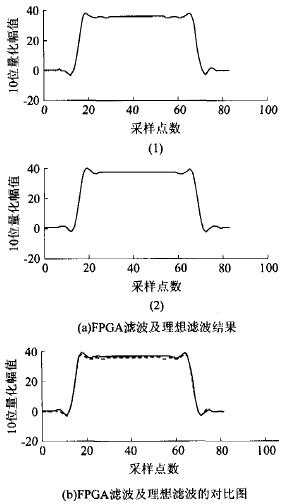

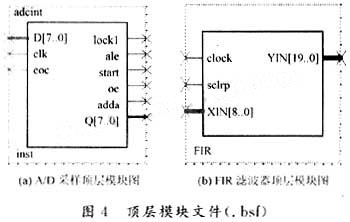

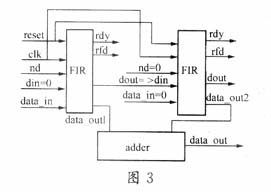

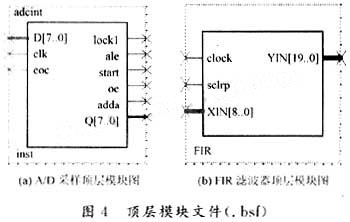

7689 本文簡要介紹了FIR數(shù)字濾波器的結(jié)構(gòu)特點(diǎn)和基本原理,提出基于FPGA和DSP Builder的FIR數(shù)字濾波器的基本設(shè)計流程和實(shí)現(xiàn)方案。##FIR 數(shù)字濾波器的詳細(xì)設(shè)計。

2014-07-24 15:30:05 9476

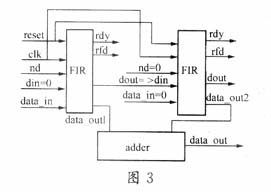

9476

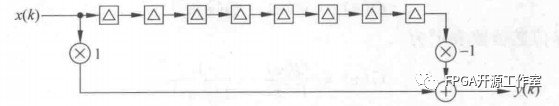

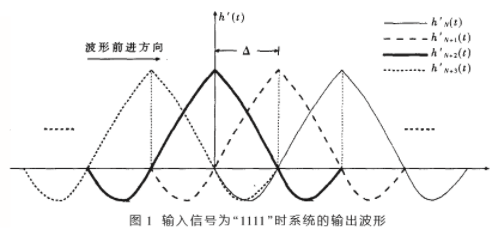

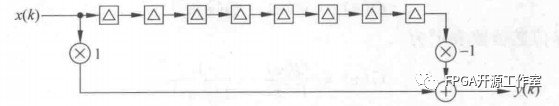

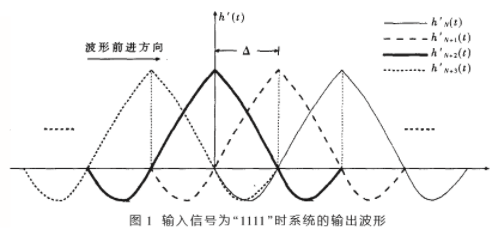

sample rate convert 和 down sample rate convert 的FPGA實(shí)現(xiàn)打下基礎(chǔ)。 1 梳狀濾波器 圖1 梳狀濾波器結(jié)構(gòu) 梳狀濾波器的兩端為1和-1的權(quán)值,具有簡單

2020-11-21 09:57:00 6749

6749

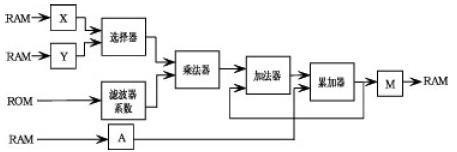

fpga實(shí)現(xiàn)濾波器fpga實(shí)現(xiàn)濾波器在利用FPGA實(shí)現(xiàn)數(shù)字信號處理方面,分布式算法發(fā)揮著關(guān)鍵作用,與傳統(tǒng)的乘加結(jié)構(gòu)相比,具有并行處理的高效性特點(diǎn)。本文研究了一種16階FIR濾波器的FPGA設(shè)計方法

2012-08-12 11:50:16

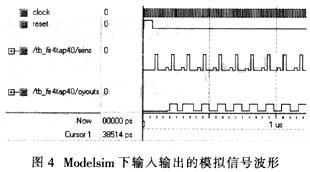

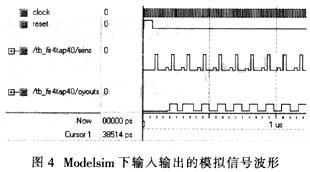

。本文研究了一種16階FIR濾波器的FPGA設(shè)計方法,采用Verilog HDI語言描述設(shè)計文件,在Xilinx ISE 7.1i及ModelSim SE 6.1b平臺上進(jìn)行了實(shí)驗(yàn)仿真及時序分析,并探討了實(shí)際工程中硬件資源利用率及運(yùn)算速度等問題。

2012-08-11 18:27:41

診斷儀對超聲信號進(jìn)行動態(tài)濾波。動態(tài)濾波包含模擬動態(tài)濾波和數(shù)字動態(tài)濾波。模擬動態(tài)濾波器要改變器件的參數(shù),從而達(dá)到改變通頻帶中心頻率的效果,方法簡易,效果很好。同時,控制信號是來自FPGA輸送出的數(shù)字信號,經(jīng)D/A轉(zhuǎn)換所得,采用FPGA實(shí)現(xiàn)控制信號,實(shí)現(xiàn)了很高的精度,達(dá)到了預(yù)想的效果。

2019-10-17 07:34:05

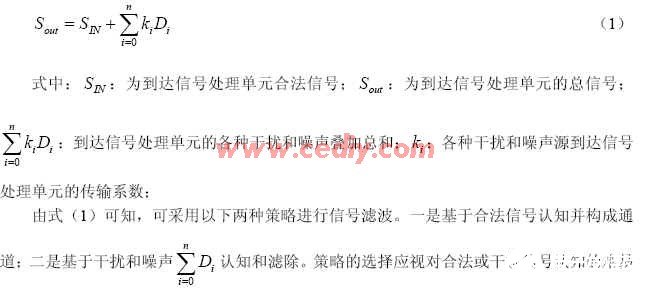

字技術(shù)迅速發(fā)展以后,相關(guān)濾波也經(jīng)常利用A/D板對信號采樣后,在計算機(jī)中實(shí)現(xiàn),成為數(shù)字濾波的一種形式。本文設(shè)計了一種實(shí)現(xiàn)相關(guān)濾波的方法,這是相關(guān)分析在測試技術(shù)中的一個典型應(yīng)用。圖1所示為相關(guān)濾波器的典型框圖

2019-05-06 09:26:39

CIC抽取濾波器MATLAB仿真和FPGA實(shí)現(xiàn)(1)設(shè)計理想濾波器目標(biāo):1、濾波器在有效頻段內(nèi)紋波滿足設(shè)計要求。2、抽取或內(nèi)插處理后在有效頻段內(nèi)不產(chǎn)生混疊。3、濾波器實(shí)現(xiàn)簡單,需要資源較少。這個

2021-08-17 08:27:40

FIR濾波器的實(shí)現(xiàn)方法有哪幾種?基于Verilog HDL的FIR數(shù)字濾波器設(shè)計與仿真

2021-04-09 06:02:50

使用iir濾波器相對fir濾波器可以在使用更小的階數(shù)的情況下實(shí)現(xiàn)更好的效果。實(shí)驗(yàn)證明,可能20階的iir效果堪比500階左右的fir濾波器效果。首先放出iir的matlab仿真代碼:%本程

2021-12-22 08:29:40

主要任務(wù):1.熟悉低通濾波器的原理及應(yīng)用2.熟悉FPGA的硬件描述3.FPGA如何實(shí)現(xiàn)小數(shù)分頻器4.用MATLAB對低通濾波器的驗(yàn)證預(yù)期成果或目標(biāo):FPGA對低通濾波器的Verilog(或VHDL

2013-04-04 22:16:11

診斷儀對超聲信號進(jìn)行動態(tài)濾波。動態(tài)濾波包含模擬動態(tài)濾波和數(shù)字動態(tài)濾波。模擬動態(tài)濾波器要改變器件的參數(shù),從而達(dá)到改變通頻帶中心頻率的效果,方法簡易,效果很好。同時,控制信號是來自FPGA輸送出的數(shù)字信號

2019-07-23 06:11:34

本帖最后由 eehome 于 2013-1-5 09:50 編輯

基于FPGA的FIR濾波器設(shè)計與實(shí)現(xiàn) 文章研究基于FPGA、采用分布式算法實(shí)現(xiàn)FIR濾波器的原理和方法,用

2012-08-11 15:32:34

數(shù)字濾波器、DSP器件或可編程邏輯器件(如FPGA)實(shí)現(xiàn)。因?yàn)椋?b class="flag-6" style="color: red">FPGA實(shí)現(xiàn)數(shù)字濾波器具有實(shí)時性強(qiáng)、靈活性高、處理速度快以及小批量生產(chǎn)成本低等優(yōu)點(diǎn),所以得到了較為廣泛的應(yīng)用。本文以巴特沃思數(shù)字

2019-07-08 07:18:25

基于FPGA的fir濾波器實(shí)現(xiàn)

2017-08-28 19:57:36

本帖最后由 eehome 于 2013-1-5 09:50 編輯

基于fpga的fir濾波器的實(shí)現(xiàn)

2012-08-17 16:42:33

【作者】:袁江南;湯碧玉;陳輝煌;【來源】:《廈門大學(xué)學(xué)報(自然科學(xué)版)》2010年02期【摘要】:給出了一種自適應(yīng)濾波器的設(shè)計和FPGA的實(shí)現(xiàn)方法.簡要分析了最小均方誤差(LMS)、歸一化最小均方

2010-04-24 09:01:12

【作者】:丁穩(wěn)房;鄭利枝;黃文聰;張黨文;【來源】:《湖北工業(yè)大學(xué)學(xué)報》2010年01期【摘要】:根據(jù)有源電力濾波器的基本原理,介紹了硬件電路和控制方法.控制器件采用DSP TMS320F2812.

2010-04-24 09:06:54

濾波器是任何信號處理系統(tǒng)的關(guān)鍵組成部分,隨著現(xiàn)代應(yīng)用的日趨復(fù)雜,濾波器設(shè)計的復(fù)雜程度也日益提高。采用 FPGA 設(shè)計和實(shí)現(xiàn)的高性能濾波器的能力是模擬方法所望塵莫及的。另外,采用FPGA

2019-09-18 08:28:47

本文介紹了一種采用級聯(lián)結(jié)構(gòu)在FPGA上實(shí)現(xiàn)IIR數(shù)字濾波器的方法。

2021-04-15 06:16:32

本文提出一種基于Stratix系列FPGA器件的新的實(shí)時高速脈動FIR濾波器的快速實(shí)現(xiàn)方法。

2021-05-06 09:50:42

濾波器在FPGA中的實(shí)現(xiàn)用FPGA來實(shí)現(xiàn)濾波器的設(shè)計優(yōu)點(diǎn)用FPGA來設(shè)計濾波器,不但設(shè)計簡單,而且成本小,可靠性好。且無需像傳統(tǒng)的設(shè)計芯片一樣進(jìn)行測試。主要優(yōu)點(diǎn):設(shè)計簡潔。若設(shè)計有誤,則只需

2021-07-30 07:03:10

如何用中檔FPGA實(shí)現(xiàn)多相濾波器?

2021-04-29 06:30:57

并行流水結(jié)構(gòu)FIR的原理是什么基于并行流水線結(jié)構(gòu)的可重配FIR濾波器的FPGA實(shí)現(xiàn)

2021-04-29 06:30:54

目前FIR濾波器的硬件實(shí)現(xiàn)的方式有哪幾種?怎么在FPGA上實(shí)現(xiàn)FIR濾波器的設(shè)計?

2021-05-07 06:03:13

用FPGA來實(shí)現(xiàn)濾波器的設(shè)計優(yōu)點(diǎn)有哪些?

2021-11-05 07:59:53

利用matlab設(shè)計一個線性相位FIR帶通濾波器,并在FPGA上實(shí)現(xiàn)。要求:1、濾波器指標(biāo):過渡帶帶寬分別為100~300HZ,500~700HZ,阻帶允許誤差為0.02,通帶允許誤差為0.01,采樣

2015-06-16 19:25:35

軟件無線電中的多速率信號處理.介紹r級聯(lián)積分梳狀濾波器的基本組成及設(shè)計原理,給出了基于FPGA 的具體設(shè)計方案及實(shí)現(xiàn)方法。仿真結(jié)果表明,該設(shè)計簡單合理,使用靈活方便,

2009-07-07 14:38:30 32

32 本文提出了一種采用現(xiàn)場可編程門陣列器件 FPGA 實(shí)現(xiàn)FIR 字濾波器硬件電路的方案,該方案基于只讀存儲器ROM 查找表的分布式算法。并以一個十六階低通FIR 數(shù)字濾波電路在ALTERA 公

2009-08-31 16:47:47 45

45 本文介紹了自適應(yīng)濾波器的實(shí)現(xiàn)方法,給出了基于LMS 算法自適應(yīng)濾波器在FPGA 中的實(shí)現(xiàn),簡單介紹了這種實(shí)現(xiàn)方法的各個功能模塊,主要包括輸入信號的延時輸出模塊、控制模塊

2009-09-14 15:51:00 34

34 本文利用Xilinx公司Virtex系列器件的特殊結(jié)構(gòu),提出了一種比較新穎的數(shù)字匹配濾波器設(shè)計方法,它在保證了該匹配濾波器與傳統(tǒng)匹配濾波器性能

2009-09-15 09:07:29 22

22 基于FPGA對稱型FIR濾波器的設(shè)計與實(shí)現(xiàn):在基于FPGA的對稱型FIR數(shù)字濾波器設(shè)計中,為了提高速度和運(yùn)行效率,提出了使用線性I相位結(jié)構(gòu)和加法樹乘法器的方法,并利用Altera公I(xiàn)司的FPG

2009-09-25 15:38:38 30

30 本文詳細(xì)討論了利用新版本FPGA 輔助設(shè)計軟件QuartusII6.0 中提供的浮點(diǎn)運(yùn)算功能模塊實(shí)現(xiàn)IIR 濾波器的方法,與采用FPGA 的乘法模塊的同類設(shè)計相比,此濾波器設(shè)計結(jié)構(gòu)簡單,容易擴(kuò)

2009-12-19 15:44:27 38

38 在軟件無線電的下變頻模塊中,級聯(lián)梳狀積分濾波器有著重要的應(yīng)用,其主要作用是信號的抽取與低通濾波。文中總結(jié)了級聯(lián)梳狀積分抽取濾波器的理論要點(diǎn),并介紹了采用FPGA

2010-01-06 15:16:45 31

31 數(shù)字濾波器在FPGA中的實(shí)現(xiàn)

2010-02-09 10:21:27 77

77 有源濾波器中數(shù)字低通濾波器的設(shè)計及其DSP實(shí)現(xiàn)摘要:介紹了基于瞬時無功功率理論的ip iq 諧波檢測方法及對低通濾波器的要求,分析討論了數(shù)字低通濾波器的類

2010-05-13 17:19:18 90

90 設(shè)計一個由現(xiàn)場可編程門陣列(FPGA)控制的濾波器。該濾波器主要由3個模塊組成:前置放大、濾波電路、FPGA顯示與控制電路等利用FPGA作為放大器及程控濾波器電路中繼電器組的控制模

2010-07-17 18:00:09 45

45 IIR數(shù)字濾波器設(shè)計-在FPGA上實(shí)現(xiàn)任意階IIR數(shù)字濾波器

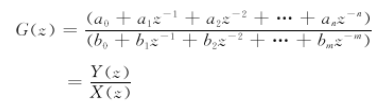

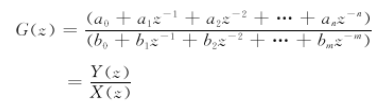

摘 要:本文介紹了一種采用級聯(lián)結(jié)構(gòu)在FPGA上實(shí)現(xiàn)任意階IIR數(shù)字濾波器的方法。此

2008-01-16 09:45:39 2857

2857

高效FIR濾波器的設(shè)計與仿真-基于FPGA

摘要:該文在介紹有限沖激響應(yīng)(FIR)數(shù)字濾波器理論及常見實(shí)現(xiàn)方法的基礎(chǔ)上,提出了一種基于FPGA的高效實(shí)現(xiàn)方案。

2008-01-16 09:56:02 2060

2060

MTD濾波器設(shè)計方法比較

早期MTD濾波器,直接采用DFT算法。該算法等效于一組窄帶濾波器組,具有數(shù)字硬件實(shí)現(xiàn)簡單的特點(diǎn),由于MTD雷達(dá)中

2009-02-27 10:03:00 2802

2802 如何用用FPGA實(shí)現(xiàn)FIR濾波器

你接到要求用FPGA實(shí)現(xiàn)FIR濾波器的任務(wù)時,也許會想起在學(xué)校里所學(xué)的FIR基礎(chǔ)知識,但是下一步該做什么呢?哪些參數(shù)是重

2009-03-30 12:25:45 4905

4905

【摘 要】 提出了一種基于分布式算法的,采用基于RAM之移位寄存器來設(shè)計可級聯(lián)FIR濾波器的設(shè)計方法。 &

2009-05-11 19:45:52 1285

1285

摘要: 提出了一種采用現(xiàn)場可編碼門陣列器件(FPGA)并利用窗函數(shù)法實(shí)現(xiàn)線性FIR數(shù)字濾波器的設(shè)計方案,并以一個十六階低通FIR數(shù)字濾波器電路的實(shí)現(xiàn)

2009-06-20 14:05:46 1679

1679

摘要: 針對在FPGA中實(shí)現(xiàn)FIR濾波器的關(guān)鍵--乘法運(yùn)算的高效實(shí)現(xiàn)進(jìn)行了研究,給了了將乘法化為查表的DA算法,并采用這一算法設(shè)計了FIR濾波器。通過FPGA仿零點(diǎn)驗(yàn)證

2009-06-20 14:09:36 1050

1050

FIR帶通濾波器的FPGA實(shí)現(xiàn)

引 言??? 在FPGA應(yīng)用中,比較廣泛而基礎(chǔ)的就是數(shù)字濾波器。根據(jù)其單位沖激響應(yīng)函數(shù)的時域特性可分為無限沖擊響應(yīng)(Infinite

2009-11-13 09:55:18 7499

7499

基于FPGA的數(shù)字濾波器的設(shè)計與實(shí)現(xiàn)

在信息信號處理過程中,如對信號的過濾、檢測、預(yù)測等,都要使用到濾波器,數(shù)字濾波器是數(shù)字信號處理中使用最廣泛的一

2010-01-07 10:45:35 4082

4082

采用DSPBuilder的FIR濾波器的方案實(shí)現(xiàn)

1.引言

在信息信號處理過程中,如對信號的過濾、檢測、預(yù)測等,都要使用濾波器,數(shù)字濾波器是數(shù)字信號處

2010-03-04 17:09:38 983

983

FPGA的Kalman濾波器的設(shè)計

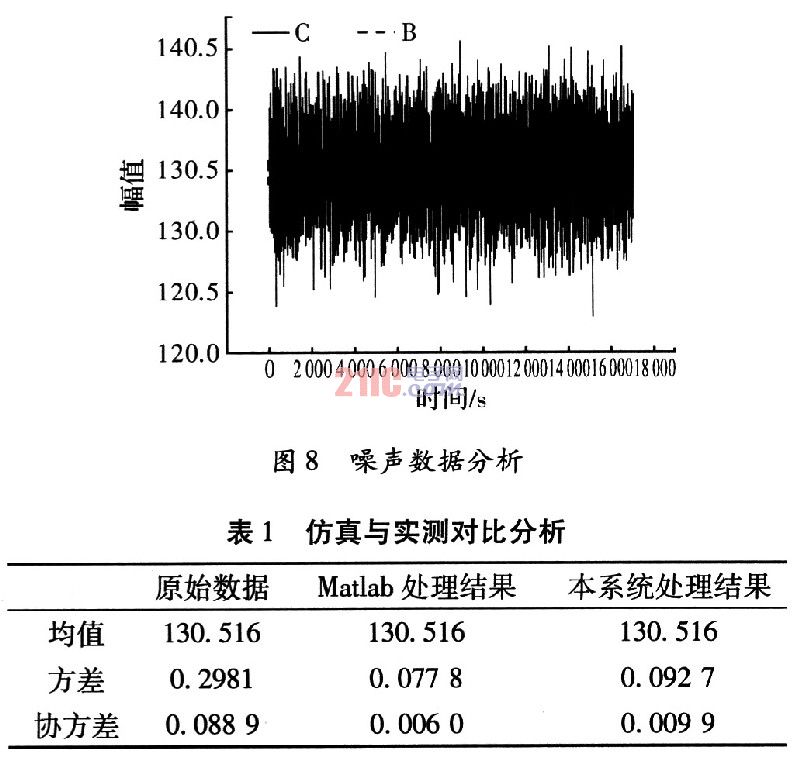

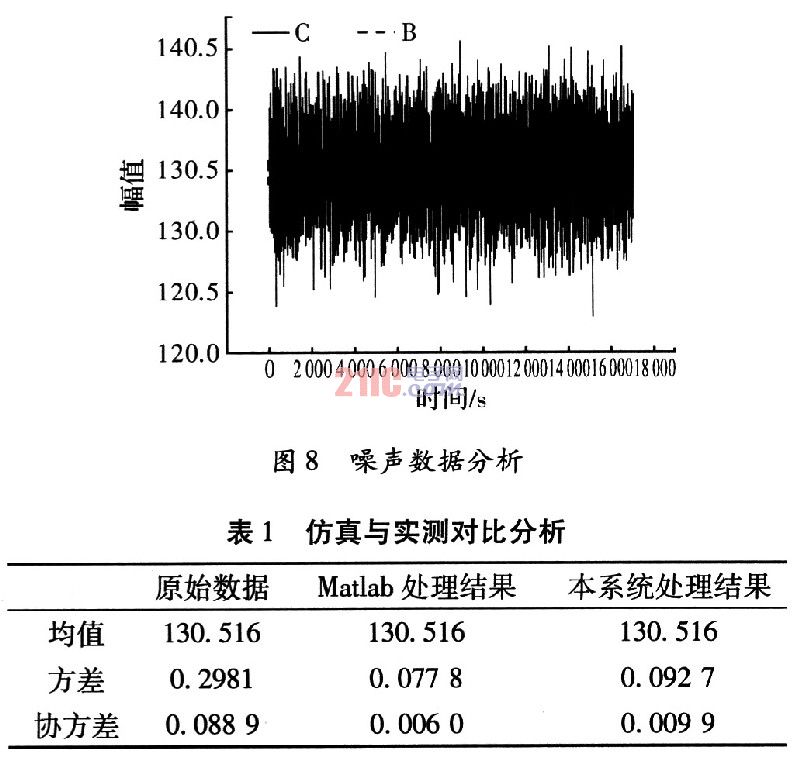

摘要:針對電路設(shè)計中經(jīng)常碰到數(shù)據(jù)的噪聲干擾現(xiàn)象,提出了一種Kalman濾波的FPGA實(shí)現(xiàn)方法。該方法采用了TI公司的高精度模數(shù)轉(zhuǎn)換

2010-04-13 13:32:46 3553

3553

DNLMS濾波器的FPGA設(shè)計方案

自適應(yīng)濾波算法的研究始于20世紀(jì)50年代末,Widrow和Hoff等人最早提出最小均方算法(LMS)。算法由于結(jié)構(gòu)簡單,計算量小,易于實(shí)

2010-05-10 10:06:23 857

857

模擬動態(tài)濾波器要改變器件的參數(shù),從而達(dá)到改變通頻帶中心頻率的效果,方法簡易,效果很好。同時,控制信號是來自FPGA輸送出的數(shù)字信號,經(jīng)D/A轉(zhuǎn)換所得,采用FPGA實(shí)現(xiàn)控制信號,實(shí)現(xiàn)了很高的精度,達(dá)到了預(yù)想的效果。

2011-01-24 10:24:53 2212

2212

摘要: 針對水下目標(biāo)跟蹤定位系統(tǒng)中信號的特點(diǎn), 采用自適應(yīng)Notch 濾波器對接收信號進(jìn)行檢測, 使系統(tǒng)在低信噪 比的情況下仍能保證較高的正確檢測率。提出了用FPGA 實(shí)現(xiàn)Notch 濾波器的硬件電路方案, 用DDS 技術(shù)解決了 Notch 濾波器的正交參考源的輸入問題, 簡化

2011-02-17 16:00:14 69

69 為補(bǔ)償傳統(tǒng)CIC濾波器的通帶衰減,提出一種改進(jìn)型的CIC抽取濾波器,即在SCIC濾波器之后級聯(lián)一個二階多項(xiàng)式內(nèi)插濾波器。基于硬件實(shí)現(xiàn)的要求,給出改進(jìn)型CIC濾波器的FPGA高效實(shí)現(xiàn)原理圖。仿真結(jié)果表明改進(jìn)的CIC濾波器具有更好的通阻帶特性。

2011-03-15 14:06:35 52

52 目前數(shù)字濾波器的硬件實(shí)現(xiàn)方法通常采用專用DSP芯片或FPGA,本文從FIR濾波器的系數(shù)考慮,采用CSD編碼,對FIR數(shù)字濾波器進(jìn)行優(yōu)化設(shè)計。

2011-08-16 10:54:41 4210

4210

基于多速率信號處理原理,設(shè)計了用于下變頻的CIC抽取濾波器,由于CIC濾波器結(jié)構(gòu)只用到加法器和延遲器,沒有乘法器,很適合用FPGA來實(shí)現(xiàn),所以本文分析了CIC濾波器的原理,性能及影

2011-08-26 15:12:11 162

162 針對羅蘭C前端 帶通濾波 的需求,提出了采用級聯(lián)形式在FPGA上實(shí)現(xiàn)羅蘭C數(shù)字帶通濾波器的方法。首先利用Matlab設(shè)計出滿足要求的濾波器,考慮硬件設(shè)計要求將參數(shù)進(jìn)行取整,并對取整

2011-08-30 16:24:25 45

45 文中設(shè)計的均衡濾波器充分利用FPGA內(nèi)部資源、時間換取空間的方法,在EP1C3系列的FPGA內(nèi)實(shí)現(xiàn)1 024階FIR數(shù)字均衡濾波器,并通過重載系數(shù),可實(shí)現(xiàn)多種頻率響應(yīng)的均衡特性、簡易數(shù)字均衡濾波

2011-10-19 15:23:48 38

38 為了產(chǎn)生調(diào)制信號的碼元速率能在大范圍內(nèi)實(shí)時可變,采用插值濾波技術(shù) 多級積分梳狀濾波器。在分析多級濾波器的結(jié)構(gòu)和特性的基礎(chǔ)上,闡述了一種利用剪除理論實(shí)現(xiàn)多級濾波器的高效

2011-12-26 18:33:08 25

25 LMS自適應(yīng)濾波器是一種廣泛使用的數(shù)字信號處理算法,對其實(shí)現(xiàn)有多種方法.通過研究其特性的基礎(chǔ)上,提出了在FPGA 中使用軟處理的嵌入式實(shí)現(xiàn)方案,文中對實(shí)現(xiàn)方式的優(yōu)缺點(diǎn)進(jìn)行了

2012-02-14 16:37:02 75

75 描述了基于FPGA的FIR濾波器設(shè)計。根據(jù)FIR的原理及嚴(yán)格線性相位濾波器具有偶對稱的性質(zhì)給出了FIR濾波器的4種結(jié)構(gòu),即直接乘加結(jié)構(gòu)、乘法器復(fù)用結(jié)構(gòu)、乘累加結(jié)構(gòu)、DA算法。在本文中給

2012-11-09 17:32:37 121

121 文中基于多速率數(shù)字信號處理原理,設(shè)計了用于數(shù)字下變頻技術(shù)的CIC抽取濾波器。通過分析CIC濾波器的原理及性能參數(shù),利用MATLAB設(shè)計了符合系統(tǒng)要求的CIC濾波器,并通過FPGA實(shí)現(xiàn)了CI

2013-04-15 19:29:28 71

71 分析了數(shù)字濾波器的原理,介紹了采用窗體函數(shù)法完成FIR數(shù)字濾波器,包括MATLAB仿真和DSP的實(shí)現(xiàn)方法。通過MATLAB仿真驗(yàn)證了所設(shè)計的濾波器具有良好的濾波功能,以TMS320F2812DSP為核心器

2013-06-09 16:21:33 158

158 基于FPGA的FIR濾波器設(shè)計與實(shí)現(xiàn),下來看看

2016-05-10 11:49:02 39

39 研究了一種采用FPGA實(shí)現(xiàn)32階FIR濾波器硬件電路方案;討論了窗函數(shù)的選擇、濾波器的結(jié)構(gòu)以及系數(shù)量化問題;研究了FIR濾波器的FPGA實(shí)現(xiàn),各模塊的設(shè)計以及如何優(yōu)化硬件資源,提高運(yùn)行速度等

2017-11-10 16:41:57 16

16 為了減少信道化接收機(jī)的資源消耗,對低通濾波器組實(shí)現(xiàn)信道化接收機(jī)的結(jié)構(gòu)進(jìn)行了研究。在前人將HB濾波器和FIR濾波器設(shè)計為多通道并采用時分復(fù)用方法的基礎(chǔ)上,將NCO和CIC濾波器也做了同樣處理,并在

2017-11-17 05:38:02 4808

4808

ISE 12.3在Xilinx xc5vsx95t-2ff1136 FPGA上實(shí)現(xiàn)了一種下采樣率為64的抽取濾波器。Modelsim仿真結(jié)果表明,該抽取濾波器設(shè)計是有效的,達(dá)到了設(shè)計指標(biāo)。

2017-11-17 09:01:55 6492

6492 摘要:有限沖擊響應(yīng)(FIR)濾波器是數(shù)字通信系統(tǒng)中常用的基本模塊。文章設(shè)計了一種流水結(jié)構(gòu)的FIR濾波器,通過FPGA對其進(jìn)行硬什加速控制。仿真結(jié)果驗(yàn)證了所設(shè)計的FIR流水結(jié)構(gòu)濾波器功能的正確性

2017-11-18 06:15:02 2101

2101

的使用,同時以整數(shù)數(shù)據(jù)處理方式實(shí)現(xiàn)了向?qū)?b class="flag-6" style="color: red">濾波器中方差和變換系數(shù)的計算,并且通過參數(shù)調(diào)整,可以方便地實(shí)現(xiàn)不同大小圖像的不同尺寸窗口的向?qū)?b class="flag-6" style="color: red">濾波。在Altera公司Cyclone系列FPGA芯片上進(jìn)行了綜合,實(shí)驗(yàn)結(jié)果表明,向?qū)?b class="flag-6" style="color: red">濾波整數(shù)FPGA結(jié)構(gòu)的處理結(jié)果與

2017-11-22 15:43:12 12

12 音頻均衡器作為高品質(zhì)音響不可或缺的關(guān)鍵附屬調(diào)節(jié)設(shè)備,在音效調(diào)整修飾方面起著至關(guān)重要的作用。一般音頻均衡器有數(shù)字和模擬兩種實(shí)現(xiàn)方法,模擬方法用有源和無源濾波器組實(shí)現(xiàn),受器件溫度等特性的影響,難以達(dá)到

2018-07-14 10:31:00 3708

3708

本文針對快速、準(zhǔn)確選擇參數(shù)符合項(xiàng)目要求的濾波器設(shè)計方法的目的,通過系統(tǒng)的介紹有限脈沖響應(yīng)( Finite Impulse Response,F(xiàn)IR)濾波器的原理、結(jié)構(gòu)形式以及幾種FIR濾波器設(shè)計方法

2017-12-21 14:53:14 14

14 ,常規(guī)做法是利用插值和抽取的方法實(shí)現(xiàn)數(shù)字信號的變采樣處理,這種方法實(shí)現(xiàn)復(fù)雜,硬件成本高。文中提出了一種高速并行成型濾波器的FPGA實(shí)現(xiàn)方法,這種基于群延時結(jié)構(gòu)的查找表算法,所需的查找表只需存儲單位沖擊響應(yīng)的采樣值,

2018-02-23 10:14:22 0

0 用FPGA實(shí)現(xiàn)抽取濾波器比較復(fù)雜,主要是因?yàn)樵?b class="flag-6" style="color: red">FPGA中缺乏實(shí)現(xiàn)乘法運(yùn)算的有效結(jié)構(gòu),現(xiàn)在,FPGA中集成了硬件乘法器,使FPGA在數(shù)字信號處理方面有了長足的進(jìn)步。本文介紹了一種采用Xilinx公司的XC2V1000實(shí)現(xiàn)FIR抽取濾波器的設(shè)計方法。

2018-04-28 11:50:00 1620

1620

本文檔內(nèi)容介紹了基于IIR數(shù)字濾波器的FPGA實(shí)現(xiàn),供參考

2018-03-02 13:45:19 36

36 基于靈活自適應(yīng)的空口波形技術(shù)FOFDM(Filtered OFDM)是現(xiàn)代通信技術(shù)的研究熱點(diǎn),設(shè)計并實(shí)現(xiàn)可調(diào)FIR濾波器是實(shí)現(xiàn)該技術(shù)的核心工作之一。本文設(shè)計的基于FPGA的可調(diào)節(jié)FIR濾波器系數(shù)

2018-07-23 17:21:00 3003

3003

在實(shí)現(xiàn)多級CIC濾波器前我們先來了解滑動平均濾波器、微分器、積分器以及梳狀濾波器原理。CIC濾波器在通信信號處理中有著重要的應(yīng)用。

2019-06-22 10:35:53 3377

3377

高通濾波器在濾波電路中占據(jù)了重要的地位,它和低通濾波器配合可以構(gòu)成超寬帶濾波器,也可以構(gòu)成通帶相接的頻率分配器,超寬帶的吸收式濾波器也需要采用這個器件。其他結(jié)構(gòu)的濾波器在課本和站上均能找到大量

2020-07-17 10:26:00 4

4 用FPGA實(shí)現(xiàn)抽取濾波器比較復(fù)雜,主要是因?yàn)樵?b class="flag-6" style="color: red">FPGA中缺乏實(shí)現(xiàn)乘法運(yùn)算的有效結(jié)構(gòu),現(xiàn)在,FPGA中集成了硬件乘法器,使FPGA在數(shù)字信號處理方面有了長足的進(jìn)步。本文介紹了一種采用Xilinx公司的XC2V1000實(shí)現(xiàn)FIR抽取濾波器的設(shè)計方法。

2020-09-25 10:44:00 3

3 數(shù)字濾波器、DSP器件或可編程邏輯器件(如FPGA)實(shí)現(xiàn)。因?yàn)椋?b class="flag-6" style="color: red">FPGA實(shí)現(xiàn)數(shù)字濾波器具有實(shí)時性強(qiáng)、靈活性高、處理速度快以及小批量生產(chǎn)成本低等優(yōu)點(diǎn),所以得到了較為廣泛的應(yīng)用。本文以巴特沃思數(shù)字帶通濾波器為例,較為詳細(xì)地介紹了其設(shè)計和實(shí)

2020-08-06 18:50:00 3

3 針對Σ△ADC輸出端存在的高頻噪聲問題,設(shè)計了一種 Sinc數(shù)字抽取濾波器,實(shí)現(xiàn)了Σ-△調(diào)制器輸出信號的高頻濾波。分析了Sinc濾波器的結(jié)構(gòu)原理,基于 Spartan6FPGA進(jìn)行濾波器的設(shè)計與實(shí)現(xiàn)

2020-08-26 17:12:00 17

17 ,基帶數(shù)字成形濾波器具有高精度、高可靠性和高靈活性等優(yōu)點(diǎn);同時還具有便于大規(guī)模集成、易于實(shí)現(xiàn)線性相位等特點(diǎn)。實(shí)現(xiàn)基帶數(shù)字成形的方法很多,與傳統(tǒng)算法相比,分布式算法可以極大地減少硬件電路的規(guī)模,提高電路的執(zhí)行速度。本文采用基于分布式算法思想的時域成形方法來實(shí)現(xiàn)基帶信號成形。

2020-09-24 19:57:57 1534

1534

一個模擬集成運(yùn)算放大器可實(shí)現(xiàn)一個二階濾波器,高階濾波器可由二階濾波器串聯(lián)而成。然而,無源元器件實(shí)現(xiàn)濾波器的誤差值為1.5%或更高,這需要提高元器件的性能。濾波器的典型的調(diào)試方法是不斷的更換元器件值

2020-11-23 16:18:00 1641

1641

為了研究不同結(jié)構(gòu)的nR數(shù)字濾波器FPGA實(shí)現(xiàn)對數(shù)字多普勒接收機(jī)中n,GA器件資源消耗及其實(shí)現(xiàn)的濾波器的速度性能,在Xilinx ISEIO.1開發(fā)平臺中,采用Verilog HDL語言分剮實(shí)現(xiàn)了

2021-01-22 16:12:27 17

17 在分析傳統(tǒng)自適應(yīng)濾波算法的基礎(chǔ)上,針對自適應(yīng)濾波器的硬件實(shí)現(xiàn),采用一種適合FPGA實(shí)現(xiàn)的DLMS算法。使用VHDL語言完成設(shè)計,仿真實(shí)驗(yàn)驗(yàn)證了設(shè)計的正確性,經(jīng)過編譯和布局布線后對改進(jìn)算法和傳統(tǒng)算法進(jìn)行了比較,結(jié)果表明改進(jìn)算法在增加硬件消耗較少的情況下有效提高了系統(tǒng)工作頻率。

2021-01-22 16:12:24 12

12 WCDMA中規(guī)定了小區(qū)搜索的時隙同步過程采用匹配濾波器的方法實(shí)現(xiàn),本論文主要研究匹配濾波器原理及FPGA實(shí)現(xiàn)結(jié)構(gòu)。

2021-01-26 16:22:43 12

12 倍,其中L為并行的路數(shù),并且運(yùn)算延遲小。首先從理論上分析了基于多相濾波器的并行濾波原理,并以八路并行為例,對FIR濾波運(yùn)算做了浮點(diǎn)仿真驗(yàn)證。然后用經(jīng)典符號數(shù)表示以及優(yōu)化定點(diǎn)濾波器系數(shù),并針對濾波器系數(shù)設(shè)計了流水線結(jié)構(gòu)。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 15

15 倍,其中L為并行的路數(shù),并且運(yùn)算延遲小。首先從理論上分析了基于多相濾波器的并行濾波原理,并以八路并行為例,對FIR濾波運(yùn)算做了浮點(diǎn)仿真驗(yàn)證。然后用經(jīng)典符號數(shù)表示以及優(yōu)化定點(diǎn)濾波器系數(shù),并針對濾波器系數(shù)設(shè)計了流水線結(jié)構(gòu)。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 7

7 提出一種新的高階FIR濾波器的FPGA實(shí)現(xiàn)方法。該方法運(yùn)用多相分解結(jié)構(gòu)對高階FIR濾波器進(jìn)行降階處理,采用改進(jìn)的分布式算法來實(shí)現(xiàn)降階后的FIR濾波器。設(shè)計了一系列階數(shù)從8到1 024的FIR濾波器

2021-03-23 15:44:54 31

31 引言 目前,用FPGA(現(xiàn)場可編程門陣列)實(shí)現(xiàn)FIR(有限沖擊響應(yīng)) 濾波器 的方法大多利用FPGA中LUT(查找表)的特點(diǎn)采用DA(分布式算法)或CSD碼等方法,將乘加運(yùn)算操作轉(zhuǎn)化為位與、加減

2022-12-01 10:20:05 2154

2154 FIR濾波器設(shè)計方法主要有窗函數(shù)法、線性最小均方差法、最大似然法、自適應(yīng)濾波法、線性預(yù)測法等。窗函數(shù)法是一種簡單的設(shè)計方法,它可以通過選擇合適的窗函數(shù)來實(shí)現(xiàn)濾波器的設(shè)計;而線性最小均方差法則是一種更加復(fù)雜的設(shè)計方法,它可以通過最小化濾波器的均方差來實(shí)現(xiàn)濾波器的設(shè)計。

2023-02-15 14:58:37 2524

2524 FIR濾波器設(shè)計方法主要有窗函數(shù)法、線性最小均方差法、最大似然法、自適應(yīng)濾波法、線性預(yù)測法等。窗函數(shù)法是一種簡單的設(shè)計方法,它可以通過選擇合適的窗函數(shù)來實(shí)現(xiàn)濾波器的設(shè)計;而線性最小均方差法則是一種更加復(fù)雜的設(shè)計方法,它可以通過最小化濾波器的均方差來實(shí)現(xiàn)濾波器的設(shè)計。

2023-02-15 15:29:19 3789

3789 本文介紹了設(shè)計濾波器的FPGA實(shí)現(xiàn)步驟,并結(jié)合杜勇老師的書籍中的串行FIR濾波器部分進(jìn)行一步步實(shí)現(xiàn)硬件設(shè)計,對書中的架構(gòu)做了簡單的優(yōu)化,并進(jìn)行了仿真驗(yàn)證。

2023-05-24 10:56:34 1843

1843

本文介紹了設(shè)計濾波器的FPGA實(shí)現(xiàn)步驟,并結(jié)合杜勇老師的書籍中的并行FIR濾波器部分進(jìn)行一步步實(shí)現(xiàn)硬件設(shè)計,對書中的架構(gòu)做了復(fù)現(xiàn)以及解讀,并進(jìn)行了仿真驗(yàn)證。

2023-05-24 10:57:36 1825

1825

。隨著現(xiàn)代數(shù)字通信系統(tǒng)對于高精度、高處理速度的需求,越來越多的研究轉(zhuǎn)向采用FPGA來實(shí)現(xiàn)FIR濾波器。而對于FIR濾波器要充分考慮其資源與運(yùn)行速度的合理優(yōu)化,各種不同的FIR濾波結(jié)構(gòu)各具優(yōu)缺點(diǎn),在了解各種結(jié)構(gòu)優(yōu)缺點(diǎn)后才能更好地選擇合適結(jié)構(gòu)來實(shí)現(xiàn)FIR濾波。

2024-11-05 16:26:54 2537

2537

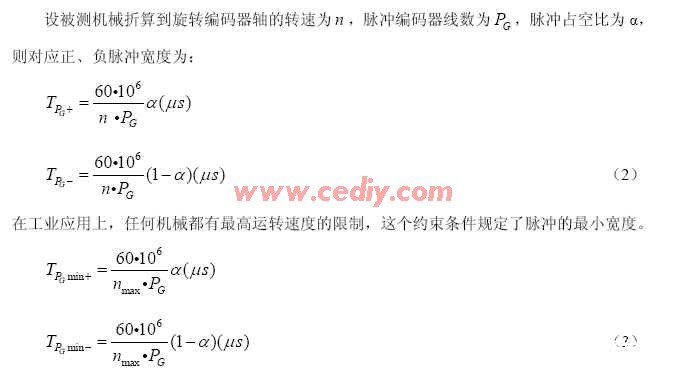

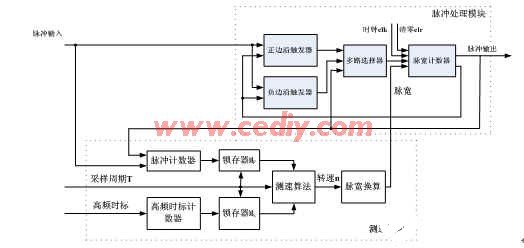

![]() 秒內(nèi)從靜止上升到額定轉(zhuǎn)速,則任意兩個相連脈沖的寬度變化為:

秒內(nèi)從靜止上升到額定轉(zhuǎn)速,則任意兩個相連脈沖的寬度變化為: (4)

(4)

(5)

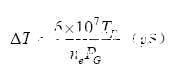

(5)![]() 為采樣周期內(nèi)計取的高頻時標(biāo)信號數(shù)。

為采樣周期內(nèi)計取的高頻時標(biāo)信號數(shù)。

電子發(fā)燒友App

電子發(fā)燒友App

評論