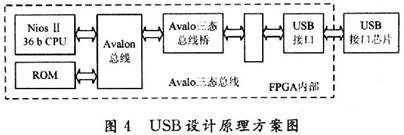

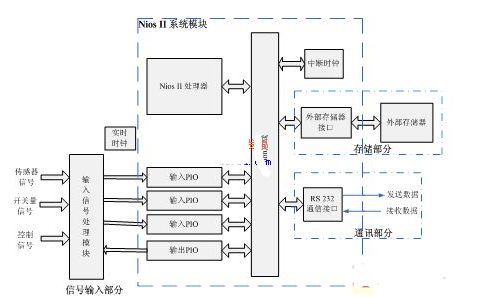

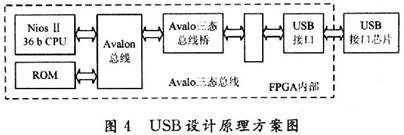

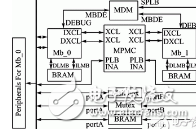

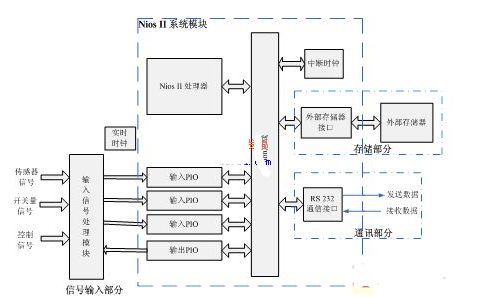

本文主要搭建一個(gè)多生理參數(shù)測(cè)量系統(tǒng)的數(shù)據(jù)處理平臺(tái),在FPGA中嵌入一個(gè)32位Nios II軟核處理器,用于控制數(shù)據(jù)的傳輸、存儲(chǔ)及顯示。主要完成了此數(shù)據(jù)處理平臺(tái)硬件系統(tǒng)的定

2010-08-18 12:10:44 1202

1202

使用Altera的嵌入式系列產(chǎn)品,您不必?fù)?dān)心處理器過時(shí)問題。這些軟核處理器具有可永久使用的許可,適用于所有Altera?FPGA。如果改動(dòng)了底層FPGA硬件,您也能夠保持您的應(yīng)用軟件投入不變

2011-11-30 16:47:06 1371

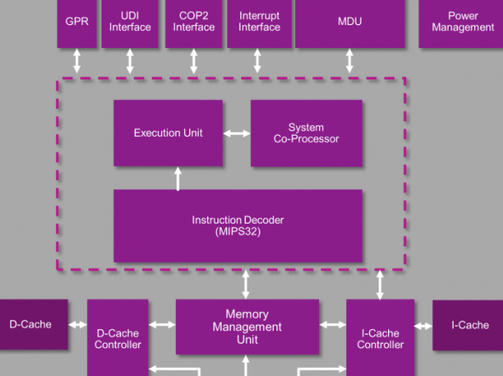

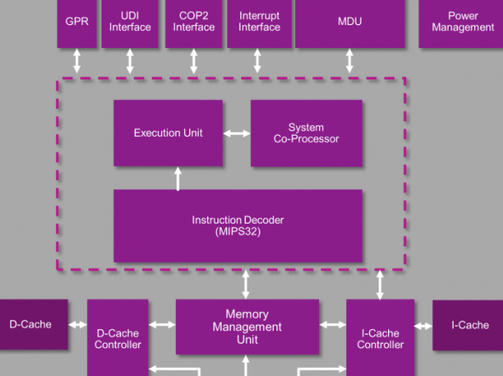

1371 課程的地方在于首次采用了一款純粹的商用軟核CPU用于研究目的,用戶可以在此課程的系統(tǒng)集成環(huán)境下詳細(xì)、深入的探索計(jì)算機(jī)架構(gòu)。 MIPSfpga使用一款MIPS系列軟核IP具體來講是microAptiv核,PIC32MK處理器采用的既是此款軟核。該核面向的是可編程邏

2018-05-21 10:17:01 8273

8273

可編程邏輯業(yè)對(duì)微處理器核的報(bào)道層出不窮,包括與ARM和MIPS的協(xié)議,這些討論已經(jīng)持續(xù)了數(shù)年。然而,討論的主題大體上沒什么改變,諸如采用硬核還是軟核?采用供應(yīng)商的特定標(biāo)準(zhǔn)還是行業(yè)標(biāo)準(zhǔn)?這些核如何用來全方位地支持生態(tài)系統(tǒng)?如何根據(jù)成本、功耗和性能來選擇微處理器?如何根據(jù)應(yīng)用來選擇核?

2019-08-08 06:43:03

FPGA是現(xiàn)場(chǎng)可編程門陣列,是可編程邏輯器件(PLD)的一種。 NIOS II是一種知識(shí)產(chǎn)權(quán)核(IP Core),是嵌在FPGA內(nèi)部的處理器軟核,相當(dāng)于在FPGA內(nèi)部設(shè)計(jì)了一個(gè)微處理器

2018-08-17 09:59:27

, 節(jié)約將近90% 的邏輯資源。 軟核(Soft IP Core) : 軟核在EDA 設(shè)計(jì)領(lǐng)域指的是綜合之前的寄存器傳輸級(jí)(RTL) 模型;具體在FPGA 設(shè)計(jì)中指的是對(duì)電路的硬件語言描述,包括邏輯描述

2018-09-03 11:03:27

,并配置相應(yīng)的參數(shù)。

在進(jìn)行參數(shù)化配置時(shí),務(wù)必注意參數(shù)的取值范圍、限制條件和影響。避免由于錯(cuò)誤的參數(shù)配置導(dǎo)致IP軟核無法正常工作。

集成和驗(yàn)證 :

將所選的IP軟核集成到FPGA項(xiàng)目中,并進(jìn)行功能驗(yàn)證

2024-05-27 16:13:24

FPGA硬核與軟核處理器有什么區(qū)別和聯(lián)系?

2023-05-30 20:36:48

如何根據(jù)成本、功耗和性能來選擇微處理器?FPGA結(jié)構(gòu)中硬核和軟核的特點(diǎn)是什么?處理器IP有什么重要性?

2021-04-08 06:16:37

求大神,FPGA內(nèi)部的PCI的IP軟核實(shí)現(xiàn)PCI接口設(shè)計(jì)?

2013-05-02 16:12:21

使用fpga做一個(gè)arm的軟核處理器,那么用戶程序如何燒到rom里面,fpga又如何能使rom里的程序加載到ram運(yùn)行呢?對(duì)于硬件如何啟動(dòng)軟件運(yùn)行不懂,希望有人能解答一下。

2017-03-31 15:31:33

處理器上有更多的選擇,Altera公司宣布,F(xiàn)reescale將為SOPC Builder工具推出32位V1 ColdFire軟核。為迅速方便的使用Altera? Cyclone? III FPGA建立

2008-06-17 11:40:12

在其業(yè)內(nèi)領(lǐng)先的低成本Cyclone TM FPGA系列和Nios軟核嵌入式處理器成功的基礎(chǔ)上,Altera現(xiàn)在推出了第二代產(chǎn)品系列。Cyclone II器件為用戶提供更高的邏輯密度和新增硬件性能,比

2019-07-18 07:43:25

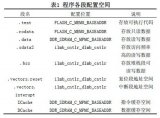

核,而如何針對(duì)特定的微處理器選擇合適的嵌入式操作系統(tǒng)是SOPC開發(fā)的難點(diǎn)之一。本文針對(duì)Xilinx公司的MicroBlaze軟核,介紹了PetaLinux嵌入式操作系統(tǒng)及其移植方法,研究了PetaLinux的相關(guān)配置和啟動(dòng)方案。

2020-03-16 06:37:20

求教e203 軟核如何和FPGA通信

2025-11-07 06:15:50

申請(qǐng)理由:項(xiàng)目描述:現(xiàn)公司在做一個(gè)關(guān)于導(dǎo)航定位系統(tǒng)的項(xiàng)目。現(xiàn)在設(shè)定的主要思路是: 將采集到的加速度計(jì)與陀螺的數(shù)據(jù),送進(jìn)FPGA,經(jīng)過平滑濾波模塊后,再送往MicroBlaze核模塊,與預(yù)先標(biāo)定

2016-10-12 09:52:40

個(gè)能執(zhí)行幾條指令的處理模塊ip核。它的功能將很簡(jiǎn)單。三、把處理器的框圖構(gòu)建出來,分模塊寫出較為完善的IP核。其中存儲(chǔ)器暫時(shí)不用SDRAM,寫驅(qū)動(dòng)IP還是有難度的。四、如果時(shí)間允許,給寫好的處理器擴(kuò)展外部模塊如SDRAM,VGA,TFT等等。五、給FPGA燒寫nios系統(tǒng)。

2017-07-25 18:02:36

可編程邏輯業(yè)對(duì)微處理器核的報(bào)道層出不窮,包括與ARM和MIPS的協(xié)議,這些討論已經(jīng)持續(xù)了數(shù)年。然而,討論的主題大體上沒什么改變,諸如采用硬核還是軟核?采用供應(yīng)商的特定標(biāo)準(zhǔn)還是行業(yè)標(biāo)準(zhǔn)?這些核如何用來全方位地支持生態(tài)系統(tǒng)?如何根據(jù)成本、功耗和性能來選擇微處理器?如何根據(jù)應(yīng)用來選擇核?

2019-08-13 07:52:46

架構(gòu)雙核ARM Cortex-A9 處理器:一個(gè)應(yīng)用級(jí)的處理器,能運(yùn)行完整的像Linux 這樣的操作系統(tǒng)傳統(tǒng)的現(xiàn)場(chǎng)可編程門陣列(Field Programmable Gate Array,FPGA

2021-07-23 09:23:34

的RISC CPU設(shè)計(jì)是一個(gè)從抽象到具體的過程,本文根據(jù)FPGA的結(jié)構(gòu)特點(diǎn),圍繞在FPGA上設(shè)計(jì)實(shí)現(xiàn)八位微處理器軟核設(shè)計(jì)方法進(jìn)行探討,研究了片上系統(tǒng)的設(shè)計(jì)方法和設(shè)計(jì)復(fù)用技術(shù),并給出了指令集和其調(diào)試方法,提出

2021-07-11 08:00:01

基于NIOS II 軟核處理器的SOPC 技術(shù)摘要:介紹了基于NIOS II 軟核處理器的SOPC 技術(shù),分析了傳統(tǒng)方法和基于SOPC 技術(shù)的方法實(shí)現(xiàn)擴(kuò)頻收發(fā)機(jī)的優(yōu)劣,詳細(xì)說明了嵌有雙NIOS II

2009-10-06 15:05:24

對(duì)設(shè)計(jì)進(jìn)行綜合,下載到FPGA中就可以方便地實(shí)現(xiàn)一個(gè)具有高速DSP功能的嵌入式處理器。那么直接在讀寫寄存器上進(jìn)行嵌入式軟核Nios Ⅱ串口編程,有哪些方法?我們應(yīng)該注意哪些事項(xiàng)呢?

2019-08-06 06:37:27

有沒有帶DSP軟核的FPGA,要求DSP運(yùn)行速度在50kHz以上。

2014-09-29 18:13:51

你好 我對(duì)Saprtan 3E有一些疑問。 (1)當(dāng)試圖將軟處理器嵌入到傳統(tǒng)FPGA中時(shí),主要問題是什么以及如何解決它。(2)Saprtan 3E如何解決這個(gè)問題,因?yàn)樗枰獙?b class="flag-6" style="color: red">軟核處理器嵌入到傳統(tǒng)

2019-06-05 07:48:29

編程接口共用或并存,可能包含部分可編程模擬電路,單芯片、低功耗。本文主要研究的是應(yīng)用嵌入式系統(tǒng)開發(fā)的軟硬件協(xié)同設(shè)計(jì)方法來實(shí)現(xiàn)一個(gè)集軟核處理器的嵌入式設(shè)計(jì)平臺(tái),在此基礎(chǔ)上,如有必要還可集成嵌入式操作系統(tǒng)。

2020-03-13 07:03:54

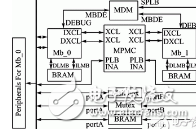

處理器間通信和中斷方面仍需進(jìn)一步的研究。本文在處理器間通信和中斷控制方面進(jìn)行了深入的研究。MicroBlaze是一個(gè)被優(yōu)化過的可以在Xilinx公司FPGA中運(yùn)行的軟核處理器,可以和其他外設(shè)IP核一起完成

2021-03-16 07:44:35

本文設(shè)計(jì)了一種在多處理器系統(tǒng)中的Nios II軟核處理器的啟動(dòng)方案,這個(gè)方案在外部處理器向Nios II的程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器加載數(shù)據(jù)時(shí),可以控制Nios II處理器的啟動(dòng)。

2021-04-27 06:52:42

本文介紹了一種基于FPGA及NiosII軟核處理器與TFT-LCD接口的方法。它直接采用CPU對(duì)存貯器的讀寫,實(shí)現(xiàn)了對(duì)TFT-LCD屏的實(shí)時(shí)操作。它具有直接、有效和速度快等特點(diǎn)。該設(shè)計(jì)使CPU對(duì)TFT-LCD的控制極其簡(jiǎn)單化。

2021-05-08 07:21:11

本文根據(jù)FPGA的結(jié)構(gòu)特點(diǎn),圍繞在FPGA上設(shè)計(jì)實(shí)現(xiàn)八位微處理器軟核設(shè)計(jì)方法進(jìn)行探討,研究了片上系統(tǒng)的設(shè)計(jì)方法和設(shè)計(jì)復(fù)用技術(shù),并給出了指令集和其調(diào)試方法,提出了一種基于FPGA的微處理器的IP的設(shè)計(jì)方法。

2021-04-29 06:38:37

最近看了《步步驚芯——軟核處理器內(nèi)部設(shè)計(jì)分析》,感覺不錯(cuò),對(duì)OR1200的分析比較透徹,好不容易找到了清晰版《步步驚芯——軟核處理器內(nèi)部設(shè)計(jì)分析》前1-4章的PDF文件,建議大家下載看看。

2013-11-03 13:59:03

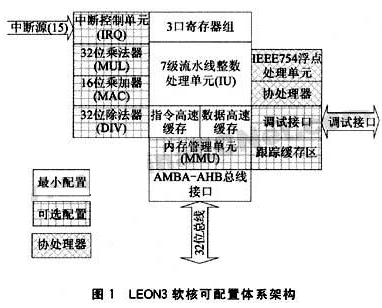

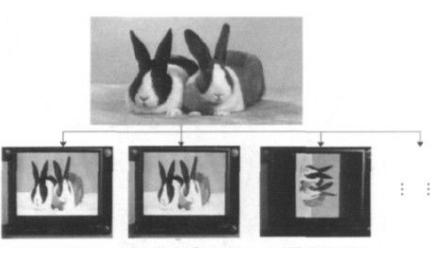

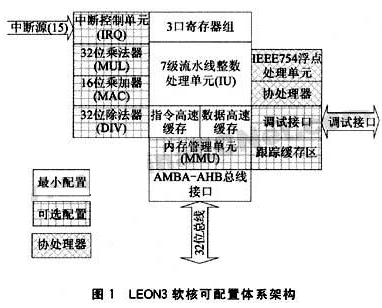

本文介紹了基于LEON3開源軟核處理器的動(dòng)態(tài)圖像邊緣檢測(cè)SoC設(shè)計(jì)。 實(shí)驗(yàn)結(jié)果表明該SoC系統(tǒng)工作正常,可以實(shí)現(xiàn)每秒22~25幀,最佳分辨率為400×240和640×480的動(dòng)態(tài)圖像邊緣檢測(cè)

2021-02-22 07:50:13

請(qǐng)教大神怎樣使用ARM DesignStart計(jì)劃開放的處理器核搭建SoC系統(tǒng)呢?

2022-07-29 15:01:05

新手學(xué)習(xí)FPGA有點(diǎn)疑問: 1, 很多教程所謂的NIOSII只是一個(gè)軟核吧, 跟我選哪款FPGA處理器沒關(guān)系吧? 2, 這么說的話我買黑金199塊錢的那款板子也完全夠用?

2019-04-08 09:34:36

片上Nios Ⅱ嵌入式軟核多處理器系統(tǒng)具有哪些優(yōu)勢(shì)?如何實(shí)現(xiàn)片上嵌入式Nios Ⅱ軟核六處理器系統(tǒng)的設(shè)計(jì)?

2021-04-19 08:17:09

包含一個(gè)以上的嵌入式處理器IP(Intellectual Property,知識(shí)產(chǎn)權(quán))核,具有小容量片內(nèi)高速RAM資源,豐富的IP核資源可供靈活選擇,有足夠的片上可編程邏輯資源,處理器高速接口和FPGA編程接口共用或并存,可能包含部分可編程模擬電路,單芯片、低功耗[1]。

2019-08-23 08:18:51

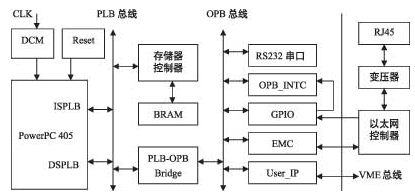

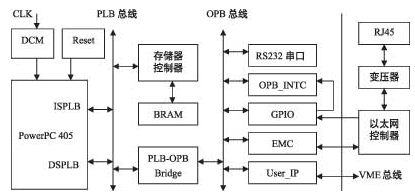

分析軟處理器MicroBlaze 的體系結(jié)構(gòu), 給出MicroBlaze 內(nèi)核在軟件無線電系統(tǒng)中的應(yīng)用, 實(shí)現(xiàn)SOPC(可編程系統(tǒng)芯片)。

2009-04-15 10:16:09 22

22 介紹了基于ALTERA 公司FPGA 的雙NIOSII 軟核處理器在化工設(shè)備——脫丁烷塔控制系統(tǒng)中的應(yīng)用。由于雙CPU 處在同一塊FPGA 芯片中,并且分擔(dān)了不同的控制環(huán)節(jié),使得整個(gè)控制系統(tǒng)與同

2009-11-27 15:40:17 6

6 分析軟處理器MicroBlaze 的體系結(jié)構(gòu),給出MicroBlaze 內(nèi)核在軟件無線電系統(tǒng)中的應(yīng)用,實(shí)現(xiàn)SOPC

2009-11-30 15:02:14 31

31 基于FPGA 的嵌入式ASIP 軟核設(shè)計(jì)與實(shí)現(xiàn)作者:李慶誠(chéng) 任健 劉嘉欣 黃寶貞 來源:微計(jì)算機(jī)信息摘要:采用ASIP+FPGA 模式設(shè)計(jì)了一款嵌入式微處理器軟核,以該軟核為例從體系結(jié)構(gòu)和

2010-02-06 10:44:40 30

30 采用ASIP+FPGA模式設(shè)計(jì)了一款嵌入式微處理器軟核,以該軟核為例從體系結(jié)構(gòu)和指令集設(shè)計(jì)兩方面對(duì)ASIP+FPGA模式微處理器軟核的設(shè)計(jì)進(jìn)行了分析和驗(yàn)證,最后通過與傳統(tǒng)微處理器對(duì)比

2010-07-28 17:41:46 17

17 什么是雙核處理器 什么是雙核處理器呢?雙核處理器背后的概念蘊(yùn)涵著什么意義呢?簡(jiǎn)而言之,雙核處理器即是基于單個(gè)半導(dǎo)體的一個(gè)處理器上擁有兩個(gè)一樣功能的處理器核

2006-10-12 09:47:11 17682

17682 摘要: 分析軟處理器MicroBlaze的體系結(jié)構(gòu),給出MicroBlaze內(nèi)核在軟件無線電系統(tǒng)中的應(yīng)用,實(shí)現(xiàn)SOPC(可編程系統(tǒng)芯片)。

關(guān)鍵詞: FPGA IP Core SOP

2009-06-20 10:47:52 3592

3592

對(duì)六核處理器的應(yīng)用測(cè)試很關(guān)鍵

談到對(duì)新六核X86處理器的升級(jí),IT專家表示,沒有什么能夠代替內(nèi)部實(shí)際應(yīng)用測(cè)試的作用。

距AMD公司發(fā)布其代號(hào)為“伊斯

2009-12-21 09:47:24 905

905 Inte Yonah雙核處理器

作為Intel首款移動(dòng)雙核處理器,Yonah將采用65nm工藝,內(nèi)部集成1.51億個(gè)晶體管,前端總線667MHz,這將對(duì)改善處理器的散

2010-01-21 11:35:30 995

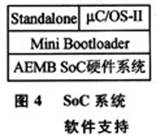

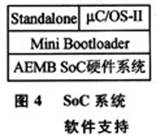

995 AEMB軟核處理器設(shè)計(jì)的SoC系統(tǒng)驗(yàn)證平臺(tái)

本文采用OpenCores組織所發(fā)布的32位微處理器AEMB作為SoC系統(tǒng)的控制中心,通過Wishbone總線互聯(lián)規(guī)范將OpenCores組織

2010-05-24 11:02:58 1040

1040

0 引言

本文采用了基于NiosⅡ軟核處理器的SOPC技術(shù)來實(shí)現(xiàn)數(shù)碼相框的設(shè)計(jì),從根本上改變了傳統(tǒng)設(shè)計(jì)方案的不足。NiosⅡ軟核嵌入式處理器是Altera公司提供的SOPC解決

2010-08-23 10:22:39 1600

1600

簡(jiǎn)單來說,雙核處理器就是在一個(gè)硅片上集成兩個(gè)CPU。那么什么是雙核處理器呢?雙核處理器背后的概念蘊(yùn)涵著什么

2010-10-08 18:21:50 1139

1139 MiC roBlaze 是Xilinx公司針對(duì)嵌入式處理器開發(fā)應(yīng)用推出的一種32位通用微處理器IP核,利用它可以進(jìn)行基于FPGA的嵌入式系統(tǒng)設(shè)計(jì)。本文結(jié)合圖像采集系統(tǒng)中對(duì)數(shù)據(jù)處理速度要求高,而系統(tǒng)

2011-05-14 17:00:51 26

26 Altera公司 (NASDAQ: ALTR)、MIPS科技公司(NASDAQ: MIPS) 以及System Level Solutions (SLS) 公司今天推出了MIPS-Based?、FPGA優(yōu)化軟核處理器,適用于Altera FPGA以及ASIC器件。

2011-06-01 09:35:53 1318

1318 本文結(jié)合具體應(yīng)用需求,介紹了利用嵌入式CPU Leon3軟核處理器對(duì)Virtex系列FPGA的配置進(jìn)行控制的方法。此系統(tǒng)能夠?qū)崿F(xiàn)FPGA配置數(shù)據(jù)的重構(gòu),并且減少了外圍CPU和CPLD器件的使用,具有很好

2011-07-04 10:13:41 3895

3895

本文闡述了一種基于NiosII 軟核處理器技術(shù)的數(shù)字式超聲探傷系統(tǒng)設(shè)計(jì)方案,與傳統(tǒng)數(shù)字式超聲探傷系統(tǒng)進(jìn)行了比較,討論了數(shù)字式超聲探傷系統(tǒng)的工作原理及NiosII 軟核處理器設(shè)計(jì)過程

2011-09-21 16:40:50 32

32 MicroBlaze嵌入式處理器軟核是Xilinx公司推出的基于fpga的微處理器,它采用32位精簡(jiǎn)指令集(RISC)哈佛總線架構(gòu),具有運(yùn)行速度快、占用資源少、可配置性強(qiáng)等優(yōu)點(diǎn)。借助Xilinx EDK(嵌入式開發(fā)

2011-11-16 11:54:22 66

66 Nios II系列軟核處理器是Altera的第二代FPGA嵌入式處理器,其性能超過200DMIPS,在Altera FPGA中實(shí)現(xiàn)僅需35美分。Altera的Stratix 、Stratix GX、 Stratix II和 Cyclone系列FPGA全面支持Nios II處理器,以

2011-11-30 16:33:33 6642

6642

本文利用Altera公司的FPGA開發(fā)工具對(duì)皋于國(guó)產(chǎn)龍芯I號(hào)處理器IP核的SoC芯片進(jìn)行ASIC流片前的系統(tǒng)驗(yàn)證,全實(shí)時(shí)方式運(yùn)行協(xié)同設(shè)計(jì)所產(chǎn)生的硬件代碼和軟件代碼,構(gòu)建一個(gè)可獨(dú)立運(yùn)行、可現(xiàn)場(chǎng)

2012-04-21 15:22:01 8784

8784

NiosII軟核處理器是Altera公司開發(fā),基于FPGA操作平臺(tái)使用的一款高速處理器,為了適應(yīng)高速運(yùn)動(dòng)圖像采集,提出了一種基于NiosII軟核處理的步進(jìn)電機(jī)接口設(shè)計(jì),使用verilog HDL語言完成該接

2012-06-12 09:09:07 43

43 電子發(fā)燒友網(wǎng)核心提示 :與其他軟核處理器相比,世界上越來越多的設(shè)計(jì)人員使用了Nios II嵌入式處理器,該處理器一直是FPGA和HardCopy ASIC設(shè)計(jì)的業(yè)界標(biāo)準(zhǔn)處理器。NiosII系列嵌入式處理器

2012-10-17 13:50:04 8129

8129 本系統(tǒng)采用經(jīng)濟(jì)型的Cyclone II FPGA芯片作為核心,基于Nios II軟核處理器,采用軟硬件結(jié)合的方式設(shè)計(jì)數(shù)碼相框并實(shí)現(xiàn)。

2013-01-08 11:07:15 9965

9965

基于NIOSⅡ嵌入式軟核處理器的LCD控制方法研究,很好的設(shè)計(jì)資料,快來學(xué)習(xí)吧。

2016-05-09 15:46:27 6

6 FPGA和Nios_軟核的語音識(shí)別系統(tǒng)的研究。

2016-05-10 10:46:40 20

20 到目前為止,我們已經(jīng)在之前的文章中聊過Zynq SOC內(nèi)部的 PS和PL,以及在Zynq SoC PS部分的ARM Cortex-A9處理器上運(yùn)行的操作系統(tǒng)。但是有一個(gè)領(lǐng)域我們還沒有去探索過,那就是在芯片的PL上構(gòu)建軟核處理器。

2017-02-08 14:04:41 1465

1465

關(guān)于GRVI Phalanx ,它是一個(gè)大規(guī)模并行RISC-V FPGA加速器,由GRVI和Phalanx結(jié)合而成。其中GRVI是一個(gè)FPGA實(shí)現(xiàn)的RISC-V RV32I軟處理器核,同時(shí)也是手工藝映射和處理元素性能/面積俱最佳的并行處理器。

2017-02-15 16:57:11 4811

4811 雙核處理器的視頻監(jiān)控系統(tǒng)設(shè)計(jì)

2017-10-26 11:12:04 12

12 PicoBlaze是8位微處理器,在Xilinx公司的Virtex、Spartan-II系列以上FPGA與CoolRunner-II系列以上的CPLD器件設(shè)計(jì)中以IP核的方式提供,使用是免費(fèi)的?。常見的版本有KCPSM3和KCPSM6。其中KCPSM支持7系列的Xilinx FPGA。

2017-11-17 20:28:01 4345

4345

設(shè)計(jì)了一款基于雙MicroBlaze軟核處理器、面向嵌入式領(lǐng)域的SOPC系統(tǒng),在信息處理繁忙的情況下,實(shí)現(xiàn)兩軟核處理器之間的同步、通信和中斷功能,提高信息吞吐率和系統(tǒng)靈活性,降低設(shè)備尺寸。兩處理器

2017-11-18 03:50:27 4439

4439

的可靠性。FPGA可使數(shù)字系統(tǒng)在線重新配置,設(shè)計(jì)更加靈活,且易于更改和升級(jí)[1-3]。更為重要的是,目前,Spartan3E系列現(xiàn)場(chǎng)可編程陣列中可以嵌入32位MicroBlaze軟核處理器。因此,利用

2018-07-16 13:09:00 2167

2167

嵌入式系統(tǒng)的核心是RISC 處理器,具有代表性的RISC軟核處理器是Nios Ⅱ處理器。軟核處理器是指用編程的方法生成的處理器。是一種將硬件邏輯、智能算法、硬件描述語言和編程有機(jī)的結(jié)合出來,設(shè)計(jì)處理器硬件電路的新技術(shù)。

2018-04-07 09:27:00 1444

1444

Altera公司的Nios嵌入式軟核處理器以其成本低廉,設(shè)計(jì)靈活等特點(diǎn),在嵌入式應(yīng)用領(lǐng)域得到了廣泛的應(yīng)用,同時(shí)LCD也越來越多地在各種儀器儀表和測(cè)控系統(tǒng)中作為人機(jī)界面和顯示模塊。本文利用SOPC技術(shù)

2018-06-04 09:44:00 1450

1450

FPGA在嵌入式設(shè)計(jì)中的應(yīng)用越來越普遍。了解怎樣采用流行的Nios? II 軟核處理器來輕松開發(fā)FPGA嵌入式系統(tǒng)軟件。

在這一5分鐘的視頻中,您將:

觀看Cyclone? III

2018-06-22 02:01:00 5267

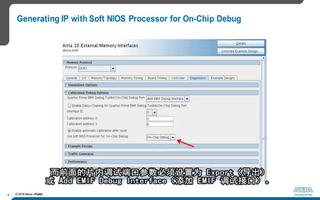

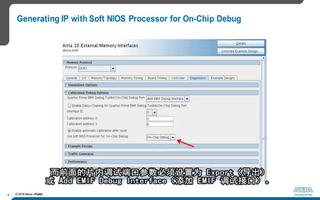

5267 使用片內(nèi)調(diào)試 Nios 軟核處理器

2018-06-20 05:53:00 3888

3888

基于Nios軟核的SoPC系統(tǒng)設(shè)計(jì)是整個(gè)系統(tǒng)硬件設(shè)計(jì)的核心,包括Nios軟核處理器的設(shè)計(jì)、數(shù)據(jù)采集控制的設(shè)計(jì)、圖像信號(hào)FFT分析的實(shí)現(xiàn)、參數(shù)顯示以及RS232通信模塊的設(shè)計(jì)等。另外,使用Nios進(jìn)行嵌入式設(shè)計(jì)在硬件上必需使用Altera公司的FPGA。

2019-08-21 14:22:37 1698

1698

Xilinx公司的MicroBlaze 32位軟處理器核是支持CoreConnect總線的標(biāo)準(zhǔn)外設(shè)集合。MicroBlaze處理器運(yùn)行在150MHz時(shí)鐘下,可提供125 D-MIPS的性能,非常適合設(shè)計(jì)針對(duì)網(wǎng)絡(luò)、電信、數(shù)據(jù)通信和消費(fèi)市場(chǎng)的復(fù)雜嵌入式系統(tǒng)。

2018-12-05 17:18:05 13

13 介紹Verilog基本語法,使用verilog編寫簡(jiǎn)單功能的電路,利用主流EDA工具進(jìn)行仿真和綜合。

第二方面,介紹處理器架構(gòu)知識(shí),揭開CPU的神秘面紗。以ARM架構(gòu)為例,透過ARMv4 架構(gòu),詳解處理器內(nèi)部組成。

2019-08-29 06:07:00 3058

3058 和Altera 公司部分FPGA 上的資源利用和性能情況。此外,基于SOPC技術(shù)將處理器軟核和CAN 控制器軟核集成在單片FPGA 中,構(gòu)建了一種新型的CAN 總線系統(tǒng),并在該系統(tǒng)中完成了對(duì)控制器軟核的測(cè)試驗(yàn)證。

2019-07-19 17:48:41 27

27 嵌入式處理器是嵌入式系統(tǒng)的核心,有硬核和軟核之分。

2019-10-18 10:36:28 7066

7066

八核處理器是什么意思?處理器是一臺(tái)電腦的大腦,它的性能直接影響著整體電腦的性能。大家對(duì)處理器了解多少,知道八核處理器是什么嗎,下面小編給大家科普一下。

2020-05-23 09:38:55 21493

21493 SOPC技術(shù),即軟核處理器,最早是由Altera公司提出來的,它是基于FPGA的SOC片上系統(tǒng)設(shè)計(jì)技術(shù)。

2021-04-15 09:48:46 10800

10800 擴(kuò)充、可升級(jí)的功能,已逐漸成為一個(gè)新興的技術(shù)方向。SoPC的核心是在FPGA上實(shí)現(xiàn)的嵌入式微處理器核,目前主要有Xilinx公司的32位軟核MicroBlaze、32位PowerPC系列處理器硬核PowerPC 405,以及Altera公司的Nios系列微處理器軟核等。

2021-06-17 11:40:52 3579

3579

SoC芯片的核心是實(shí)現(xiàn)運(yùn)算和控制功能的微處理器。LEON是一款基于SPARC V8架構(gòu)的開源微處理器IP軟核,在VHDL源代碼基礎(chǔ)上,結(jié)合具體需求加入定制的運(yùn)算單元和外設(shè)接口建立SoC系統(tǒng)。在配置靈活的LEON核上運(yùn)行Embedded Linux,提供SoC調(diào)試和測(cè)試的基本平臺(tái)。

2021-06-17 14:32:42 3523

3523

SOPC技術(shù)最早是由Altera公司提出來的,它是基于FPGA的SOC片上系統(tǒng)設(shè)計(jì)技術(shù)。是使用FPGA的邏輯和資源搭建的一個(gè)軟核CPU系統(tǒng),由于是使用F...

2022-01-26 19:03:52 2

2 在前文中,我們了解到兩種 FPGA 嵌入式處理器核方案:軟核與硬核。本文將展開討論軟核在一個(gè)基于 FPGA 通信系統(tǒng)中的應(yīng)用。軟核,由 FPGA...

2022-02-07 10:07:43 4

4 DesignStart計(jì)劃,在FPGA上搭建一個(gè)Cortex-M3軟核處理器,以Xilinx Artix-7系列FPGA為例,介紹如何定制一顆ARM Cortex-M3 SoC軟核,并添加GPIO

2022-08-30 11:14:13 4039

4039 SOPC技術(shù),即軟核處理器,最早是由Altera公司提出來的,它是基于FPGA的SOC片上系統(tǒng)設(shè)計(jì)技術(shù)。是使用FPGA的邏輯和資源搭建的一個(gè)軟核CPU系統(tǒng),由于是使用FPGA的通用邏輯搭建的CPU

2022-12-06 10:00:39 2318

2318 在FPGA中嵌入硬核處理器內(nèi)核的早期嘗試未能激發(fā)整個(gè)行業(yè)的興趣或革新技術(shù):太多,太快,也許。整個(gè)行業(yè)都回歸到軟核選項(xiàng)上,但很快就會(huì)發(fā)現(xiàn)嵌入式處理器確實(shí)存在市場(chǎng);它只需要正確的解決方案。可以說,結(jié)果證明是ARM。

2023-04-25 09:55:04 606

606 本指南提供了有關(guān) AMD Vivado Design Suite 中包含的 32 位和 64 位 MicroBlaze V 軟核處理器的信息。該文檔旨在用作為處理器硬件架構(gòu)的指南,隨附《RISC-V 指令集手冊(cè)》第一卷和第二卷。

2024-10-16 09:17:55 1628

1628

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論