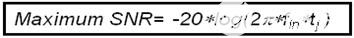

本文介紹了如何準確地估算采樣時鐘抖動,以及如何計算正確的上下整合邊界。

2012-04-01 10:19:38 2333

2333

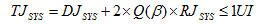

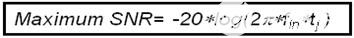

本系列文章共有三部分,第 1 部分重點介紹如何準確地估算某個時鐘源的抖動,以及如何將其與 ADC 的孔徑抖動組合。在第 2 部分中,該組合 抖動 將用于計算 ADC 的 SRN,然后將其與實際

2012-05-07 11:37:30 3382

3382

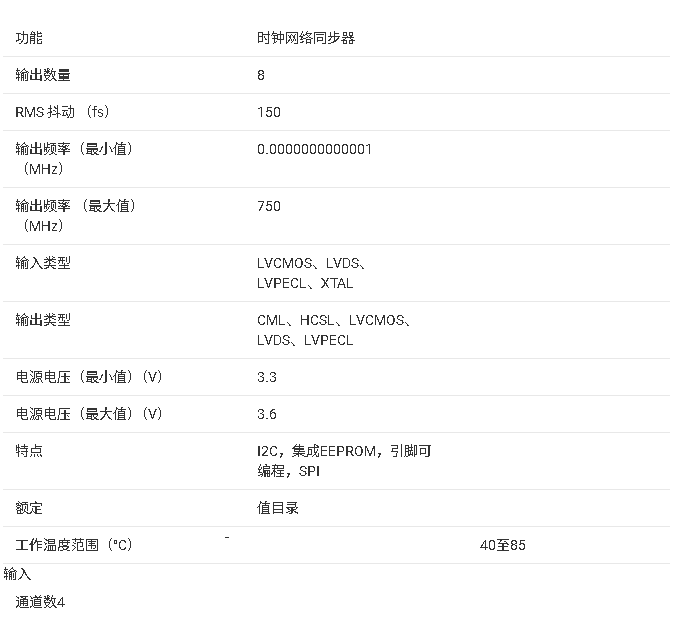

為了正確理解時鐘相關器件的抖動指標規格,同時選擇抖動性能適合系統應用的時鐘解決方案,本文詳細介紹了如何理解兩種類型時鐘驅動器的抖動參數,以及從鎖相環輸出噪聲特性理解時鐘器件作為合成器、抖動濾除功能時的噪聲特性。

2013-06-21 15:40:41 19925

19925

隨著通信系統中的時鐘速率邁入GHz級,抖動在數字設計領域中日益得到人們的重視。在高速系統中,時鐘或振蕩器波形的時序誤差會限制一個數字I/O接口的最大速率。不僅如此,它還會導致通信鏈路的誤碼率增大,甚至限制A/D轉換器的動態范圍。

2023-08-11 09:34:01 10218

10218

時鐘抖動技術適合于各種周期性的脈沖信號,典型的是電力電子設備中的PWM電壓和數字電路中的時鐘信號。

2023-09-11 10:55:34 2596

2596

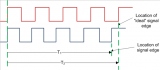

時鐘抖動是相對于理想時鐘沿實際時鐘存在不隨時間積累的、時而超前、時而滯后的偏移稱為時鐘抖動,簡稱抖動

2023-11-08 15:08:01 3278

3278

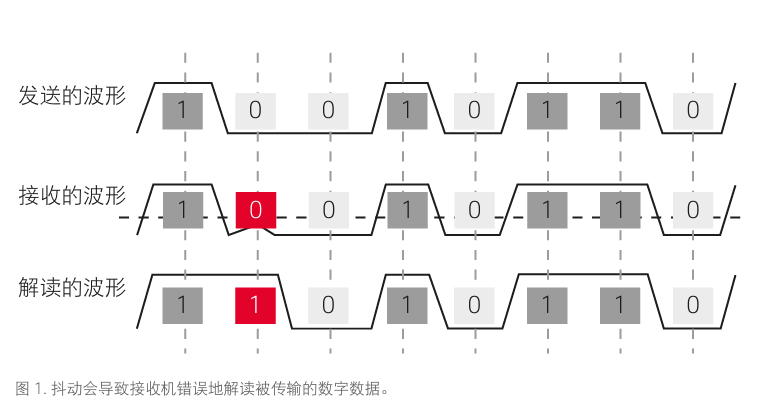

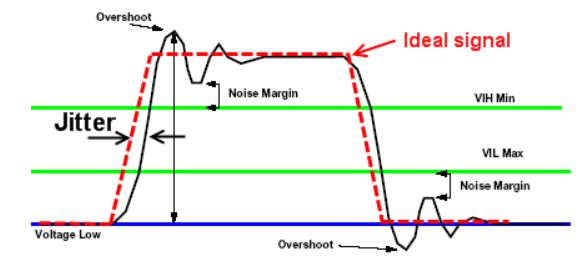

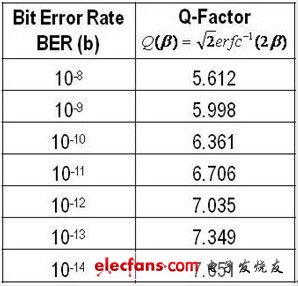

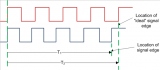

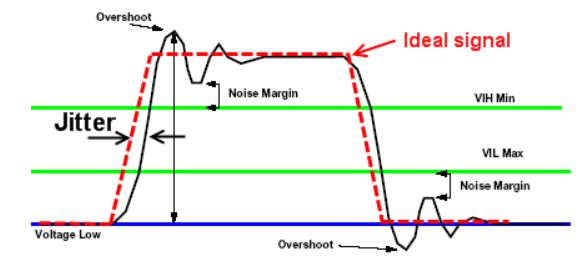

抖動的定義是“信號的各個有效瞬時對其當時的理想位置的短期性偏離。”簡單來說,抖動是指相對于其應當發生跳變的時間,信號實際跳變時有多長時間的提前或延遲。對于數字信號而言,這個有效瞬時就是信號的 跳變點

2023-11-29 18:26:23 4532

4532

秒 (fs))以保持系統性能。盡管溫度和電壓會發生變化,但它們還必須隨著時間的推移保持其低抖動規格。 一些抖動是由信號路徑噪聲和失真引起的,使用時鐘恢復和重定時技術可以在一定程度上減少抖動。然而,抖動也由時鐘源產生,時鐘源通常是一個振蕩器。這

2024-01-01 13:55:00 1813

1813

在高速光通信系統中,時鐘信號的相位穩定性與輸出結構決定了整個鏈路的同步能力與數據可靠性。傳統的CMOS單端輸出振蕩器難以滿足SerDes、CDR、PAM4調制等對低抖動與對稱輸出的要求。此背景下,集

2025-06-25 11:00:00 1837

1837

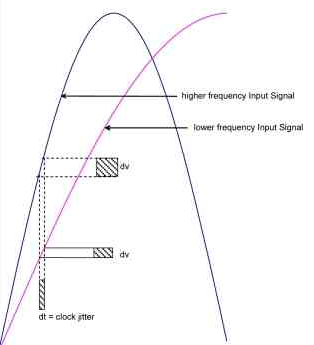

對高速信號進行高分辨率的數字化處理需審慎選擇時鐘,才不至于使其影響模數轉換器(ADC)的性能。那么時鐘抖動會對高速ADC的性能有什么影響呢?

2021-04-08 06:00:04

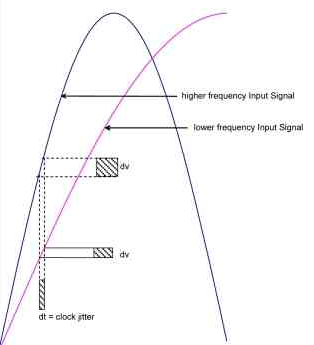

圖1強調了噪聲源而不是固有抖動會引起定時抖動錯誤。更快的邊沿速率減少了時鐘信號上的電壓噪聲對時鐘抖動性能的影響。這種現象并非是僅屬于時鐘信號的特點。在接收時鐘信號或測量抖動性能的設備內,這種機理也表現得很明顯。…

2022-11-23 07:59:49

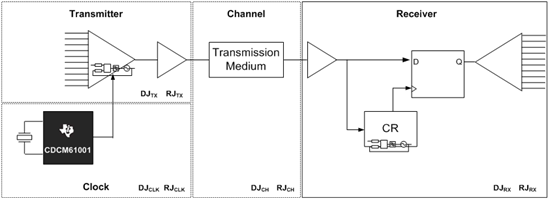

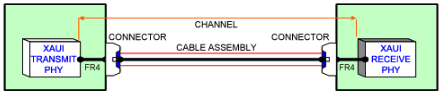

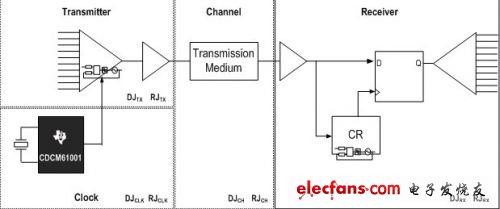

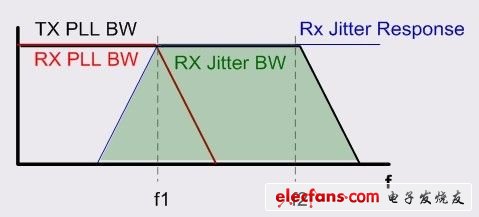

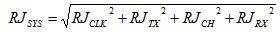

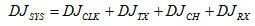

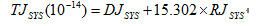

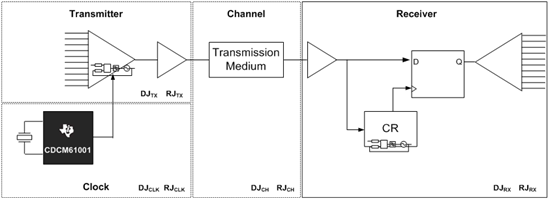

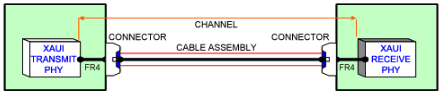

作者:John Johnson,德州儀器 本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。 用于在更遠距離對日益增長的海量數據進行傳輸的一些標準不斷出現。來自各行業的工程師們組成

2018-09-19 14:23:47

本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。 用于在更遠距離對日益增長的海量數據進行傳輸的一些標準不斷出現。來自各行業的工程師們組成了各種委員會和標準機構,根據其開發標準的目標

2022-11-23 06:59:24

的時鐘)。高速時鐘如何驅動串行鏈路?我應該在哪里連接?以上來自于谷歌翻譯以下為原文Hi all, I want to connect twoFreeware ML605 boards

2019-02-13 06:22:28

高速串行鏈路系統對信號的影響是什么?常用的補償技術有哪些?

2021-06-10 06:20:34

即可滿足 PCIe Gen1 到 Gen7 的抖動規范,適用于數據中心、服務器、存儲系統及工業高速鏈路的主時鐘分配。核心特性BAW 諧振器技術集成體聲波(BAW)諧振器,無需外部晶體或振蕩器,簡化設計并

2025-11-11 09:10:42

DN1013- 了解時鐘抖動對高速ADC的影響

2019-07-17 06:41:39

各種抖動技術規范是什么抖動的影響有哪些

2021-04-06 09:22:00

,對各種抖動技術規范的更深入理解現已變得非常重要。從 10Gb 以太網網絡到 PCIe 等高速互聯技術,鏈路中所暗含的穩健性都與降低定時裕度密切相關。簡言之,抖動就是信號邊沿與理想值或理想間隔的偏差

2018-09-13 14:29:18

的外部抖動消除時鐘每個通道的功耗最低(額定 800mW/通道)鏈路聚合將低速信號多路復用到單一的高速串行鏈路,從而有助于減少系統中的電纜或路由線跡使用 TLK10081 在系統的接收側進行解聚

2018-08-03 08:32:03

今天,我將幫助您了解如何更好地理解各種抖動技術規范。隨著高速應用中的定時要求日趨嚴格,對各種抖動技術規范的更深入理解現已變得非常重要。從 10Gb 以太網網絡到 PCIe 等高速互聯技術,鏈路中所

2022-11-21 06:02:44

模擬信號鏈的基本構建塊予以探討和研究。討論運放的一些基本應用,描述一些運放性能的指標,包括模擬信號處理以及支持這些功能所必須的器件。歡迎多提保貴意見和建議。 早在推出這本信號鏈基礎知識合集之前,我們還推出

2019-01-05 09:45:19

。這工作正常,直到我決定董事會所做的測量不夠準確(在時間軸上)。因此,我將生成的時鐘使能信號(2MHz)輸出到IO-Pin,并使用示波器測量頻率抖動。抖動似乎具有高斯分布,標準偏差約為28ns。我還測量

2020-08-19 06:09:57

連接,如圖 1 所示。請注意圖中箭頭表示信號方向。圖 1 — JESD204B TX 至 RX 鏈路的信號連接從 TX (tx_dataout) 到 RX 的信號是包含數據鏈路的串行解串器信道信號。這些

2022-11-21 07:18:42

需求。作為該最新博客系列的開篇文章,我將幫助您了解如何正確測量時鐘緩沖器的附加抖動。為什么抖動很重要?在當今數據通信、有線及無線基礎設施以及其它高速應用等高級系統中,時鐘抖動是整體系統性能的關鍵因素。要

2018-09-13 14:38:43

一塊音視頻處理芯片輸出1080i的數據Data及其同步時鐘Clk,但是時鐘clk的抖動很大,我該如何處理呢?另外,抖動很大的時鐘源能否在后面接入一個模擬鎖相環降低時鐘的抖動呢?

2018-11-12 09:12:43

時鐘抖動或結束時鐘抖動的最佳方法是什么?

2021-03-17 07:04:07

爬升到25GbE,并且允許的BER在1e-18時變為標準值,高質量、低抖動基準時鐘在保護信號完整性方面的重要性變得不可小覷。在用一個眼圖來解決鏈路無法正常運行的問題后,你現在需要確保你的設計是穩健耐用

2018-09-05 16:07:30

程度!隨著數據速率的增加,鏈路抖動允許量變得越來越嚴格。硬件工程師將主要精力放在如何使他們的整個線路卡能夠支持最大吞吐量,而為基準時鐘產生的隨機抖動分配盡可能小的允許量。針對基準時鐘,對于一條25GbE

2022-11-18 07:31:24

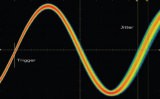

隨著數據速率的提高,時鐘抖動分析的需求也在與日俱增。在高速串行數據鏈路中,時鐘抖動會影響發射機、傳輸線和接收機的數據抖動。保證時鐘質量的測量也在不斷發展

2008-12-27 12:24:05 6

6 隨著數據速率的提高,時鐘抖動分析的需求也在與日俱增。在高速串行數據鏈路中,時鐘抖動會影響發射機、傳輸線和接收機的數據抖動。保證時鐘質量的測量也在不斷發展。目前

2009-07-07 14:01:21 20

20 DVI 接口的數據傳輸信號頻率已接近微波波段,在如此高速串行數據通訊中會表現出典型的抖動效應。DVI 接口電路設計中抖動是DVI 接口的TMDS 鏈路通訊的最為關心的問題之一,本

2009-09-25 16:55:47 41

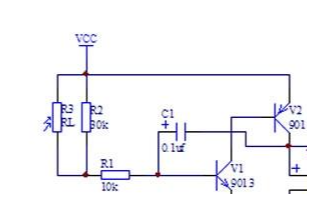

41 介紹了一種用于高速ADC 的低抖動時鐘穩定電路。這個電路由延遲鎖相環(DLL)來實現。這個DLL 有兩個功能:一是通過把一個時鐘沿固定精確延遲半個周期,再與另一個沿組成一個新

2009-11-26 15:55:15 28

28 本文主要討論采樣時鐘抖動對ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。

2009-11-27 11:24:07 15

15 高速互聯鏈路中參考時鐘的抖動分析與測量

在高速互聯鏈路中,發送器的參考工作時鐘的抖動是影響整個

2010-04-15 14:01:39 19

19 隨著新一代串行數據標準成功地從快速過渡到超高速,設計人員需要花費大量時間考慮這些高速信號的模擬設計,只是簡單關注1、0數字域信號遠遠不能滿足實際要求。為了找到潛在

2010-08-20 10:38:29 33

33 該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動指標,設計難度遠遠高于預期。關

2009-04-21 23:14:05 1036

1036

摘要:該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動指標,設計難度遠遠高于預

2009-04-22 09:35:13 410

410

摘要:這是一篇關于時鐘(CLK)信號質量的應用筆記,介紹如何測量抖動和相位噪聲,包括周期抖動、逐周期抖動和累加抖動。本文還描述了周期抖動和相位噪聲譜之間的關系,并介紹

2009-04-22 10:16:50 4761

4761

摘要:該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動指標,設計難度遠遠高于預

2009-04-25 09:54:26 638

638

摘要:該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動指標,設計難度遠遠高于預

2009-05-08 10:19:03 566

566

MAX3624 低抖動、精密時鐘發生器,提供四路輸出

概述

MAX3624是一款低抖動精密

2009-09-18 08:56:41 945

945

理解不同類型的時鐘抖動

抖動定義為信號距離其理想位置的偏離。本文將重點研究時鐘抖動,并探討下面幾種類型的時鐘抖動:相鄰周期抖動、周期抖動、時間間隔誤

2010-01-06 11:48:11 2094

2094

時鐘抖動時域分析(下):

2012-05-08 15:26:25 29

29 介紹 此應用筆記側重于不同類型的時鐘抖動。時鐘抖動是從它的時鐘邊沿偏差理想的位置。了解時鐘抖動非常重要在應用中,因為它起著關鍵作用,在時間預算一個系統。 隨著系統數據速率的增加,定時抖動成為關鍵

2017-04-01 16:13:18 6

6 歡迎繼續關注《定時決定一切》系列文章!上次我們探討了對 PLL 環路濾波器響應的理解。今天,我將幫助您了解如何更好地理解各種抖動技術規范。隨著高速應用中的定時要求日趨嚴格,對各種抖動技術規范的更深

2017-04-08 04:56:31 1217

1217

了解高速ADC時鐘抖動的影響將高速信號數字化到高分辨率要求仔細選擇一個時鐘,不會妥協模數轉換器的采樣性能(ADC)。 在這篇文章中,我們希望給讀者一個更好的了解時鐘抖動及其影響高速模數轉換器的性能

2017-05-15 15:20:59 13

13 時鐘抖動時域分析,第 2 部分

2017-10-26 16:10:42 6

6 時鐘抖動時域分析 第 3 部分

2017-10-26 16:13:28 4

4 時鐘產生抖動(jitter)會使發生抖動的時鐘信號與未發生抖動的時鐘信號在時域上存在偏差,從而使模數轉換器的采樣頻率發生紊亂,最終導致模數轉換器采樣的不穩定性,使輸出信號存在頻譜毛刺,導致誤碼率上升

2017-11-11 18:22:26 9

9 本文主要討論采樣時鐘抖動對 ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。 ADC 是現代數字解調器和軟件無線電接收機中連接模擬信號處理部分和數字信號處理部分的橋梁,其性能在很大程度上決定了

2017-11-27 14:59:20 18

18 時鐘配有體聲波(BAW)諧振器,適用于400 Gbps鏈路,能幫助系統以更高的速度傳輸更多數據,同時提供比同類產品更高的系統抖動裕量。

2019-06-20 11:37:03 4650

4650 時鐘設計人員通常會提供一個相位噪聲,但不提供抖動規格。相位噪聲規格可以轉換為抖動,首先確定時鐘噪聲,然后通過小角度計算將噪聲與主時鐘噪聲成分進行比較。相位噪聲功率通過計算圖9中的灰色區域積分得出。

2019-08-20 11:06:53 9314

9314

時鐘抖動性能主題似乎是時鐘,ADC和電源的當前焦點供應廠家。理由很清楚;時鐘抖動會干擾包括高速ADC在內的數字電路的性能。高速時鐘可以對它們所接收的功率的“清潔度”非常敏感,盡管量化關系需要一些努力。

2019-09-14 11:24:00 9399

9399

本文針對全方位的信號路徑系統中的高速全差分運放及高頻寬14位模擬/數字轉換器的隨機及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術。研究選用雙級聯PLLatinum架構,配置高性能壓控振蕩器(VCXO),很好地實現了降噪和時鐘抖動濾除的作用。

2020-09-23 10:45:00 2

2 對高速信號進行高分辨率的數字化處理需審慎選擇時鐘,才不至于使其影響模數轉換器(ADC)的性能。借助本文,我們將使讀者更好地理解時鐘抖動問題及其對高速ADC性能的影響。

2020-08-20 14:25:16 1408

1408

信號與時序的變化會導致接收信號與理想信號略有不同,這被稱為抖動。抖動不會引起信號幅度的變化。由于抖動引起的變化在于信號相位,寬度和周期。這是一個有害因素,可能導致串行鏈路的誤碼率增加。由于設計的簡化

2021-02-20 14:20:50 9052

9052

AD9524:帶6路差分或13路LVCMOS輸出的抖動凈化器和時鐘發

2021-03-19 07:03:02 10

10 AD9525: 8路LVPECL輸出低抖動時鐘發生器

2021-03-21 15:00:20 0

0 電子發燒友網為你提供相位噪聲處理:時鐘抖動或結束時鐘抖動的最佳方法是什么?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:49:06 26

26 高速ADC使用外部輸入時鐘對模擬輸入信號進行采樣,如圖1所示。圖中顯示了輸入采樣時鐘抖動示意圖。 圖1、ADC采樣 輸入模擬信號的頻率越高,由于時鐘抖動導致的采樣信號幅度變化越大,這點在圖2中顯示的非常明顯。輸入信號頻率為F2=100MHz時,采樣幅度變化如圖紅色虛

2021-04-07 16:43:45 10607

10607

超低抖動時鐘的產生與分配

2021-04-18 14:13:51 8

8 ADC時鐘接口中的最小抖動

2021-05-09 12:19:40 6

6 DN1013-了解時鐘抖動對高速ADC的影響

2021-05-11 18:22:19 0

0 作者:John Johnson,德州儀器?

?

本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。

?

用于在更遠距離對日益增長的海量數據進行傳輸的一些標準不斷出現。來自

2021-11-22 15:52:21 2117

2117

PCIe 和網絡時鐘抖動測量之間的另一個顯著差異在圖 2 中并不明顯。數字采樣示波器 (DSO) 用于獲取時鐘周期或波形文件以計算 PCIe 時鐘抖動,而不是 PNA。造成這種情況的主要原因是 PCIe 時鐘支持擴頻,而網絡時鐘不支持,而且從歷史上看,PNA 一直無法使用正在擴頻的時鐘。

2022-05-05 15:50:44 7109

7109

超低抖動時鐘發生器如何優化串行鏈路系統性能

2022-11-04 09:50:15 0

0 時鐘抖動使隨機抖動和相位噪聲不再神秘

2022-11-07 08:07:29 4

4 時鐘抖動解秘—高速鏈路時鐘抖動規范基礎知識

2022-11-07 08:07:30 2

2 對于頻率成分相對較低的輸入信號,例如在1MHz以下,時鐘抖動變得不那么重要,但是當輸入信號的頻率為幾百兆赫茲時,時鐘上的抖動將成為誤差的主要來源,并且將成為SNR的限制因素。

2023-01-03 14:35:04 2164

2164

在設計中使用超快速數據轉換器的高速應用通常需要非常干凈的時鐘信號,以確保外部時鐘源不會對系統的整體動態性能產生不需要的噪聲。因此,選擇合適的系統組件至關重要,這有助于產生低相位抖動時鐘。以下應用筆記可作為選擇合適的元件的寶貴指南,以設計適用于超快速數據轉換器的基于PLL的低相位噪聲時鐘發生器。

2023-02-25 10:50:48 4207

4207

,設計人員還必須檢查其設計的參數化領域。信號完整性(SI)工程師必須減輕或消除時序抖動對系統性能的影響。以下討論提供了一個簡單實用的過程,用于表征1Gbps及以上的高速串行數據鏈路。

2023-03-08 14:10:00 1878

1878

1.1.1.??抖動定義和分類 ITU-T G.701對抖動的定義為:“抖動是指數字信號在短期內相對于理想位置發生的偏移重大影響的短時變化”。 對于真實物理世界中的時鐘源,比如晶振、DLL、PLL,它們的時鐘輸出周期都不可能是一個單點的固定值,而是隨時間而變化的

2023-03-10 14:54:32 1847

1847

抖動和相位噪聲是晶振的非常重要指標,本文主要從抖動和相位噪聲定義及原理出發,闡述其在不同場景下對數字系統、高速串行接口、數據轉換器和射頻系統的影響。

2023-03-26 09:09:11 1867

1867

高速串行鏈路的表征取決于SI工程師發現、理解和解決嚴重抖動問題的能力。在本討論中,我們假設 PHY(物理層)或 SerDes(串行器-解串器)設備的時鐘和數據恢復 (CDR) 模塊符合適用于該設備

2023-04-03 11:27:21 2407

2407

系統時序設計中對時鐘信號的要求是非常嚴格的,因為我們所有的時序計算都是以恒定的時鐘信號為基準。但實際中時鐘信號往往不可能總是那么完美,會出現抖動(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 5281

5281 隨著數據速率的增加,鏈路抖動允許量變得越來越嚴格。硬件工程師將主要精力放在如何使他們的整個線路卡能夠支持最大吞吐量,而為基準時鐘產生的隨機抖動分配盡可能小的允許量。針對基準時鐘,對于一條25GbE

2023-04-17 10:37:30 1249

1249

) 以及其他通常要求時域抖動規范(如周期)的應用生成時鐘- 周期和周期抖動。 然而,對于串行解串器 (SerDes)、千兆以太網 (GbE)、10 GbE、同步光網絡/同步數字體系 (SONET/SDH) 和光纖通道等高速接口,情況就不同了。有嚴格的頻域抖動要求。 為了正常運行,這些高速接口依賴于低頻

2023-05-26 22:15:02 3574

3574 首先,我們需要理解什么是時鐘抖動。簡而言之,時鐘抖動(Jitter)反映的是時鐘源在時鐘邊沿的不確定性(Clock Uncertainty)。

2023-06-02 09:09:06 3288

3288

理想值附近的一個范圍內,從而造成相鄰的時鐘邊沿存在偏差。在時序分析時,時鐘抖動是一個重要的因素。多種因素會導致時鐘抖動,包括PLL回路噪聲、電源紋波、熱噪聲以及信號之間的串擾等。

2023-06-09 09:40:50 3109

3109

本文主要介紹了時鐘偏差和時鐘抖動。

2023-07-04 14:38:28 3231

3231

電子發燒友網站提供《時鐘抖動對ADC性能有什么影響.pdf》資料免費下載

2023-11-28 10:24:10 1

1 ,通常低于 100 飛秒 (fs),以保持系統性能。這些時鐘還必須長期保持低抖動規格,且不受溫度和電壓的影響。 某些抖動是由信號路徑噪聲和失真引起的,使用重復時鐘和重定時技術可以在一定程度上減少抖動。不過,抖動也是由時鐘源產生的,時鐘源通常是振蕩器。這是由于各

2024-02-13 17:47:00 2102

2102

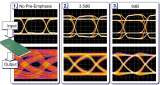

。均衡(Equalization)就是為了應對ISI抖動,而被廣泛應用的黑科技。既然ISI抖動的根源,是傳輸鏈路對不同頻率信號損耗的差異,均衡就是要想辦法補償掉這個差異,讓不同頻率信號的幅度都能保持均勻。根據均衡技術所使用的位置,一般分為發送端均衡(Tx EQ)和接收端均衡(Rx EQ)。

2024-07-03 10:00:14 1987

1987

在《做信號鏈,你需要了解的高速信號知識(一)》中,我們探討了LVDS和JESD204B標準的優勢,這些標準在高速信號傳輸中提供了更高的速率、更低的功耗和更好的抗干擾能力。接下來,我們將深入探討高速信號傳輸中的抖動和眼圖挑戰。

2024-07-03 10:29:59 3442

3442

時鐘抖動(Clock Jitter)是時鐘信號領域中的一個重要概念,它指的是時鐘信號時間與理想事件時間的偏差。這種偏差不僅影響數字電路的時序性能,還可能對系統的穩定性和可靠性造成不利影響。以下是對時鐘抖動工作原理的詳細闡述,內容將圍繞其定義、類型、產生原因、影響及應對措施等方面展開。

2024-08-19 17:58:11 5343

5343 在FPGA(現場可編程門陣列)設計中,消除時鐘抖動是一個關鍵任務,因為時鐘抖動會直接影響系統的時序性能、穩定性和可靠性。以下將詳細闡述FPGA中消除時鐘抖動的多種方法,這些方法涵蓋了從硬件設計到軟件優化的各個方面。

2024-08-19 17:58:54 3753

3753 時鐘抖動和相位噪聲是數字系統和通信系統中兩個至關重要的概念,它們之間存在著緊密而復雜的關系。以下是對時鐘抖動和相位噪聲關系的詳細探討,旨在全面解析兩者之間的相互作用和影響。

2024-08-19 18:01:57 2380

2380 時鐘抖動(Jitter)和時鐘偏移(Skew)是數字電路設計中兩個重要的概念,它們對電路的時序性能和穩定性有著顯著的影響。下面將從定義、原因、影響以及應對策略等方面詳細闡述時鐘抖動和時鐘偏移的區別。

2024-08-19 18:11:30 3230

3230 通過上一期我們了解到:數字電子產品中電源軌噪聲和時鐘抖動是有關聯的,以及測量電源軌噪聲的方案,接下來我們基于實際測量,揭示電源軌噪聲對系統時鐘抖動的影響。

2024-11-22 16:11:22 1176

1176

14路差分輸出時鐘抖動消除器SC6302,兼容HMC7044

2025-03-05 10:18:43 785

785

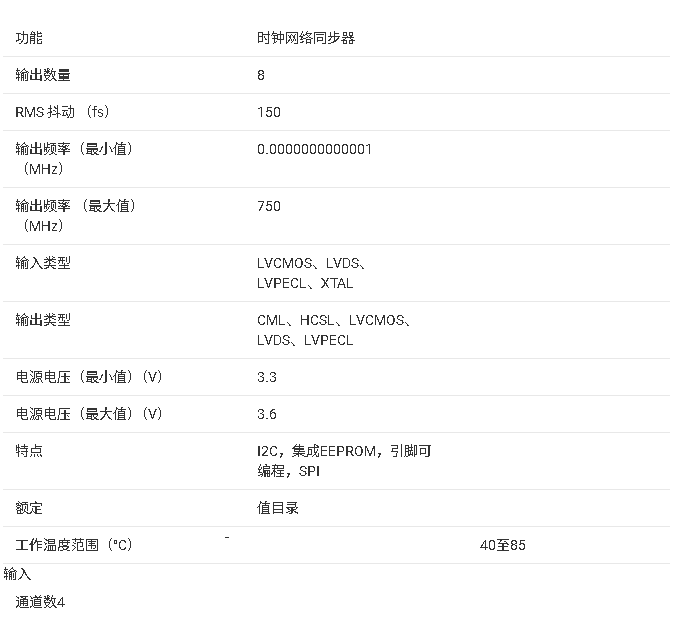

該LMK05318是一款高性能網絡同步器時鐘器件,可提供抖動清除、時鐘生成、高級時鐘監控和卓越的無中斷開關性能,以滿足通信基礎設施和工業應用的嚴格時序要求。該器件的超低抖動和高電源噪聲抑制 (PSNR) 可降低高速串行鏈路中的誤碼率 (BER)。

2025-09-12 13:49:59 687

687

該LMK05028是一款高性能網絡同步器時鐘器件,可提供抖動清除、時鐘生成、高級時鐘監控和良好的無中斷開關性能,以滿足通信基礎設施和工業應用的嚴格時序要求。該器件的低抖動和高PSNR降低了高速串行鏈

2025-09-12 14:18:25 862

862

電子發燒友App

電子發燒友App

評論