作者:John Johnson,德州儀器

本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。

用于在更遠距離對日益增長的海量數據進行傳輸的一些標準不斷出現。來自各行業的工程師們組成了各種委員會和標準機構,根據其開發標準的目標(數據吞吐量和通信距離)確定抖動預算;同時還要考慮到組成通信鏈路的模塊的局限性。

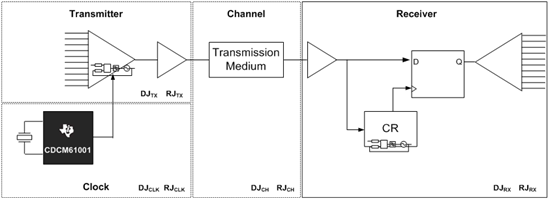

圖 1 通信鏈路—抖動組件

圖 1 顯示了集成有一個嵌入式時鐘的典型高速通信鏈路。每個子系統(時鐘、發送器、通道和接收機)都會對整體抖動預算的增加產生影響。子系統抖動包括一個決定性 (DJ) 組件和一個隨機組件 (RJ),如圖 1 所示。為了實現可接受的通信效果,必須滿足下列條件:

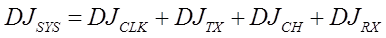

方程式 1

方程式 1

其中:TJSYS 是總抖動,而 1UI 為1個單位時間間隔(1 比特時間)

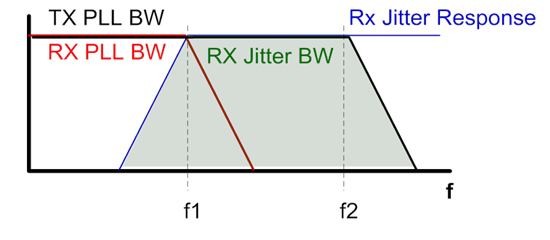

總抖動 (TJ) 包括每個子系統決定性抖動和隨機抖動的和。由于隨機抖動自身的屬性,進行這種求和時需要特別注意。隨機抖動呈現高斯(隨機)分布,并且無邊界。因此,隨機抖動可表示為一個 RMS 值,并且在規定測量/整合帶寬范圍內對其進行估算。例如,圖 1 所示接收機的抖動測量帶寬便為 f2 - f1(參見圖 2)。這是因為接收機鎖相環路 (PLL) 追蹤 f1 以下的抖動(從而排斥它),而發射 PLL 的頻率上限為 f2。從接收機的角度來看,使鏈路性能降低的隨機抖動降至這些限制之間。

圖 2 高速通信鏈路—隨機抖動測量帶寬

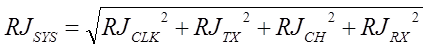

由于隨機抖動是隨機過程產生的結果,系統總隨機抖動的計算需要進行方和根 (RSS) 計算,如方程式2所示:

方程式 2

決定性抖動源和的計算很簡單:

方程式 3

方程式 3

最后,可對系統總抖動進行估算,由此可以實現鏈路預算;但是,還需要做更多的工作。這種計算涉及統計數學。需要用到一種被稱之為 Q 因數的參數(參見表 1)。Q 因數的大小具體取決于誤碼率 (BER),同時還要根據鏈路性能/可靠性目標來選擇。由于隨機抖動的無邊界屬性,(最終)會出現誤碼。例如,10-8 的 BER 意味著,每發送 100,000,000 比特便會有一個比特被錯誤解釋。現代的通信系統通常會要求一個達到或者超過 10-12 以上的 BER。

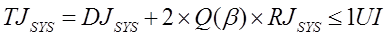

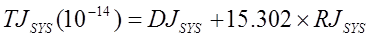

系統總抖動(以及鏈路預算)可使用方程式 4 計算得到:

方程式 4

方程式 4

例如,10-14 的 BER 時,總抖動為:

方程式 5

方程式 5

本文討論了構成總抖動預算的一些參數。下一次,我們將探討時鐘,并研究隨機抖動和相位噪聲之間的關系。

編輯:jq

-

嵌入式

+關注

關注

5198文章

20442瀏覽量

333979 -

模擬

+關注

關注

7文章

1447瀏覽量

85378 -

時鐘

+關注

關注

11文章

1971瀏覽量

134984

發布評論請先 登錄

LMK04000 系列時鐘抖動清理器:高精度時鐘解決方案深度剖析

CDCLVD2106:高性能雙路 1:6 低附加抖動 LVDS 時鐘緩沖器的深度解析

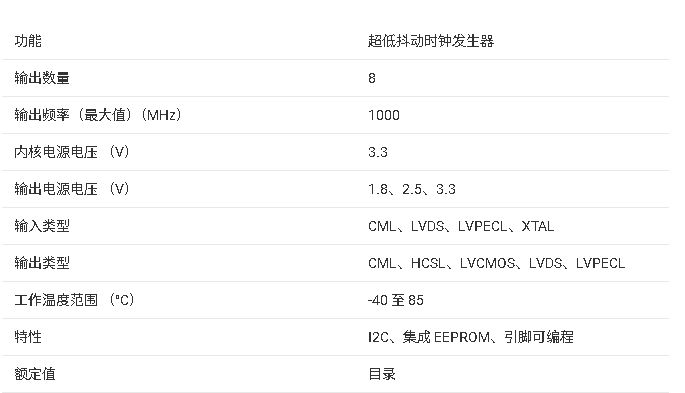

LMK3H2104超低抖動時鐘發生器

SN65LVCP15:高速串行鏈路的理想選擇

高速光模塊時鐘解決方案:YSO233UJ通過高基頻光刻工藝實現超低抖動與高頻率穩定性

LMK03318 具有單 PLL 的超低抖動時鐘發生器系列技術手冊

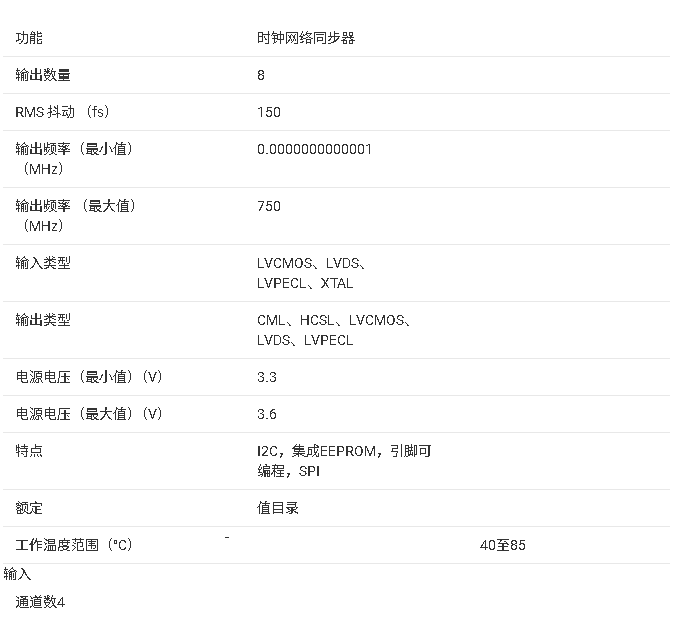

?LMK05028 低抖動雙通道網絡同步器時鐘芯片總結

LMK05318 帶BAW的超低抖動單通道網絡同步器時鐘技術手冊

差分輸出 × 超低抖動:打造高速穩定的大型數據同步時脈

差分輸出VCXO:低抖動時鐘源助力光通信系統精密同步

AD9547雙路/四路輸入網絡時鐘發生器/同步器技術手冊

高速鏈路時鐘抖動規范基礎知識

高速鏈路時鐘抖動規范基礎知識

評論