PCI SIG 于 2017 年 9 月批準了 PCIe Gen4 規范的 1.0 版。PCIe Gen5 規范于 2018 年 4 月底移至 0.7 版,并計劃在 2018 年 9 月發布 0.9 版。Gen5 規范的發展速度要快得多比他們為 Gen4 所做的。如今,大多數新設計活動都集中在 PCIe Gen3 或 Gen4 上,現在深入研究 PCIe Gen5 設計還為時過早,因此我們暫時將重點放在 PCIe Gen3 和 Gen4 上。

在我們深入研究之前,我想指出 PCIe Gen4 的一個有益特性是時鐘抖動的計算與 Gen3 相同。唯一的區別是 PCIe Gen4 抖動限制為 500fs rms,而不是 Gen3 的 1ps rms。這意味著,如果您使用 PCIe Gen3 計算來計算時鐘抖動并且您的結果小于 500fs rms,那么您可以將時鐘用于 PCIe Gen4。

PCI Express 時鐘的相位噪聲測量技術與用于網絡時鐘的技術有很大不同。本博文的其余部分對兩者進行了比較和對比。

讓我們從常用的 12kHz – 20MHz 磚墻濾波器開始,該濾波器通常與相位噪聲分析儀 (PNA) 一起用于測量網絡時鐘,參見圖 1。線性垂直刻度以 dBc/Hz 為單位(每個頻率下相對于載波的分貝)和對數水平刻度以赫茲為單位。對于 PCIe 時序,載波是 100MHz 時鐘。以太網時鐘通常使用 156.25MHz。

簡單檢查表明,在 12kHz 和 20MHz 之間的“通帶”沒有衰減,如 0dBc 處的水平線所示。12kHz 和 20MHz 處的垂直線完全衰減了通帶外的頻率。我們將這些垂直線稱為“磚墻”過濾器。這意味著抖動計算包括通帶區域內的所有噪聲并排除通帶外的所有噪聲。該濾波器對通帶中的所有噪聲內容同樣敏感。

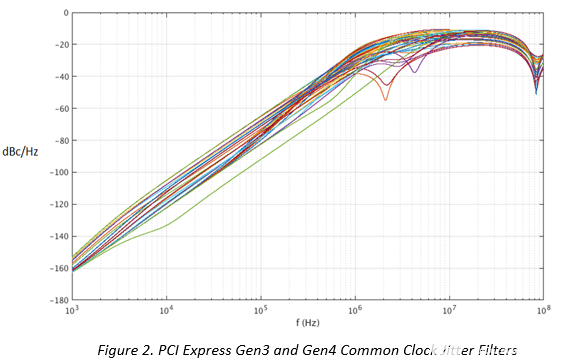

圖 2 說明了在計算抖動之前應用于 PCIe 時鐘抖動的濾波器組合。PCIe Gen3 和 Gen4 時鐘抖動是應用 64 個濾波器組合后獲得的最差值。這個最差值必須小于規范限制。

檢查圖 2 可以看出與圖 1 的 12kHz – 20MHz 濾波器的顯著差異。最明顯的差異是沒有磚墻。相反,在 1MHz 以下有 20dB/decade 的衰減。(注意:十年是對數刻度上的 10 的冪 [104 到 105、105 到 106])。這種衰減適用于常見的時鐘系統,因為我們假設低頻噪聲很常見,并且我們指定所有 PLL(時鐘 PLL 和 TX/RX PLL)來跟蹤它。這意味著 PCIe Gen3 和 Gen4 通用時鐘系統對低頻時鐘抖動的敏感度低于網絡系統。這也是為什么用于普通時鐘系統的非常好的 PCIe 時鐘通常具有相對較高的 12kHz – 20MHz 相位抖動數。這也是為什么為通用時鐘系統指定的時鐘不一定在單獨的時鐘系統中使用的原因。

下一個要注意的事項是濾波器通過了 1MHz 以上的大部分噪聲,實際上濾波器在 1MHz 以上相當平坦。這意味著 PCIe Gen3 和 Gen4 通用時鐘時序對 1MHz 以上的抖動最為敏感。

PCIe 和網絡時鐘抖動測量之間的另一個顯著差異在圖 2 中并不明顯。數字采樣示波器 (DSO) 用于獲取時鐘周期或波形文件以計算 PCIe 時鐘抖動,而不是 PNA。造成這種情況的主要原因是 PCIe 時鐘支持擴頻,而網絡時鐘不支持,而且從歷史上看,PNA 一直無法使用正在擴頻的時鐘。

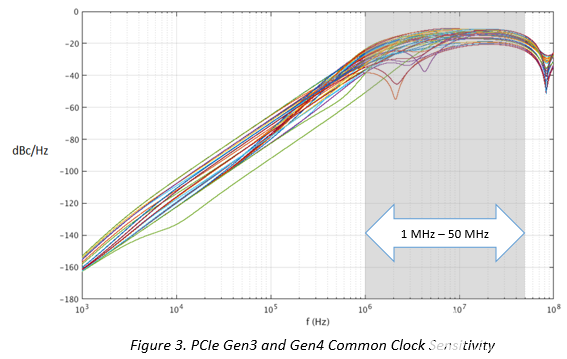

根據 Nyquist,對信號進行采樣的行為將所有信息混疊到 f/2。對于 100MHz PCIe 時鐘,這意味著從 DSO 獲得的文件包含高達 50MHz 的有用信息。這也意味著基于 DSO 數據的 PCIe 時鐘抖動計算一直計算到 50MHz!盡管濾波器在 1MHz 以上大約 -20dBc,但 PCIe Gen3 和 Gen4 通用時鐘抖動在 1MHz 到 50MHz 的范圍內最為敏感,如圖 3 所示。

審核編輯:郭婷

-

濾波器

+關注

關注

162文章

8412瀏覽量

185725 -

示波器

+關注

關注

113文章

7075瀏覽量

196087 -

PCIe

+關注

關注

16文章

1461瀏覽量

88428

發布評論請先 登錄

LMK5B12212網絡同步器:以太網網絡應用的高性能解決方案

LMK3H2104超低抖動時鐘發生器

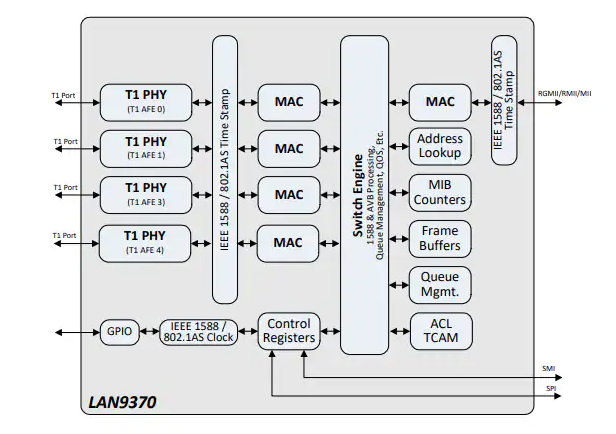

LAN9370汽車級以太網交換機芯片技術解析

WiFi和以太網哪個更快

以太網入門:從零開始,掌握以太網基礎知識!

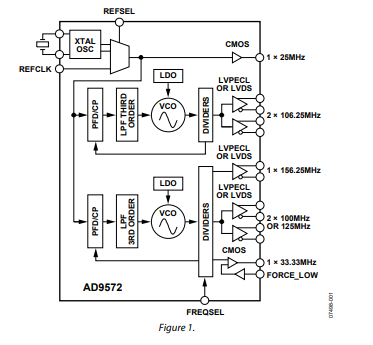

AD9572光纖通道/以太網時鐘發生器IC,PLL內核,分頻器,7路時鐘輸出技術手冊

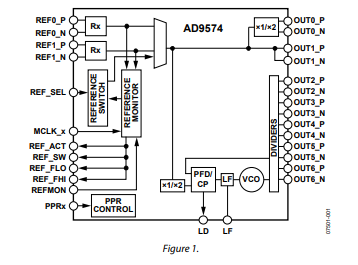

AD9574以太網 千兆以太網時鐘發生器技術手冊

以太網與現場總線技術區別詳解

愛普生SG2520CAA有源晶振賦能車身以太網 PHY

廣成科技CAN轉以太網模塊的作用和應用

比較和對比PCIe和以太網時鐘抖動規范

比較和對比PCIe和以太網時鐘抖動規范

評論