凱芯Cascade 64Mbit pSRAM CSL6408SB-A4為醫療手環提供高密度低功耗存儲方案,支持200MHz高速數據緩存,待機電流低至1.8μA。其工業級溫度范圍與ECC糾錯能力保障生命體征數據可靠存儲,助力設備實現長效續航與臨床級監測精度。

2025-12-09 09:21:00 357

357

工業數據中臺完全支持接入MySQL數據庫 ,且通過數據同步、集成與治理等技術手段,能夠充分發揮MySQL在數據存儲與事務處理方面的優勢,同時彌補其在數據分析與共享能力上的不足,具體分析如下: 技術

2025-12-04 11:23:34 287

287

使用DMA將數據從FLASH傳輸到SRAM

下載示例

演示AT32F系列使用DMA將數據從FLASH傳輸到SRAM的使用方法。

注:本例程對應的代碼是基于雅特力提供的V2.x.x 板級支持包

2025-12-03 16:26:37

嚴苛的場景。MD6639若需替代TI或ADI的同類電源管理芯片,需根據具體參數和應用場景篩選,ADI的LTM46xx系列(如LTM4661)在高頻、高集成度場景中更具優勢,而TI的TPS54xxx系列

2025-12-02 09:19:08

在各類電子設備與嵌入式系統中,存儲器的性能與功耗表現直接影響著整體設計的穩定與效率。低功耗SRAM,特別是異步SRAM系列,憑借其出色的能效比與高可靠性,正成為越來越多工業控制、通信設備及便攜終端中的關鍵部件。

2025-11-25 15:42:56 271

271

通過標準I/O操作磁盤文件時,為了減少系統調用的次數,標準I/O函數會將用戶讀取或寫入文件的數據緩存在stdio緩沖區,然后再一次性將stdio緩沖區中緩存的數據通過調用系統調用系統I/O寫入到系統I

2025-11-19 16:24:10

、英尚微電子代理的高性能PSRAM芯片——EMI164LA16LM-70I,是一款專為現代智能設備設計的高性能存儲解決方案,在市場應用中得到了良好的反饋。

2025-11-18 17:24:35 255

255 DRAM利用電容存儲數據,由于電容存在漏電現象,必須通過周期性刷新來維持數據。此外,DRAM采用行列地址復用設計,提高了存儲密度,但增加了控制復雜性。它廣泛用于大容量、低成本存儲場景,如計算機內存。

2025-11-18 11:49:00 477

477 在現代高性能電子系統中,存儲器的讀寫速度往往是影響整體性能的關鍵因素之一。同步SRAM(Synchronous Static Random Access Memory)正是在這一需求下發展起來的重要

2025-11-18 11:13:01 242

242 和size參數,可以分別指定兩個參數為NULL和0。標準錯誤stderr默認屬于這一種類型,從而保證錯誤信息能夠立即輸出。

? _IOLBF:采用行緩沖I/O。當在輸出或輸入中遇到換行符\"

2025-11-14 09:02:30

在處理器性能持續攀升的今天,存儲系統的速度已成為制約整體算力的關鍵瓶頸之一。作為最接近CPU核心的存儲單元,SRAM(靜態隨機存取存儲器)承擔著高速緩存的重要角色,其性能直接影響數據處理效率。當前

2025-11-12 13:58:08 455

455 PSRAM(偽靜態隨機存儲器)是一種兼具SRAM接口協議與DRAM內核架構的特殊存儲器。它既保留了SRAM無需復雜刷新控制的易用特性,又繼承了DRAM的高密度低成本優勢。這種獨特的設計使PSRAM在嵌入式系統和移動設備領域獲得了廣泛應用。

2025-11-11 11:39:04 497

497 型的調試工具來實時監控內存使用情況。

是否有其他方法(例如構建報告、SDK 功能或EZ-USB? Suite 內的工具)可以讓我檢查固件使用了多少 SRAM?

2025-11-11 06:33:59

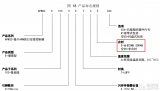

景中實現對德州儀器(TI)和安世半導體(Nexperia)等品牌的有效替代。長晶代理商南山電子將基于長晶科技目前量產的緩沖器產品,詳細介紹其型號、性能參數、封裝形

2025-11-07 17:18:33 728

728

電子發燒友網站提供《DDR3 SDRAM參考設計手冊.pdf》資料免費下載

2025-11-05 17:04:01 4

4 在有些情況下,我們想要把代碼放到SDRAM運行。下面介紹在APM32的MCU中,如何把代碼重定位到SDRAM運行。對于不同APM32系列的MCU,方法都是一樣的。

2025-11-04 09:14:18 4981

4981

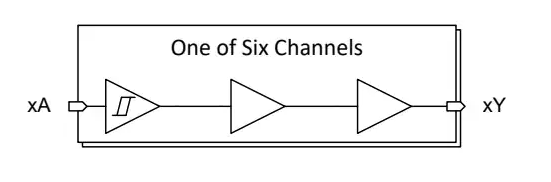

時鐘緩沖器廣泛應用于各種電子系統中,以下是一些典型的應用場景:1.通信設備:在高速通信設備中,時鐘信號的質量直接影響數據傳輸的準確性。時鐘緩沖器通過優化信號完整性,確保通信系統的穩定性和可靠性。2.

2025-10-30 14:12:01 290

290

OV7725 輸出時序中,只有當 HREF 為高電平時,PCLK 驅動下 D[0:7]線表示的才是有效像素數據,因此,利用 HREF 控制 FIFO 的 WE 可以確保只有有效數據才被寫入到 FIFO

2025-10-29 23:11:06

凱芯CascadeTeq CSS6404SU-L是一款64Mb QSPI pSRAM,采用串行接口實現高帶寬數據傳輸,工作電壓2.7-3.6V,時鐘頻率達133MHz。適用于物聯網、便攜設備和工業控制等需要高速緩存的嵌入式場景。

2025-10-28 09:25:00 332

332

PSRAM全稱為pseudo SRAM,一般叫偽靜態SRAM,串行PSRAM具有類似SRAM的接口協議,給出地址,讀、寫命令,就可以實現存取,不同于DRAM需要用到memory controller來控制內存單元定期數據刷新

2025-10-27 16:04:47 450

450 非揮發性存儲器,如NAND、NOR Flash,數據在掉電后不會丟失。這類存儲器通常速度比較慢,可以做資料和大數據存儲。

2025-10-27 15:14:39 310

310 在存儲解決方案中,外置SRAM通常配備并行接口。盡管并口SRAM在數據傳輸率方面表現卓越,但其原有的局限性也日益凸顯。最明顯的挑戰在于物理尺寸:不論是占用的電路板空間或是所需的引腳數量,并行接口都

2025-10-26 17:25:18 835

835 QSPI PSRAM是一種集成了QSPI接口與PSRAM存儲功能的高效芯片。QSPI(四線串行外設接口)是一種高速串行通信接口,用于連接外部設備;而PSRAM(偽靜態隨機存儲器)則結合了快速隨機訪問與動態存儲的特性。

2025-10-23 15:40:17 379

379 PSRAM之所以被稱為"偽靜態"存儲器,主要是因為其采用類SRAM的接口協議:只需要提供地址和讀寫命令就可以實現數據存取,無需像傳統DRAM一樣需要內存控制器定期刷新數據單元。

2025-10-23 14:29:00 296

296 、建立讀寫操作、配置地址計數器、模擬數據流、綜合與仿真以及下載到FPGA進行硬件測試。通過實踐,掌握SRAM在FPGA中的使用和基本讀寫方法,加深對FPGA工作原理的理解。

2025-10-22 17:21:38 4118

4118

愛普科技256Mb PSRAM(如APS256XXN-OBR-BG)為WiSUN無線模塊提供高速數據緩存與臨時存儲解決方案,其166MHz速率、1.8V低功耗及小尺寸封裝顯著提升模塊在智能電網、工業自動化中的多任務處理能力和穩定性。

2025-10-14 09:25:00 265

265

keil+Env怎么把很大的數組定義到SDRAM中?

RTT自帶的SDRAM程序運行正常,能夠申請里面的空間。

但是沒有辦法把很大的數組——ltdc_lcd_framebuf[1280][800]

定義到SDRAM中,一運行就出錯,請問各位大佬怎么解決啊?

2025-10-11 16:10:01

。CDCDB400是一款DB800ZL衍生緩沖器,符合或超過DB800ZL中的系統參數規格。該器件還符合或超過了DB2000Q規格中的參數。Texas Instruments CDCDB400采用5mm × 5mm 32引腳VQFN封裝。

2025-10-06 15:28:00 1218

1218

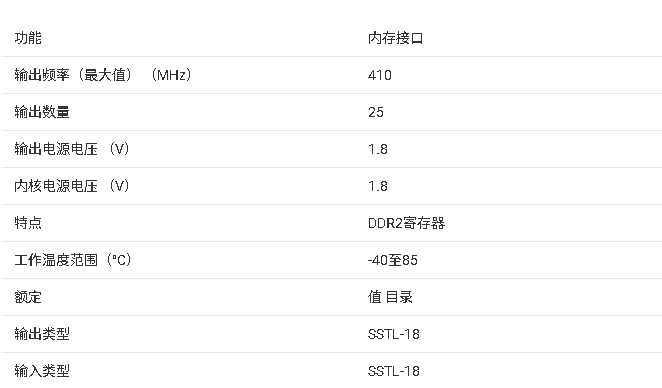

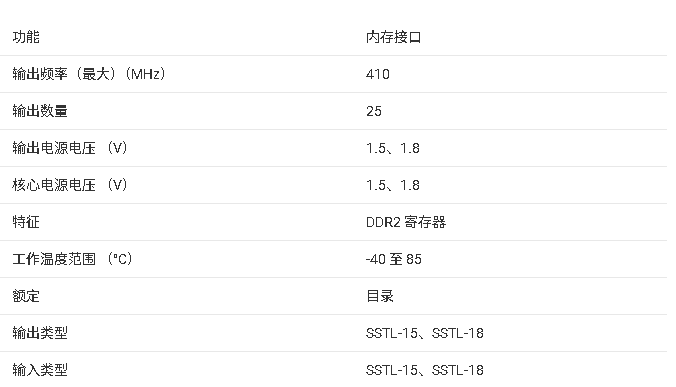

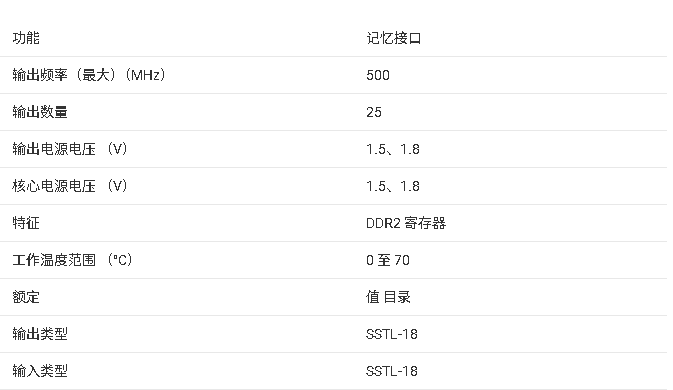

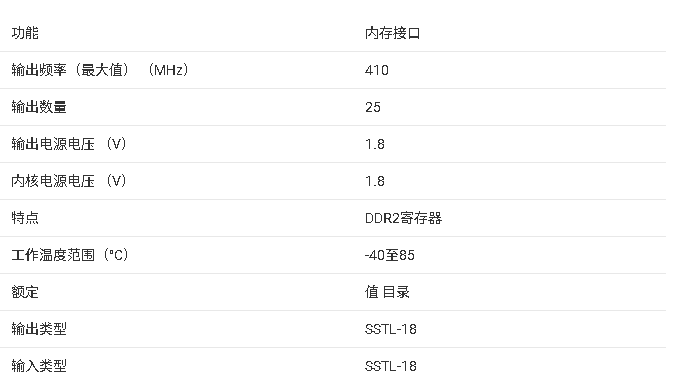

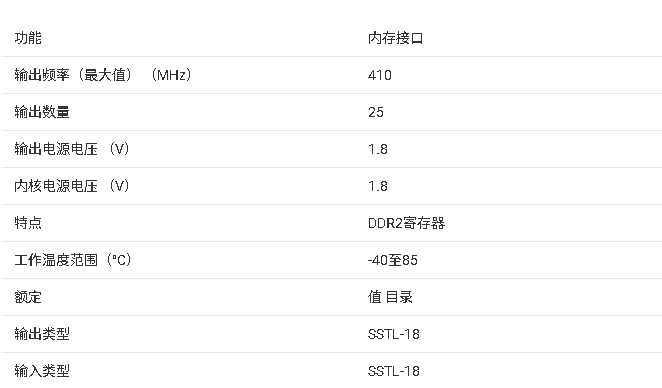

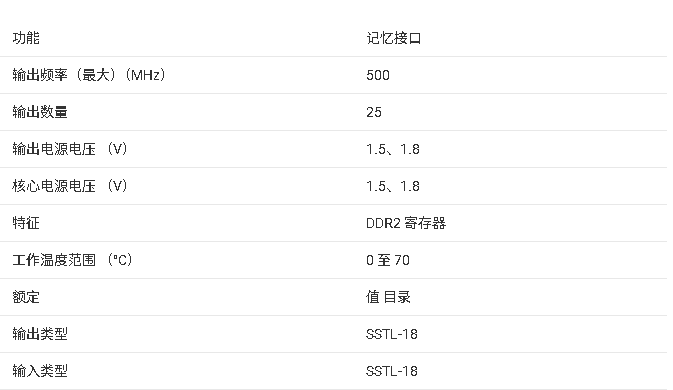

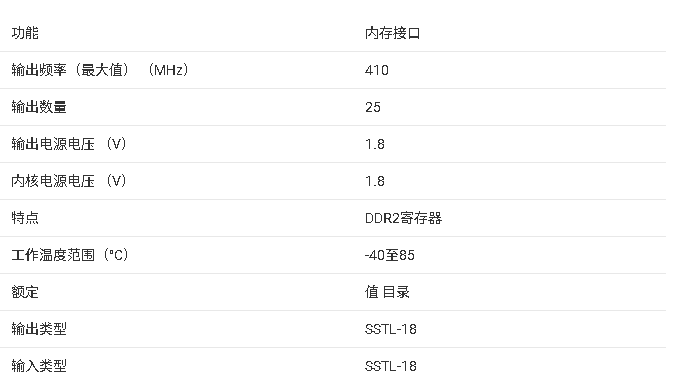

這款 25 位 1:1 或 14 位 1:2 可配置寄存器緩沖器設計用于 1.7V 至 1.9V VCC 工作。在 1:1引腳配置,每個DIMM只需要一個器件即可驅動9個SDRAM負載。在 1:2 引腳排列中 配置中,每個 DIMM 需要兩個設備來驅動 18 個 SDRAM 負載。

2025-09-18 16:52:01 801

801

裸機以及RTT初始化是可以正常讀寫的,但在線程中,用了rt_thread_mdelay,SDRAM內的數據會被清理,數據丟失,也無法讀寫了,調試發現是rt_schedule導致的,請問這個該問題如何解決?

2025-09-18 07:53:44

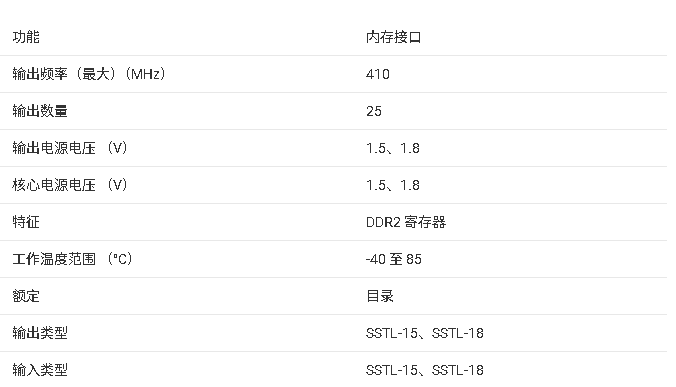

這款 25 位 1:1 或 14 位 1:2 可配置寄存器緩沖器設計用于 1.425V 至 1.9V VCC 工作。在 1:1 引腳配置中,每個 DIMM 只需要一個器件即可驅動 9 個 SDRAM 負載。在 1:2 引腳配置中,每個 DIMM 需要兩個器件來驅動 18 個 SDRAM 負載。

2025-09-17 14:19:28 577

577

這款 25 位 1:1 或 14 位 1:2 可配置寄存器緩沖器設計用于 1.7V 至 1.9V V~CC~操作。在 1:1 引腳配置中,每個 DIMM 只需要一個器件即可驅動 9 個 SDRAM

2025-09-12 09:35:37 570

570

這款 25 位 1:1 或 14 位 1:2 可配置寄存器緩沖器設計用于 1.7V 至 1.9V VCC 工作。在 1:1 引腳配置中,每個 DIMM 只需要一個器件即可驅動 9 個 SDRAM

2025-09-12 09:31:36 711

711

在此前的文章《SRAM PUF:為每顆芯片注入“不可復制的物理指紋”,守護芯片安全》中,我們探討了基于SRAM的物理不可克隆功能(PUF)的基本原理,并介紹了SRAM PUF作為一種安全可靠、經濟

2025-09-05 10:46:16 1152

1152 在電子系統設計中,時鐘信號的穩定與可靠性對于整個系統的正常運行至關重要。為了確保時鐘信號在傳輸過程中不會受到干擾或延遲,工程師們通常會使用一種名為“時鐘緩沖器”的裝置。本文將探討時鐘緩沖器的應用條件

2025-09-04 15:01:45 673

673

是否可以對 EBI 進行 DMA?我有從 USB 到 SDRAM 的 DMA 工作,但是當我將 DMA 目標地址更改為 EBI(60000000 美元)時,我沒有收到任何外部總線活動。如果我將 DMA 到 SDRAM 中的臨時緩沖區,然后將 CPU 復制到 EBI,它會按預期工作。

2025-08-29 07:05:06

CBB81電容屬于高壓諧振薄膜電容器,主要用于高壓、高頻、大電流電路中,事實上,有很多電容器的作用和CBB81電容是一樣的,可以互相替代,cbb81電容用什么可以代替?

2025-08-26 14:23:46 1031

1031 PY32F003 是普冉半導體推出的一款高性價比國產32位微控制器,PY32F003是一款高性價比的國產替代方案,可以用來替換一些進口MCU。芯片采用32 位 ARM? Cortex?-M0+內核

2025-08-21 11:50:09

兩個總線能不能同時使用,用了華邦的SDRAM發現SDRAM數據高概率讀寫錯誤,但是用ISSI的沒問題。如果不對外部SRAM讀寫就正常。

2025-08-12 06:56:57

凱芯CSS12804SU-O 128Mbit pSRAM以2.1Gbps帶寬、1.8μA待機、3×3mm封裝重塑穿戴存儲:實時緩存健康數據,支撐AR與邊緣AI,工業級耐寬溫,國產化30%成本優勢,續航延長30%,零重構兼容主流平臺。

2025-08-04 10:00:00 551

551

與軟件問題

鏈路層錯誤檢測與修復

場景:PCIe鏈路因信號完整性問題(如插損、串擾)導致誤碼率(BER)升高,引發鏈路訓練失敗或數據重傳。

作用:

捕獲DLLP包中的ACK/NAK字段,統計重傳率

2025-07-29 15:02:27

打算先判斷 USB IN 是否存在數據,再執行后續獲取數據的步驟,但一旦調用 USBDevice->BulkInEndPt->XferData,就無法再次獲取數據。是否有其他 USB API 可以實現我的這一功能?#CYUSB3KIT-003

2025-07-28 06:52:41

:

1.哪個函數可以讀取USB端口緩沖區數據的實際字節數?

2. 哪個函數可以讀取 GPIF II 上 DMA 緩沖區數據的實際字節數?

3、GPIF II 接口的標志信號會受 USB 端口狀態的影響嗎?會怎樣,然后又會產生怎樣的影響?

2025-07-21 07:27:08

RISC-V 作為一種開源指令集架構,憑借其靈活性、可擴展性和開源特性,在數據中心領域的應用正從探索階段逐步向實際落地推進。目前,RISC-V 在數據中心的應用處于 “能跑通但需優化” 的階段。從

2025-07-18 13:38:15 5192

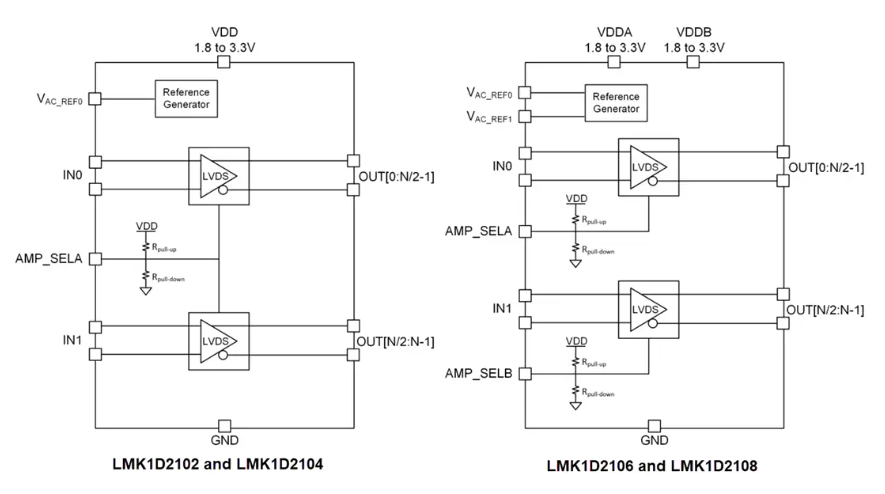

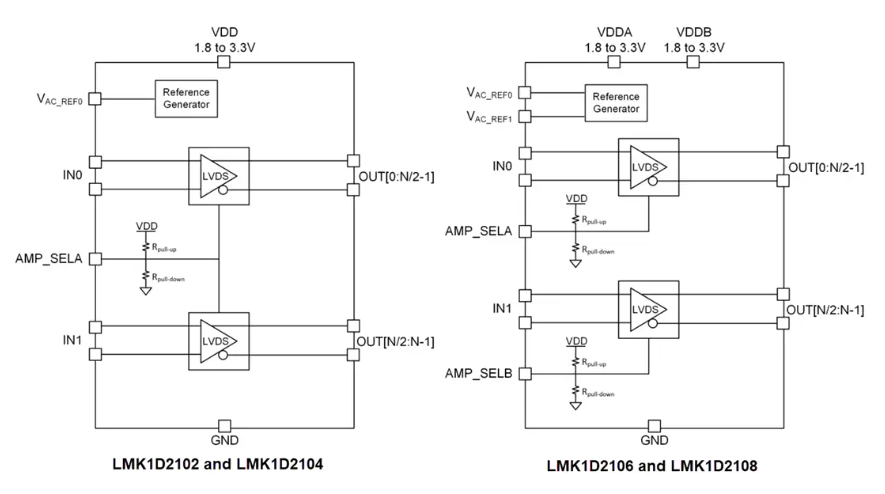

5192 (LMK1D2106L) 或八個 (LMK1D2108L) LVDS輸出。輸入可以是LVDS、LVPECL、HCSL、CML或LVCMOS。LMK1D210xL專門設計用于驅動50Ω 傳輸線。在單端模式下驅動輸入時,向未使用的負輸入引腳施加適當的偏置電壓。

2025-07-17 11:17:27 586

586

在使用USB軟件獲取數據是,下位機給我發送了13個32位數據到USB IN緩沖區,為什么我調用API函數想要第一次取1個32位數據,取完之后再取12位數據,程序會卡死。

2025-07-16 08:12:04

AEC-Q100認證。這些緩沖器用于開關去抖、啟用或禁用數字信號、消除緩慢或嘈雜的輸入信號以及在復位期間保持控制器。

2025-07-15 10:00:42 635

635

一般我們開發MCU自帶的SRAM,對一般應用來說,已經夠用了,但是對于內存需求較高的場合,比如跑GUI或者算法等,自帶的內存會就不夠用,這個時候就要外擴SRAM或SDRAM。

2025-07-15 09:33:09 1781

1781

客戶要求Flash driver不能存儲在Flash中,需要在升級的時候,由CAN FBL發送到SRAM中,再運行SRAM中的Flash driver

我應該如何實現這個要求?如何能把Flash driver分離成一個單獨的部分,再由CAN FBL加載到SRAM中?你們有相關的文檔和示例程序嗎?

2025-07-15 07:22:16

近日,紫光國芯自主研發的PSRAM(低功耗偽靜態隨機存儲器)芯片系列產品正式發布,并同步上線天貓官方旗艦店。此次上新的PSRAM產品兼容業界主流接口協議Xccela,容量覆蓋32Mb,64Mb

2025-07-01 16:42:50 1443

1443 近期受晶圓廠委托, 季豐在執行完SRAM芯片在中子輻射下SER測試后, 通過對SRAM芯片的深入研究,對測試失效數據的分析,將邏輯失效地址成功轉換為物理坐標地址,最終在圖像上顯示失效位置,幫助客戶直觀地看到失效點分布位置。 通過多個失效芯片圖像的疊加,客戶可以看到多個芯片失效積累效果。

2025-06-03 10:08:45 861

861

速率)接口,旨在為主機控制 器和外設(如閃存、SRAM 等)之間提供高效的數據傳輸。該接口采用 12 個信號引腳,包括一 個差分時鐘對(或單端)、一個讀寫數據選通(RWDS)信號、一個片選(CS#)信號

2025-05-29 15:44:59

時鐘緩沖器作為現代電子技術中的一項關鍵元件,其在信息化建設和智能化發展中所扮演的角色日益凸顯。隨著社會的不斷發展,人們對信息傳輸的速度和準確性要求越來越高,時鐘緩沖器以其獨有的功能,確保了數據

2025-05-27 14:08:45 564

564

最近有客戶反映國產FPGA京微齊力P2器件內部合封的pSRAM控制器讀寫效率很高,能達80%以上,而且合封了4片8bit位寬pSRAM芯片,按250MHz主頻DDR雙沿讀寫算下來80%效率能跑

2025-05-16 14:19:39 1517

1517

中說“套接字在填充或清空 DMA 緩沖區后,需要一段有限的時間(最多幾微秒)才能從一個 DMA 描述符切換到另一個 DMA 描述符”(第 14 頁)并且“如果外部外圍設備在套接字從內存中檢索下一個

2025-05-16 07:51:28

2 次傳輸,再次卡住的時間更短,然后順利傳輸數據。

Buffers working until they get stuck緩沖器在卡住之前一直在工作

前兩個緩沖區的標志 A(上)和 B(下),然后

2025-05-16 07:18:39

我想知道我是否可以在數據和電源中使用 Cypd2122 作為 DRP?

如果是,有任何參考設計或應用說明嗎?

數據表說不推薦用于新設計,為什么?

2025-05-07 07:28:43

遷移。 在荷蘭,我們說蘋果和梨不能相提并論,但這并不完全正確。兩者都是所謂的手工水果,一個硬一點,另一個軟一點。 但拿開源技術與大型技術相比,就好比拿烤箱與餐廳相比。大型科技公司提供完善的服務支持,如今他們在自己的數據中

2025-04-30 16:49:28 557

557 滾珠螺桿在數控機床中如何降低摩擦系數?

2025-04-24 17:49:18 594

594

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代產品,相較于DDR2,DDR3有更高的運行性能與更低的電壓。

2025-04-10 09:42:53 3930

3930

如何使用 S32 Design Studio for ARM 將自定義數據放入 SRAM 中以進行S32K146?

2025-04-01 08:27:32

mcxn947自帶的ram太小了,無法滿足需求,想外擴一塊psram,比如樂鑫的esp-psram64芯片,這個需求有哪個案例可以參考嗎?

2025-03-31 06:54:14

ASL6328替代AG7220|替代AG7120|HDMI延長線纜方案|HDMI信號放大方案ASL6328芯片設計原理圖:

ASL6328特性

概述

符合 HDMI 2.0 規范,數據速率高達

2025-03-28 16:19:50

(主)

int_sram_no_cacheable

int_sram_shareable

由于我超出了 RAM 使用量 (int_sram),我能夠將一些數據

2025-03-27 07:16:12

RFID洗滌標簽在數字化工廠中的應用,以其耐用性、高效性和智能化管理能力,為紡織、洗滌和制造行業提供了全面的解決方案。以下是RFID洗滌標簽在數字化工廠中的主要應用場景及其優勢:1.生產流程優化

2025-03-26 16:54:52 564

564

RFID標簽在數字化工廠中的應用,以其高效、精準和自動化的特性,正在成為推動制造業數字化轉型的重要工具。以下是RFID標簽在數字化工廠中的主要應用場景及其優勢:1.生產流程優化與追蹤實時追蹤

2025-03-25 14:13:13 735

735

在嵌入式開發中,流緩沖區(Stream Buffer)是FreeRTOS中用于高效處理字節流數據傳輸的核心機制,尤其適合任務間或中斷與任務間的連續數據傳輸場景(如串口通信、網絡數據流等)。本文將深入

2025-03-24 11:37:29

數據中臺是一種集成和管理企業內部及外部數據的技術架構,旨在實現數據的采集、存儲、處理、分析和應用。它能夠解決多個方面的問題,具體如下: ? ? 一、數據孤島問題 數據孤島是指不同部門或系統之間的數據

2025-03-18 15:24:43 562

562 直線導軌在數控機床中起著關鍵作用,通常用于支撐和導向機床上移動的部件,以確保其運動精度和穩定性。

2025-03-13 17:43:48 912

912

采用STM32F427+FPGA+Flash。

STM32通過FMC總線訪問FPGA內部SRAM,起始地址為0x60000000;

Flash中存儲FPGA的配置數據,STM32和FPGA均可

2025-03-12 07:59:54

SDRAM和NAND都使能了,都能正常工作,但是讀取Nand數據然后存放到SDRAM中,發現SDRAM中的數據是錯誤的。但是將數據存到內部的IRAM中數據是正確的。請問NAND跟SDRAM不能同時訪問么?該問題同時存在于STM32F767跟STM32H743中。請幫忙解答,謝謝!

2025-03-11 08:13:19

兩塊SRAM分別位于不同的基地址,有什么方法可以使這兩塊區域SRAM當成一塊使用

2025-03-07 08:59:10

想用來做一個手表,怕內存不夠用想外擴,不知道2mb flash和768kb的sram夠不夠,打算外擴esp-psram,8M。希望能夠有大佬能夠給出建議,感謝回答!!

2025-03-07 07:23:53

HAC925QN是一款2.1GHz,2路輸出差分高性能時鐘扇出緩沖器,且高度通用、低附加抖動的產品,可以生成兩路LVPECL時鐘副本的緩沖區輸出,可以支持LVPECL、LVDS或LVCMOS輸入。最大時鐘頻率高達2.1GHz。該器件專為高頻、低相位噪聲時鐘和數據信號的信號扇出而設計。

2025-03-06 15:11:55 0

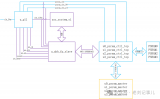

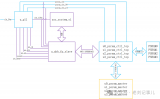

0 前言 SDRAM控制器里面包含5個主要的模塊,分別是PLL模塊,異步FIFO 寫模塊,異步FIFO讀模塊,SDRAM接口控制模塊,SDRAM指令執行模塊。 其中異步FIFO模塊解讀

2025-03-04 10:49:01 2301

2301

一、前言 在全球半導體供應鏈波動的背景下,"國產替代"已成為中國硬科技領域的關鍵詞。而在時鐘信號領域這一核心賽道,華奧創芯推出的HAC946QN時鐘緩沖器,憑借其突破性性能表現,正成為硬件工程師替代

2025-02-27 11:59:18 1464

1464 為了加深讀者對 FPGA 端控制架構的印象,在數據讀取的控制部分,首先我們可以將SDRAM 想作是一個自來水廠,清水得先送至用戶樓上的水塔中存放,在家里轉開水龍頭要用水時,才能及時供應,相同

2025-02-26 15:27:09 1813

1813

Ti是否有一款停產的DLP產品,型號為1191-403BC.官網已經查不到此型號。是否有替代型號可以推薦?以及替代型號與原型號有哪些差別,謝謝!

2025-02-26 08:26:57

command.v文件對應圖中SDRAM指令執行模塊,它會從SDRAM接口控制模塊接收指令,然后產生控制信號直接輸出到SDRAM器件來完成所接收指令的動作。

2025-02-25 10:32:12 1034

1034

物聯網數據中臺可以接入的設備種類非常廣泛,涵蓋了從簡單的傳感器到復雜的智能設備。以下是物聯網數據中臺常見的接入設備類型: 1. 傳感器 : - 環境監測傳感器 :溫度、濕度、氣壓、空氣質量等傳感器

2025-02-24 11:07:29 733

733 手中的一支智能筆。在數字前端開發中,工程師要編寫RTL(寄存器傳輸級)代碼,這就好比是在創作一篇特殊的文章。Gvim提供了一個書寫的平臺,讓工程師能夠輸入、修改和組織代碼內容。 它類似于傳統的紙質筆記本,但功能強大得多。在這個“筆記本”里,工程師可以精

2025-02-20 10:21:08 840

840 時鐘緩沖器是一種用于生成、處理和分配時鐘信號的電子電路,主要用于確保數字系統中各模塊的同步操作。其核心功能是對輸入時鐘信號進行調理和分配,以提供高質量、低抖動的時鐘信號。

2025-02-17 14:34:51 2136

2136 SAFERTOS中的流緩沖區(Stream buffer)機制,可以實現任務到任務或中斷到任務之間的通信。字節流是由發送方寫入緩沖區,接收方讀取緩沖區數據。流緩沖區作為隊列的輕量級級替代方案,適合單讀單寫場景,寫者在流緩沖區中放置任意數量的字節,讀者讀取任意數量的字節。

2025-02-14 11:33:16 1074

1074

1、TLV5616存在數據間隔轉換 2、 數據轉換過程中當數字量為奇數值時寫不進去或著轉換不出模擬量的問題! 芯片工作外圍:5v (VCC)、Uref 2.56v(基準電壓)

2025-02-14 08:12:26

HAC946QN是一款2.1GHz,6路輸出差分高性能時鐘扇出緩沖器,且高度通用、低附加抖動的產品,可以生成六路LVPECL時鐘副本的緩沖區輸出。可以支持LVPECL、LVDS、HCSL或

2025-02-13 16:56:46 1

1 、HCSL 或 LVCMOS(單端)輸入。該產品具有配備中 心抽頭的差分輸入,100Ω片上終端電阻器。最大時鐘頻率高達 2.1GHz。該器件 專為高頻、低相位噪聲時鐘和數據信號的信號扇出而設計。

a) 1:8 差分時鐘緩沖器;

?b) 通用輸入接受 LVPECL、LVDS 和 HCSL

2025-02-13 16:54:49 0

0 HAC925QN 是一款 2.1GHz,2 路輸出差分高性能時鐘扇出緩沖器,且高度 通用、低附加抖動的產品,可以生成兩路 LVPECL 時鐘副本的緩沖區輸出,可 以支持 LVPECL、LVDS 或

2025-02-13 16:53:50 0

0 、HCSL 或 LVCMOS(單端)輸入。該產品具有配備中 心抽頭的差分輸入,100Ω片上終端電阻器。最大時鐘頻率高達 2.1GHz。該器件 專為高頻、低相位噪聲時鐘和數據信號的信號扇出而設計。

a) 1:4 差分時鐘緩沖器;

?b) 通用輸入接受 LVPECL、LVDS 和 HCSL

2025-02-13 16:53:42 0

0 HAC946QN時鐘緩沖器的技術優勢與應用場景,完全替代ADCLK946BCPZ

2025-02-13 14:09:13 897

897 按鍵KEY1觸發寫,將計數器產生的0到255的數據寫到FIFO寫模塊里面,繼而寫到SDRAM 器件里面。

2025-02-07 09:33:41 1192

1192

高速緩沖存儲器(Cache)是內存的一種特殊形式,但它與通常所說的主存儲器(RAM)有所不同。在計算機存儲體系中,Cache位于CPU和主存儲器之間,用于存儲CPU近期訪問過的數據或指令,以加快數據的訪問速度。

2025-01-29 11:48:00 3395

3395 量子芯片在未來某些領域的應用可能會展現出更大的優勢,但它目前并不能完全替代半導體芯片。以下是對這一觀點的詳細解釋:

2025-01-27 13:51:00 2593

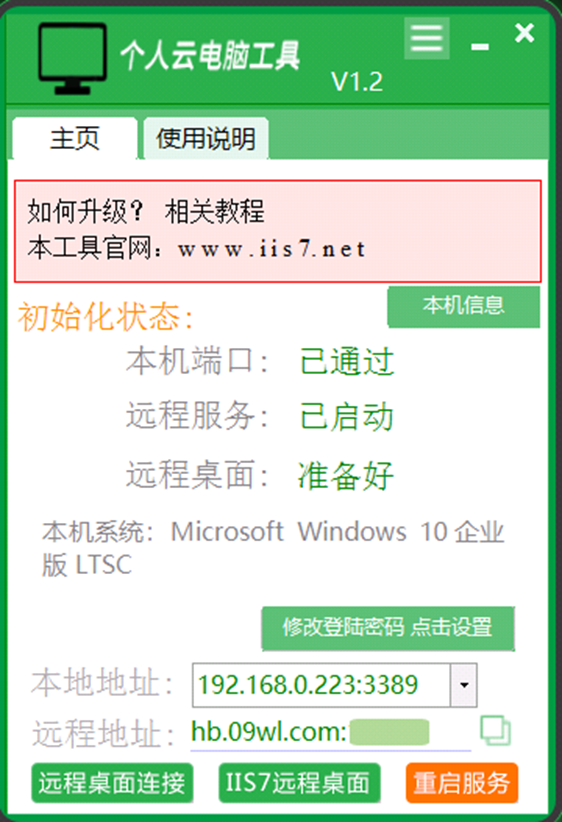

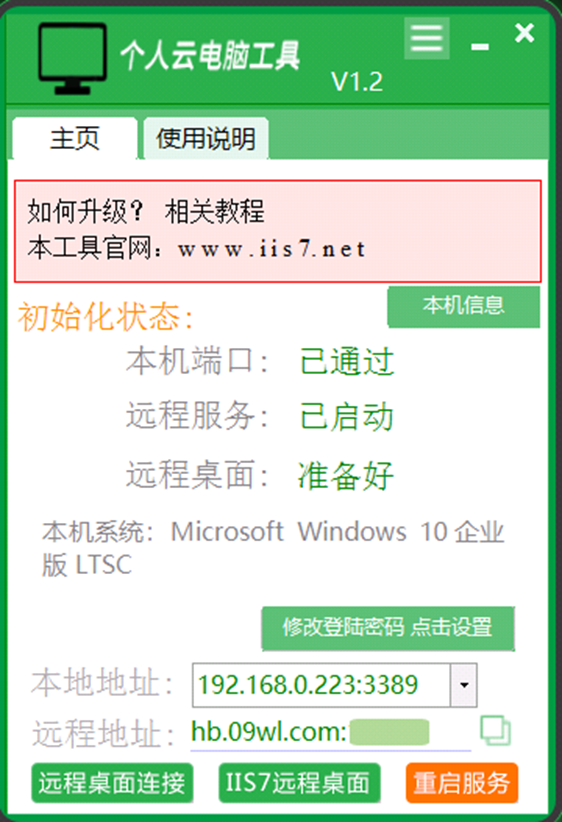

2593 放在云端,讓用戶可以通過任何設備訪問強大的計算能力。今天就為大家介紹怎么操作電腦替代云存儲。 ? ?在數字化時代,將閑置的舊電腦改造成私有云存儲服務器,不僅可以充分利用閑置的硬件資源,還能為家庭或個人提供一個安全、

2025-01-16 09:10:21 742

742

卡諾圖(Karnaugh map,簡稱K-map)在數字電路中具有廣泛的應用,它主要用于布爾代數表達式的簡化和最小化,從而優化數字電路的設計。以下是卡諾圖在數字電路中的具體應用: 一、布爾代數

2025-01-14 17:08:29 2549

2549 物聯網數據中臺是一個集成和管理大量設備產生的數據的平臺,主要功能包括數據采集、數據管理、數據可視化和數據分析等。它為企業提供了一個全面的數據管理和分析解決方案,有助于企業在數字化轉型中實現更高的效率

2025-01-10 11:24:20 833

833 工控主板作為數控機床的核心組件之一,發揮著至關重要的作用。以下是工控主板在數控機床設備中應用的詳細介紹:

2025-01-09 15:33:57 877

877 數據庫是現代信息技術中存儲和管理數據的核心組件。字符串作為最常見的數據類型之一,在數據庫中的存儲方式對其性能和可擴展性有著重要影響。 數據類型 固定長度字符串 :如CHAR類型,它為每個字符串分配

2025-01-07 15:41:59 1338

1338

電子發燒友App

電子發燒友App

評論