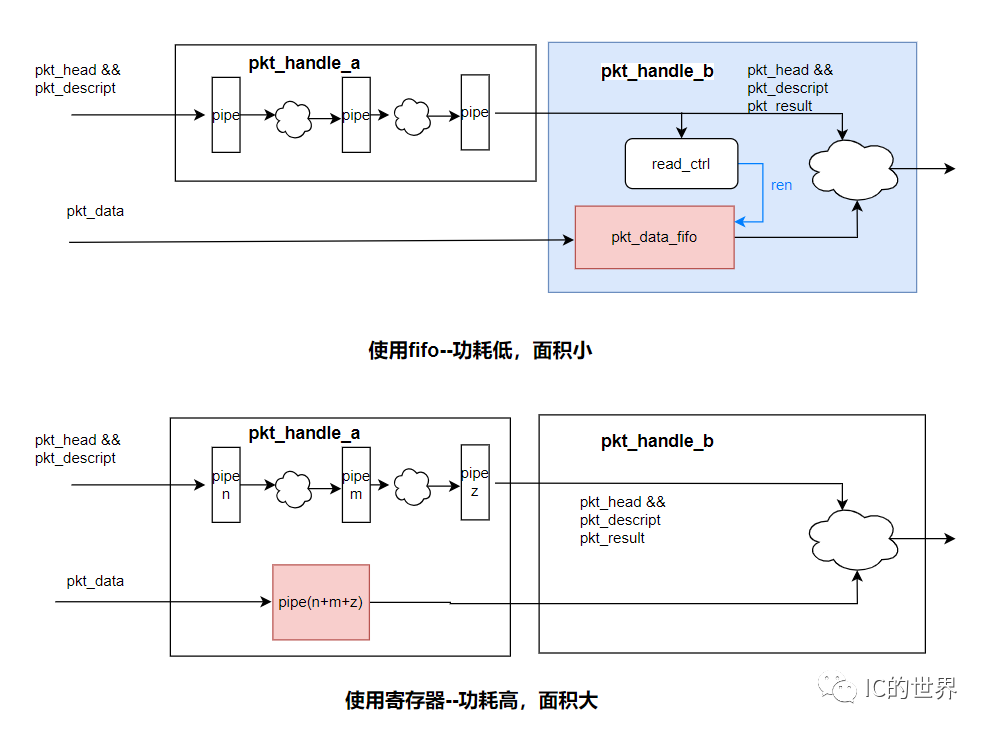

本案例中,我們講解一種使用fifo節約資源,降低功耗的設計。如圖所示,pkt_handle_a模塊是對數據包進行處理的模塊,但是不需要包數據(pkt_data),而僅僅需要根據包頭(pkt_header)和包描述符(pkt_descript)。

這時候該怎么設計呢?

可以采用如下方式:在pkt_handle_b模塊使用一個fifo用于存儲包數據(pkt_data),pkt_handle_a模塊的輸入僅僅只有包頭和包描述符,pkt_handle_a模塊完成包處理后新增處包處理結果(pkt_result),送到pkt_handle_b模塊,pkt_handle_b模塊在需要讀出包數據(pkt_data)的時候才將fifo內的數據讀出。

在包數據位寬較大,pkt_handle_a流水拍數較大時,相對于使用寄存器對包數據(pkt_data)進行打拍,使用fifo存儲包數據(pkt_data)的實現方式更有優勢,功耗低,面積小。

雖然從存儲bit位角度計算兩種設計需要的bit位幾乎相同,但是相對于寄存器,底層用ram實現的fifo面積更小,功耗更低。

pkt_handle_a和pkt_handle_b之間可能存在更多的模塊,數據流水可能長達幾十到上百個周期,因此流水拍數越大,節約面積,降低功耗的效果越明顯。

審核編輯:劉清

-

IC設計

+關注

關注

38文章

1373瀏覽量

108302 -

RAM

+關注

關注

8文章

1399瀏覽量

120540 -

FIFO設計

+關注

關注

0文章

7瀏覽量

5116

原文標題:IC設計:ram的應用-一種降功耗的設計方法

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

IC芯片功耗有哪些降低方法?

請問如何讓音頻功率降低功耗?

如何讓音頻功率降低功耗?

一種異步FIFO的設計方法

一種低功耗觸摸按鍵應用的設計方法

一種低功耗智能傳感主動式標簽的設計

一種使用fifo節約資源降低功耗的設計方法

一種使用fifo節約資源降低功耗的設計方法

評論