MCS—96系列單片機的中斷系統頗具特色,其中斷優先級的控制極具靈活性,用戶可采用軟、硬件結合的方法隨心所欲地安排各類中斷源的優先級。

2012-05-03 16:36:53 2942

2942 很多人在配置STM32中斷時對固件庫中的這個函數NVIC_PriorityGroupConfig()——配置優先級分組方式,會很不理解,尤其是看中文翻譯版的,因為中文翻譯版里把這里翻譯成“先占優先級和從優先級”這樣翻譯其實是不對的,很容易讓人誤解。

2017-12-22 06:25:00 11318

11318 若單片機同時接收到幾個中斷請求時,單片機對中斷請求的響應順序是如何確定的?實際上,單片機是通過中斷優先級來確定中斷響應順序的。

2023-10-31 14:42:51 3625

3625

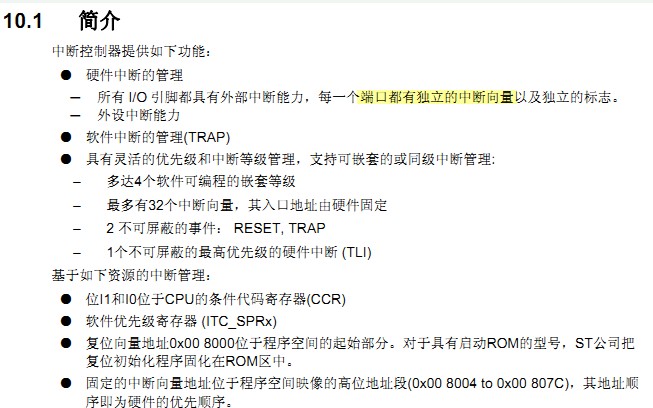

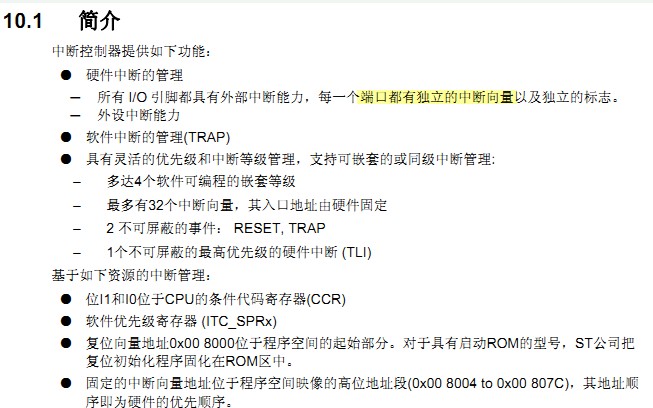

由于今天一直STM8S 的程序,關于STM8s的中斷一直是處于只知道用,卻不理解中斷流程,以及關于中斷的基本概念。本篇文檔主要說明中斷的基本概念、機制、流程、處理方法等。 一些問題:1.什么叫軟件

2021-08-16 06:41:02

1、中斷優先級中斷優先級的設置雖然能夠比較合理的管理資源,但是如果在中斷里寫太多內容會導致另一個中斷可能永遠進不去的現象。比如在定時器中斷里定20ms,但是中斷里面處理的代碼量太多超過20ms,則會

2021-11-24 06:22:24

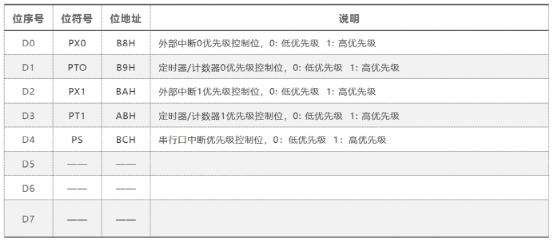

STC12C5A60S2單片機復位后IP、IP2、IPH、IP2H均為00H,各個中斷源都是低優先級=》不能被同級中斷所中斷中斷優先控制寄存器IP、IP2、IPH、IP2H例如:想要實現外部中斷1被中斷0中斷,設置外部中斷0為最高優先級(優先級3)...

2021-11-25 06:32:12

初始化All_Init();函數在BSP_Init.c中看下源程序u8 All_Init(){NVIC_PriorityGroupConfig(NVIC_GROUP);//中斷優先級組別設置SysTick_Configuration(); //滴答時鐘Delay_ms(100);.

2021-08-06 06:53:10

一:綜述STM32 目前支持的中斷共為 84 個(16 個內核+68 個外部), 16 級可編程中斷優先級的設置(僅使用中斷優先級設置 8bit 中的高 4 位)和16個搶占優先級(因為搶占優先級

2021-08-13 06:50:02

項目中同時使用了藍牙和usb host,同時開啟了看門狗,并在TIM1中斷中定時喂狗,當藍牙和USB同時工作時,看門狗無法及時喂狗導致芯片復位,實際上程序沒有死機,打算提高TIM1的中斷優先級,中斷

2022-07-26 06:00:43

ESP32S2有六級中斷, 如何設置中斷優先級? 比如在GPIO例程里 ,這種中斷優先級是如何設置的呢?

中斷寄存器列表里 ,只有簡稱,哪里能獲取這個名稱所對應的功能??

2024-06-21 07:59:34

ESP32S2 有六級中斷, 如何設置中斷優先級? 比如在GPIO例程里 ,這種中斷優先級是如何設置的呢?中斷寄存器列表里 ,只有簡稱,哪里能獲取這個名稱所對應的功能??

2023-02-20 07:08:41

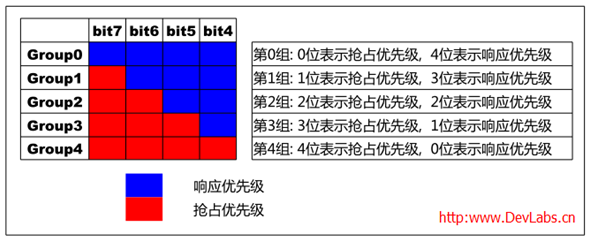

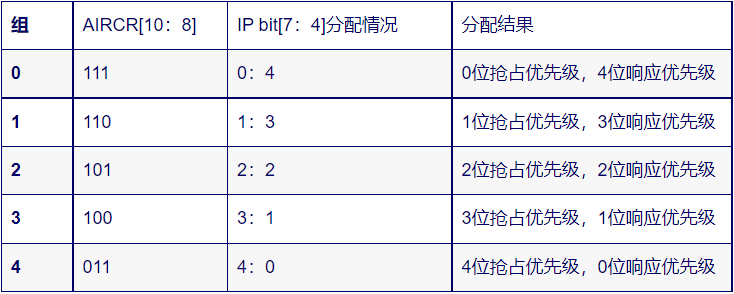

一、NVIC 中斷優先級分組1、中斷管理方法:對stm32分為四組,0~4組,同時每個中斷設置一個搶占優先級和一個響應優先級2、區別:3、中斷優先級函數:二、中斷優先級設置1、中斷設置相關寄存器2

2022-01-11 06:48:55

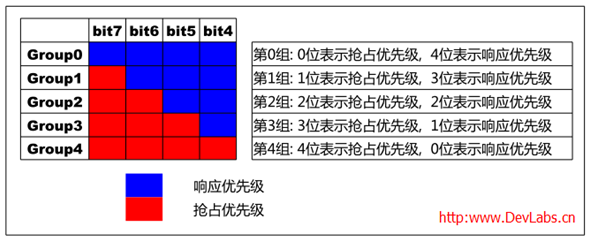

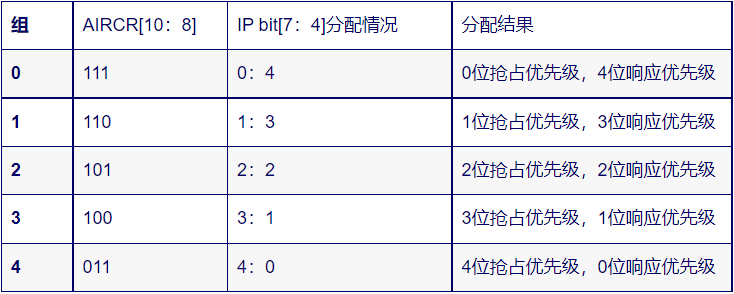

NVIC中斷優先級管理中斷優先級分組:STM32F407系列把中斷分為5個組:(0~4)對0-4每個中斷設置一個搶占優先級和響應優先級值(值越小優先級越高)且第n個分組來說,有n位搶占優先級(值0

2021-08-16 08:06:19

cpu文件夾下context_rvds.S的匯編部分,中斷優先級設置為15,代碼如下:匯編代碼解釋如下:查閱手冊得知:PendSV優先級設置寄存器地址為0xe000ed22SysTick優先級設置寄存器

2022-04-25 11:09:32

的搶占優先級是可以打斷正在進行的低搶占優先級中斷的搶占優先級相同的中斷,高優先級的響應優先級是不可以打斷低響應優先級的中斷2. 中斷優先級設置的步驟:系統運行開始的時候設置中斷分組確定組號,也就是調用函數NVIC_PriorityGroupConfig();定搶占優先級和子優

2022-01-14 09:20:22

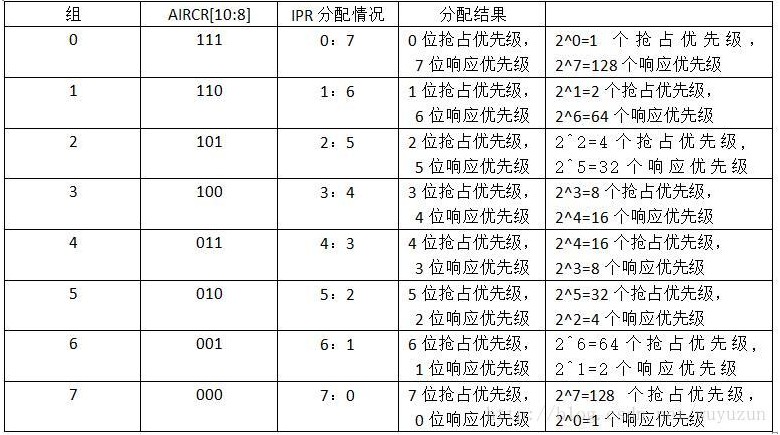

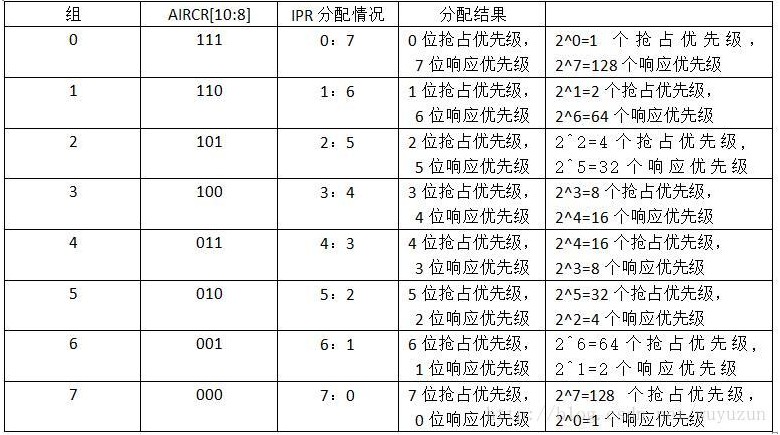

指定響應優先級,那么搶占式優先級就有000-111共八種數據選擇,也就是有八個中斷嵌套,而響應優先級中有0和1兩種,總共有8*2=16種優先級。 中斷源優先級具體的設置了該中斷源的優先級別 在一個程序

2018-07-06 03:27:03

STM32中斷中設置的先占式優先級與從優先級如何理解?

2023-03-24 17:55:46

中斷管理方法:首先,對STM32中斷進行分組,組0~4。同時,對每個中斷設置一個搶占優先級和一個響應優先級值。分組配置是在寄存器SCB->AIRCR中配置:高優先級的搶占優先級是可以打斷正在進行的低搶占優先級中斷的。搶占優先級相同的中斷,高響應優先級不可以打斷低響應優先級的中斷。搶占優先級相

2021-08-16 06:40:50

中斷優先級設置步驟:系統運行后先設置中斷優先級分組。在主函數調用函數:void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup);整個系統

2021-08-13 07:01:07

STM8中斷優先級怎么設置

2023-10-25 06:49:00

TIM1不能進中斷TIM1溢出中斷優先級設置為1(中斷時間為100us),程序運行開始的時候可以進中斷,但是運行一會兒后就不能進中斷了。TIM16溢出中斷優先級設置也為1,中斷時間50ms,但是沒有

2021-08-16 06:55:18

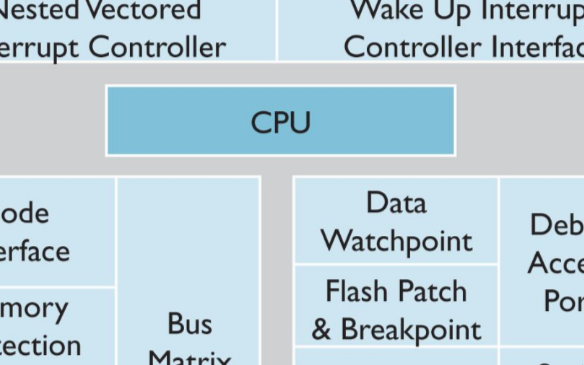

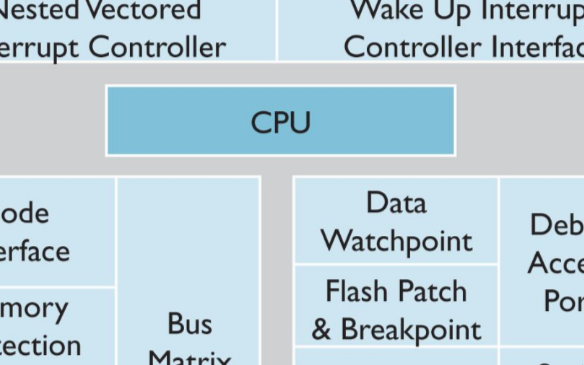

Fault 優先級為負(高于普通中斷優先級)且不可調整。接著簡單了解一下中斷優先級(NVIC.)STM32嵌套向量中斷控制器(NVIC)中斷優先級理解CM3內核寄存器AIRCR——應用程序中斷及復位控制寄存器

2014-04-15 14:14:09

Cortex M內核中每個中斷都有一個8位的優先級設置寄存器這個8位的寄存器可以分為搶占優先級和子優先級兩個部分(通過設置優先級組設置)搶占優先級和子優先級有什么用?舉例說明:有兩個中斷A、BA

2022-01-25 06:07:42

請教大家個小白問題,中斷優先級組為2,就是說所有60個中斷每個中斷的中斷優先寄存器的高4為重的最高2位是搶占優先級(可設置搶占優先級位0-3),低2位是響應優先級(響應優先級為0-3)。這樣理解有錯

2019-06-24 04:35:02

最近在學習ucosii有這樣一個疑問,關于stm32的systick作為ucosii的基準時鐘,systick的中斷優先級是否應該設置為最高優先級的嵌套中斷。理由是什么?各位大俠求指教!!!

2024-05-16 06:44:15

詳細介紹中斷、中斷優先級、中斷優先級組、搶占優先級和響應優先級概念。

2021-08-16 07:50:30

最近在學習FreeRTOS,例程中涉及到中斷優先級和線程優先級的概念,有幾點不太明白想請教下大家。1.中斷優先級和線程優先級是不是同一組優先級?我的理解為不是一組,所有中斷都高于線程優先級,不知道理解

2020-06-18 22:41:49

在調查 S32K1 上的中斷優先級問題時,我發現 RTD 示例中沒有一個設置了中斷優先級。中斷優先級不應該設置如下嗎?IntCtrl_Ip_Init(&IntCtrlConfig_0);此外

2023-03-15 08:04:24

FreeRTOS 函數(例如給出信號量“xSemaphoreGiveFromISR()”),將會出現故障。FreeRTOS 檢查中斷的優先級,如果優先級高于設置級別,則將應用斷言。我可以手動設置優先級

2023-01-12 06:07:09

configMAX_SYSCALL_INTERRUPT_PRIORITY 中斷優先級設置問題從CortexM角度Cortex-M構架自身最多允許256級可編程優先級(優先級配置寄存器最多8位,所以

2021-12-16 07:08:25

如何設置一個具有自己優先級的軟件中斷來處理這個問題?我不想在這里更改其他內容的優先級。sw 中斷是否可以有自己的處理程序?如何?先感謝您!

2022-12-13 07:29:19

關于搶占優先級和子優先級:

1)具有高搶占式優先級的中斷可以在具有低搶占式優先級的中斷服務程序執行過程中被響應,即中斷嵌套,或者說高搶占式優先級的中斷可以搶占低搶占式優先級的中斷的執行。

2)在搶占

2025-12-03 07:11:35

stm32的中斷嵌套優先級stm32NVIC優先級分組中斷優先級配置寄存器NVIC_IPRx描述搶占優先級與響應優先級 ,在Cortex_m3中,該寄存器被定義為8bit,考慮stm32允許具有較少

2021-08-13 09:45:55

一:綜述 STM32 目前支持的中斷共為 84 個(16 個內核+68 個外部), 16 級可編程中斷優先級 的設置(僅使用中斷優先級設置 8bit 中的高 4 位)和16個搶占優先級(因為搶占優先級最多可以有四位數)。 二:優先級判斷 STM32(Cortex-M3)中有兩

2021-08-13 07:08:40

有大神接觸過s12g64芯片嗎?現在遇到個問題,中斷優先級怎么設置?開發時,設計到定時中斷和串口接受中斷,默認定時中斷優先級高于串口接受中斷,怎么可以設置串口接受中斷高于定時中斷?查閱了相關資料,此芯片沒有相應寄存器

2019-05-15 10:12:51

因為項目對時序輸出要求比較嚴格,WIFI中斷優先級比硬件定時器中斷優先級要高,在定時器中斷里面對GPIO管腳控制被延長執行,請問有什么方法降低WIFI中斷的優先級?

2023-02-16 08:30:55

因為項目對時序輸出要求比較嚴格,WIFI中斷優先級比硬件定時器中斷優先級要高,在定時器中斷里面對GPIO管腳控制被延長執行,請問有什么方法降低WIFI中斷的優先級?

2024-06-19 07:37:19

原子的列程上貌似木有設置滴答的中斷優先級,想問問系統中斷的優先級 和 普通中斷(比如 定時器0中斷 串口中斷 DMA中斷 等等)的優先級有什么不同?哪個更高些?找到 STM32的編程手冊才發現 系統中斷的設置寄存器和普通的不一樣。。。。。

2019-05-28 04:37:19

。 ICPR[8]—中斷解掛控制寄存器組,用來解除掛起。 IABR[8]—中斷激活標志寄存器組,對應位如果為1則表示中斷正在被執行。 IP[240]—中斷優先級控制寄存器組,它是用來設置中斷優先級的。我們只用

2016-07-12 16:32:46

為了解決MCS-51系列單片機只能由IP寄存器設定兩級優先級的問題,文中給出了利用軟件對中斷優先級進行擴展的方法,同時給出了高于兩個優先級的多優先級軟件擴展程序.

2009-04-30 13:43:28 29

29 鑒于MCS-51 系統只提供“二級中斷嵌套”, 提出擴展51 系統中斷優先級的純軟件方法。其利用51系統內建的中斷允許寄存器IE 和中斷優先級寄存器IP,通過屏蔽字機制來實現;以C51 的

2009-05-15 16:23:34 19

19 )、串口中斷(S)。如果當前指令是RETI或是對IE、IP操作的指令,將封裝CPU對中斷的響應,且必須再執行完一條指令之后才會響應中斷。2 中斷優先級軟擴展的方法首先,給出軟擴展的第一種方法,并分析其特點

2006-03-11 11:49:11 1202

1202

1.ARM cortex_m3內核支持256個中斷(16個內核+240外部)和可編程256級中斷優先級的設置,與其相關的中斷控制和中斷優先級控制寄存器(NVIC、SYSTICK等)也都屬于cortex_m3內核的部分。STM32采用了cortex_m3內核,所以這部分仍舊保留使用,但STM32并沒有使用

2011-02-28 14:38:38 146

146 STM32(Cortex-M3)中有兩個優先級的概念搶占式優先級和響應優先級,有人把響應優先級稱作亞優先級或副優先級,每個中斷源都需要被指定這兩種優先級。

2011-11-04 15:02:43 41

41 單片機外部中斷實驗和中斷優先級實驗所需的C語言程序和電路圖適于初學者使用

2015-11-16 18:32:25 0

0 STM32中斷優先級和開關總中斷 教程

2015-11-23 18:03:11 0

0 NVIC中斷優先級分組

2017-03-26 10:45:36 1

1 什么是優先級 優先級是具有高搶占式優先級的中斷可以在具有低搶占式優先級的中斷處理過程中被響應,即中斷嵌套,或者說高搶占式優先級的中斷可以嵌套低搶占式優先級的中斷。 當兩個中斷源的搶占式優先級相同

2017-10-13 11:48:47 5898

5898 硬件最低優先級。 configMAX_SYSCALL_INTERRUPT_PRIORITY用來設置可以在中斷服務程序中安全調用FreeRTOS API函數的最高中斷優先級。優先級小于等于這個宏所代表的優先級時,程序可以在中斷服務程序中安全的調用F

2017-11-29 19:46:01 2652

2652

原以為2812中斷不能設置優先級。實際上硬件上優先級是做好的。但軟件上有辦法來設置優先級。

2018-04-08 17:20:48 20

20 先占優先級也就是搶占優先級,概念等同于51單片機中的中斷。假設有兩中斷先后觸發,已經在執行的中斷先占優先級如果沒有后觸發的中斷 先占優先級更高,就會先處理先占優先級高的中斷。也就是說又有較高的先占優先級的中斷可以打斷先占優先級較低的中斷。這是實現中斷嵌套的基礎。

2018-12-07 15:09:53 10085

10085

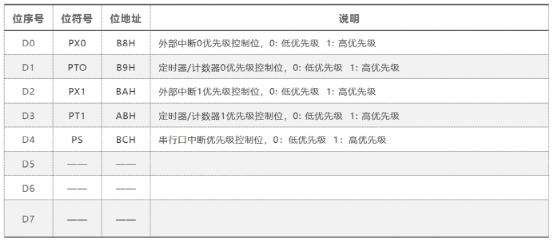

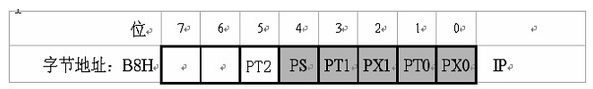

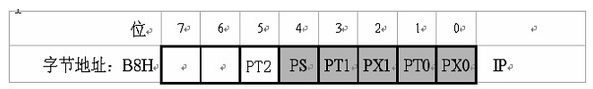

PS:串行口中斷優先級控制位。PS=1設定串行口為高優先級中斷;PS=0為低優先級中斷。

PT1:T1中斷優先級控制位。PT1=1設定定時器T1為高優先級中斷;PT1=0為低優先級中斷

2018-12-17 16:28:45 34691

34691 再看看STM8S的中斷管理。STM8S采用軟件優先級和硬件優先級來控制一個中斷的響應,先比較軟件優先級只有當軟件優先級一致時才會比較硬件優先級,由于硬件優先級具有唯一性,這樣便保證了某一時刻定會只有一個中斷被處理。

2019-02-11 10:00:00 5771

5771

基本型80C51系列單片機有5個中斷源,2個優先級,每個中斷源可通過軟件設置為高優先級或低優先級中斷,可以實現二級中斷服務嵌套。

2019-09-03 17:28:00 5

5 在MCS-中斷優先級中由中斷優先級寄存器IP來高置的,IP中某位設為1,相應的中斷就是高優先級,否則就是低優先級。

2019-08-20 17:31:00 2

2 同一優先級中的中斷申請不止一個時,則有中斷優先權排隊問題。同一優先級的中斷優先權排隊,由中斷系統硬件確定的自然優先級形成。

2019-08-02 17:34:00 1

1 51單片機(80C51系列)有5個中斷源,2個優先級,可以實現二級中斷服務嵌套。現在很多擴展的51單片機已經有4個優先級(或更多)和更多的中斷源了。在說到中斷之前,我先來定義一下優先級,明白了

2019-07-23 17:37:00 1

1 51單片機(80C51系列)有5個中斷源,2個優先級,可以實現二級中斷服務嵌套。現在很多擴展的51單片機已經有4個優先級(或更多)和更多的中斷源了。在說到中斷之前,我先來定義一下優先級,明白了

2019-07-09 17:41:00 3

3 其實都是查詢優級。首先查詢優先級是不可以更改和設置的。這是一個中斷優先權排隊的問題。是指多個中斷源同時產生中斷信號時,中斷仲裁器選擇對哪個中斷源優先處理的順序。而這與是否發生中斷服務程序的嵌套

2019-07-03 17:41:00 1

1 PX0(IP.0),外部中斷0優先級設定位;

PT0(IP.1),定時/計數器T0優先級設定位;

PX1(IP.2),外部中斷0優先級設定位;

PT1(IP.3),定時/計數器T1

2019-10-14 16:15:21 52944

52944

Cortex支行中斷嵌套, 允許高優先級的中斷搶占低優先級的中斷。 Cortex M3/M4可支行多達256級的可編程優先級和128級的搶占, 但有3個系統異常優先級固定, 并且優先級為負數, 高于其它任何異常, 這三個異常分依次為 復位, NMI, Hard Fault.

2019-10-14 16:31:45 12316

12316

STM32中斷,及FreeRTOS中斷優先級配置

2020-03-04 11:45:36 10078

10078

中斷優先級是CPU響應中斷的先后順序。中斷優先處理的原則是:

2020-07-17 09:35:40 12282

12282 STC12C5A60S2單片機復位后IP、IP2、IPH、IP2H均為00H,各個中斷源都是低優先級=》不能被同級中斷所中斷中斷優先控制寄存器IP、IP2、IPH、IP2H例如:想要實現外部中斷1被中斷0中斷,設置外部中斷0為最高優先級(優先級3)...

2021-11-17 09:36:03 6

6 STM32d的中斷優先級由NVIC_IPRx寄存器來配置,IPR的寬度為8bit所以原則上每個中斷可配置的優先級為0~255,數值越小優先級越高,但對于大部分的 Cortex-M3芯片都會精簡

2021-11-19 10:21:04 52

52 的中斷,需要在低優先級的中斷程序中手動打開全局中斷便能位,因為在進入中斷服務子程序時全局中斷便能位被清零,即禁止響應其它中斷。 msp...

2021-11-19 19:06:02 11

11 、NVIC中斷優先級管理1. 中斷簡介在Cortex-M3(CM3)內核中,每個中斷的優先級都是用寄存器中的8位來設置的,這樣就有2^8 =256級中斷,意味著可以支持256個中斷,這其中包含了16個內核

2021-11-26 11:36:12 2

2 Cortex M內核中每個中斷都有一個8位的優先級設置寄存器這個8位的寄存器可以分為搶占優先級和子優先級兩個部分(通過設置優先級組設置)搶占優先級和子優先級有什么用?舉例說明:有兩個中斷A、BA

2021-12-01 11:51:05 4

4 NVIC中斷優先級管理NVIC中斷優先級分組NVIC中斷優先級設置NVIC總結CM3 內核支持 256 個中斷,其中包含了 16 個內核中斷和 240 個外部中斷,并且具有 256級的可編程中斷設置

2021-12-04 17:06:08 7

7 前言這一篇博客主要講解NVCI中斷優先級分組,優先級設置。參考資料《STM32F1開發指南-庫函數版本》 4.5小節《STM32中文參考手冊》第九章

2021-12-04 18:51:05 10

10 FreeRTOS中斷優先級和任務優先級架構:Cortex-M3版本:FreeRTOS V9.0.0前言:最開始,我并沒有搞清楚什么是中斷優先級和任務優先級,但看了部分資料后發現這兩個并沒有半毛錢關系

2021-12-04 20:21:10 14

14 記錄一下,方便以后翻閱~主要內容:1) NVIC中斷優先級分組;2) NVIC中斷優先級設置。官方資料:《STM32中文參考手冊V10》第9章——中斷和事件1. NVIC中斷優先級分組

2021-12-04 20:21:11 9

9 STM32----NVIC中斷優先級之前在學習和應用STM32時總是有疑惑,總是感覺優先級分組有點混亂,而且在排序中斷優先級時沒有一定的頭緒,在疫情期間對這一方面的知識進行了深入的了解,下面將我學到

2021-12-04 20:36:10 1

1 stm32中斷優先級分組轉載:http://news.eeworld.com.cn/mcu/article_2018053039408.html一、搶占優先級和響應優先級STM32 的中斷

2022-01-14 15:04:46 3

3 STM32NVIC中斷優先級CM3內核共支持256個中斷,其中包含了16個內核中斷,240個外部中斷,并且具有256級可編程中斷設置。但是stm32并沒有使用CM3內核全部的東西,stm32有84

2022-01-14 15:15:49 2

2 STM32中斷優先級和開關總中斷一,中斷優先級:STM32(Cortex-M3)中的優先級概念STM32(Cortex-M3)中有兩個優先級的概念——搶占式優先級和響應優先級,有人把響應優先級稱作

2022-01-14 15:24:52 13

13 中斷優先級分組(NVIC)值越低,優先級越高

2022-01-14 15:27:55 1

1 硬件中斷優先級中0最高,依次優先級降低。只有當軟件優先級相同時,單片機才進行硬件優先級的判斷,且硬件優先級不能中斷嵌套。軟件配置中斷優先級時,0為優先級最低,依次優先級增加。軟件中斷可以有高優先級中斷搶占低優先級的情況,實現中斷嵌套。...

2022-01-14 15:28:56 1

1 的搶占優先級是可以打斷正在進行的低搶占優先級中斷的搶占優先級相同的中斷,高優先級的響應優先級是不可以打斷低響應優先級的中斷2. 中斷優先級設置的步驟:系統運行開始的時候設置中斷分組確定組號,也就是調用函數NVIC_PriorityGroupConfig();定搶占優先級和子優

2022-01-14 15:29:56 1

1 使用該內核所有的東西,但對我們來說只是會配置就可以了。對于其中斷數量只是了解就OK了,如果真的有需要用到其所有數量的中斷的大佬,也不會看我的文章了,中斷作為單片機最重要的外設之一,其優先級是最重要的,STM32的中斷優先級配置主要有以下兩個方面一是中斷分組;二是對每一個中斷中斷設置其搶占優先級和響應優先級。

2022-01-14 15:46:00 1

1 STM32F103只用了4個位來表達優先級,因此最多支持16級的可編程優先級(0~15),15為最低優先級。

2022-01-25 18:59:01 1

1 下面就來說說關于Cortex-M的中斷,及FreeRTOS中斷優先級配置原理。

2022-02-08 15:30:51 3

3 51單片機包含五個中斷源,兩級中斷優先級,優先級可編程設置,通過IP進行設置。

2022-02-09 12:32:53 2

2 首先我們需要知道什么是中斷優先級:中斷優先級是CPU響應中斷的先后順序

2022-05-18 15:10:46 31405

31405

S7-1200-CPU 支持優先級 1(最低)到 27(最高)。為 OB 分配其啟動事件的優先級。中斷 OB 只能由時間錯誤中斷進行中斷。 此規則也適用于優先級高于當前激活 OB 的事件。即,除時間錯誤中斷 OB 外,只能激活一個中斷 OB。

2023-01-07 11:41:04 3264

3264 AXI Interrupt Controller支持中斷優先級。 在Vivado Block Design中, bit-0連接的中斷優先級最高

2023-07-11 17:03:58 1736

1736

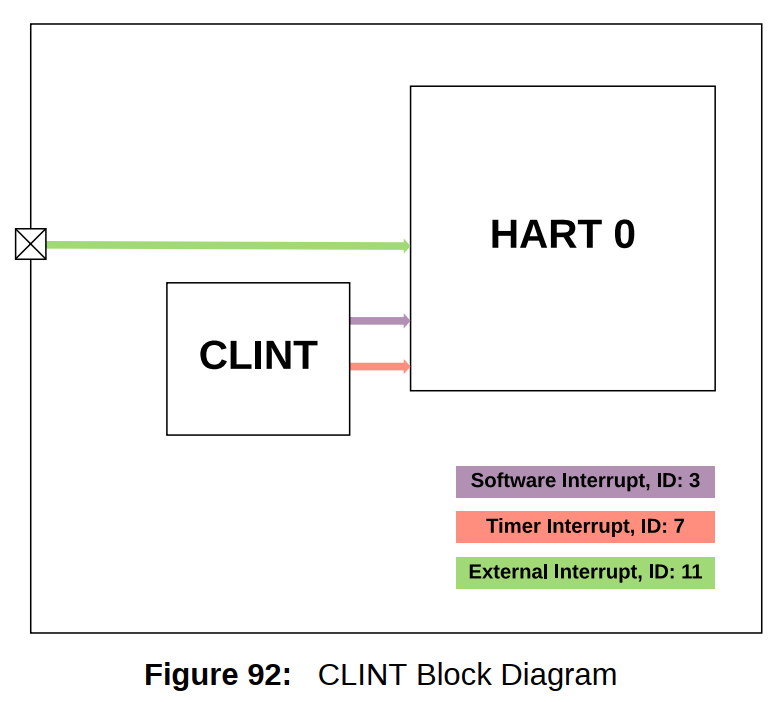

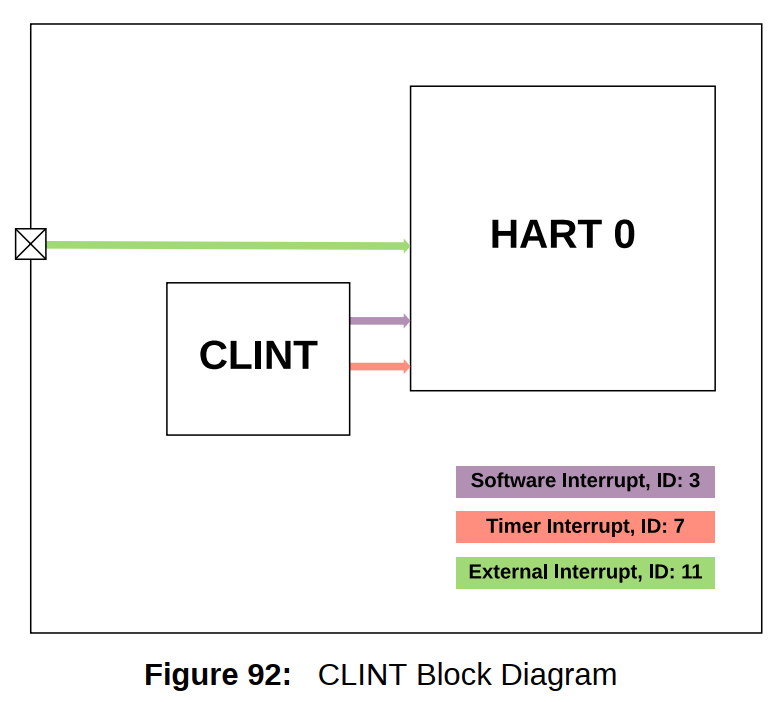

內核本地中斷(CLINT) 下圖為CLINT示意圖,CLINT通過固定的中斷號和優先級,可將軟件中斷或定時器中斷直接發送給指定的hart,該過程沒有仲裁。 CLINT 占地面積小,可直接向 hart

2023-10-08 09:30:53 1416

1416

看到一個交流群在討論關于【關于STM32中斷優先級的話題】,其中就有小伙伴提到:為什么有些STM32中斷沒有【子優先級】?

2023-10-17 15:50:58 1754

1754

使用GD32 MCU的過程中,大家可能會有以下疑問:中斷優先級如何配置和使用?

2024-01-10 10:30:39 4802

4802

FreeRTOS是一個流行的實時操作系統,它廣泛應用于嵌入式系統開發。在FreeRTOS中,中斷優先級是一個重要的概念,因為它決定了中斷處理的順序和響應時間。 1. 理解中斷優先級 在討論如何設置

2024-09-02 14:17:03 2219

2219

電子發燒友App

電子發燒友App

評論