它們的基本設(shè)計(jì)方法是借助于 EDA 設(shè)計(jì)軟件,用原理圖、狀態(tài)機(jī)和硬件描述語(yǔ)言等方法,生成相應(yīng)的目標(biāo)文件,最后用編程器或下載電纜,由 CPLD/FPGA 目標(biāo)器件實(shí)現(xiàn)。 生產(chǎn) CPLD/FPGA

2019-03-04 14:10:13

不知原子哥SD卡寫多個(gè)塊的函數(shù)(SD_WriteMultiBlock(u32 sector, const u8 *data, u8 count))通過了沒,最近用原子例程里的SD卡驅(qū)動(dòng)移植了FATFS,一次寫超過512字節(jié)就寫不成功

2019-04-17 06:35:05

),有時(shí)我們不需要使用完整的UART的功能和這些輔助功能。或者設(shè)計(jì)上用到了FPGA/CPLD器件,那么我們就可以將所需要的UART功能集成到FPGA內(nèi)部。使用VHDL將UART的核心功能集成,從而使整個(gè)設(shè)計(jì)更加緊湊、穩(wěn)定且可靠。本文應(yīng)用EDA技術(shù),基于FPGA/CPLD器件設(shè)計(jì)與實(shí)現(xiàn)UART。

2012-05-23 19:37:24

用VS1003做(支持SD卡_TF卡_U盤)__原創(chuàng)制作

2012-08-16 17:01:42

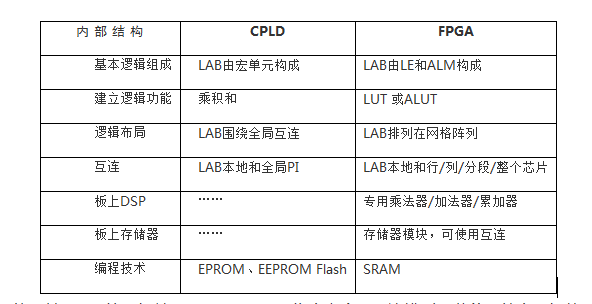

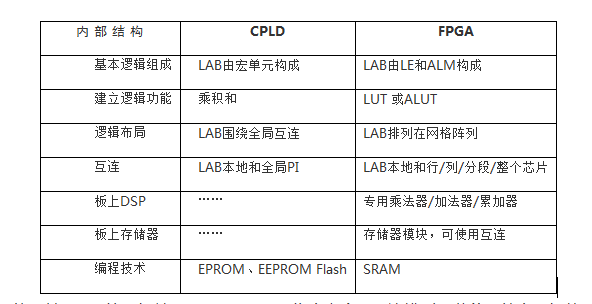

FPGA與CPLD的辨別和分類主要是根據(jù)其結(jié)構(gòu)特點(diǎn)和工作原理。通常的分類方法是:將以乘積項(xiàng)結(jié)構(gòu)方式構(gòu)成邏輯行為的器件稱為CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列

2019-07-01 07:36:55

FPGA與CPLD的區(qū)別

盡管很多人聽說過CPLD,但是關(guān)于CPLD與FPGA之間的區(qū)別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復(fù)編程的邏輯器件”,但是在技術(shù)上卻有一些差異。簡(jiǎn)單

2011-09-27 09:49:48

。⑧CPLD保密性好,FPGA保密性差。⑨一般情況下,CPLD的功耗要比FPGA大,且集成度越高越明顯。隨著復(fù)雜可編程邏輯器件(CPLD)密度的提高,數(shù)字器件設(shè)計(jì)人員在進(jìn)行大型設(shè)計(jì)時(shí),既靈活又容易,而且產(chǎn)品

2012-10-26 08:10:36

盡管很多人聽說過FPGA和CPLD,但是關(guān)于FPGA與CPLD之間的區(qū)別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復(fù)編程的邏輯器件”,但是在技術(shù)上卻有一些差異。簡(jiǎn)單地說,F(xiàn)PGA就是將

2019-02-21 06:19:27

CPLD是什么?FPGA包含哪幾類可編程資源呢?FPGA可編程器件和CPLD可編程器件有哪些相同點(diǎn)和不同點(diǎn)?

2021-11-10 07:42:51

IIC總線通訊接口器件的CPLD實(shí)現(xiàn)摘要:介紹了采用ALTERA公司的可編程器件EPF10K10LC84-3實(shí)現(xiàn)IIC總線的通訊接口的基本原理,并給出了部分的VHDL語(yǔ)言描述。該通訊接口與專用的接口芯片相比,具有使用靈活、系統(tǒng)配置方便的特點(diǎn)。 [/hide]

2009-10-30 14:57:35

`現(xiàn)在我有一個(gè)atmel的cpld芯片,用了個(gè)如下圖所示的下載線一直不能發(fā)現(xiàn)設(shè)備,如圖.不知道哪位大哥告訴一下該怎么玩,另買一個(gè)altera的byteblaster嗎我只有一個(gè)積分。。`

2015-12-18 21:07:50

本帖最后由 palatree 于 2012-3-22 16:42 編輯

本節(jié)將介紹,如何在FPGA/CPLD中用I2C實(shí)現(xiàn)多個(gè)芯片的連接?I2C總線的特點(diǎn)除了電源和接地使用只有2線(名為“問責(zé)

2012-03-22 16:40:33

UID Unique Identification)等功能以保護(hù)用戶的設(shè)計(jì)安全。

Compact系列CPLD器件 包含G(通用型)、L(低功耗)和D支持主自加載雙啟動(dòng)功能三種版本,支持兩個(gè)速度等級(jí)5和6

2024-04-27 21:42:48

橫機(jī)是針織機(jī)械的一種,為生產(chǎn)羊毛衫,圍巾帽子等的主要生產(chǎn)設(shè)備,全機(jī)由130多個(gè)零件裝置而成。橫機(jī)機(jī)頭板需要控制很多針,一般使用CPLD(Complex Programmable Logic

2022-11-14 06:52:19

單片機(jī)的優(yōu)缺點(diǎn)分別是什么?CPLD器件的優(yōu)缺點(diǎn)有哪些?為什么會(huì)說CPLD器件和單片機(jī)結(jié)合能優(yōu)勢(shì)互補(bǔ)?CPLD器件和單片機(jī)是如何進(jìn)行優(yōu)勢(shì)互補(bǔ)的?

2021-04-14 07:09:40

什么時(shí)候適合采用CPLD替代微控制器?什么時(shí)候可以采用CPLD作為微控制器的輔助器件?

2021-04-28 06:16:59

多種配置模式,支持遠(yuǎn)程升級(jí)和雙啟動(dòng)功能,同時(shí)提供UID(Unique Identification)等功能以保護(hù)用戶的設(shè)計(jì)安全。Compact 系列 CPLD 器件包含 G(通用型)、L(低功耗)和D

2024-03-16 07:08:16

可編程邏輯器件FPGA/CPLD結(jié)構(gòu)與應(yīng)用.ppt

2017-01-21 20:34:49

本設(shè)計(jì)利用CPLD進(jìn)行數(shù)字邏輯器件設(shè)計(jì),并配合多路精密程控放大,實(shí)現(xiàn)了寬輸入范圍高精度頻率測(cè)量,頻率測(cè)量穩(wěn)定度達(dá)10 -7,而且將輸入信號(hào)的范圍進(jìn)行了有效地拓寬,使這種高精度頻率計(jì)的應(yīng)用領(lǐng)域更加廣泛。同時(shí),解決了傳統(tǒng)分立數(shù)字器件測(cè)頻時(shí)存在的問題。

2021-05-14 06:24:24

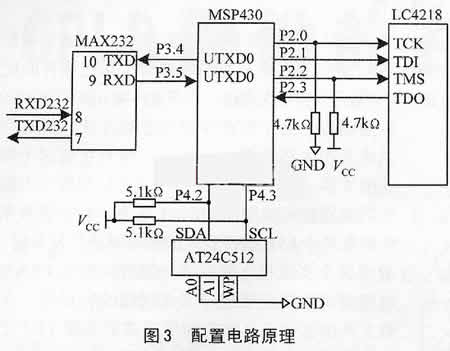

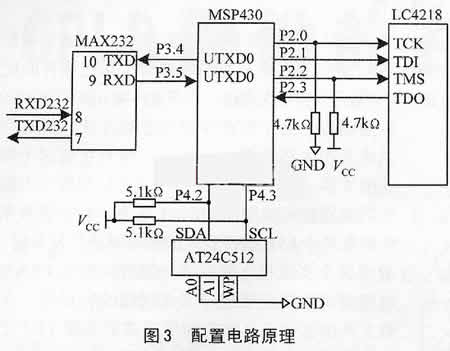

本文介紹一個(gè)用微控制器在系統(tǒng)配置Lattice MACH4000系列CPLD器件的方案。

2021-04-30 06:43:20

數(shù)字增益控制電路的原理是什么如何用CPLD器件實(shí)現(xiàn)DAGC運(yùn)算?數(shù)控衰減器在中頻電路中引入的沖擊振蕩問題數(shù)控衰減器的實(shí)現(xiàn)方法

2021-04-08 06:02:44

本設(shè)計(jì)采用了復(fù)雜可編程器件CPLD,用CPLD完成了PC104總線與429總線通訊的主要電路,大大節(jié)省了硬件資源,本文著重介紹了CPLD部分的設(shè)計(jì)。

2021-04-29 06:47:46

如何采用Altera的CPLD器件實(shí)現(xiàn)時(shí)間統(tǒng)一系統(tǒng)的B碼源設(shè)計(jì)?

2021-05-07 06:21:24

安路CPLD支持熱插拔不?

2023-08-11 10:00:03

安路的CPLD可以支持在線升級(jí)不?

2023-08-11 06:06:11

安路的CPLD可以支持級(jí)聯(lián)不?

2023-08-11 08:45:57

安路CPLD可以支持背景升級(jí)不?

2023-08-11 06:08:19

請(qǐng)問8148能支持64SD卡嗎,用是可以用,但是看到8148手冊(cè)上說SD卡支持2.0協(xié)議,而2.0協(xié)議上說支持的SD卡容量最大到32GB,所以我才有了這個(gè)疑問

2019-02-22 11:26:53

從器件資料中看到DM368能夠同時(shí)處理多個(gè)視頻流,但是在硬件連接上沒有看到多個(gè)視頻的輸入接口,是不是DM368本身不支持多個(gè)鏡頭呢?還是說有特殊的方式來支持?

2019-08-23 09:05:37

XC9500系列CPLD器件是什么?XC9500系列CPLD器件遙控編程的實(shí)現(xiàn)方法有哪些?如何實(shí)現(xiàn)CPLD遙控編程?

2021-04-27 07:15:42

用Xilinx CPLD作為電機(jī)控制器

2008-07-28 15:49:42 51

51 《Altera FPGA/CPLD設(shè)計(jì)(高級(jí)篇)》結(jié)合作者多年工作經(jīng)驗(yàn),深入地討論了Altera FPGA/CPLD的設(shè)計(jì)、優(yōu)化技巧。在討論FPGA/CPLD設(shè)計(jì)指導(dǎo)原則的基礎(chǔ)上,介紹了Altera器件的高級(jí)應(yīng)用;引領(lǐng)讀者

2009-02-12 09:19:12 4807

4807 ATMEL CPLD ATF15XX器件的下載軟件 (for Windows)

2009-03-21 11:52:16 47

47 EPM570T144C5N - 芯片, CPLD, MAX II, 570單元, 144TQFP

2022-07-29 17:19:16

用ALTERA 公司MAX7000 系列CPLD 芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA 總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL 設(shè)計(jì)部分。

2009-04-14 17:36:07 29

29 用ALTERA 公司MAX7000 系列CPLD 芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA 總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL 設(shè)計(jì)部分。

2009-05-14 13:24:39 16

16 介紹利用Altera 公司CPLD 器件實(shí)現(xiàn)對(duì)電機(jī)高精度、寬范圍調(diào)速的控制方案,并給出簡(jiǎn)明扼要的VHDL 程序結(jié)構(gòu)與仿真結(jié)果。

2009-05-15 14:00:03 23

23 可編程邏輯器件cpld 和fpga 以及xilinx webpack 4.2 ISE 的介紹;用xilinxwebpack 4.2 ISE 設(shè)計(jì)七段譯碼器的顯示.關(guān)鍵詞 ASIC Xinlinx

2009-08-15 09:21:52 22

22 UART 是廣泛使用的串行數(shù)據(jù)通訊電路。本設(shè)計(jì)包含UART 發(fā)送器、接收器和波特率發(fā)生器。設(shè)計(jì)應(yīng)用EDA 技術(shù),基于FPGA/CPLD 器件設(shè)計(jì)與實(shí)現(xiàn)UART。關(guān)鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 24

24 CPLD 器件應(yīng)用隨著生產(chǎn)工藝的逐步提高以及 CPLD 開發(fā)系統(tǒng)的不斷完善,CPLD 器件容量也由幾百門飛速發(fā)展到百萬(wàn)門以上,使得一個(gè)復(fù)雜數(shù)字系統(tǒng)完全可以在一個(gè)芯片中實(shí)現(xiàn)。HDL

2010-01-27 11:40:02 48

48 CPLD 器件在單片機(jī)控制器中的使用摘要:CPLD 器件與單片機(jī)結(jié)合,可以優(yōu)勢(shì)互補(bǔ),組成靈活的、硬軟件都可現(xiàn)場(chǎng)編程的控制器,縮短開發(fā)周期,適應(yīng)市場(chǎng)需要。結(jié)合實(shí)際工作的經(jīng)驗(yàn)

2010-02-08 09:49:56 42

42 用CoolRunner-II CPLD降低設(shè)計(jì)難度(提高易用性):CoolRunner-II CPLD 入門套件內(nèi)置實(shí)時(shí)功耗測(cè)量與報(bào)告功能。XMeter程序讀出1.8V電源的功耗測(cè)量值,并且將數(shù)據(jù)實(shí)時(shí)繪制成曲線圖。

2010-04-25 10:27:26 16

16 基于FPGA/CPLD芯片的數(shù)字頻率計(jì)設(shè)計(jì)摘要:詳細(xì)論述了利用VHDL硬件描述語(yǔ)言設(shè)計(jì),并在EDA(電子設(shè)計(jì)自動(dòng)化)工具的幫助下,用大規(guī)模可編程邏輯器件(FPGA/CPLD)實(shí)現(xiàn)

2010-04-30 14:45:13 132

132 當(dāng)利用CPLD/FPGA開發(fā)系統(tǒng)完成數(shù)字電路或系統(tǒng)的開發(fā)設(shè)計(jì)并仿真校驗(yàn)通過之后,就需要將獲得的CPLD/FPGA編程配置數(shù)據(jù)下載到CPLD/FPGA芯片中,以便最后獲得所設(shè)計(jì)的硬件數(shù)字電路或系

2010-06-01 10:14:46 24

24 設(shè)計(jì)了一種基于DSP+CPLD構(gòu)架的電能質(zhì)量監(jiān)測(cè)裝置,該裝置利用CPLD產(chǎn)生DSP外圍器件的控制時(shí)序,丈中詳細(xì)介紹了CPLD對(duì)DSP外圍器件的邏輯接口設(shè)計(jì),通過MAX+PLUSII對(duì)CPLD的控制時(shí)序進(jìn)行

2010-08-26 16:06:20 31

31 以CPLD器件EPM7128SLC84-6為核心的電器定時(shí)開關(guān)控制系統(tǒng)設(shè)計(jì)實(shí)現(xiàn)24小時(shí)制時(shí)鐘功能,可同時(shí)設(shè)置多個(gè)電器的定時(shí)自動(dòng)開啟和關(guān)閉,開關(guān)時(shí)間從0時(shí)0分到23時(shí)59分之間任意可調(diào)。CPLD部分使

2010-12-17 15:42:23 28

28 摘要:用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL設(shè)計(jì)部分。CPLD(Complex Programmable Logi

2006-05-26 21:52:11 1159

1159

用單片機(jī)配置CPLD器件

ALTERA公司的可編程序邏輯器件APEX20K、FLEX10K和FLEX6000雖應(yīng)用廣泛,但由于其內(nèi)部采用SRAM存儲(chǔ)配置數(shù)據(jù),每次系統(tǒng)上電時(shí),必須用配置芯片對(duì)其進(jìn)行配置

2009-03-28 16:18:06 1423

1423

什么是CPLD

CPLD(Complex Programmable Logic Device)是Complex PLD的簡(jiǎn)稱,一種較PLD為復(fù)雜的邏輯元件。CPLD是一種用戶根據(jù)各自

2009-03-30 13:40:43 4116

4116 以下是引用片段: 摘要: 介紹一種利用微控制器動(dòng)態(tài)配置CPLD器件的方法。將配置文件存放在存儲(chǔ)器中,配置文件中的控制代碼驅(qū)動(dòng)在微處理器中運(yùn)行的配置引擎;將配置文件中的配置信息通過JTAG口移入

2009-06-20 10:44:21 3425

3425

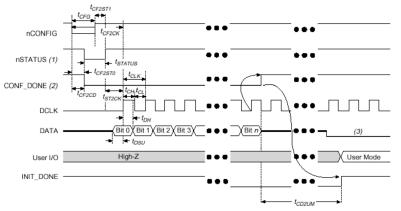

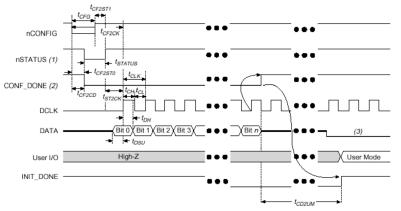

一、 配置方式

ALTERA CPLD器件的配置方式主要分為兩大類:主動(dòng)配置方式和被動(dòng)方式。主動(dòng)配置方式由CPLD器件引導(dǎo)配置操作過程,它控制著外部存儲(chǔ)器和

2009-06-20 10:58:14 2674

2674 摘 要 :UART是廣泛使用的串行數(shù)據(jù)通訊電路。本設(shè)計(jì)包含UART發(fā)送器、接收器和波特率發(fā)生器。設(shè)計(jì)應(yīng)用EDA技術(shù),基于FPGA/CPLD器件設(shè)計(jì)與實(shí)現(xiàn)UART。

2009-06-20 13:14:52 1267

1267

摘要:用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL設(shè)計(jì)部分。

關(guān)鍵詞:CPLD

2009-06-20 13:34:28 1360

1360

?摘 要:介紹了一種利用ALTERA公司的復(fù)雜可編程邏輯器件(CPLD)快速卷積法實(shí)現(xiàn)數(shù)字濾波器的設(shè)計(jì)??? 關(guān)鍵詞:CPLD 數(shù)字濾波器 信號(hào)處理

2009-06-20 14:23:56 1317

1317

CPLD,CPLD是什么意思

CPLD是指結(jié)構(gòu)比較復(fù)雜的可編程邏輯器件,它包括下述輸出宏單元結(jié)構(gòu):

(1)可編程I/O 允

2010-03-26 17:08:50 3555

3555 具體介紹了基于CPLD 器件設(shè)計(jì)單穩(wěn)態(tài)窄脈沖展寬電路的詳細(xì)過程和這種單穩(wěn)態(tài)窄脈沖展電路的特點(diǎn),給出了相應(yīng)的時(shí)序仿真波形,提出了提高展寬脈沖寬度精確度的方法。

2011-12-17 00:23:00 35

35 整個(gè)設(shè)計(jì)采用MAX+ plus II開發(fā)平臺(tái),VHDL編程實(shí)現(xiàn),基于可編程邏輯器件CPLD設(shè)計(jì)多波形信號(hào)發(fā)生器。用VHDL編程實(shí)現(xiàn),其設(shè)計(jì)過程簡(jiǎn)單,極易修改,可移植性強(qiáng)。系統(tǒng)以CPLD為核心,采用直接數(shù)字合成技術(shù),輔以必要的模擬電路,構(gòu)成一個(gè)波形穩(wěn)定,精度較高的函數(shù)信號(hào)發(fā)生器。

2016-10-12 16:51:10 15

15 可編程邏輯器件FPGA/CPLD結(jié)構(gòu)與應(yīng)用

2016-12-11 23:38:39 0

0 用CPLD實(shí)現(xiàn)FIR數(shù)字濾波器的設(shè)計(jì),下來看看

2017-01-10 21:35:20 15

15 用CPLD實(shí)現(xiàn)FIR數(shù)字濾波器,好資料,下來看看

2017-01-10 21:35:20 24

24 CPLD和FPGA都是我們經(jīng)常會(huì)用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區(qū)分,把他們都叫做FPGA。那么兩者到底有什么區(qū)別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區(qū)別。

2017-09-18 16:35:32 5

5 FPGA(Field-Programmable Gate Array),即現(xiàn)場(chǎng)可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域

2017-10-24 10:04:00 48952

48952 CPLD即復(fù)雜可編程邏輯器件,是從PAL和GAL器件發(fā)展出來的器件,相對(duì)而言規(guī)模大,結(jié)構(gòu)復(fù)雜,屬于大規(guī)模集成電路范圍。是一種用戶根據(jù)各自需要而自行構(gòu)造邏輯功能的數(shù)字集成電路。其基本設(shè)計(jì)方法是借助集成

2017-10-24 10:40:00 103030

103030 CPLD(Complex Programmable Logic Device)復(fù)雜可編程邏輯器件,是從PAL和GAL器件發(fā)展出來的器件,相對(duì)而言規(guī)模大,結(jié)構(gòu)復(fù)雜,屬于大規(guī)模集成電路范圍。是一種用戶

2017-10-24 11:37:04 14470

14470 PLD和FPGA都是由邏輯陣列模塊構(gòu)成的,但是CPLD LAB基于乘積和宏單元,而FPGA LAB使用基于LUT的邏輯單元。CPLD LAB圍繞中心全局互連排列,隨著器件中邏輯數(shù)量的增加,呈指數(shù)增長(zhǎng)。

2018-04-17 17:08:00 3668

3668

AMD公司最先生產(chǎn)帶有宏單元的可編程邏輯器件PAL22V10。目前PAL22V10已成為劃分PLD的界限。可編程邏輯器件所包含的門數(shù)大于PAL22V10所包含則門數(shù),就被認(rèn)為是復(fù)雜可編程邏輯器件,即CPLD。

2018-05-24 01:39:00 4488

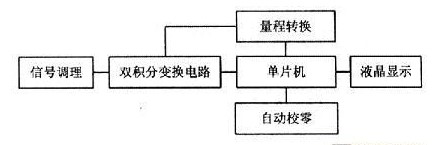

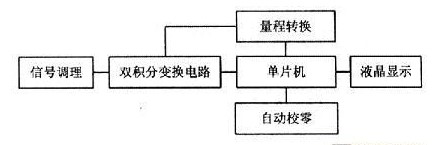

4488 設(shè)計(jì)了基于CPLD的數(shù)字電壓表,采用CPLD器件作為核心處理電路,用單片機(jī)進(jìn)行控制,能較好地減小外界干擾,提高分辨率。該數(shù)字電壓表能夠自動(dòng)轉(zhuǎn)換量程,從而可提高數(shù)字電壓表的性能。

2019-04-23 08:28:00 2979

2979

介紹了一種用CPLD(復(fù)雜可編程邏輯器件)作為核心控制電路的測(cè)試系統(tǒng)接口,通過時(shí)cPLD和竹L電路的比較及cPLD在系統(tǒng)中實(shí)現(xiàn)的強(qiáng)大功能,論述了CPLD在測(cè)試系統(tǒng)接口中應(yīng)用的可行性和優(yōu)越性,簡(jiǎn)單介紹

2019-01-01 16:18:00 2544

2544

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA教程之ALTERA的CPLD與FPGA器件的詳細(xì)資料說明主要內(nèi)容包括了:一、Altera器件一般介紹,二、MAX 7000 系列器件,三、FLEX10K系列器件,四、邊界掃描測(cè)試

2019-02-27 17:27:31 17

17 以 CPLD 器件 EPM7128SLC84- 6 為核心的電器定時(shí)開關(guān)控制系統(tǒng)設(shè)計(jì)實(shí)現(xiàn) 24 小時(shí)制時(shí)鐘功能, 可同時(shí)設(shè)置多個(gè)電器的定時(shí)自動(dòng)開啟和關(guān)閉, 開關(guān)時(shí)間從 0 時(shí) 0 分到 23

2019-06-11 08:00:00 4

4 FPGA/CPLD能完成任何數(shù)字器件的功能,上至高性能CPU,下至簡(jiǎn)單的74電路,都可以用FPGA/CPLD來實(shí)現(xiàn)。

2020-01-20 09:29:00 4186

4186 。而計(jì)劃在 2021 年年初發(fā)布的 Linux 5.11 內(nèi)核將初步支持 7.10 規(guī)范以及更高版本的核心支持。 在今年 5 月發(fā)布 SD Express 8.0 規(guī)范以來,有關(guān)于該規(guī)范的新聞就比較

2020-12-16 14:11:14 1839

1839

FPGA CPLD可編程邏輯器件的在系統(tǒng)配置方法(深圳市村田電源技術(shù)有限公司)-FPGA CPLD可編程邏輯器件的在系統(tǒng)配置方法? ? ? ? ? ? ? ? ? ?

2021-09-18 10:51:20 13

13 在Linux開源操作系統(tǒng)迎來30 周年之際,Analog Devices, Inc. (ADI)宣布擴(kuò)充其Linux發(fā)行版的器件驅(qū)動(dòng),讓Linux內(nèi)核能夠識(shí)別并支持1000多個(gè)ADI外設(shè)。

2021-12-01 11:15:57 1404

1404

電子發(fā)燒友網(wǎng)站提供《用XC9536制作小型CPLD學(xué)習(xí)板.zip》資料免費(fèi)下載

2022-07-22 11:30:30 3

3 電子發(fā)燒友網(wǎng)站提供《Compact系列CPLD器件數(shù)據(jù)手冊(cè).pdf》資料免費(fèi)下載

2022-09-26 10:18:18 3

3 CPLD的MAX系列器件庫(kù)max-13.0.1.232

2022-12-21 17:26:11 9

9 可編程邏輯包括 PAL、GAL、PLD 等。通過不斷發(fā)展,它已經(jīng)發(fā)展成為現(xiàn)在的CPLD/FPGA。CPLD(復(fù)雜可編程邏輯器件)和FPGA(現(xiàn)場(chǎng)可編程門陣列)的功能基本相同,只是實(shí)現(xiàn)原理略有不同。當(dāng)

2023-07-03 14:33:38 10709

10709

本文檔主要描述了深圳市紫光同創(chuàng)電子有限公司(以下簡(jiǎn)稱紫光同創(chuàng))Compact 系列 CPLD 器件 的產(chǎn)品型號(hào)與資源規(guī)模列表、功能說明,以及直流和交流特性等內(nèi)容,能讓用戶對(duì) CPLD 器件有全面 的了解,方便用戶進(jìn)行器件選型。

2023-07-04 14:52:43 17

17 你知道CPLD嗎?它是“復(fù)雜可編程邏輯器件”的縮寫,它是一種數(shù)字IC,允許用戶根據(jù)需要多次重寫和擦除程序。隨著CPLD等可編程器件的出現(xiàn),產(chǎn)品開發(fā)變得更快、成本更低。在本文中,將介紹CPLD和PLD(可編程邏輯器件)。

2023-07-06 14:30:49 8126

8126 增長(zhǎng)。FPGA的LAB以網(wǎng)格陣列排列,隨器件密度線性增長(zhǎng)。CPLD互連包括LAB本地可編程陣列及中心可編程互連。FPGA器件除了包括本地互連,用于各個(gè)LAB,但是和LAB邏輯分開,器件還包括行列互連,這些互連跨過陣列中的多個(gè)LAB,以及整個(gè)芯片的長(zhǎng)寬。

2024-01-23 09:17:04 2281

2281 FPGA(現(xiàn)場(chǎng)可編程門陣列)和CPLD(復(fù)雜可編程邏輯器件)都是可編程邏輯器件,但它們?cè)?b class="flag-6" style="color: red">多個(gè)方面存在顯著的區(qū)別。

2024-03-15 14:56:58 2318

2318 派4B支持的SD卡類型 樹莓派4B支持的SD卡類型主要有以下幾種: 1.1 SD卡(Secure Digital Card) SD卡是一種非常常見的存儲(chǔ)卡類型,廣泛應(yīng)用于各種設(shè)備中。樹莓派4B支持標(biāo)準(zhǔn)

2024-08-30 17:02:28 3665

3665 (Complex Programmable Logic Device) :CPLD是一種可編程邏輯器件,通常由多個(gè)小規(guī)模的邏輯單元組成,這些單元通過可編程的互連網(wǎng)絡(luò)連接起來。CPLD適合于實(shí)現(xiàn)小規(guī)模到中等規(guī)模

2025-01-23 09:46:36 2762

2762 隨著電子技術(shù)的快速發(fā)展,可編程邏輯器件在各個(gè)領(lǐng)域中的應(yīng)用越來越廣泛。CPLD作為一種靈活、成本效益高的解決方案,被廣泛應(yīng)用于多種電子系統(tǒng)設(shè)計(jì)中。 CPLD概述 CPLD是一種可編程邏輯器件,它通過

2025-01-23 09:48:12 2315

2315 CPLD(Complex Programmable Logic Device,復(fù)雜可編程邏輯器件)的功耗控制是嵌入式系統(tǒng)設(shè)計(jì)中的重要考慮因素,特別是在便攜式或電池供電的設(shè)備中。以下是一些關(guān)鍵

2025-01-23 10:00:03 1116

1116 可編程的邏輯器件,它允許設(shè)計(jì)者在制造后對(duì)邏輯功能進(jìn)行配置。CPLD通常由多個(gè)可配置的邏輯塊(Logic Blocks)和可編程互連(Interconnect)組成,這些邏輯塊通過編程可以連接成復(fù)雜的邏輯功能。 1.2 ASIC(應(yīng)用特定集成電路) ASIC是一種為特定應(yīng)用定制的集成電路,它在設(shè)計(jì)

2025-01-23 10:04:17 1338

1338

圖1 用CPLD增加SD端口

圖1 用CPLD增加SD端口

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論