?

| 以下是引用片段: |

?

關鍵詞: ISP 在系統可編程技術 動態配置 CPLD

引言

隨著應用的不斷深入,嵌入式系統升級的問題擺在了人們面前。在這種背景下ISP技術應運而生。

在系統可編程ISP(In Ststem Programmability)技術是指能對器件、電路甚至整個系統進行現場升級和功能重構的技術。這種重構可以在實驗開發過程中、制造過程中,甚至是在交付用戶使用之后進行;而整個在系統可編程設計的最后一個步驟,也是最關鍵的步驟,也是最關鍵的步驟,就是器件的配置。配置過程加載設計規定的編程數據到器件中,以定義器件內部功能塊及其互連,從而實現器件功能的重構升級。

當然ISP配置方式是多種多樣的,其中計算機加下載線就是最常見的配置器件的方法;但是這個方法需要計算機配合,對嵌入式系統來說不太實用,因此需要一個更加方便靈活的配置方案。Lattice公司CPLD器件不僅具有ISP功能,同時融合引腳鎖定功能和JTAG技術,使得拋棄計算機而使用微控制器在系統配置、修改、升級CPLD器件成為可能。特別是引腳鎖定功能,實現了真正意義上的“動態”配置。采用引腳鎖定技術,將配置前引腳狀態鎖定,配置完成以后各個引腳仍能保持配置前狀態。本文介紹一個用微控制器在系統配置Lattice MACH4000系列CPLD器件的方案。

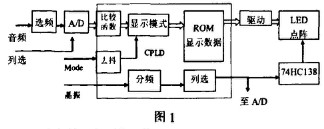

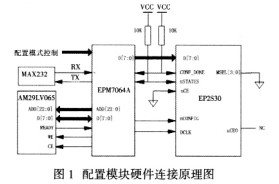

圖1

1 原理

ISP器件要實現配置,除了ISP器件的硬件系統中要提供正確的ISP接口以外,還需要有配置文件和配置工具。

(1)配置接口

Lattice公司為器件提供了ISP接口和JTAG接口。

ISP接口是Lattice公司自行開發設計的,具有如下引腳定義:

SDI——數據輸入和狀態機控制;

MODE——和SDI一起控制狀態機;

MODE——和SDI一起控制狀態機;

SCLK——時鐘輸入;

SDO——數據輸出,可選引腳;

IspEN——工作模式和配置模式選擇,同時還有一個ISP狀態機,包含3個狀態,由MODE和SDI控制狀態機所處技術,在Shift狀態通過SDI移入命令,在Execute狀態執行命令。

聯合測試行動小組JTAG(Joint Test Action Group)在20世紀80年代中期制定了邊界掃描技術,在1990年被修改后成為IEEE的一個標準——IEEE1149.1-1990。這個標準即為JTAG。邊界掃描技術最初發展鹽業,是為了測試電路各個IC器件之間的互邊是否正確。隨著ISP發展,許多生產廠商利用JTAG規定的四條引腳的測試存取口作為ISP的開發平臺,使得ISP也變得有標準可循,給用戶帶來了極大方便,于是JTAG在其權限內把ISP性能擴充到了IEEE1149.1中。發展到現在可以這樣說,IEEE1149.1標準為我們提供了一條簡單的串行接口,將那些具有JTAG接口的器件串接在一打掃描鏈中。通過這個接口既能實現ISP又能實現測試。

IEEE1149.1標準對邊界掃描結構的定義包括4個基本單元:4個引腳的測試存取口TAP(Test Access Port)、數據寄存器、指令寄存器和TAP控制器。TAP引腳定義如下:TCK為測試時鐘輸入,TDI為測試數據輸入,TDO為測試數據輸出,TMS為測試模式選擇。數據寄存器包含兩種BYPASS寄存器和BSR(Boundary Scan Register)寄存器,其中BSR由BSC(Boundary Scan Cell)串聯而成,正是通過BSC才把來自于TAP的數據移入ISP芯片內部邏輯。另外TAP控制器作為一個有限狀態機,共有16個狀態。它控制著測試存取口、指令寄存器和數據寄存器。TAP控制器如圖1所示。

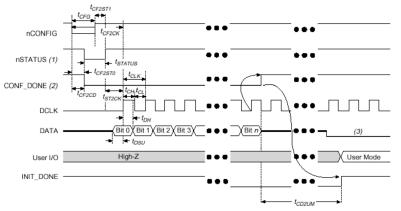

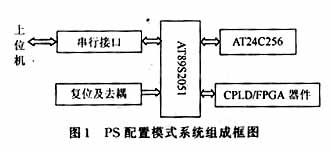

通過TCK、TMS控制TAP控制器的狀態。當TAP控制器處于Shift-IR狀態時,TDI口進入的指令被移進指令寄存器;當TAP控制器入于Update-IR狀態時,指令寄存器的指令有效。根據這個原理,通過控制此狀態機,將配置信息移入器件內。另外,TAP測試存取口4個引腳有嚴格的時序要求,如圖2所示。

其中TMS、TDI在TCK上升沿有效,TDO在TCK下降沿有效。要想通過JTAG口實現ISP或者測試,都必須遵守這些時序要求。

通過對兩種接口的研究發現,它們均能實現ISP,然而JTAG口的測試功能以及與其它具有JTAG口器件之間的靈活的連接性顯得更有優勢,這也使得Lattice公司認識到了ISP接口的局限,因此在它后來開發生產的新器件中都采用了JTAG。在本方案中用到的LatticeMACH4000系列CPLD器件,運行頻率最高達400MHz,待機電流僅為20μA,宏單元數目最高達1024個,引腳到引腳延時2.5ns,在系統配置要用JTAG接口。

圖2

(2)配置文件

在進行配置前需要得到一個JED文件,也就是我們所說的熔絲圖文件。在這個文件里包含了相應器件的配置信息,即該器件內部互連邏輯。在開發環境ispLEVER3.0里按照自上而下的順序進行邏輯設計,經過行為仿真和時序仿真后,開發環境將生成這個熔絲圖文件。除了JED文件,另外還需要一個能說明菊花花鏈組成順序的.xcf文件。特別是當系統中有多個ISP器件且組成菊花鏈進行配置時,通過這個文件將分散在各個器件內部的JTAG鏈按照先后順序組成一條系統級的掃描鏈,下載工具通過這個文件里的信息決定當前TDI上的數據是哪個器件的數據。有了這2個文件以后就可以通過下載工具進行器件配置了。

(3)配置工具

Lattice公司在PC和Workstation平臺提供的下載工具叫IspVM。通過這個下載軟件加上下載線可以實現器件配置。另外,Lattice在業界首創的利用系統板上的微控制器或微處理器進行編程的嵌入式、多供應商、單鏈、在系統可編程工具IspVM EMBEDDED,作為一種軟件實現,一旦在微控制器或處理器安裝成功,系統將有能力直接通過電路板上的處理器對板上所有可編程邏輯器件進行編程或再編程,而無需使用下載電費或人工干預。當然,為了使用這種軟件,必須將JED文件轉化成該軟件支持的文件格式VME。VME作為專門支持IspVM EMBEDDED的文件,里面除了包括來自于JED和XCF的配置信息以外,不覺包括了能驅動IspVM EMBEDDED配置引擎的控制信息。正是這些控制信息使TAP狀態機進入相應狀態,從而將配制信息移入器件內。需要注意的是,如果要將VME存儲在存儲器上,還需要將其轉化成HEX格式。本方案將在MSP430單片機上實現IspVM EMBEDDED,從而提供一種嵌入式系統升級方案。

2 方案設計

系統硬件電路如圖3所示。

MSP430單片機P2口作為配置接口,接到Lattice MACH4128V的JTAG口上,外掛一個E2PROM,用來存儲HEX格式的VME文件。整個過程是,通過串口接收來自計算機的配置文件,放到E2PROM,接收完畢以后,單片機運行配置引擎,讀取E2PROM,配置指令通過JTAG口對Lattice MACH 4128V進行配置。需要指出的是,Lattice MACH 4128V并沒有用專門的引腳來控制進入配置模式或退出配置模式,而僅僅是通過TAP控制所處狀態來決定的。IEEE1149.1標準中規定:器件加電時或應用中不利用邊界掃描邏輯,強迫TAP控制器處于Test-Logic-Reset狀態,因此在通過程序控制JTAG進行器件配置結束時,一定要通過軟件方式強迫TAP控制器回到Test-Logic-Reset狀態,下面提到的ispVMEnd()函數實現的就是這個功能。另外,當通過JTAG口完成器件配置或測試以后,TMS、TDI引腳器件內部上拉。雖然如此,為了防止TCK可能出現的信號使JTAG狀態機離開Test-Logic-Reset狀態,或者因為上電瞬間可能產生的TCK信號導致狀態機進入未知狀態,設計電路時必須在TMS引腳加4.7kΩ下拉電阻。另外,電路中Vcc=3.3V。

3 軟件介紹

軟件部分包括PC機程序和MSP430單片機程序。其中PC機程序將HEX格式的VME文件通過串口傳送給單片機;MSP430單片機程序包括ispVM EMBEDDED,串口讀寫和E2PROM讀寫部分。

作為整個配置的核心,ispVM EMBEDDED主要由存儲在E2PROM的VME文件驅動,從而將配置信息串行移入Lattice MACH 4128中。整個過程如下:首先,驗證VME文件的版本,只有相應版本的ispVM EMBEDDED才能解釋同樣版本的VME文件,ispVMStart()函數強迫TAP狀態機進入配置主引擎ispVMCode(),來自于VFME中的控制代碼將驅動這個引擎執行相應操作,其中3個控制代碼最為常見的STATE、SIR、SDR和STATE代碼控制TAP狀態機進入聲明的狀態,如Shift-DR、Shift-IR等。SIR代碼表明將向器件中移入指令流,SDR代碼表明將向器件中移入數據流。通過這種方式,配置主引擎ispVMCode()將VME中包含的配置信號器件從而完成配置,配置完成ispVMCode()返回一個配置成功與否的代碼。最后ispVMEnd()強迫TAP狀態機進入Test-Logic-Reset狀態。

Void ispVMEnd(void){

IspVMStateMachine(RESET);/*TAP狀態機進入Test-Logic-Reset狀態*/

IspVMDelay(1);/*一段延時后,器件由配置模式切換到運行模式*/

}

事實上,作為專門針對嵌入式平臺的配置工具ispVM EMBEDDED并不依賴于特定的硬件或系統平臺,所以可以很容易地往用戶自己的系統上移植。3個與硬件相關的函數需要用戶自己改寫,Readprot()從輸入引腳讀一個字節,Writeport()通過輸出引腳向外發送一個字節,ispVMDelay()系統延時。在MSP430上的實現如下:

#define pinTDI 0x02 //定義P2.1為TDI

#define pinTDO 0x08 //定義P2.3為TDO

short int isp_pins用來存放當前JTAG口的引腳信號

unsigned char readPort(void){

unsigned char PortVal;

PortVal=P2IN; //讀取P2口

return ((unsigned char)(PortVal &pinTDO)?0x01:0x00));//返回TDO引腳信號

}

void writePort(unsigned char pins,unsigned char value){

if(value)

isp_pins=pins|isp_pins;//把isp-pins引腳置高

else

isp_pins=~pins&isp_pins;//把isp-pins引腳置低

P2OUT=isp_pins;

}

void ispVMDeay(unsigned short int delay_time){//delay_time來自于配置文件,通過它告訴配置引擎具體需要延時多久

if(delay_time &0xA000){//ms級延時

delay_time &=~0xA000;

}

else if(delay_time>=1000)//如果是μs級,轉換成ms級延時

delay_time=delay_time/1000;

else

delay_time=1;//延時小于1ms時,就延時1ms

PS1ms=delay_time;

CCTL0=CCIE; //開定時

while(PS1ms){};//在中斷PS1ms

CCTL0&=~CCIE; //關定時

}

有一點需要指出,ispVM EMBEDDED要求將已轉化成HEX格式的VME作為程序的一部分固化在單片機里。很顯然,要想更換配置文件,就必須連同單片機程序一同換掉。這對實現動態配置是不利的,也是為什么在本方案中外加E2PROM的原因。這樣無須更改程序,只換掉E2PRO中的配置文件即可。因此還需要更改GetByte()函數。

對24C512的操作應該遵循I2C總線協議,而在MSP430中沒有I2C總線硬件,所以本方案中用軟件方法模擬。由于I2C串行總線數據交換速度較慢,因而當從E2PROM中讀出數據再往CPLD中移入時,形成了配置過程的速度瓶頸。在解決這個問題時,我們充分利用了MSP430149單片機內部2KB RAM,采用E2PROM最快的讀取方式——順序讀,將配置數據預先讀入到RAM中,GetByte()函數直接從RAM中讀取數據。這種方法在一定程度上提高了配置速度。我們改寫的GetByte()函數是這樣的:

unsigned char GetByte()

{ unsigned char data;

static unsigned short int index=0;

……

if(index==0){ //有新的數據來自E2PROM

fp=wmeArray;//放在unsigned char vmeArray[1024]

}

data=*fp++;

if(index<1024)

index++;

else {

index=0;

if((num+1024)>totalnum是已經讀取字節數)

ReadBlock(address,totalnum-num);//totalnum是整個配置文件字節數

}

else{

ReadBlock(address,1024);//從I2PROM的

address=adress+1024;//adress地址開始讀1024字節

}

}

return(data);

}

PC機上應用程序用Delphi7.0開發設計,利用專門的串口控件很容易開發出串口通信程序,從而將VME配置文件發送到MSP430。當配置完成以后由MSP430返回“配置成功”。

4 結論

我們設計的基于MSP430的CPLD動態配置方案,充分利用了CPLD可重復配置的特性,為嵌入式系統升級重構提供了一種新的思路,將來一定有很好的應用前景。當然在這個方案中,由于采用外加E2PROM的原因,在配置速度上較慢。雖然本方案針對的是Lattice MACH4000系列CPLD器件,但是稍加改動也可用于Lattice其它ispJTAG器件,如ispXPLD、

ispGDX2等。另外在實際應用中,如果能加上網絡模塊,還可以實現遠程的動態配置。

電子發燒友App

電子發燒友App

評論