摘要:用ALTERA公司MAX7000系列CPLD芯片實現單片機與PC104 ISA總線接口之間的并行通信,給出系統設計方法及程序源代碼。包括通信軟件和AHDL設計部分。

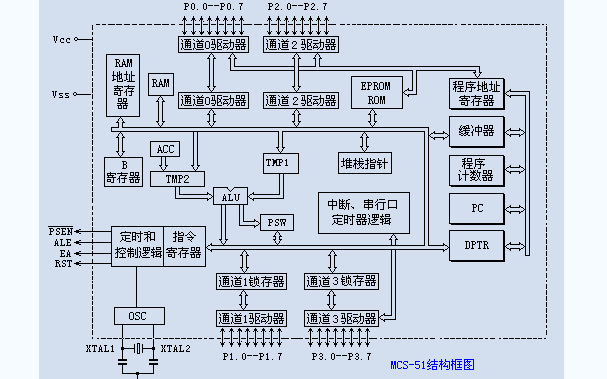

CPLD(Complex Programmable Logic Device)是一種復雜的用戶可編程邏輯器件,由于采用連續連接結構。這種結構易于預測延時,從而電路仿真更加準確。CPLD是標準的大規模集成電路產品,可用于各種數字邏輯系統的設計。近年來,由于采用先進的集成工藝和大批量生產,CPLD器件成本不斷下降,集成密度、速度和性能大幅度提高,一個芯片就可以實現一個復雜的數字電路系統;再加上使用方便的開發工具,使用CPLD器件可以極大地縮短產品開發周期,給設計、修改帶來很大方便[1]。本文以ALTERA公司的MAX7000系列為例,實現MCS51單片機與PC104 ISA總線的并行通信。采用這種通信方式,數據傳輸準確、高速,在12 MHz晶振的MCS51單片機控制的數據采集系統中,可以滿足與PC104 ISA總線接口實時通信的要求,通信速率達200 Kbps。

1 系統總體設計方案

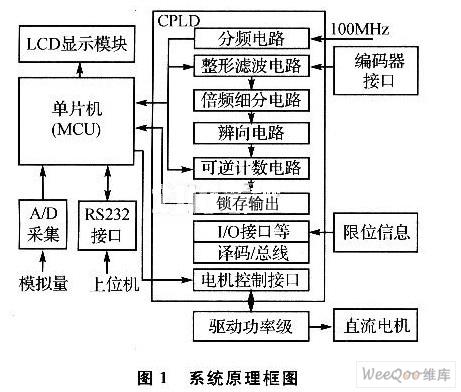

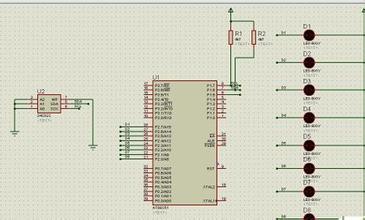

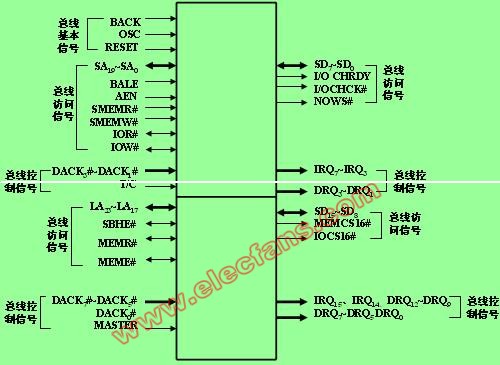

本系統用CLPD實現單片機與PC104 ISA總線接口的并行通信。由于PC104主要完成其它方面的數據采集工作,只是在空閑時才能接收單片機送來的數據,所以要求雙方通信的實時性很強,但數據量不是很大。因此,在系統設計中單片機中斷方式接收數據,PC104采用查詢方式接收數據。系統設計方案如圖1所示。

在圖1單片機部分,D[0..7]是數據總線,A[0..15]是地址總線,RD和WR分別是讀寫信號線,INT0是單片機的外部中斷。當單片機的外部中斷信號有效時,單片機接收數據。

在CPLD部分,由一片MAX7000系列中的EPM7128LSC84來實現,用來完成MCS51與PC104ISA總線接口之間的數據傳輸、狀態查詢及延時等待。

在PC104 ISA部分,只用到ISA的8位數據總線D[0..7],A[0..9]是PC104的地址總線;IOW和IOR是對指定設備的讀寫信號;AEN是允許DMA控制地址總線、數據總線及讀寫命令線進行DMA傳輸,及對存儲器和I/O設備的讀寫;IOCHRDY是I/O就緒信號,I/O通道就緒為高,此時處理機產生的存儲器讀寫周期為4個時鐘周期,產生的I/O讀寫周期和DMA字節傳輸均需5個時鐘周期,MCS51通過置此信號為低電平來使CPU插入等待周期,從而延長I/O周期;SYSCLK是系統時鐘信號,是為了與外部設備保持同步;RESETDR是上電復位或系統初始化邏輯,是系統總清信號。

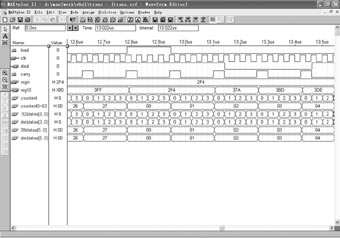

2 基于MAX+plus II的硬件實現

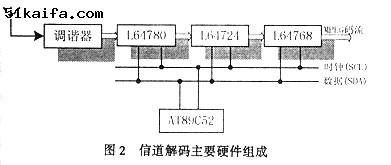

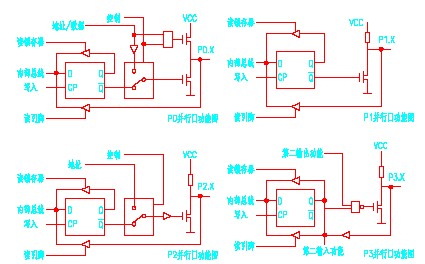

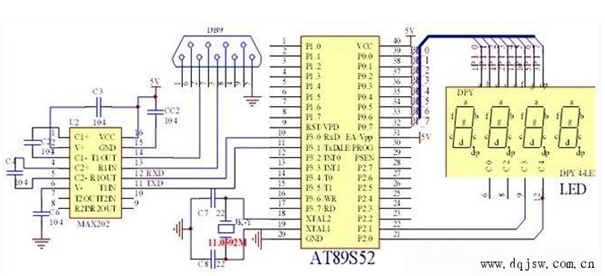

本系統是用ALTERA公司的CPLD開發工具MAX+plusII。它支持多種輸入方式,給設計開發提供了極大的方便。系統的主體部分仍是用原理圖輸入方式。由于庫中提供了現在的芯片,所以使用很方便。原理圖輸入部分如圖2和圖3所示。圖2主要完成單片機與ISA接口通信中的數據傳輸和握手判斷。

D[0..7] 單片機的8位雙向數據總線;

PCD[0..7] ISA接口的8位雙向數據總線;

PCRD ISA接口的讀有效信號;

PCWR ISA接口的寫有效信號;

判斷單片機已寫數據或讀走數據;

PCSTATE 單片機用此查詢ISA接口已取走數據;

MSCRD 單片機的讀有效信號;

MCSWR 單片機的寫有效信號;

INT0 單片機的外部中斷信號;

當MCUWR信號有效后,單片機把數據鎖存于74LS374(1)中,此時,PCSTATE變為高電平。PC104用STATE信號選通74LS244來判斷數據位PCD0是否為高電平,如果為高,說明單片機送來了數據,那么使PCRD有效,從數據存器74LS374(1)中取走數據。此時,PCSTATE變為低電平,單片機通過判斷此信號為低電平來判定PC104已取走了數據,可以發下一個數據。

當PCWR信號有效后,PC104把數據鎖存于74LS374(2)中,此時,INT0變為低電閏,單片機產生外部中斷,使MCSRD信號有效,從數據鎖存器74LS374(2)中取走裝飾,INT0變為高電平。PC104用STATE信號選通74LS244判斷數據位PCD1是否為高電平,如果為高電平,說明單片機取走了數據,可以發送下一個數據。 PC104與單片機進行通信,最關鍵的就是速度匹配問題。由于PC104的速度快,而單片機的速度較慢,所以,要在PC104的IOCHRDY處插入等待周期,如圖3所示。

IOCHRDY 用來使ISA接口等待5個時鐘周期;

DLY_D 延時輸入信號;

DLY_CK 延時等待時鐘信號;

DLY_CLR 等待清除信號,為開始下一次送數周期作準備;

DELAY 延時5個時鐘周期后的輸出信號,作為DLY_CLR信號的輸入;

SYSCLK ISA接口的系統時鐘信號。

在MCS51與PC104進行通信的過程中,DLY_D信號一直有效(高電平)。在信號SYSCLK的作用下,每5個時鐘周期DELAY信號有效一次,即為高電平。此時DLY_CLR信號有效(低電平),IOCHRDY信號變為高電平,PC104可以讀寫數據。

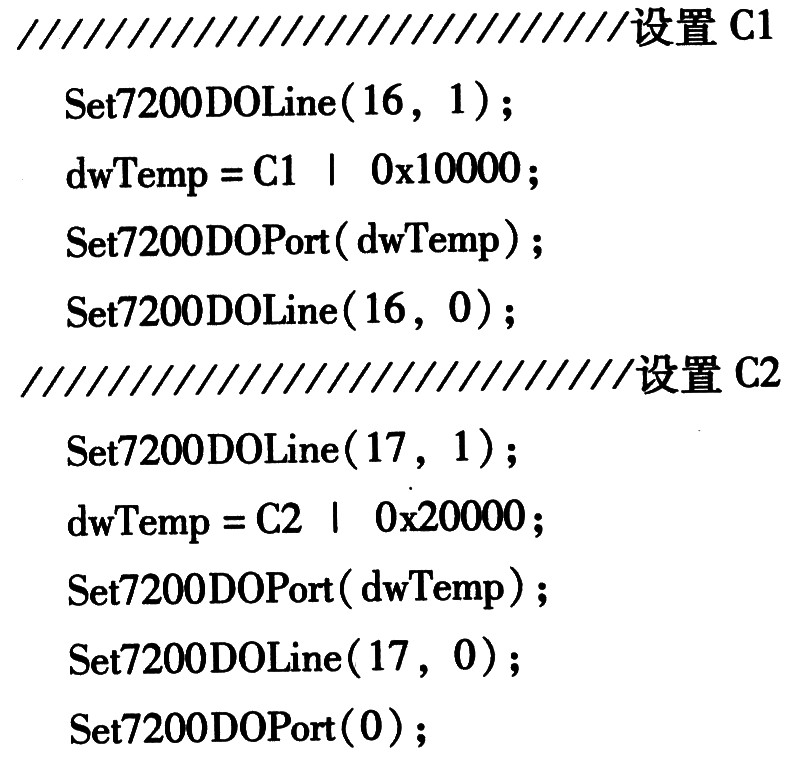

地址譯碼部分采用文本輸入方式,用ALTERA公司的硬件設計開發語言AHDL(Altera Hardware Description Language)。AHDL是一種模塊化的高級語言,完全集成于MAX+plusII系統中,特別適合于描述復雜的組合邏輯、狀態機和真值表,地址譯碼部分用文本輸入方式,這充分體現了文本輸入方式的優點。文本輸入內容如下:

(

PCA[9..0] : INPUT;

AEN,IOR,IOW : INPUT;

RESETDR,DELAY : INPUT;

A[15..14] :INPUT;

RD,WR : INPUT;

DLY_D : OUTPUT;

DLY_CK : OUTPUT;

DLY_CLR : OUTPUT;

STATE : OUTPUT;

PCRD : OUTPUT;

PCWR : OUTPUT;

MCURD : OUTPUT;

MCUWR : OUTPUT;

)

BEGIN

!DLY_CLR=RESETDR#DELAY;

DLY_D=!AEN & (PCA[9..1]= =H"110");

DLY_CK=!AEN & (PCA[9..1]= =H"110")&(!IOR # ! IOW);

!PCWR=!AEN&(PCA[9..0]= =H"220")& !IOW;

!PCRD=!AEN&(PCA[9..0]= =H"220")& !IOR;

!STATE=!AEN&(PCA[9..0]= =H"221")&!IOR;

!MCSRD=([15..14]= =H"1")& !RD;

!MCSWR=(A[15..14]= =H"2"& !WR;

END;

說明:PCA[9..0]是PC104的地址信號,A[15..14]是單片機的地址信號,PC104用到端口地址220H和221H。

3 通信軟件設計

PC104是基于ISA總線的,在系統軟件設計中要防止地址沖突。PC104中使用A0~A9地址位來表示I/O端口地址,即可有1024個口地址:前512個供系統板使用,后512個供擴充槽使用。當A9=0時表示為系統板上的口地址;A9=1時,表示擴充插槽接口卡上的口地址[2]。因此,采用保留的口地址220H和221H,保證不會發生地址沖突。

本程序中PC104采用查詢方式接收數據,單片機用中斷方式接收數據。

#define pcreadwrite 0x220 /*PC104讀寫數據口地址*/

#define pcrdstate 0x221 /*PC104查詢狀態口地址*/

PC104寫數據函數:

Void pcwrite(int port,unsigned char ch)

{ outportb(pcreadwrite,ch);

while ((inportb(pcrdstate)&0x02)!=0x02); /*等待單片機讀走數據*/

{ }

}

單片機讀子程序:

MCUWR:MOV DPTR,#4000H

MOVX A,@DPTR

RETI

PC104讀數據函數:

Unsigned char pcread(int port)

{ while((inportb(pcrdstate)&0x01)!=0x01);/*等待單片機寫數據*/

{}

return inportb(pcreadwrite);

}

單片機寫子程序:

MCUWR:MOV DPTR,#8000H

MOVX @DPTR,A

;等待PC104讀走數據

RET

4 結論

用CPLD實現單片機與ISA總線接口的并行通信,電路結構簡單、體積小,1片CPLD芯片足夠,并且控制方便,實時性強,通信效率高。本設計方法已成功地應用于作者開發的各種數據采集系統中,用作單片機與PC104之間的并行數據通信,效果非常理想。

- 并行通信(11154)

- 用CPL(6357)

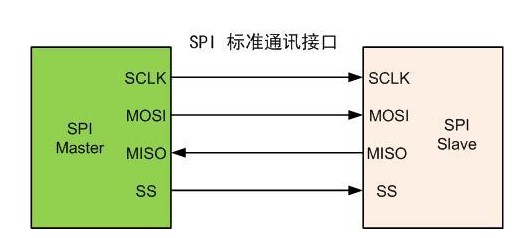

單片機spi通信原理詳解

4992

4992

CPLD加51單片機讓系統更高效

單片機通信的相關資料分享

單片機通信的相關資料推薦

單片機P口接PCI/ISA數據總線

單片機的總線

并行通信和串行通信的相關資料分享

用VC實現PC機與單片機的通信

FPGA/CPLD與單片機相比有哪些優勢?

LONWORKS控制模塊與MCS-51單片機的并行通信

基于CPLD的單片機與ISA總線接口并行通信

基于MCS51系列單片機法人雙機并行互連實現

如何實現單片機與CPLD通訊呢?

如何利用CPLD實現單片機PCI接口設計

如何利用CPLD幫助單片機完成與PCI設備間的通信任務

用單片機實現溫度遠程顯示

53

53單片機多機并行通訊的一種方法

119

119PC機與單片機的并行通信協議

77

77利用單片機實現CPLD的在系統編程

22

22基于CPLD的單片機PCI接口設計

34

34用CPLD 實現單片機與ISA 總線并行通信

29

29循環冗余校驗碼的單片機及CPLD 實現

16

16用87C196NT單片機實現CAN總線通信

34

34用CPLD 實現單片機與ISA 總線并行通信

16

16單片機+CPLD結構體系在電子設計中的應用

17

17單片機應用系統的CPLD 應用設計

39

39用VC實現PC機與單片機的通信

58

58用組態王實現PC機與多臺單片機的遠程通信

61

61單片機與FPGA CPLD總線接口邏輯設計

83

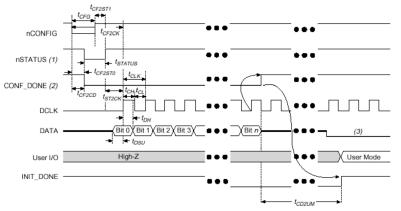

83基于單片機的CPLD/FPGA被動串行下載配置的實現

19

19采用ATMEGA128單片機結合CPLD 實現了對VGA顯示

107

107基于單片機和CPLD的頻率測量研究

42

42單片機應用系統的CPLD應用設計

39

39MCS51系列單片機雙機并行互連的實現方法

49

49用51單片機控制RTL8029實現以太網通信

58

58基于單片機+CPLD的多路精確延時控制系統設計

43

43基于ISA總線的計算機與DSP的通信

37

37CPLD與51單片機總線接口程序

1142

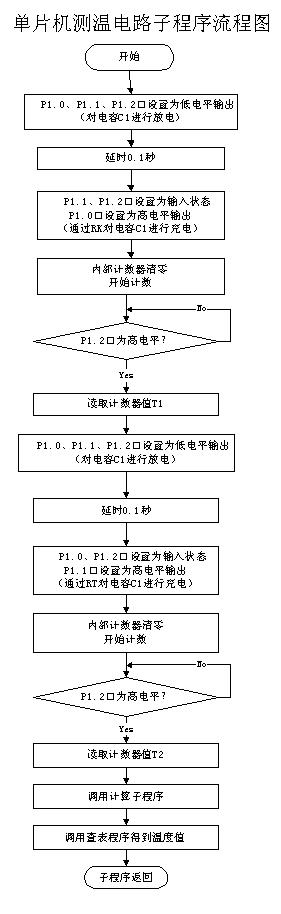

1142用單片機實現的測溫電路

1744

1744

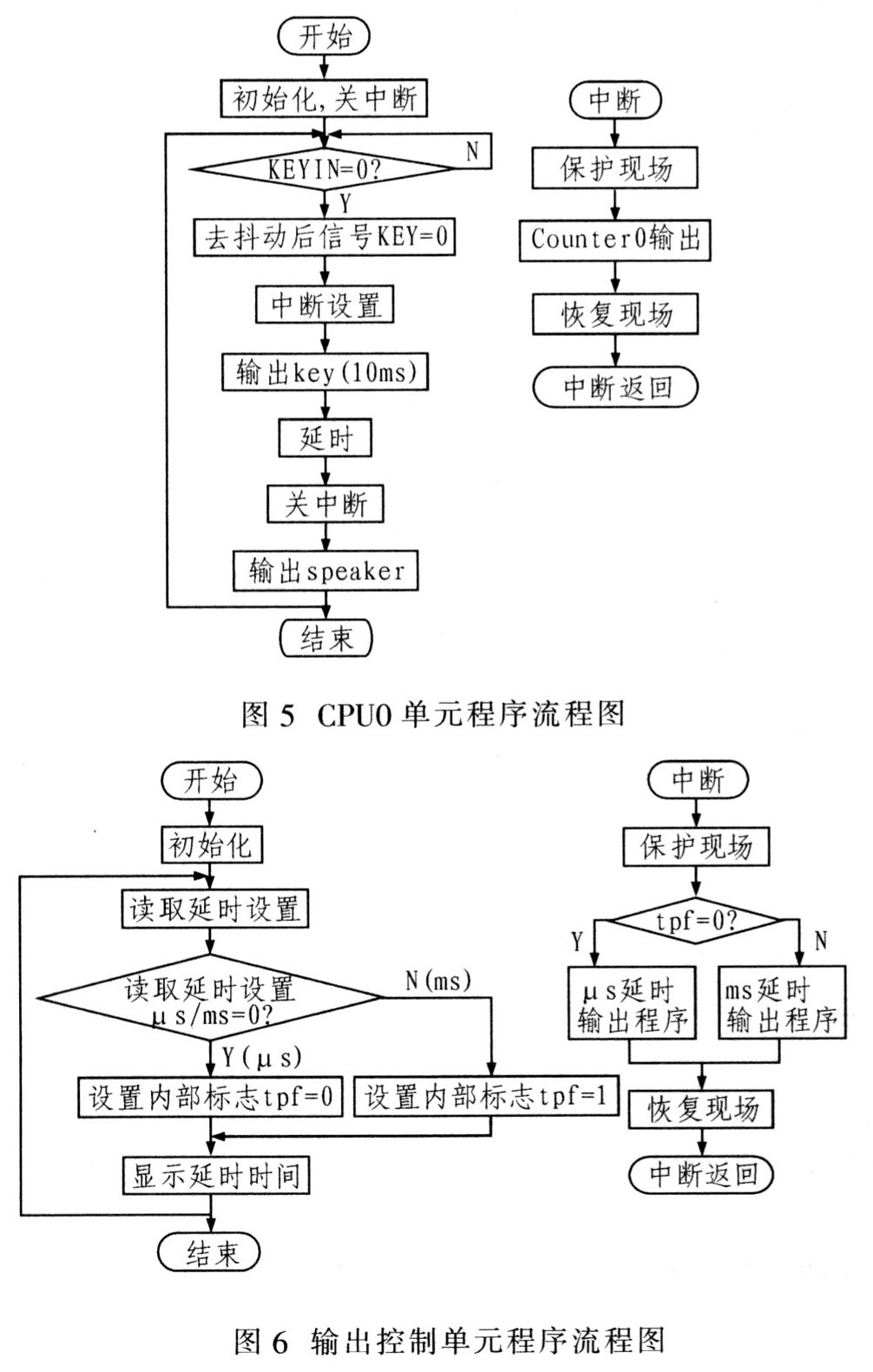

單片機+CPLD的多路精確延時控制系統

2256

2256

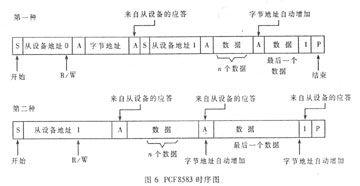

基于DSP與CPLD的I2C總線接口的設計與實現

1487

1487

用單片機配置CPLD器件

1423

1423

單片機脈沖信號源的CPLD實現方案

1924

1924

用VHDL語言在CPLD上實現串行通信

963

963

基于CPLD的單片機PCI接口設計

1166

1166

用CPLD實現單片機與ISA總線并行通信

1360

1360

基于CPLD的單片機與PCI接口設計解決方案

1044

1044

I2C總線的單片機C語言實現及其應用

3293

3293

單片機并行口,單片機并行口結構原理是什么?

3813

3813

用MODBUS實現觸摸屏與單片機的通信

331

331CAN總線+單片機實現通信網絡設計

7351

7351

基于單片機的多機并行通信設計

2485

2485

單片機串行口的并行通信技術

103

103用單片機實現溫度遠程顯示資料

13

13基于單片機與FPGA的總線接口邏輯設計

4439

4439什么是單片機的串口通信?

62202

62202

用Win32API實現PC機與多單片機的串行通信

1

1采用軟件模擬SPI總線實現雙單片機數據通信模塊的設計

3623

3623

基于單片機和CPLD的高精度大型望遠鏡伺服控制器設計

4935

4935

如何使用單片機的IO口模擬串行實現數據通信的資料概述

12

12如何用51單片機實現IIC通信

17060

17060

如何實現PC機與51系列單片機的通信

6733

6733

AVR單片機與CPLD的通信設計

1477

1477如何實現計算機與單片機之間的通信

8952

8952

如何實現PC機與單片機實現通信

49

49單片機實現多機通信的資料和程序

8509

8509單片機的結構和原理說明

6295

6295

51單片機實現的雙機通信設計仿真

17

17制定通信協議,實現單片機與PC機通信

22

22用單片機串口和modbus poll 進行通信

23

23單片機中并行是什么意思

2237

2237 電子發燒友App

電子發燒友App

評論