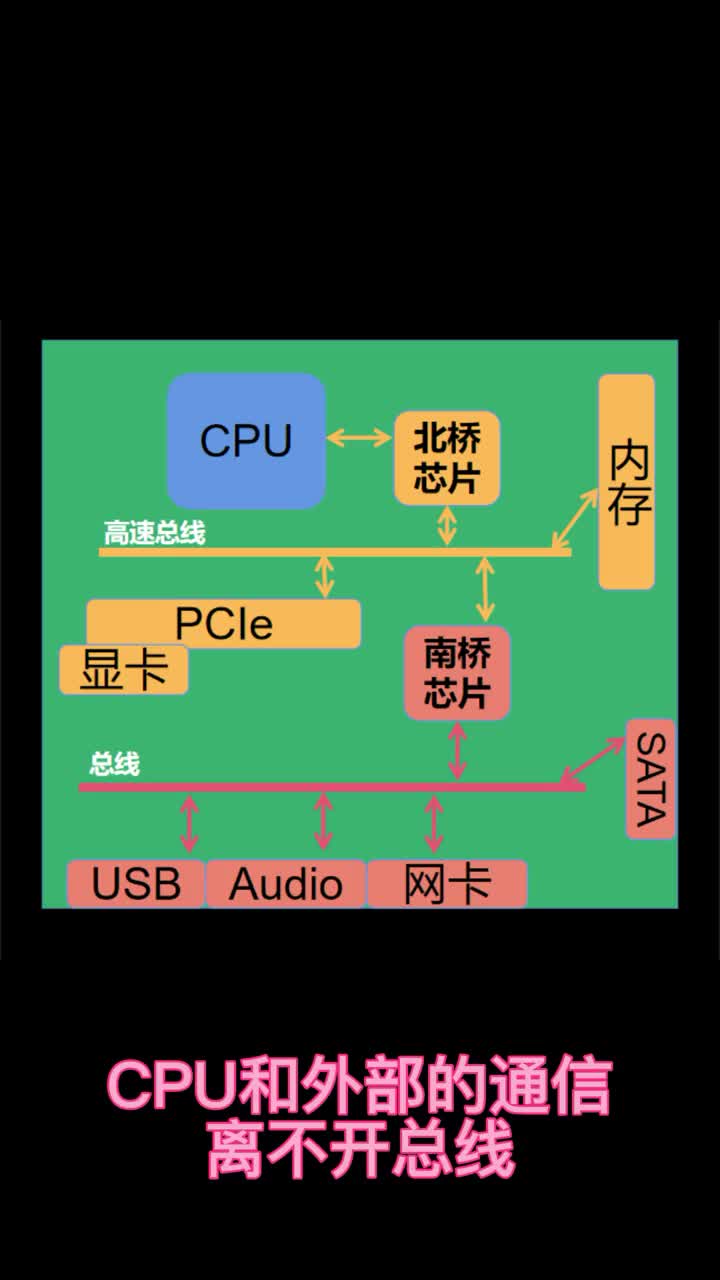

作為一名PCB設(shè)計(jì)工程師,具備一些高速方面的知識(shí)是非常有必要的,甚至說(shuō)是必須的。就信號(hào)來(lái)說(shuō),高速信號(hào)通常見(jiàn)于各種并行總線(xiàn)與串行總線(xiàn),只有知道了什么是總線(xiàn),才能知道它跑多快,才能開(kāi)始進(jìn)行布線(xiàn)。

總線(xiàn)

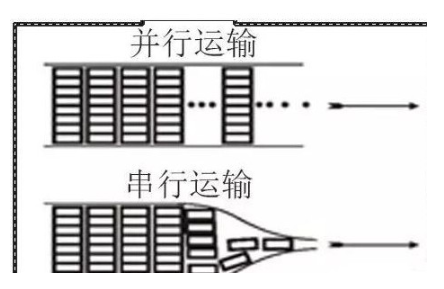

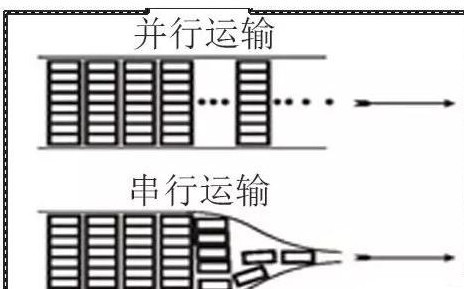

總線(xiàn)是兩個(gè)或兩個(gè)以上設(shè)備通訊的共享物理通路,是信號(hào)線(xiàn)的集合,是多個(gè)部件間的公共連線(xiàn),用于在各個(gè)部件間傳輸信息。按照工作模式不同,總線(xiàn)可以分為兩種類(lèi)型:一種是并行總線(xiàn),一種是串行總線(xiàn)。

并行總線(xiàn)

同一時(shí)刻可以傳輸多位數(shù)據(jù),好比是一條允許多輛車(chē)并排開(kāi)的寬敞道路,而且它還有雙向單向之分。

串行總線(xiàn)

在同一時(shí)刻只能傳輸一個(gè)數(shù)據(jù),好比只容許一輛車(chē)行走的狹窄道路,數(shù)據(jù)必須一個(gè)接一個(gè)傳輸、看起來(lái)仿佛一個(gè)長(zhǎng)長(zhǎng)的數(shù)據(jù)串,故稱(chēng)為“串行”。

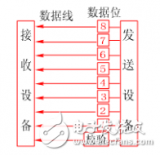

并行傳輸最好的例子就是存儲(chǔ)芯片DDR,它是有一組數(shù)據(jù)線(xiàn)D0—D7,加DQS,DQM,這一組線(xiàn)是一起傳輸?shù)模瑹o(wú)論哪位產(chǎn)生錯(cuò)誤,數(shù)據(jù)都不會(huì)正確的傳送過(guò)去,只有重新傳輸。所以數(shù)據(jù)線(xiàn)每根線(xiàn)要等長(zhǎng),必須得繞幾下才行。 串行數(shù)據(jù)就不一樣,數(shù)據(jù)是一位一位的傳,位與位之間是沒(méi)有聯(lián)系的。不會(huì)因?yàn)檫@位有錯(cuò)誤,使下一位不能傳輸。并行數(shù)據(jù)是一組數(shù)據(jù)其中一位不對(duì),整組數(shù)據(jù)都不行。

布線(xiàn)要求

并行總線(xiàn)的布線(xiàn)要求

(1)建議總線(xiàn)優(yōu)選內(nèi)層布線(xiàn),盡量增大與其它布線(xiàn)的間距。

(2)除特殊要求外,單線(xiàn)設(shè)計(jì)阻抗保證50歐,差分設(shè)計(jì)阻抗保證100歐。

(3)建議同一組總線(xiàn)保持布線(xiàn)基本等長(zhǎng),與時(shí)鐘線(xiàn)遵循一定的時(shí)序關(guān)系,參照時(shí)序分析強(qiáng)果控制布線(xiàn)長(zhǎng)度。

(4)建議盡可能的靠近本組總線(xiàn)的I/O電源或GND參考平面,保證參考平面的完整性。

(5)上升時(shí)間小于1ns的總線(xiàn),要求有完整參考平面,不得跨分割。

(6)建議低位地址總線(xiàn)參照時(shí)鐘布線(xiàn)要求。

(7)蛇形繞線(xiàn)線(xiàn)的間距不得小于3倍線(xiàn)寬。

高速串行總線(xiàn)的布線(xiàn)要求

頻率高于100Mbps的串行總線(xiàn),在布線(xiàn)設(shè)計(jì)中除遵循并行總線(xiàn)通用的串?dāng)_控制、布線(xiàn)規(guī)則之外,還需額外考慮一些要求:

(1)高速串行總線(xiàn)需要考慮布線(xiàn)的損耗,確定線(xiàn)寬線(xiàn)長(zhǎng)。

(2)建議一般情況下線(xiàn)寬不小于5mil,布線(xiàn)盡量短。

(3)高速串行總線(xiàn)除Fanout過(guò)孔外,盡量不要打孔換層。

(4)串行總線(xiàn)所涉及的插件管腳,速率達(dá)3.125Gbps以上時(shí),應(yīng)優(yōu)化反焊盤(pán)以減少阻抗不連續(xù)帶來(lái)的影響。

(5)建議高速串行總線(xiàn)布線(xiàn)換層時(shí),選擇使用過(guò)孔Stub最小的布線(xiàn)層,對(duì)于到連接器的信號(hào),在布線(xiàn)空間有限時(shí),過(guò)孔Stub短的布線(xiàn)層,優(yōu)先分配給發(fā)送端。

(6)建議速率達(dá)3.125Gbps或以上時(shí),信號(hào)過(guò)孔旁打地孔,AC藕合電容也要對(duì)反焊盤(pán)特殊處理。

(7)如果高速信號(hào)過(guò)孔采用背鉆處理,需要考慮電源地平面通流能力變小,以及通流瓶頸變窄后的濾波環(huán)路電感增大帶來(lái)的影響。

(8)高速信號(hào)避開(kāi)平面層的分割線(xiàn),信號(hào)線(xiàn)邊緣與分割線(xiàn)邊緣空間水平間距保證3W。

(9)收發(fā)兩個(gè)方向的高速信號(hào),不能交叉在一起走線(xiàn)。 本文轉(zhuǎn)載自:掌工知 聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有,如涉及侵權(quán),請(qǐng)后臺(tái)聯(lián)系小編進(jìn)行處理。

責(zé)任編輯人:CC

-

并行總線(xiàn)

+關(guān)注

關(guān)注

0文章

30瀏覽量

13878 -

高速串行總線(xiàn)

+關(guān)注

關(guān)注

0文章

4瀏覽量

3602

原文標(biāo)題:PCB設(shè)計(jì)必備知識(shí):并行總線(xiàn)VS串行總線(xiàn)

文章出處:【微信號(hào):gh_454737165c13,微信公眾號(hào):Torex產(chǎn)品資訊】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

高速PCB并行總線(xiàn)和串行總線(xiàn)

串行總線(xiàn)會(huì)替代并行總線(xiàn)嗎?#高速接口

干貨總結(jié)|手把手教你讀懂CAN總線(xiàn)#汽車(chē)CAN總線(xiàn)? #總線(xiàn)傳輸 #高速串行總線(xiàn) #總線(xiàn)解碼

什么是基于FPGA的ARM并行總線(xiàn)?

了解了串行/并行高速信號(hào),你才能開(kāi)始PCB布線(xiàn)

高速串行總線(xiàn)與并行總線(xiàn)的差別是什么?

串行總線(xiàn)和并行總線(xiàn)的區(qū)別

并行總線(xiàn)有哪些?串行總線(xiàn)有哪些?

基于FPGA的ARM并行總線(xiàn)和端口設(shè)計(jì)

PCB設(shè)計(jì)必備知識(shí):并行總線(xiàn)VS串行總線(xiàn)

什么是串行總線(xiàn)和并行總線(xiàn)?

串行總線(xiàn)的優(yōu)缺點(diǎn)優(yōu)點(diǎn)

并行總線(xiàn)和串行總線(xiàn)的區(qū)別

高速串行總線(xiàn)有哪些

高速并行總線(xiàn)的工作原理是什么 高速并行總線(xiàn)有哪些

并行總線(xiàn)和高速串行總線(xiàn)的布線(xiàn)要求

并行總線(xiàn)和高速串行總線(xiàn)的布線(xiàn)要求

評(píng)論