?

PCLe總線的層次結構

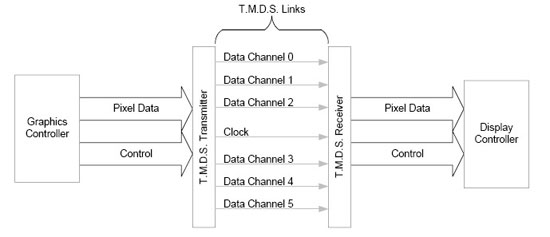

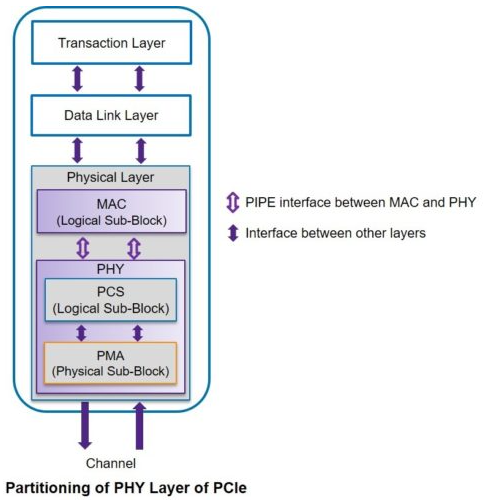

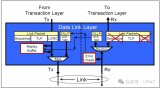

PCIe總線采用了串行連接方式,并使用數據包(Packet)進行數據傳輸,采用這種結構有效去除了在PCI總線中存在的一些邊帶信號,如INTx和PME#等信號。在PCIe總線中,數據報文在接收和發送過程中,需要通過多個層次,包括事務層、數據鏈路層和物理層。PCIe總線的層次結構如圖44所示。

PCIe總線的層次組成結構與網絡中的層次結構有類似之處,但是PCIe總線的各個層次都是使用硬件邏輯實現的。在PCIe體系結構中,數據報文首先在設備的核心層(Device Core)中產生,然后再經過該設備的事務層(Transaction Layer)、數據鏈路層(Data Link Layer)和物理層(Physical Layer),最終發送出去。而接收端的數據也需要通過物理層、數據鏈路和事務層,并最終到達Device Core。

1 事務層

事務層定義了PCIe總線使用總線事務,其中多數總線事務與PCI總線兼容。這些總線事務可以通過Switch等設備傳送到其他PCIe設備或者RC。RC也可以使用這些總線事務訪問PCIe設備。

事務層接收來自PCIe設備核心層的數據,并將其封裝為TLP(Transaction Layer Packet)后,發向數據鏈路層。此外事務層還可以從數據鏈路層中接收數據報文,然后轉發至PCIe設備的核心層。

事務層的一個重要工作是處理PCIe總線的“序”。在PCIe總線中,“序”的概念非常重要,也較難理解。在PCIe總線中,事務層傳遞報文時可以亂序,這為PCIe設備的設計制造了不小的麻煩。事務層還使用流量控制機制保證PCIe鏈路的使用效率。有關事務層的詳細說明見第6章。

2 數據鏈路層

數據鏈路層保證來自發送端事務層的報文可以可靠、完整地發送到接收端的數據鏈路層。來自事務層的報文在通過數據鏈路層時,將被添加Sequence Number前綴和CRC后綴。數據鏈路層使用ACK/NAK協議保證報文的可靠傳遞。

PCIe總線的數據鏈路層還定義了多種DLLP(Data Link Layer Packet),DLLP產生于數據鏈路層,終止于數據鏈路層。值得注意的是,TLP與DLLP并不相同,DLLP并不是由TLP加上Sequence Number前綴和CRC后綴組成的。

3 物理層

物理層是PCIe總線的最底層,將PCIe設備連接在一起。PCIe總線的物理電氣特性決定了PCIe鏈路只能使用端到端的連接方式。PCIe總線的物理層為PCIe設備間的數據通信提供傳送介質,為數據傳送提供可靠的物理環境。

物理層是PCIe體系結構最重要,也是最難以實現的組成部分。PCIe總線的物理層定義了LTSSM(Link Training and Status State Machine)狀態機,PCIe鏈路使用該狀態機管理鏈路狀態,并進行鏈路訓練、鏈路恢復和電源管理。

PCIe總線的物理層還定義了一些專門的“序列”,有的書籍將物理層這些“序列”稱為PLP(Phsical Layer Packer),這些序列用于同步PCIe鏈路,并進行鏈路管理。值得注意的是PCIe設備發送PLP與發送TLP的過程有所不同。對于系統軟件而言,物理層幾乎不可見,但是系統程序員仍有必要較為深入地理解物理層的工作原理。

數據鏈路的擴展

PCIe鏈路使用端到端的數據傳送方式。在一條PCIe鏈路中,這兩個端口是完全對等的,分別連接發送與接收設備,而且一個PCIe鏈路的一端只能連接一個發送設備或者接收設備。因此PCIe鏈路必須使用Switch擴展PCIe鏈路后,才能連接多個設備。使用Switch進行鏈路擴展的實例如圖45所示。

在PCIe總線中,Switch[2]是一個特殊的設備,該設備由1個上游端口和2~n個下游端口組成。PCIe總線規定,在一個Switch中可以與RC直接或者間接相連[3]的端口為上游端口,在PCIe總線中,RC的位置一般在上方,這也是上游端口這個稱呼的由來。在Switch中除了上游端口外,其他所有端口都被稱為下游端口。下游端口一般與EP相連,或者連接下一級Switch繼續擴展PCIe鏈路。其中與上游端口相連的PCIe鏈路被稱為上游鏈路,與下游端口相連的PCIe鏈路被稱為下游鏈路。

上游鏈路和下游鏈路是一個相對的概念。如上圖所示,Switch與EP2連接的PCIe鏈路,對于EP2而言是上游鏈路,而對Switch而言是下游鏈路。

在上圖所示的Switch中含有3個端口,其中一個是上游端口(Upstream Port),而其他兩個為下游端口(Downstream Port)。其中上游端口與RC或者其他Switch的下游端口相連,而下游端口與EP或者其他Switch的上游端口相連。

在Switch中,還有兩個與端口相關的概念,分別是Egress端口和Ingress端口。這兩個端口與通過Switch的數據流向有關。其中Egress端口指發送端口,即數據離開Switch使用的端口;Ingress端口指接收端口即數據進入Switch使用的端口。

Egress端口和Ingress端口與上下游端口沒有對應關系。在Switch中,上下游端口可以作為Egress端口,也可以作為Ingress端口。如圖45所示,RC對EP3的內部寄存器進行寫操作時,Switch的上游端口為Ingress端口,而下游端口為Egress端口;當EP3對主存儲器進行DMA寫操作時,該Switch的上游端口為Egress端口,而下游端口為Ingress端口。

PCIe總線還規定了一種特殊的Switch連接方式,即Crosslink連接模式。支持這種模式的Switch,其上游端口可以與其他Switch的上游端口連接,其下游端口可以與其他Switch的下游端口連接。

PCIe總線提供CrossLink連接模式的主要目的是為了解決不同處理器系統之間的互連,如圖46所示。使用CrossLink連接模式時,雖然從物理結構上看,一個Switch的上/下游端口與另一個Switch的上/下游端口直接相連,但是這個PCIe鏈路經過訓練后,仍然是一個端口作為上游端口,而另一個作為下游端口。

處理器系統1與處理器系統2間的數據交換可以通過Crosslink進行。當處理器系統1(2)訪問的PCI總線域的地址空間或者Requester ID不在處理器系統1(2)內時,這些數據將被Crosslink端口接收,并傳遞到對端處理器系統中。Crosslink對端接口的P2P橋將接收來自另一個處理器域的數據請求,并將其轉換為本處理器域的數據請求。

使用Crosslink方式連接兩個拓撲結構完全相同的處理器系統時,仍然有不足之處。假設圖46中的處理器系統1和2的RC使用的ID號都為0,而主存儲器都是從0x0000-0000開始編址時。當處理器1讀取EP2的某段PCI總線空間時,EP2將使用ID路由方式,將完成報文傳送給ID號為0的PCI設備,此時是處理器2的RC而不是處理器1的RC收到EP2的數據。因為處理器1和2的RC使用的ID號都為0,EP2不能區分這兩個RC。

由上所述,使用Crosslink方式并不能完全解決兩個處理器系統的互連問題,因此在有些Switch中支持非透明橋結構。這種結構與PCI總線非透明橋的實現機制類似,本章對此不做進一步說明。

使用非透明橋僅解決了兩個處理器間數據通路問題,但是不便于NUMA結構對外部設備的統一管理。PCIe總線對此問題的最終解決方法是使用MR-IOV技術,該技術要求Switch具有多個上游端口分別與不同的RC互連。目前PLX公司已經可以提供具有多個上游端口的Switch,但是尚未實現MR-IOV技術涉及的一些與虛擬化相關的技術。

即便MR-IOV技術可以合理解決多個處理器間的數據訪問和對PCIe設備的配置管理,使用PCIe總線進行兩個或者多個處理器系統間的數據傳遞仍然是一個不小問題。因為PCIe總線的傳送延時仍然是制約其在大規模處理器系統互連中應用的重要因素。

電子發燒友App

電子發燒友App

評論