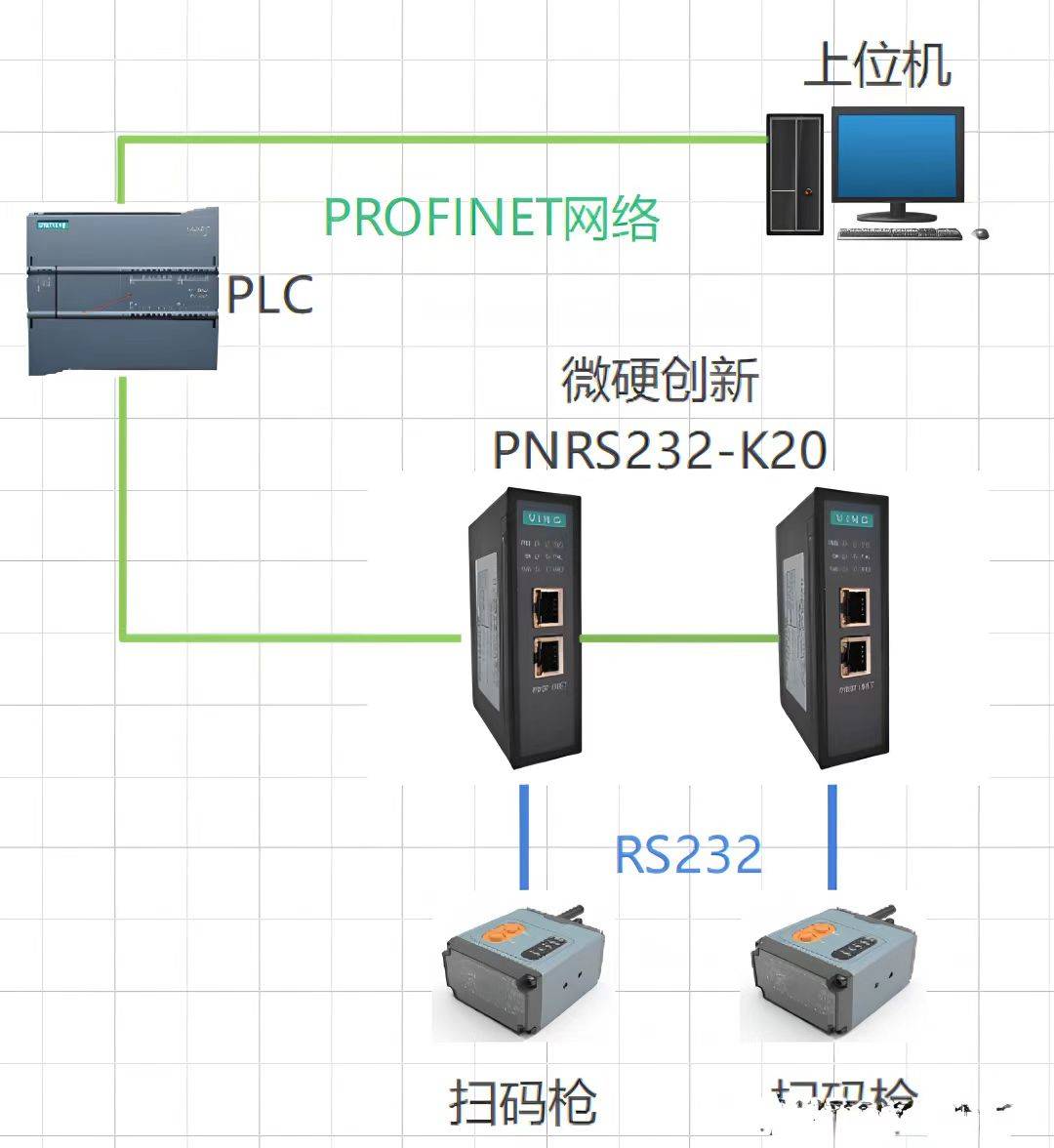

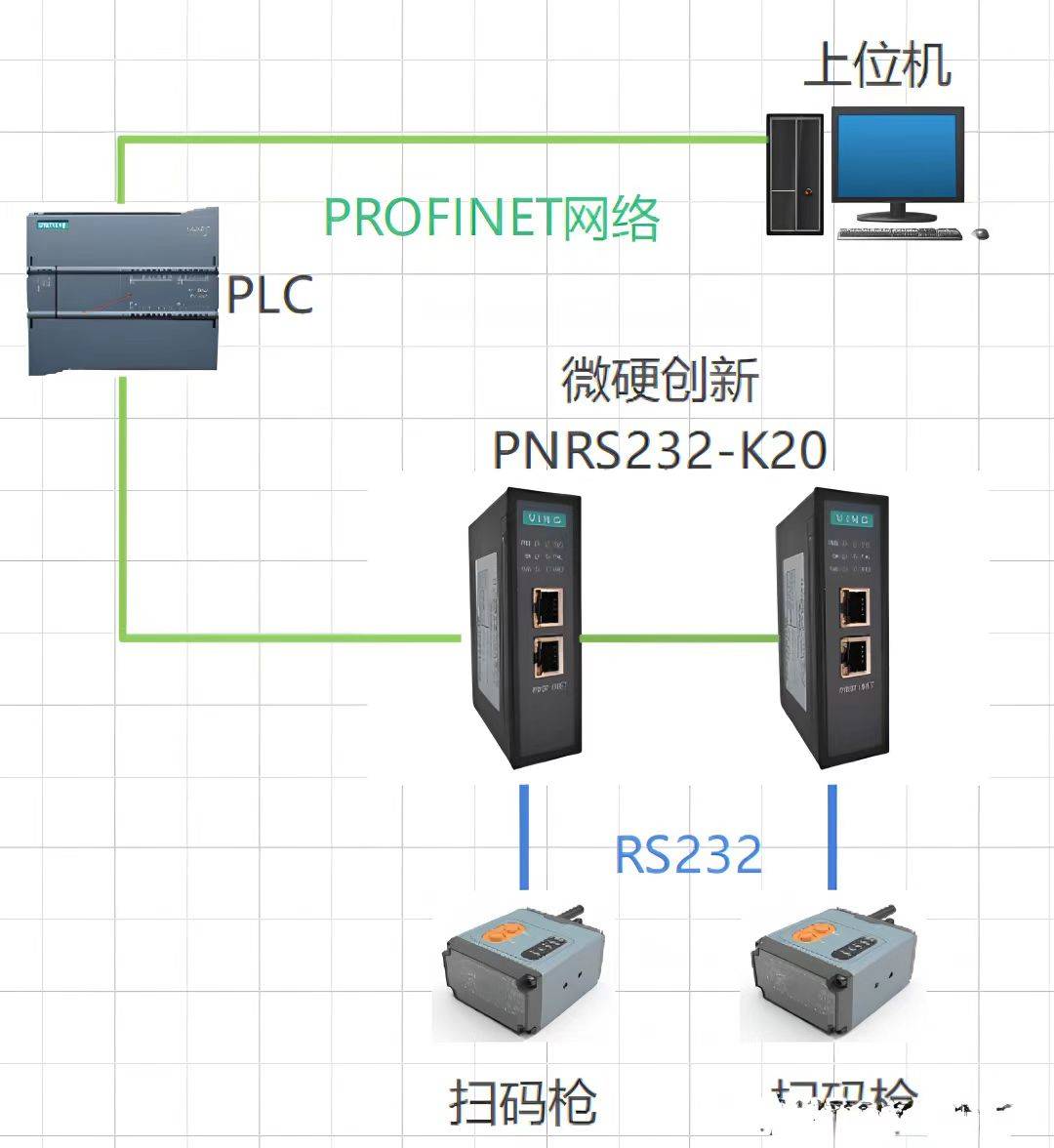

由于PROFINET網絡協議逐漸在各種行業中得到廣泛應用,同時條碼技術的成熟和廣泛應用,將掃碼掃上來的數據要傳送在PROFINET網絡,這種需求越來越多的情況下,不同協議之間可以實現協議轉換

2022-09-23 18:41:18 5622

5622

遠創智控的YC-EIP-RS485/232通訊網關,自主研發的ETHERNET/IP從站功能,完美解決了這個難題。這款網關不僅可以將ETHERNET/IP網絡和RS485/RS232總線連接起來

2023-07-22 09:20:52 3366

3366

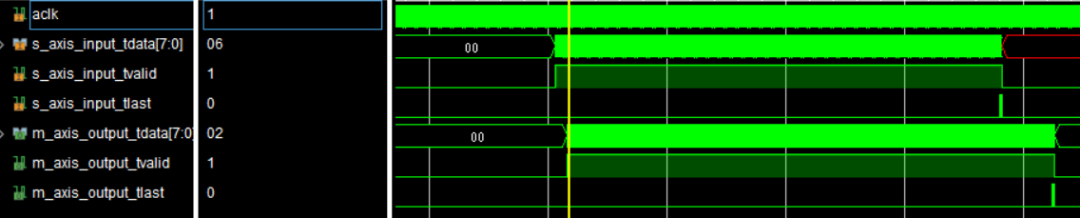

Xilinx的FIR IP核屬于收費IP,但是不需要像 Quartus那樣通過修改license文件來破解。如果是個人學習,現在網絡上流傳的license破解文件在破解Vivado的同時也破解

2025-03-01 14:44:19 2709

2709

本文介紹如何利用FPGA和DMA技術處理來自AD9280和AD9708 ADC的數據。首先,探討了這兩種ADC的特點及其與FPGA的接口兼容性。接著,詳細說明了使用Xilinx VIVADO環境下

2025-07-29 14:12:22 4847

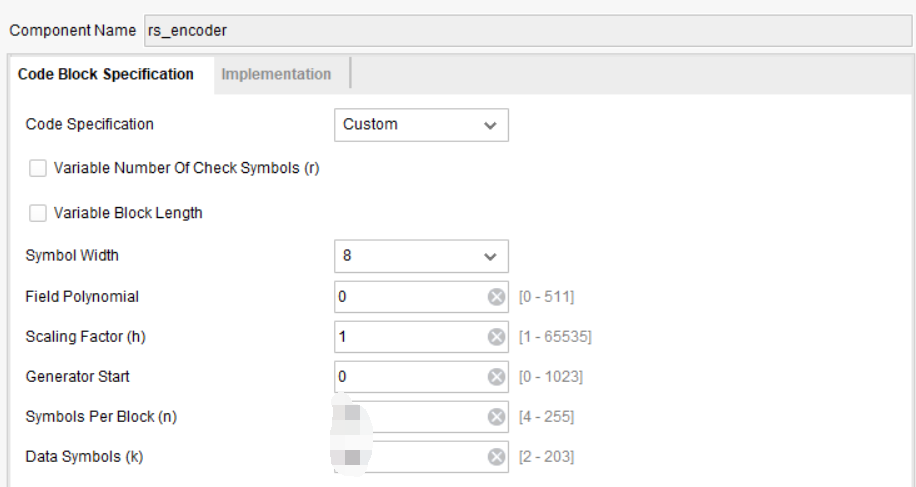

4847 本人使用RS IP核進行編碼時出現IP核后面帶有美元符號,不能正常使用。求大神給予破解幫助。

2019-08-20 11:34:00

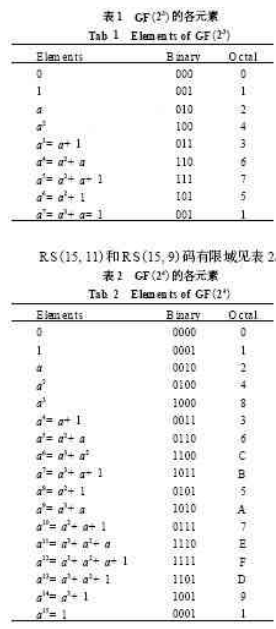

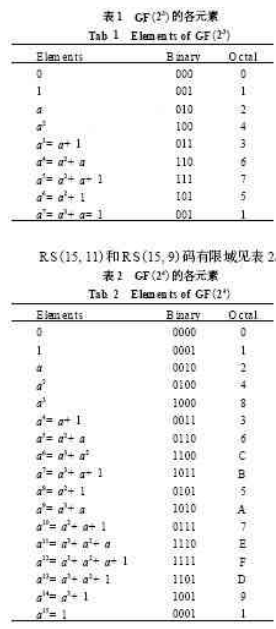

本文以戰術軍用通信系統的首選碼RS(31,15)碼為例,對生成多項式進行了優化,并采用查表法的原理極大地提高了編碼器運算數據的能力,縮短了運算周期,最終利用VHDL語言編譯,在FPGA中實現,得到了正確的RS編譯碼。

2021-05-06 09:27:33

論壇里面的大神們,有沒有已經完成LDPC碼編譯碼算法的FPGA實現,本人目前在做這方面的項目,時間比較緊,緊急求購IP核。。

2012-04-16 23:43:28

本帖最后由 allan***c 于 2018-3-16 10:48 編輯

Labview基于VISA實現RS232、RS485 Modbus的通訊,剛在網上查了寫資料,做了這么個程序,親

2018-03-14 10:28:45

【摘要】:Viterbi譯碼器在通信系統中應用非常普遍,針對采用DSP只能進行相對較低速率的Vit-erbi譯碼的問題,人們開始采用FPGA實現高速率Viterbi譯碼。本文首先簡單描述了

2010-04-26 16:08:39

技術可以使誤碼率進一步的降低。RS碼屬于分組碼,是BCH碼的一個子類,是最大距離可分碼,它是由Reed和Solomon于1960年構造出來。由于它具有很強的糾正隨機錯誤和突發錯誤的能力,以及極低的不可探測的差錯率,所以RS碼已經廣泛應用于深空通信、衛星通信、存儲介質、數字視頻廣播和擴頻數字通信中。

2019-09-26 07:11:07

如標題所示,我們分享如何在Vivado上仿真蜂鳥SOC,仿真NucleiStudio編譯好的程序

具體步驟

1. 將蜂鳥soc移植到Vivado

只要將端口映射好,注意配置好時鐘和bank

2025-10-21 11:08:55

RS485線在F103環境下進行UART通信實驗和RS232通信實驗在F407環境下進行RS485實驗(1.我的103板子沒有485口,2.正好看下開發板環境不同的差異)UART通信實驗(通用異步收發器)UART串口通信原理:什么是串行通信?什么是異步通信?什么是全雙工?什么是串行.

2022-02-17 07:17:45

如何利用VHDL實現線性分組碼編譯碼器的設計?

2021-04-28 06:41:40

本文研究了RS碼的實現方法,并基于Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS編譯碼器的設計,同時對其進行了仿真和在線調試,并給出了功能仿真圖和測試結果。時序仿真結果表明,該編譯碼器能實現預期功能。

2021-06-21 06:23:53

RS糾錯編碼是目前最有效、應用最廣泛的差錯控制編碼之一,是一種糾錯能力很強的多進制BCH碼,也是一類典型的代數幾何碼。它是由里德(Reed)和索洛蒙(Solomon)應用MS多項式于1960年首先構造出來的。

2019-08-20 08:16:26

截短Reed-Solomon碼譯碼器的FPGA實現提出了一種改進的BM算法,并在此基礎上提出了一種大量采用并行結構的截短RS碼譯碼器的實現方式。驗證表明,該算法能顯著提高基于FPGA的RS譯碼

2009-09-19 09:39:43

Turbo碼編碼器的FPGA實現Turbo碼譯碼器的FPGA實現Turbo碼編譯碼器的性能有哪些?

2021-05-07 06:06:23

請教一下大神如何在STM32中實現LIN協議和RS485協議呢?

2022-12-13 07:17:37

前言 隨著數字化廣播電視技術的迅速發展和基于MPEG-2標準的圖像壓縮和復用技術的完善,利用PC對大容量信息的處理變得日益重要,如基于PC的軟復用器的實現,使得通過PC接收DVB(數字視頻廣播)碼流

2019-05-05 09:29:32

【作者】:楊一波;李廣軍;【來源】:《信息與電子工程》2010年01期【摘要】:根據RS編碼器的特點,提出了一種可以實現任意編碼多項式、任意并行倍數的并行RS編碼器IP的自動生成方法。該方法

2010-04-22 11:46:09

本文介紹的是利用多路轉換開關實現準多點RS-232通信。

2009-04-20 11:30:51 39

39 詳細介紹了嵌入式L inux 編譯環境的架構, 討論了如何在L inux2. 4 環境下實現IP 安全協議, 實現數據安全傳輸, 通過利用L inux 實現防火墻所提供的5 個鉤子函數掛載點, 將安全模塊嵌入到

2009-04-21 23:30:01 28

28 本文主要講述的是如何利用多路轉換開關實現準多點RS-232通信。

2009-04-23 08:58:40 27

27 針對LDPC碼與RS碼的串行級聯結構,提出了一種基于Chase的聯合迭代譯碼方法。軟入軟出的RS譯碼器與LDPC譯碼器之間經過多次信息傳遞,性能可以逼近最大似然譯碼。模擬結果顯示:

2009-05-12 21:47:25 22

22 本文利用Altera 公司開發的RS、NCO 和FIR IP core 以及Simulink、DSP_Builder中的模塊快速搭建了一個RS(204,188) +DQPSK 的低中頻調制解調系統。分別在Simulink、Modelsim 中驗證了系統的功能,

2009-08-10 11:09:07 10

10 RS 碼以其強大的糾正隨機錯誤和突發錯誤的能力,被廣泛地應用于各種數字通信系統中,本文首先敘述了RS 碼譯碼的基本原理,給出了實現RS 碼軟判決譯碼的方法和用DSP 實現譯碼的

2009-08-19 10:26:07 22

22 本文利用可編程邏輯的靈活性和Nios 的強大處理能力,將多種編譯碼模塊和微處理器模塊集成到一片FPGA 內部,方便地實現了通用編譯碼器的設計。由于采用了VHDL 語言,使系統具有可移

2009-11-30 14:27:56 22

22 本文探討了無線通信中廣泛涉及的差錯控制問題,介紹了卷積碼的編譯碼原理。提出了一種卷積碼編碼,及其高速Viterbi 譯碼的實現方案,對譯碼的各個組成部分作了分析,并在FP

2010-01-06 15:06:59 13

13 提出用Reed Solomon(RS)乘積碼作為外碼,卷積碼作為內碼的級聯碼方案并且內外碼間用Congruential 向量生成的交織圖案對RS 碼符號進行重排列。對此級聯碼采用的迭代譯碼基于成員碼的軟

2010-02-10 11:09:30 10

10 摘要:在數字通信中,選擇合適在信道中傳輸的碼型是十分重要的,HDB3碼是比較常用的信道傳輸碼型,因此HDB3碼的編譯碼就顯得非常重要.多數的數字基帶信號用單極性不歸零碼(NR

2010-05-17 09:08:49 43

43 本文探討了無線通信中廣泛涉及的差錯控制問題,介紹了卷積碼的編譯碼原理。提出了一種卷積碼編碼,及其高速Viterbi譯碼的實現方案,對譯碼的各個組成部分作了分析,并在FPGA中實現

2010-07-21 17:20:04 22

22 針對固定碼長Turbo碼適應性差的缺點,以LTE為應用背景,提出了一種幀長可配置的Turbo編譯碼器的FPGA實現方案。該設計可以依據具體的信道環境和速率要求調節信息幀長,平衡譯碼性

2010-11-11 16:07:59 26

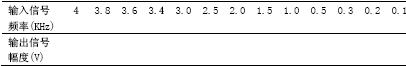

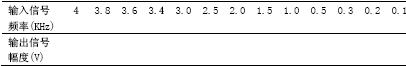

26 PCM編譯碼實驗

一、實驗目的1. 掌握PCM編譯碼

2008-10-21 13:35:45 9567

9567

基于BIST的編譯碼器IP核測

隨著半導體工藝的發展,片上系統SOC已成為當今一種主流技術。基于IP復用的SOC設計是通過用戶自定義邏輯(UDL)和連線將IP核整合

2008-12-27 09:25:39 1195

1195

LDPC編譯碼LDPC碼是一種線性分組奇偶校驗碼,它采用基于因子圖的置信傳播(Belief Propagation,BP)迭代譯碼算法進行譯碼。其性能接近Turbo碼,不規則LDPC碼甚至超過Tur

2009-03-01 17:36:05 2334

2334

差錯控制編碼技術對改善誤碼率、提高通信的可靠性具重要作用。RS碼既可以糾正隨機錯誤,又可以糾正突發錯誤,具有很強的糾錯能力,在通信系統中應用廣

2009-03-28 16:38:42 935

935

實驗九 PCM編譯碼 一、實驗目的

1. 掌握PCM編譯碼原理。 2. 掌握PCM基帶信號的形成過程

2009-04-01 14:44:49 11459

11459

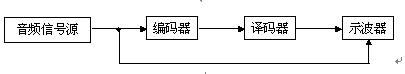

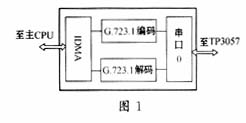

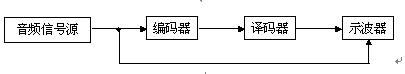

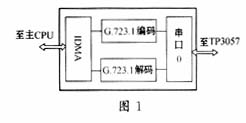

【摘 要】 介紹了ITU-TG.723.1標準語音編譯碼器的算法及其在ADSP-2181芯片上的實現 。軟硬件結合實現了語音信號的采樣和實時編譯碼,完全符合ITU-TG.723.1標準的定點算法

2009-05-10 19:54:11 1801

1801

摘要:提出了基于歐氏算法和頻譜分析相結合的RS碼硬件編譯碼方法;利用FPGA芯片實現了GF(2 8)上最高速率為50Mbps、最大延時為640ns的流式譯碼方案,滿足了高速

2009-06-20 14:19:33 1136

1136

卷積碼/Viterbi譯碼,卷積碼/Viterbi譯碼是什么意思

卷積碼在一個二進制分組碼(n,k)當中,包含k個信息位,碼組長度為n,每個碼組的(

2010-03-18 14:09:21 2453

2453 RS糾錯編碼是目前最有效、應用最廣泛的差錯控制編碼之一,是一種糾錯能力很強的多進制BCH碼,也是一類典型的代數幾何碼。它是由里德(Reed)和索洛蒙(Solomon)應用MS多項式于1960年首

2010-06-04 08:28:18 2015

2015

摘要! 在介紹(RS糾錯編碼原理的基礎上#將其應用于水聲數據的無線傳輸中$ 在仿真環境以 及聯機實驗中#對(RS碼應用前后的糾錯效果進行了分析比較$ 結果表明#在糾錯范圍內#水聲數據無

2011-04-08 16:47:33 21

21 介紹了ITU-TG.723.1標準語音編譯碼器的算法及其在ADSP-2181芯片上的實現 。軟硬件結合實現了語音信號的采樣和實時編譯碼,完全符合ITU-TG.723.1標準的定點算法,通過了ITU-T的所

2011-07-06 09:49:07 1807

1807

從赫夫曼樹定義及算法出發,介紹了一個赫夫曼編譯碼系統的設計與實現過程。這對于深入理解數據結構、程序設計有益。

2011-10-19 14:44:01 31

31 利用ME算法實現結構設計了一種低資源占用率、低成本的高速RS譯碼器。邏輯綜合及仿真結果表明,基于Altera公司CycloneII系列FPGA的RS(255,239)譯碼器,工作時鐘達210 MHz,可滿足數據速率1.68 Gb

2011-12-15 17:23:28 28

28 結合RS碼的基本特性,講述了RS碼的編解碼過程,給出了經過實際驗證的RS編解碼在超短波跳頻電臺開發中的軟件應用實例。

2012-02-13 10:07:26 26

26 本文介紹了 RS[ 255, 223 ]編譯碼器的 FPGA設計和基于線形反饋移位寄存器的編碼器設計 , 以及由伴隨式計算、關鍵方程求解、錢氏搜索、Forney算法等功能模塊組成的譯碼器。為了實現簡單

2012-05-22 10:43:40 45

45 針對區域內多個小區普查的需求,對復雜環境下低信噪比WCDMA小區搜索進行了針對性改進,采用差分相干累積以及RS軟譯碼算法提高了低信噪比條件下WCDMA小區搜索性能并利用FPGA進行了工

2012-08-13 17:26:45 25

25 介紹了符合CCSDS標準的RS(255,223)碼譯碼器的硬件實現結構。譯碼器采用8位并行時域譯碼算法,主要包括了修正后的無逆BM迭代譯碼算法,錢搜索算法和Forney算法。采用了三級流水線結構實現

2013-01-25 16:43:46 68

68 基于FPGA的RS碼電路設計,編碼譯碼原理。

2016-03-30 16:32:42 2

2 RS編解碼的FPGA實現-說明RS編解碼的FPGA實現-說明。

2016-05-04 15:59:44 21

21 testbench來驗證設計。 Integrate帶有Xilinx IP Block的 HLS IP 這里展示了在IP Integrator中,如何將兩個HLS IP blocks跟Xilinx IP FFT結合在一起 ,并且在Vivado中驗證設計。

2017-02-07 17:59:29 4760

4760

本文從研究應用于AOS系統的RS(255,223)編譯碼接口卡出發,深入地分析和研究了糾錯碼原理、RS編譯碼算法與設計、PCI總線標準與設計和FPGA技術。 隨著科技的發展,糾錯碼技術在通信領域

2017-08-31 14:50:39 4

4 。但是工業設備的使用環境經常比較惡劣,可能會存在噪聲或者電源諧波的干擾,RS-232在如此環境下抗干擾的能力遠不及RS-485,除此之外,RS-232只能是一對一控制,而RS-485則可以實現一對多控制;RS-232一般是9針公頭,而RS-485則是兩根線就可以控制。因此工業環境下的串行通信

2017-09-29 17:10:28 6

6 提出了RS編碼的實現方法,并對編碼進行了時序仿真。仿真結果表明,該譯碼器可實現良好的糾錯功能。 RS(ReedSolomon)碼是差錯控制領域中的一種重要線性分組碼,既能糾正隨機錯誤,又能糾正突發錯誤,且由于其出色的糾錯能力,已被NASA、ESA、CCSDS等空間組織接受

2017-10-17 11:21:32 47

47 (;A平臺,利用Xilinx lSE軟件和Verilog硬件描述語言,對譯碼器中各個子模塊進行了設計和仿真。整個譯碼器設計過程采用流水線處理方式。時序仿真結果表明在保證錯誤符號不大于8個的情況下,經過295個固有延遲之后,每個時鐘周期均可連續輸出經校正的碼字,該RS譯碼器的糾錯能

2017-11-07 15:27:06 15

15 在ISE下,對綜合后的網表進行編輯幾乎是不可能的事情,但在Vivado下成為可能。Vivado對Tcl的支持,使得Tcl腳本在FPGA設計中有了用武之地。本文通過一個實例演示如何在Vivado下利用Tcl腳本對綜合后的網表進行編輯。

2017-11-18 03:16:01 8351

8351

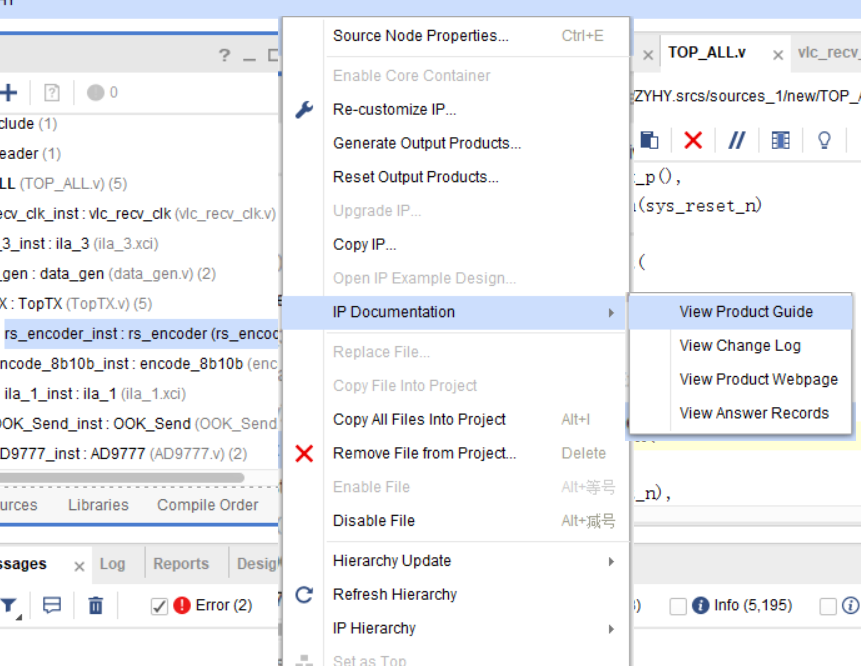

在Vivado下,有兩種方式管理IP。一種是創建FPGA工程之后,在當前工程中選中IP Catalog,生成所需IP,這時相應的IP會被自動添加到當前工程中;另一種是利用Manage IP,創建獨立

2017-11-18 04:22:58 6145

6145 該文通過對低密度校驗(LDPC)碼的編譯碼過程進行分析,提出了一種基于FPGA 的LDPC 碼編譯碼器聯合設計方法,該方法使編碼器和譯碼器共用同一校驗計算電路和復用相同的RAM 存儲塊,有效減少

2017-11-22 07:34:01 5141

5141

中小長度的數據報文業務為主,所以突發通信中的Turbo碼的碼長也是中等長度以下的。本文面向突發數據通信中的信道編碼應用,研究了短幀長Turbo碼編譯碼算法的FPGA實現。實現中采用了優化的編譯碼算法,以降低譯碼復雜度和譯碼延時。最后仿真和測試了Turbo譯碼器的糾錯性能和吞吐量。

2018-07-12 08:15:00 4457

4457

及1090ES擴容數據鏈結構,設計RS碼的碼元總長度為54;然后,通過Matlab仿真,探討了不同RS碼編碼效率下的差錯性能及其對1090ES擴容系統性能的影響,由此確定了RS碼編碼效率的最佳選取范圍為0.6-0.7;最后,具體分析所選定編碼效率范圍內RS碼的差錯性能,進一步確定了信息碼元長度,仿真結

2018-01-04 16:02:02 0

0 面向云存儲容錯系統提出了一種RS再生糾刪碼,該編碼繼承了RS編碼容多錯的可靠性,又能實現容三錯的高效性。對RS再生碼中單節點故障混合修復方法進行了介紹,并求出了混合修復時磁盤讀取數的理論下界。從

2018-02-07 15:53:48 0

0 coding,RS-CC碼)以構造等效刪除信道,并采用實時性高的短I_T碼實現糾刪功能。設計了一種適合短I.T碼的譯碼算法,同時給出了編碼度分布的選取方法。仿真結果表明,與已有短噴泉碼相比,文中短I_T碼成功譯碼時所需編碼冗余更少,應用到級聯方案后的數據傳輸可靠性明顯提高

2018-03-20 16:19:12 0

0 此視頻概述了Vivado Design Suite中的IP加密。

它涵蓋了IP加密工具流程,如何準備加密IP以及如何在Vivado中運行加密工具。

2018-11-20 06:34:00 7426

7426 了解Vivado實現中2015.3中的新增量編譯功能,包括更好地處理物理優化和自動增量編譯流程。

2018-11-30 19:24:00 5024

5024 第三代移動通信系統多種方案中,考忠將Turbo碼作為無線信道的編碼標準之- ~。 本文討論了Turbo碼的編譯碼基本原理,對Turbo碼的幾種常用的編譯碼算法進行了分析,并在給出編譯碼器模型的基礎上,用MATLAB語言實現了整個系統的計算機仿真并給出參

2019-01-04 10:40:42 19

19 二值圖。其次,將原始QR碼利用RS編碼矩陣進行異或操作得到中間QR碼,該QR碼和背景圖的顯著二值圖完全一致;然后,將背景圖像和中間QR碼按照特定的融合策略進行融合。最后,將融合圖再次利用RS糾錯機制進一步擴大美化區域,得到最終的

2019-01-17 13:39:45 21

21 本文檔的主要內容詳細介紹的是如何在WIN10系統下安裝AliOS Things的編譯環境。

2019-05-15 18:09:00 1

1 本文檔的主要內容詳細介紹的是如何在Linux環境下實現Python環境的搭建。

2020-08-24 12:12:00 14

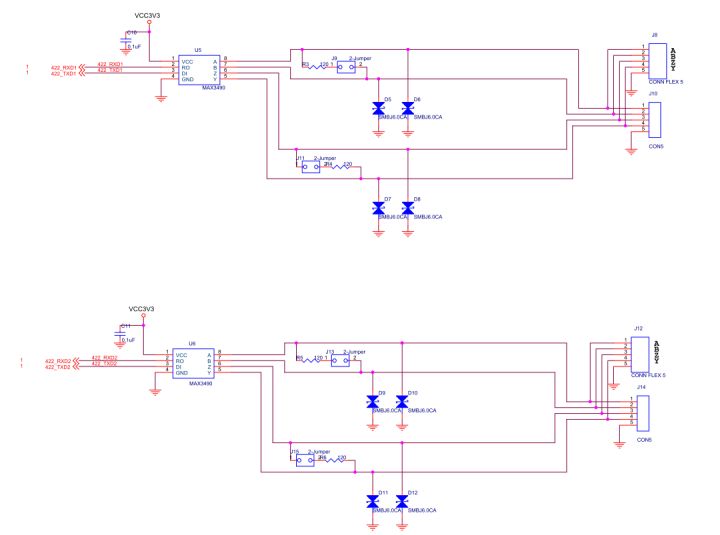

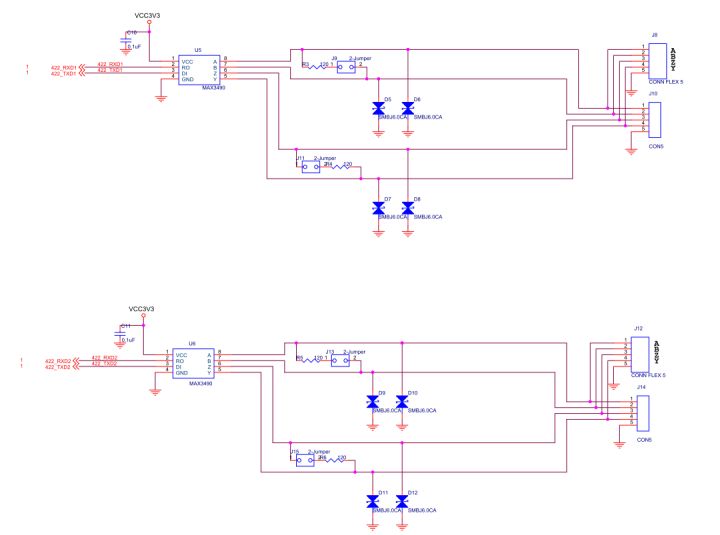

14 本章利用AN3485模塊實現RS422接口數據傳輸。關于模塊,在前面的RS232實驗中已經介紹過,本實驗不再贅述。RS422與RS232在與FPGA的連接的接口上是一樣的,都是TXD和RXD,因此,本實驗在RS232實驗的基礎上,例化出兩路連接到RS422接口芯片MAX3490上

2022-02-09 09:49:07 4227

4227

本文介紹如何在 vivado 開發教程(一) 創建新工程 的基礎上, 使用IP集成器, 創建塊設計。

2022-02-08 10:47:39 3601

3601

了在不增加譯碼復雜度的情況下實現有效而可靠的通信.通過將各級編解碼模塊化,利用FPGA技術實現了整個級聯糾錯編譯碼系統.實驗結果表明,模塊化的FPGA嵌入式設計不僅提高了系統的穩定性,還大大縮短了開發周期.

2021-02-01 14:26:42 5

5 RS碼在通信領域有著廣泛的應用,其中最重要的是關鍵方程的求解.傳統歐幾里德算法在求解關鍵方程時需要進行多項式次數的判斷,從而造成硬件電路復雜,譯碼速度下降.通過對綜合除法進行推廣,提出了一種改進型

2021-02-01 14:25:00 10

10 結構化LDPC碼可進行相應擴展通過對編譯碼算法,優化編譯碼結構進行調整,降低了編譯碼囂硬件實現中的關鍵路徑遲延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片實現了一個碼長10 240,碼率1/2的非正則結構化LDPC碼編碼器和譯碼器。實現結果表明:該編碼器信息吞吐量為1.878 Gb/

2021-03-26 15:58:00 12

12 基于軟件無線電的NRLDPC編譯碼設計與實現。

2021-05-28 10:07:04 5

5 成部分。Reed-So lomon (RS)碼是目前最有效、應用最廣的差錯控制編碼之一,是一類具有很強糾錯能力的多進制BCH 碼, 它既可以糾正突發錯誤, 也可以糾正隨機錯誤。RS 碼主要應用于實時性較高的移動通信系統、深空通信、數字衛星電視、磁記錄系統等方面。

2021-05-28 11:40:10 4465

4465

的,特別是在短的中等碼長下,性能接近香農限。本文是基于課題的要求,在Quartus II軟件中通過調用IP核的方式實現RS編譯碼過程,并通過Modelsim進行仿真驗證。

2022-09-28 10:02:21 7

7 通常情況下,一旦創建好Vivado工程,添加了相應的RTL文件,Vivado會自動找到設計的頂層文件,正確地顯示設計層次。在這個過程中,Vivado會自動分析文件的編譯順序。那么是否可以手動調整文件的編譯順序呢?答案是肯定的。

2023-01-06 09:27:39 6199

6199 隨著工業自動化技術的不斷發展,越來越多的工業設備在使用時需要進行數據通信。其中,RS485通信協議是一種常見的工業通信協議,而TCP/IP協議則是互聯網通信的標準協議。為了實現RS485協議與TCP

2023-05-05 15:50:44 4402

4402

網上有位讀者發來信息,說不知如何用RS編譯碼函數替換之前程序中的BCH編譯碼函數,因此我就又寫了一個程序,專門講解這個仿真過程。本科階段一般會涉及BCH、RS和卷積碼這三種編碼,了解各自特點,會用

2023-05-21 10:30:02 1131

1131

那么,它是如何實現這一功能的呢?YC-EIP-RS485/232是一款自主研發的通訊網關,可以在ETHERNET/IP網絡中做從站,同時在RS485/RS232網絡中做主站或從站,實現數據互通。這款

2023-07-11 09:19:58 1786

1786

你是否曾經遇到過這樣的問題:如何將ETHERNET/IP網絡和RS485/RS232總線連接起來呢?

2023-07-30 16:58:23 2023

2023

Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7270

7270

電子發燒友網站提供《基于VHDL語言的循環碼編譯碼系統的設計.pdf》資料免費下載

2023-10-13 14:31:37 1

1 主要介紹如何在本地搭建編譯環境來編譯rockchipBBuildrootllinuxSDK的源代碼。d當前sdk只支持在linux環境下編譯,并提供linux的交叉編譯工具。

2021-12-13 11:23:13 18

18 RS232轉PROFINET網關,實現固定式超市收銀掃碼機與PLC之間的無縫鏈接

2023-11-24 11:21:16 1159

1159

多個RS485設備如何實現防水連接 RS485是一種常見的串行通信協議,被廣泛應用于工業自動化設備以及各類傳感器、儀表等設備之間的通信。然而,在特殊工作環境下,如戶外、潮濕或濕潤的環境中,防水連接

2024-01-05 14:03:56 1387

1387 關鍵字 Ethernet IP,RS232,Ethernet IP轉RS232 背景 此案例為上海某車廠設備改造項目客戶。使用小疆Ethernet轉RS232網關連接掃碼槍進入生產線。上海某汽車

2024-01-09 16:05:10 1085

1085

在Vivado下,有兩種方式管理IP。一種是創建FPGA工程之后,在當前工程中選中IP Catalog,生成所需IP,這時相應的IP會被自動添加到當前工程中;另一種是利用Manage IP,創建獨立的IP工程,缺省情況下,IP工程的名字為magaged_ip_project。

2024-04-22 12:22:53 1963

1963

電子發燒友網站提供《如何在RS-485系統中隔離信號和電源.pdf》資料免費下載

2024-08-27 09:48:53 3

3 在一些應用中,需要從EtherNet/IP協議的PLC采集數據,并將其傳輸到RS485/232接口的設備,如霍尼韋爾的掃碼槍。通過使用捷米特JM-EIP-RS485/232協議轉換網關,可以實現這一

2024-11-02 10:38:08 1418

1418

在PROFINET網絡,這種需求越來越多的情況下,不同協議之間可以實現協議轉換就尤為重要,此方案是以微硬創新協議轉換網關為例,介紹如何實現RS485/ RS232 /MODBUS轉PROFINET

2025-03-13 10:48:11 818

818

本文探討了如何通過RS232轉Profinet技術,實現1200PLC與掃碼槍之間的通信,幫助構建高效、穩定的自動化生產系統。RS232是一種低成本、易用的串行通信協議,但傳輸速度較慢,且傳輸距離短。

2025-03-25 12:31:35 658

658

電子發燒友App

電子發燒友App

評論