對FPGA設(shè)計中常用的復(fù)位設(shè)計方法進行了分類、分析和比較。針對FPGA在復(fù)位過程中存在不可靠復(fù)位的現(xiàn)象,提出了提高復(fù)位設(shè)計可靠性的4種方法,包括清除復(fù)位信號上的毛刺、異步復(fù)位同步釋放、采用專用全局

2014-08-28 17:10:03 9365

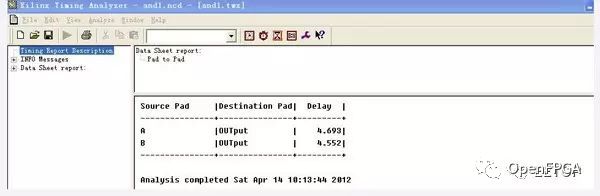

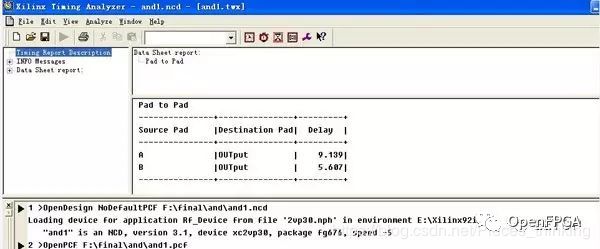

9365 信號在FPGA器件中通過邏輯單元連線時,一定存在延時。延時的大小不僅和連線的長短和邏輯單元的數(shù)目有關(guān),而且也和器件的制造工藝、工作電壓、溫度等有關(guān)。

2020-03-29 10:27:00 4067

4067 影響電路工作的可靠性、穩(wěn)定性,嚴(yán)重時會導(dǎo)致整個數(shù)字系統(tǒng)的誤動作和邏輯紊亂。下面就來討論交流一下FPGA 的競爭冒險與毛刺問題。

在數(shù)字電路中,常規(guī)介紹和解釋:

什么是競爭與冒險現(xiàn)象:

在組合電路中

2023-11-02 17:22:20

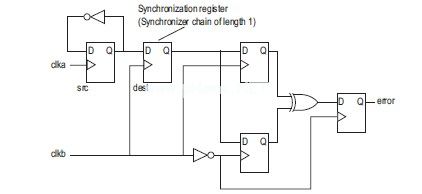

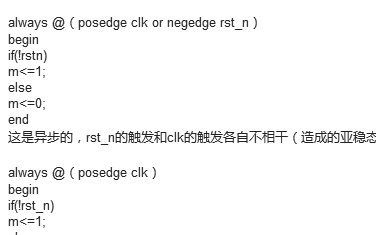

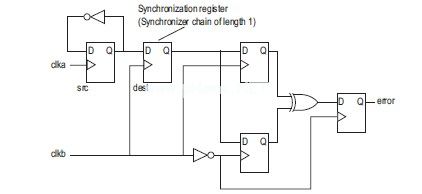

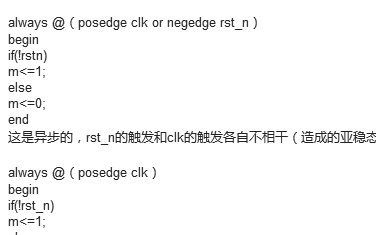

的,亞穩(wěn)態(tài)主要發(fā)生在異步信號檢測、跨時鐘域信號傳輸以及復(fù)位電路等常用設(shè)計中。03 亞穩(wěn)態(tài)危害由于產(chǎn)生亞穩(wěn)態(tài)后,寄存器 Q 端輸出在穩(wěn)定下來之前可能是毛刺、振蕩、固定的某一電壓值。在信號傳輸中產(chǎn)生亞穩(wěn)態(tài)

2020-10-22 11:42:16

冒險往往會影響到邏輯電路的穩(wěn)定性。時鐘端口、清零和置位端口對毛刺信號十分敏感,任何一點毛刺都可能會使系統(tǒng)出錯,因此判斷邏輯電路中是否存在冒險以及如何避免冒險是設(shè)計人員必須要考慮的問題。如何處理毛刺

2018-08-01 09:53:36

競爭冒險:在組合電路中,當(dāng)邏輯門有兩個互補輸入信號同時向相反狀態(tài)變化時,輸出端可能產(chǎn)生過渡干擾脈沖的現(xiàn)象,稱為競爭冒險。那么 FPGA 產(chǎn)生競爭冒險的原因是什么呢? 信號在 FPGA 器件內(nèi)部通過

2024-02-21 16:26:56

用FPGA做DDS,請教這種由于輸出信號的各位跳變時間有差異導(dǎo)致的毛刺怎么解決?

2017-05-17 09:57:54

有先有后,這種時差引起的現(xiàn)象稱為競爭(Race)。競爭的結(jié)果將很可能導(dǎo)致冒險(Hazard)發(fā)生(例如產(chǎn)生毛刺),造成錯誤的后果,并影響系統(tǒng)的工作。組合邏輯電路的冒險僅在信號狀態(tài)改變的時刻出現(xiàn)毛刺,這種冒險

2014-06-30 15:45:20

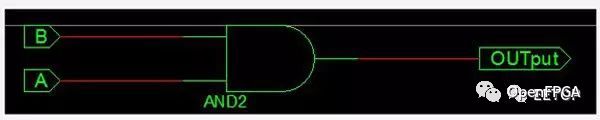

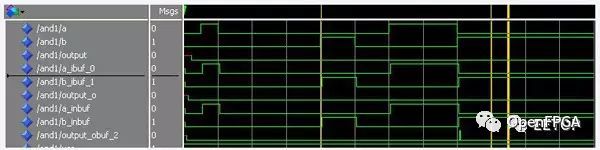

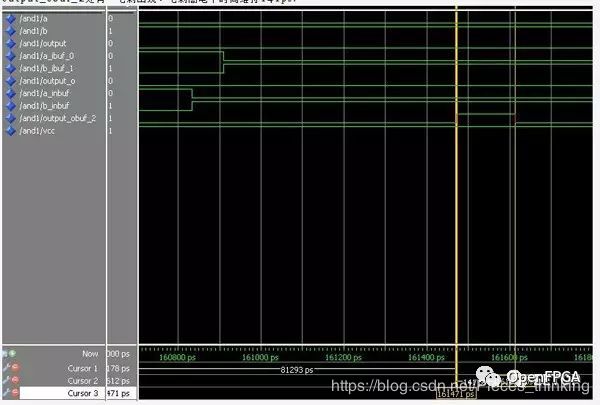

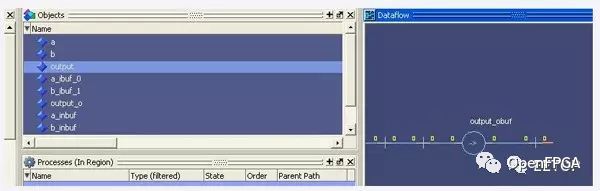

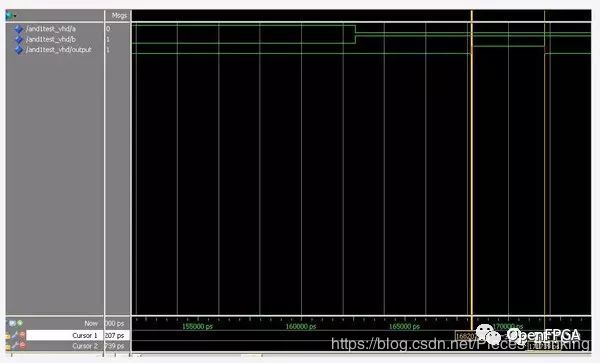

,我們稱之為“毛刺”。如果一個組合邏輯電路中有毛刺出現(xiàn),就說明該電路存在“冒險”。(特權(quán)同學(xué),版權(quán)所有)下面我們可以列舉一個簡單例子來看看毛刺現(xiàn)象是如何產(chǎn)生和消除的。如圖5.14所示,這里在圖5.10

2015-07-08 10:38:02

FPGA 20 位總線輸入經(jīng)過164245轉(zhuǎn)換后,高低電平變化時有時有毛刺,能達到4.6V。不知會不會燒壞FPGA。也沒找到技術(shù)支持電話。哪位大哥哥幫幫我。謝謝了

2013-07-15 15:01:45

FPGA的IO口輸出20M頻率方波信號,上升沿和下降沿有毛刺怎么辦?串聯(lián)磁珠或者匹配電阻有效嗎?同事想的辦法是在后面加個高頻的運放組成的射極跟隨器。我認為毛刺會通過射極跟隨器走到下一級電路。不知道怎么解決好?

2019-01-21 06:35:23

在FPGA的設(shè)計中,毛刺現(xiàn)象是長期困擾電子設(shè)計工程師的設(shè)計問題之一,是影響工程師設(shè)計效率和數(shù)字系統(tǒng)設(shè)計有效性和可靠性的主要因素。由于信號在FPGA的內(nèi)部走線和通過邏輯單元時造成的延遲,在多路信號變化

2012-09-06 14:37:54

,提高電路的穩(wěn)定性,而且其先進的開發(fā)工具使整個系統(tǒng)的設(shè)計調(diào)試周期大大縮短。而在FPGA設(shè)計中也存在一些難點問題,本文將主要分析、討論毛刺信號的產(chǎn)生原因及消除毛刺的方法。通過綜合運用這些方法,可以最大

2009-04-21 16:47:58

摘 要:以現(xiàn)場可編程門陣列(以下簡稱FPGA)在設(shè)計中由于其內(nèi)部構(gòu)成,容易引起競爭問題。以我們在實驗教學(xué)中的應(yīng)用與實踐為主線,詳細介紹了消除競爭冒險的各種方法。關(guān)鍵詞:現(xiàn)場可編程

2009-04-21 16:44:44

下面對FPGA設(shè)計中常用的復(fù)位設(shè)計方法進行了分類、分析和比較。針對FPGA在復(fù)位過程中存在不可靠復(fù)位的現(xiàn)象,提出了提高復(fù)位設(shè)計可靠性的4種方法,包括清除復(fù)位信號上的毛刺、異步復(fù)位同步釋放、采用專用

2021-06-30 07:00:00

FPGA連續(xù)信號給到AD9736,但是總會有周期毛刺出現(xiàn),如圖

邏輯分析儀檢查FPGA的輸出信號,沒有該毛刺出現(xiàn)

2023-12-18 06:16:33

FPGA連續(xù)信號給到AD9736,但是總會有周期毛刺出現(xiàn),如圖邏輯分析儀檢查FPGA的輸出信號,沒有該毛刺出現(xiàn)

2018-09-10 11:13:52

數(shù)字邏輯電路中的兩個基本門電路,A、B經(jīng)過不同的傳輸途徑達到,那么在設(shè)計時往往難于準(zhǔn)確知道A、B到達次序的先后,以及它們在上升時間和下降時間上的細微差異。因此,我們只能說只要存在競爭現(xiàn)象,輸出就有可能

2023-02-21 15:35:38

,因此毛刺現(xiàn)象在PLD、FPGA設(shè)計中尤為突出) 圖2給出了一個邏輯冒險的例子,從圖3的仿真波形可以看出,"A、B、C、D"四個輸入信號經(jīng)過布線延時以后,高低電平變換不是同時發(fā)生

2012-02-10 09:50:36

我用FPGA控制ad7865采集數(shù)據(jù)時,采集到的正弦波數(shù)據(jù)波形出現(xiàn)一些毛刺現(xiàn)象,請問該怎么解決,謝謝幫忙!

2014-06-07 00:00:30

錯位現(xiàn)象得到明顯好轉(zhuǎn)。示波器探頭測量信號時相當(dāng)于并聯(lián)上一個pF級的電容,也能夠一定程度上起到濾波的效果,因此可以斷定同步信號的毛刺影響了數(shù)據(jù)的采集。其中一個同步信號如圖1,兩個有效高脈沖之間有很多毛刺

2019-06-04 05:00:17

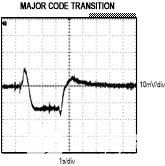

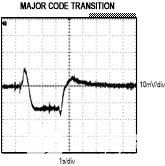

下圖是從AD5764芯片手冊中截取的。

下圖除了0 - 2.0us 是毛刺,其余部分都是穩(wěn)定在了-6mV 。

我的問題是:我用示波器測量我的波形的時候,到處都是大約20mV的毛刺。沒有像這么穩(wěn)定的 -6mV 。請問這是什么原因?

另外我想知道下圖您是用示波器側(cè)的嗎,您的電路是什么樣的呢?

2023-12-12 07:16:26

我使用AD5781的評估板,輸出10Hz 100mV的正弦波,我讀入AD7768-1的數(shù)據(jù)再通過AD5781輸出,我AD7768-1采集的數(shù)據(jù)中沒有毛刺,但我AD5781輸出的數(shù)據(jù)經(jīng)過運放

2023-12-07 06:04:30

最近使用AD768的過程中發(fā)現(xiàn),在數(shù)據(jù)轉(zhuǎn)換過程中伴隨時鐘信號的下降沿有一個4mV左右的毛刺,同時注意到fpga到da的數(shù)據(jù)線上也有這個現(xiàn)象,兩者之間是通過74alvc164245完成電平轉(zhuǎn)換的,現(xiàn)在想辦法去掉這個毛刺,請問有些什么好的建議!

2018-12-07 09:41:12

最近使用AD768的過程中發(fā)現(xiàn),在數(shù)據(jù)轉(zhuǎn)換過程中伴隨時鐘信號的下降沿有一個4mV左右的毛刺,同時注意到fpga到da的數(shù)據(jù)線上也有這個現(xiàn)象,兩者之間是通過74alvc164245完成電平轉(zhuǎn)換的,現(xiàn)在想辦法去掉這個毛刺,請問有些什么好的建議!

2023-12-22 06:59:24

在測試AD9117時,用FPGA給DAC一個正弦波的數(shù)字信號,在輸出端發(fā)現(xiàn)有脈沖毛刺出現(xiàn),在示波器上有毛刺的余暉。在頻譜上會有底噪抖動,我認為是毛刺造成,請問是否知道關(guān)于這個毛刺生成的有關(guān)原因

2019-01-17 08:19:07

前端電路輸入標(biāo)準(zhǔn)的正弦波,AD9681采集到的數(shù)據(jù)通過串行LVDS發(fā)送的到FPGA,這是FPGA采集到的波形:上邊沿下邊沿出現(xiàn)了規(guī)則的毛刺。前期排查:1、將拜倫變壓器后端的差分模擬信號飛線到另一

2019-01-18 16:33:32

前端電路輸入標(biāo)準(zhǔn)的正弦波,AD9681采集到的數(shù)據(jù)通過串行LVDS發(fā)送的到FPGA,這是FPGA采集到的波形:上邊沿下邊沿出現(xiàn)了規(guī)則的毛刺。

前期排查:

1、將拜倫變壓器后端的差分模擬信號飛

2023-12-12 06:00:44

觀察采集到的ADC波形(波形見圖片),發(fā)現(xiàn)有嚴(yán)重的毛刺現(xiàn)象,我個人認為毛刺現(xiàn)象不是PCB的問題(我之前懷疑是數(shù)據(jù)線和時鐘線沒有串聯(lián)33R的電阻,后來我串聯(lián)了33R的電阻還是不行),應(yīng)該是ADC內(nèi)部

2024-12-03 06:52:21

buffer單獨供電(3.4V),VD也用LDO單獨供電(3.3V)

FPGA對該adc進行采樣時,導(dǎo)致運放buffer輸出的信號上疊加了毛刺,毛刺的峰值大概100mV左右,毛刺的周期和采樣周期相同

2024-11-18 06:04:27

黃色為Vtune電壓,藍色為MUXOUT鎖定指示。如圖所示,黃色尖狀毛刺出現(xiàn)時,未鎖定。請問是,ADF4153A器件原因造成的隨機性不鎖定現(xiàn)象嘛?并且會在不鎖定的時刻出現(xiàn)毛刺。

2018-08-03 07:53:20

用LSM6DSM芯片,采集三軸加速度信號,出現(xiàn)如下的毛刺現(xiàn)象電路原理圖如下請問大家遇到過類此問題嘛,怎么解決的!謝謝!!

2019-04-02 19:39:40

工作,是芯片有問題嗎?

設(shè)計PLD/FPGA內(nèi)部電路與設(shè)計74的分立電路是有區(qū)別的。這個問題是由于電路中的毛刺產(chǎn)生的。電路布線長短不同造成延時不一致,有競爭冒險,會產(chǎn)生毛刺。分立元件之間存在分布電容

2024-04-12 16:58:35

我采用TLV3501將混頻后的50Hz正弦波變成方波,然后送入FPGA,對方波信號進行檢測,發(fā)現(xiàn)方波信號有有毛刺導(dǎo)致FPGA誤觸發(fā),有什么辦法減少方波的毛刺呀

2025-05-28 10:31:52

我們設(shè)計的電源是24V 3A。

1、毛刺現(xiàn)象:

在功放輸出端的波形測量到的波形在冷機啟動工作的前幾秒內(nèi)有頂部毛刺現(xiàn)象,然后工作一段時間后,波形又正常了;

如下圖是啟動時的波形:

再過8s后波形

2024-09-29 06:13:53

參數(shù):電壓15V,喇叭4歐、15W,電路基本上是按照TPA3118D2EVM電路,BTL模式,后面的LC為22uh、680nF,

產(chǎn)生問題現(xiàn)象,在某一段頻率會出現(xiàn)毛刺波形,聲音中有噪聲,像是失真的樣子,請問這問題出在那個方面,急需各位大神們幫助,謝謝了

2024-10-25 07:42:47

控制fpga進行,該階躍信號連接到fpga的某個引腳。發(fā)現(xiàn)在PCI-6733輸出的波形在時鐘的邊沿有毛刺。請問毛刺是什么原因呀?是時鐘的質(zhì)量不夠好嗎?還是接地有什么問題?

2020-05-17 09:24:09

如何解決電路中短時脈沖波形失真的所謂“毛刺”現(xiàn)象?并提出相應(yīng)的解決辦法。

2021-04-08 06:25:08

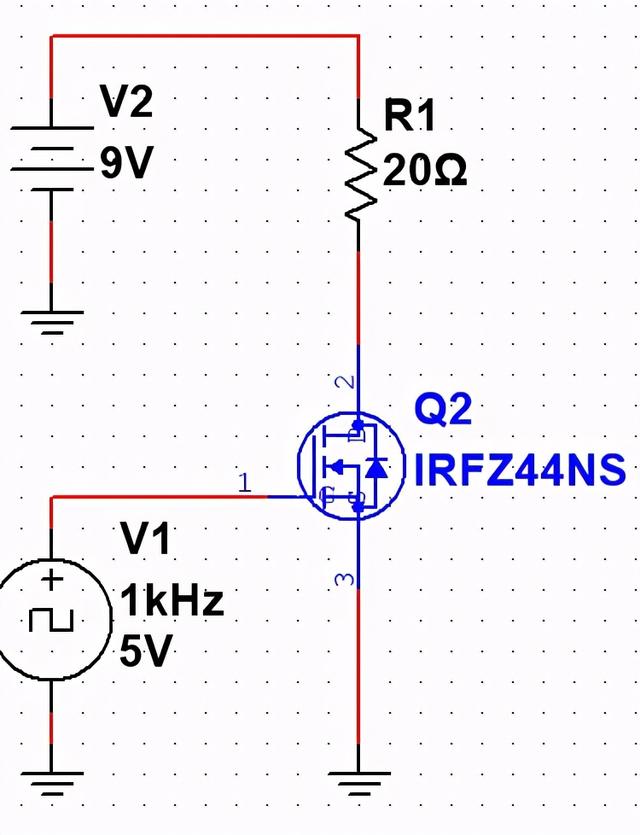

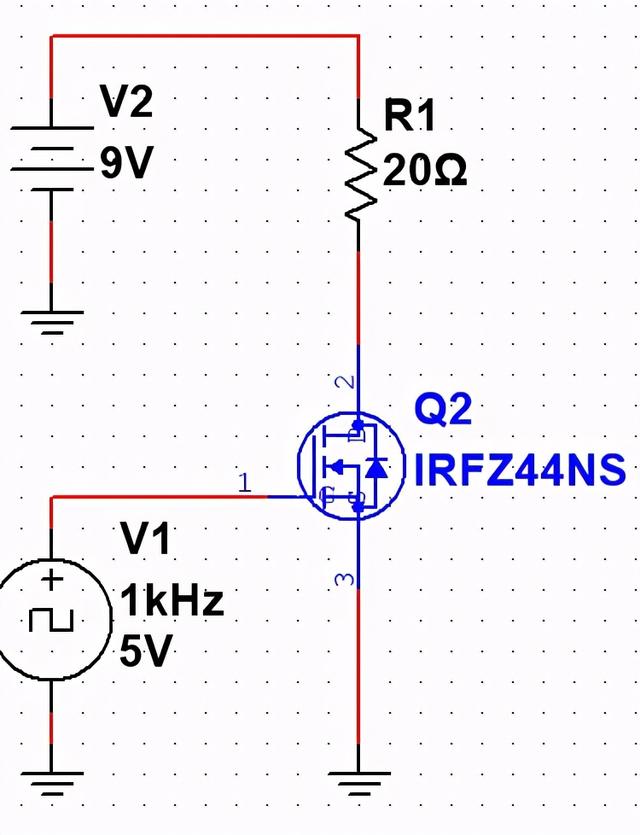

毛刺現(xiàn)象是我們每一個電子愛好者避之唯恐不及的,今天我們來學(xué)習(xí)一個毛刺現(xiàn)象以及如何規(guī)避它,進而掌握電感升壓的原理。簡單場管開關(guān)電路讓我們從一個簡單的電路開始,該電路使用一個 N 溝道場效應(yīng)管控制 20

2021-12-30 07:09:17

用FPGA做數(shù)字頻率計 捕捉上升沿低頻部分的方波是靠比較器產(chǎn)生的 LM339KHz級別還好Hz級的信號 頻率越低 示波器拉開看 產(chǎn)生的信號上升沿里面全是毛刺低頻部分 使用LM339的探測范圍要求

2016-06-28 18:31:31

,就說明該電路存在“冒險”。(與分立元件不同,由于 PLD 內(nèi)部不存在寄生電容電感,這些毛刺將被完整的保留并向下一級傳遞,因此毛刺現(xiàn)象在 PLD、FPGA 設(shè)計中尤為突出)。毛刺的累加,將會影響整個

2023-05-30 17:15:28

的看到毛刺現(xiàn)象(圖3-數(shù)字處理過程中已減去直流偏置),數(shù)字量采樣時 采樣了4次,去掉最大和最小值,在進行平均的;如果僅采樣一次,那毛刺更大。一開始懷疑是3.3V電壓源的問題(產(chǎn)生直流偏置,和對AD口進行

2018-10-08 17:02:49

我在調(diào)試ADS5400的時候,1G采樣率,雙通道,DDR模式,發(fā)現(xiàn)采集到的數(shù)據(jù)在沒有信號輸入時有毛刺現(xiàn)象。在spi不配置的情況下,輸出偏移二進制,理論上ADS5400輸出的值在2048左右,但是會出現(xiàn)520和3320的數(shù)據(jù)。這種情況該如何應(yīng)該,試過在fpga調(diào)整相移,效果不明顯。

2024-12-12 06:45:46

想測頻10-300kHz,信號跳變的時候毛刺很多,硬件定型了,只能用fpga濾波,誰有比較好的解決方法,能有現(xiàn)成代碼最好了,謝謝啦

2013-11-29 23:08:31

論述了電路中普遍存在的對偶現(xiàn)象,主要表現(xiàn)在對偶元件、對偶電路和對偶定律。利用對偶性有助于研究和設(shè)計各種應(yīng)用電路。關(guān)鍵詞:

2010-04-16 08:21:00 34

34 通過回顧混沌現(xiàn)象的歷史研究,介紹了混沌的Li?鄄Yoke定義及其特征;分析了非線性RLC串聯(lián)電路的電路方程和參數(shù),并利用梅利尼科夫(Melnikov)方法推斷出非線性RLC串聯(lián)電路中存在

2010-12-20 16:36:48 45

45 最新的化學(xué)去毛刺工藝

一提到去毛刺,很多人馬上聯(lián)想到的是洗磨。洗磨是現(xiàn)在運用最為普遍的一種去毛

2009-03-20 13:39:22 1417

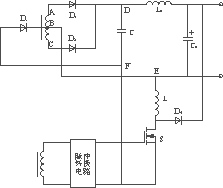

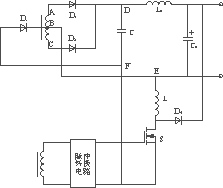

1417 高頻整流電路中的新型電壓毛刺無損吸收電路

0 引言

電壓毛刺是高頻變換器研制和生產(chǎn)過程中的棘手問題,處理得不好會帶來許多的

2009-07-06 08:27:55 1701

1701

電路的諧振現(xiàn)象分析

諧振現(xiàn)象是交流電路中產(chǎn)生的一種特殊現(xiàn)象,對諧振現(xiàn)象的研究有著重要的意義。在實

2009-07-27 08:11:02 11883

11883

理解FPGA中的壓穩(wěn)態(tài)

? 本白皮書介紹FPGA 中的壓穩(wěn)態(tài),為什么會出現(xiàn)這一現(xiàn)象,它是怎樣導(dǎo)致設(shè)計失敗的。介紹怎樣計算壓穩(wěn)態(tài)MTBF,重點是對結(jié)果造成影響的各種器

2010-02-04 11:01:51 945

945

組合邏輯中的競爭與冒險及毛刺的處理方法 在組合邏輯中,由于門的輸入信號通路中經(jīng)過了不同的延時,導(dǎo)致到達該門的時間不一致叫競爭。產(chǎn)生毛刺叫冒險。如果布爾式中有相反的信號則可能產(chǎn)生競爭和冒險現(xiàn)象。解決方法:一是添加布爾式的(冗余)消去項,但是不

2011-01-24 18:12:53 0

0 本文從FPGA的原理結(jié)構(gòu)的角度探討了產(chǎn)生毛刺的原因及產(chǎn)生的條件,在此基礎(chǔ)上,總結(jié)了多種不同的消除方法,在最后結(jié)合具體的應(yīng)用對解決方案進行深入的分析。

2011-08-03 11:48:15 2560

2560

FPGA 異步時鐘設(shè)計中如何避免亞穩(wěn)態(tài)的產(chǎn)生是一個必須考慮的問題。本文介紹了FPGA 異步時鐘設(shè)計中容易產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象及其可能造成的危害,同時根據(jù)實踐經(jīng)驗給出了解決這些問題的

2011-12-20 17:08:35 63

63 數(shù)字電路中的FPGA和verilog教程,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 17:44:30 42

42 組合邏輯中的競爭與冒險及毛刺的處理方法

2017-01-17 19:54:24 7

7 和所有的數(shù)字電路一樣,毛刺也是FPGA電路中的棘手問題,它的出現(xiàn)會影響電路工作的穩(wěn)定性,可靠性,嚴(yán)重時會導(dǎo)致整個數(shù)字系統(tǒng)的誤動作和邏輯紊亂。

2017-02-11 03:59:38 2361

2361

I2C 控制器規(guī)范 v2.1 規(guī)定了濾除快速工作模式下 SDA 和 SCL 線路上最大間距為 50ns 的毛刺。 Zynq-7000 AP SoCs PS7 中的 I2C 控制器沒有實現(xiàn)這些毛刺

2018-06-29 14:00:00 19863

19863 毛刺現(xiàn)象在FPGA設(shè)計中非常普遍, 而毛刺的出現(xiàn)往往導(dǎo)致系統(tǒng)結(jié)果的錯誤。本文從FPGA的原理結(jié)構(gòu)的角度深入探討了毛刺產(chǎn)生的原因及產(chǎn)生的條件,總結(jié)了多種不同的解決方法,并結(jié)合具體的應(yīng)用對解決方案進行

2017-11-22 14:24:54 10629

10629 鑄鐵去毛刺,切冒口,切焊口。鋁件去毛刺,發(fā)動機殼去毛刺

2017-11-24 14:40:53 3

3 數(shù)字電路設(shè)計人員經(jīng)常面臨的挑戰(zhàn)之一是要消除所設(shè)計電路的毛刺信號。為此,通常需要確保數(shù)據(jù)鎖存期間具有足夠的建立時間以及保持時間。 毛刺是不能在整個時鐘周期內(nèi)都保持有效的信號。帶毛刺的信號如果饋送

2018-03-27 18:46:00 1

1 通過改變設(shè)計,破壞毛刺產(chǎn)生的條件,來減少毛刺的發(fā)生。例如,在數(shù)字電路設(shè)計中,常常采用格雷碼計數(shù)器取代普通的二進制計數(shù)器,這是因為格雷碼計數(shù)器的輸出每次只有一位跳變,消除了競爭冒險的發(fā)生條件,避免了毛刺的產(chǎn)生。

2018-06-23 08:49:00 2095

2095

大家好,又到了每日學(xué)習(xí)的時間了,今天我們來聊一聊FPGA學(xué)習(xí)中,亞穩(wěn)態(tài)現(xiàn)象。 說起亞穩(wěn)態(tài),首先我們先來了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號在無關(guān)信號或者異步時鐘域之間傳輸時導(dǎo)致數(shù)字器件失效的一種

2018-06-22 14:49:49 3927

3927

高壓包的高壓卡簧與高壓線連接焊點有毛刺,毛刺尖端會產(chǎn)生放電現(xiàn)象,若放電,會將高壓帽橡膠燒老化。所以說如果家里或下雨季節(jié),家里比較潮濕,電視機高壓卡簧與高壓線連接焊點的毛刺會發(fā)電,導(dǎo)致電視高壓包損壞。

2019-01-22 17:04:46 34914

34914 毛刺的英文名是veining,一般金屬件表面出現(xiàn)余屑和表面極細小的顯微金屬顆粒,這些被稱為毛刺。毛刺越多,其質(zhì)量標(biāo)準(zhǔn)越低。所以企業(yè)生產(chǎn)產(chǎn)品的時候都會想辦法盡量減少出現(xiàn)的毛刺。

2019-04-29 16:03:57 14798

14798 去毛刺,就是去除在零件面與面相交處所形成的刺狀物或飛邊。毛刺的危害性尤為明顯, 逐漸引起人們的普遍重視, 并開始對毛刺的生成機理及去除方法進行研究。

2019-05-22 11:24:14 11051

11051 在機械加工過程中,不論采用多高級的精密設(shè)備,都會有或多或少的毛刺產(chǎn)生。如何高效去除毛刺成為了機械加工中的重點問題,各種方法也層出不窮,比如:

2019-12-15 10:44:30 12952

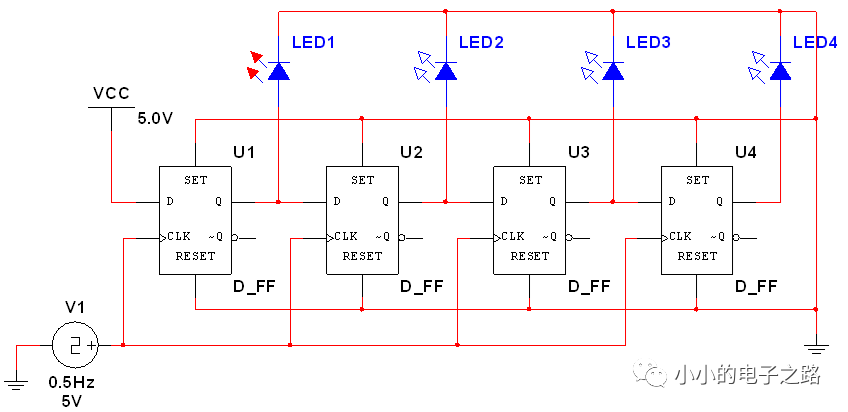

12952 最近看 advanced fpga 以及 fpga 設(shè)計實戰(zhàn)演練中有講到復(fù)位電路的設(shè)計,才知道復(fù)位電路有這么多的門道,而不是簡單的外界信號輸入系統(tǒng)復(fù)位。 流程: 1. 異步復(fù)位: 優(yōu)點:⑴大多數(shù)

2020-10-30 12:17:55 951

951 毛刺現(xiàn)象是我們每一個電子愛好者避之唯恐不及的,今天我們來學(xué)習(xí)一個毛刺現(xiàn)象以及如何規(guī)避它,進而掌握電感升壓的原理。簡單場管開關(guān)電路讓我們從一個簡單的電路開始,該電路使用一個 N 溝道場效應(yīng)管控制 20

2022-01-10 10:53:27 4

4 當(dāng)DAC輸出模擬值發(fā)生變化時,在DAC輸出端觀察到動態(tài)現(xiàn)象,表現(xiàn)為毛刺,如圖1所示。該毛刺能量定義為電壓曲線下的面積與示波器上捕獲的時間圖的關(guān)系。該毛刺能量的單位是nV × s。

2022-12-15 11:53:04 4857

4857

示波器波形毛刺通常是由信號本身帶來的噪聲或者示波器本身的問題造成的。下面是一些減少示波器波形毛刺的方法

2023-05-02 09:55:00 36194

36194 環(huán)氧樹脂包封的,正常情況下,表面都是光滑均勻的,但有極個別的會出現(xiàn)包封不良的現(xiàn)象,最終會出現(xiàn)有毛刺的問題,這甚至是很難避免的,一般生產(chǎn)的每一批CBB22電容,都有

2021-12-31 15:05:20 1252

1252

在金屬制品加工中不可避免的出現(xiàn)各種毛刺,這些毛刺對工件質(zhì)量產(chǎn)生嚴(yán)重的影響,因此去毛刺成為后續(xù)加工中一個必不可少的工序。以前大多企業(yè)通過人工去毛刺,但現(xiàn)在機械手裝配速科德Kasite浮動去毛刺主軸,將去毛刺工藝提高到一個新的水平。

2022-06-14 16:52:29 1781

1781

汽車行李架對表面處理有較高的要求,而且現(xiàn)有技術(shù)中的車頂行李架大多由多個零部件結(jié)裝構(gòu)成,其結(jié)構(gòu)通常比較復(fù)雜,有較多弧度,因此汽車行李架高效高精度打磨去毛刺難度較大。工業(yè)機器人+速科德Kasite

2022-10-26 15:21:27 3039

3039

毛刺是在進行機械加工過程中刀具與被加工的材料產(chǎn)生熱力的,如銑削、車削、磨削等。為提高工件的質(zhì)量和使用壽命,工件表面、銳角和棱邊必須達到極高的金屬潔凈度,因此金屬精密件去毛刺成為加工必不可少的一道工序。

2023-01-30 17:11:07 1712

1712

毛刺現(xiàn)象是我們每一個電子愛好者避之唯恐不及的,今天我們來學(xué)習(xí)一個毛刺現(xiàn)象以及如何規(guī)避它,進而掌握電感升壓的原理。

2023-08-15 14:53:20 6590

6590

門電路的兩個輸入信號同時向相反的邏輯電平跳變的現(xiàn)象叫做 競爭 ,這種競爭可能在電路的輸出端產(chǎn)生尖峰脈沖,這種現(xiàn)象稱為 競爭冒險 。

2023-09-25 11:50:45 5342

5342

RLC串聯(lián)電路中諧振的條件和現(xiàn)象是什么?? RLC串聯(lián)電路中,諧振是指電路在特定頻率下,電感、電容和電阻所構(gòu)成的電路中,電容、電感和電阻的阻抗相互抵消,導(dǎo)致電流達到最大值的狀態(tài)。在諧振頻率下,電路

2023-10-12 09:35:23 5578

5578 什么是毛刺?毛刺的大小和方向 如何測量毛刺的尺寸?如何檢查已去除的毛刺? 毛刺是指由于加工工藝或其他原因產(chǎn)生的金屬表面上的不平整區(qū)域或小尖刺。毛刺通常形成于金屬的切削或沖壓過程中,可能會影響產(chǎn)品

2023-12-07 14:24:36 8634

8634 如何最小化毛刺尺寸?如何控制毛刺方向? 為了得到高質(zhì)量的產(chǎn)品或工藝品,我們通常需要把毛刺的尺寸最小化,并控制其方向。毛刺會影響制品的外觀質(zhì)量、功能性能以及使用壽命。本文將介紹毛刺的形成原因、影響因素

2023-12-07 14:24:39 1683

1683 PCB鉆孔毛刺產(chǎn)生的原因及毛刺的危害 PCB(Printed Circuit Board)是一種非常重要的電子組件,被廣泛應(yīng)用于各種電子設(shè)備中。在PCB的生產(chǎn)過程中,鉆孔是一個非常關(guān)鍵的步驟,用于

2023-12-07 14:24:41 6902

6902 什么是緊固件毛刺呢?緊固件毛刺是怎么樣形成的呢?要如何很好的去除這種毛刺呢? 緊固件毛刺是指在緊固件(如螺釘、螺帽、螺栓等)的表面形成的一層或多層細小的突起。這些毛刺通常是由于制造過程中的不完

2023-12-07 14:24:44 1751

1751 沖裁加工時總是會產(chǎn)生毛刺,很難消除掉,因此,經(jīng)常在加工后進行壓毛刺來消除毛刺。鑒于分型面的問題,最近使用去毛刺的方式有增加的趨勢.

2023-12-12 14:17:08 1676

1676

信號毛刺是指信號中出現(xiàn)的突然幅度變化,通常表現(xiàn)為信號波形上的尖峰或震蕩。這種現(xiàn)象可能會導(dǎo)致電子設(shè)備的不穩(wěn)定性,甚至影響設(shè)備的正常運行。為了準(zhǔn)確觀察信號毛刺并找出其原因,使用示波器是一種常見的方法。本文將介紹如何使用示波器觀察信號毛刺,并給出一些常見的處理方法。

2023-12-26 15:04:48 2420

2420

自諧振現(xiàn)象對電路性能的影響及其避免方法? 自諧振現(xiàn)象是指電路中的元件參數(shù)(如電感、電容等)與外部激勵頻率之間存在某種特定關(guān)系,從而導(dǎo)致電路發(fā)生共振現(xiàn)象。自諧振現(xiàn)象在電路設(shè)計和應(yīng)用中是一個重要

2024-02-03 14:19:24 3076

3076 在現(xiàn)代制造業(yè)中,鋁鑄件因其質(zhì)量輕、強度高、耐腐蝕性好等性能,被廣泛應(yīng)用于航空航天、汽車制造、電子設(shè)備等眾多領(lǐng)域。然而,鋁鑄件在生產(chǎn)過程中,不可避免地會產(chǎn)生毛刺。這些毛刺不僅影響鋁鑄件的外觀質(zhì)量,還可

2025-07-16 09:40:46 338

338

超景深顯微鏡,以其亞微米級的測量能力,為鋰電池極片毛刺的檢測帶來了革命性的進步,助力鋰電池制造過程中的毛刺控制。毛刺,特別是金屬毛刺對鋰電池的危害極大,尺寸較大的

2025-08-05 17:54:10 1124

1124

電子發(fā)燒友App

電子發(fā)燒友App

評論