??????? 在FPGA的設計中,毛刺現象是長期困擾電子設計工程師的設計問題之一, 是影響工程師設計效率和數字系統設計有效性和可靠性的主要因素。由于信號在FPGA的內部走線和通過邏輯單元時造成的延遲,在多路信號變化的瞬間,組合邏輯的輸出常常產生一些小的尖峰,即毛刺信號,這是由FPGA 內部結構特性決定的。毛刺現象在FPGA的設計中是不可避免的,有時任何一點毛刺就可以導致系統出錯,尤其是對尖峰脈沖或脈沖邊沿敏感的電路更是如此。

????????任何組合電路、反饋電路和計數器都可能是潛在的毛刺信號發生器,但毛刺并不是對所有輸入都有危害,如觸發器的D輸入端,只要毛刺不出現在時鐘的上升沿并滿足數據的建立保持時間,就不會對系統造成危害。而當毛刺信號成為系統的啟動信號、控制信號、握手信號,觸發器的清零信號(CLEAR)、預置信號(PRESET)、時鐘輸入信號(CLK)或鎖存器的輸入信號時就會產生邏輯錯誤。在實際設計過程中,應盡量避免將帶有毛刺的信號直接接入對毛刺敏感的輸入端上,對于產生的毛刺,應仔細分析毛刺的來源和性質,針對不同的信號,采取不同的解決方法加以消除。

???????? 因此,克服和解決毛刺問題對現代數字系統設計尤為重要。本文從FPGA的原理結構的角度探討了產生毛刺的原因及產生的條件,在此基礎上,總結了多種不同的消除方法,在最后結合具體的應用對解決方案進行深入的分析。

1毛刺產生的原因

以圖1的例子分析毛刺產生的起因:圖1是一個3位同步加法計數器,當使能端為高電平時,在每個時鐘上升沿時刻,QA ,QB,QC從000逐步變到111,進入到全1狀態后,進位輸出端輸出半個時鐘脈沖寬度的高電平,但從圖2仿真結果中可以看到在011變化到100時刻ROC出現了尖脈沖,即毛刺。

以Xilinx的FPGA為例分析其內部結構,如圖3所示[2]。

FPGA芯片是由可構造的輸入輸出塊(Input/OutputBlock,IOB)、可構造邏輯塊(Cinfigur able Logic Block,CLB)和可編程連線資源(Programmable Interconnect Array,PIA)3種可構造單元構成的。IOB位于芯片內部四周,在內部邏輯陣列與外部芯片封裝引腳之間提供一個可編程接口,他主要由邏輯門、觸發器和控制單元組成。CLB組成了FPGA的核心陣列,能完成用戶指定的邏輯功能;每個CLB主要有一個組合邏輯、幾個觸發器、若干個多選一電路和控制單元組成;PIA位于芯片內部的邏輯塊之間,經編程后形成連線網絡,用于芯片內部邏輯間的相互連接,并在他們之間傳遞信息。從圖3中可以看出,對于不同的輸入1、2,到邏輯塊(M)的走線可能是不同的,這就造成了輸入信號的延遲,假設1、2同時變化,由于延遲的存在,到達M時就有先有后(這種現象稱為競爭),在邏輯輸出端就可能會有險象(也稱冒險),即產生了毛刺。在上述例子中的011狀態,假設QA與QB同時從1變化到0,而QC提前了2 ns從0變到1 ,產生一個2 ns的高電平,這就是毛刺。也就是說,在FPGA設計中,毛刺產生的根本原因是信號在芯片內部走線時產生的延遲。

2毛刺產生的條件

借助同樣的例子來分析毛刺產生的條件。QA,QB,QC在每一個時鐘上升沿同時發生翻轉,但實際中由于延遲的存在,并不能保證QA,QB,QC到D觸發器的布線長短一致。如果QC比Q A,QB提前了2 ns,這就形成了2 ns的全1狀態,稱為“假象全1”,進而導致進位輸出產生一個尖脈沖。值得注意的是,在3變到4即011到100時,3位中有2位同時發生翻轉,即在同一時刻有大于一個的信號發生改變。由于延遲的作用,多個信號到達終點的時間有先有后,形成了競爭,由競爭產生的錯誤輸出就是毛刺。所以,毛刺發生的條件就是在同一時刻有多個信號輸入發生改變。

3消除毛刺的方法

知道了毛刺產生的條件,就可以通過改變設計,破壞其條件來減少毛刺的發生。例如,利用格雷碼計數器每次輸出只有一位跳變的特性,代替普通的二進制計數器,避免了毛刺的產生[3]。還可以對電路進行改進,以消除毛刺對系統的影響。下面對各種方法做分別介紹:

3.1利用冗余項法

利用冗余項消除毛刺有2種方法:代數法和卡諾圖法,兩者都是通過增加冗余項來消除險象,只是前者針對于函數表達式而后者針對于真值表。以卡諾圖為例,若兩個卡諾圓相切,其對應的電路就可能產生險象。因此,修改卡諾圖,在卡諾圖的兩圓相切處增加一個圓,以增加多余項來消除邏輯冒險。但該法對于計數器型產生的毛刺是無法消除的。

3.2采樣法

由于冒險多出現在信號發生電平跳變的時刻,即在輸出信號的建立時間內會產生毛刺,而在保持時間內不會出現,因此,在輸出信號的保持時間內對其進行采樣,就可以消除毛刺信號的影響,常用的采樣方法有2種:一種使用一定寬度的高電平脈沖與輸出相與,從而避開了毛刺信號,取得輸出信號的電平值。這種方法必須保證采樣信號在合適的時間產生,并且只適用于對輸出信號時序和脈沖寬度要求不嚴的情況。另一種更常見的方法叫鎖存法,是利用D觸發器的輸入端D對毛刺信號不敏感的特點,在輸出信號的保持時間內,用觸發器讀取組合邏輯的輸出信號。由于在時鐘的上升沿時刻,輸出端Q=D,當輸入的信號有毛刺時,只要不發生在時鐘的上升沿時刻,輸出就不會有毛刺。這種方法類似于將異步電路轉化為同步電路,實現簡單,但同樣會涉及到時序問題。

3.3吸收法

由于產生的毛刺實際上是高頻窄脈沖,故增加輸出濾波,在輸出端接上小電容C就可以濾除毛刺。但輸出波形的前后沿將變壞,在對波形要求較嚴格時,應再加整形電路,該方法不宜在中間級使用。

3.4延遲法

因為毛刺最終是由于延遲造成的,所以可以找出產生延遲的支路。對于相對延遲小的支路,加上毛刺寬度的延遲可以消除毛刺。但有時隨著負載增加,毛刺會繼續出現,而且,當溫度變化,所加的電壓變化或要增加邏輯門時,所加的延遲是不同的,必須重新設計延遲線,因而這種方法也是有局限性的。而且采用延遲線的方法產生延遲會由于環境溫度的變化而使系統可靠性變差。

3.5硬件描述語言法

這種方法是從硬件描述語言入手,找出毛刺產生的根本原因,改變語言設計,產生滿足要求的功能模塊,來代替原來的邏輯功能塊。在圖1電路中,一個3位計數器可能會在011到100和101到110發生跳變時產生毛刺,究其原因是因為一次有2位發生跳變,可以采用VHDL語言對計數器編寫如下,產生的計數模塊代替原來普通的計數器。

注意在新的計數器中,每次狀態發生改變時Q0,Q1,Q2 只有1位發生跳變,從根本上消除了毛刺。但計數器的輸出狀態沒有規律,不便于其他電路利用。如果希望計數器的輸出狀態有規律變化以便其他電路使用,可以考慮采用雙輸出電路,一路是單信號輸出,一路是正常計數輸出。這種方法從根本上消除了毛刺產生的根源,具有普遍的意義,對系統也不會產生影響,是最為可靠的方法,其不利之處是這種方法對VHDL語言要求比較高,必須對電路的工作狀態及其轉變有全面的分析和掌握,而隨著電路的復雜度提高,毛刺產生的來源繁雜,實現起來比較困難。

對于一般情況下產生的毛刺,可以嘗試用D觸發器來消除。但用D觸發器消除時,有時會影響到時序,需要考慮很多問題。所以應根據不同情況,仔細地分析毛刺產生的來源和毛刺的性質,結合系統資源選擇具體辦法,消除毛刺的影響。

4具體實例

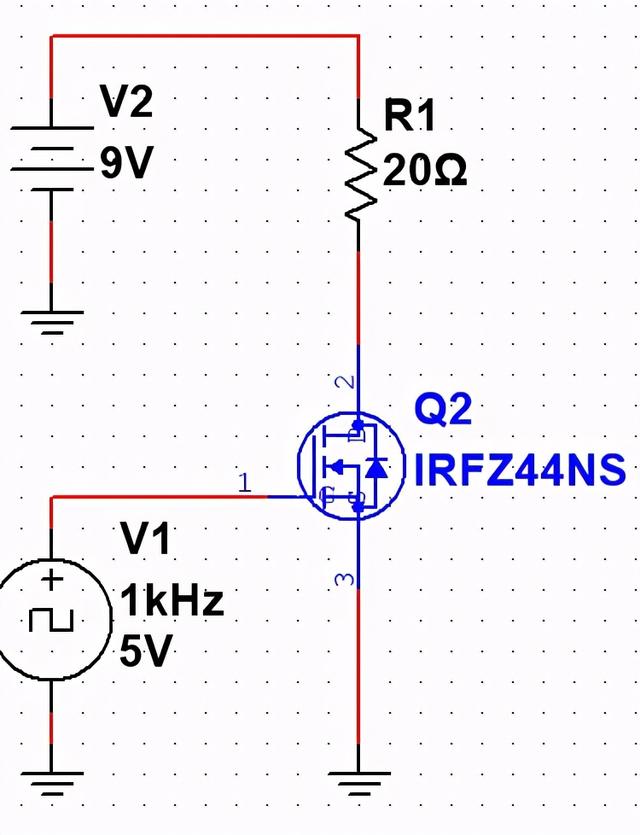

在實際應用中要對一個周期同步脈沖信號進行檢測,要求若在給定的時間內沒有檢測到同步信號則給出一定脈沖寬度的高電平,作為復位信號。設計思想是采用一個計數器,當有同步信號時對其清零,并同時開始計數,根據給定時間和系統時鐘周期設定計數器的模數,經過給定的時間后輸出高電平,滿足寬度后再置低。

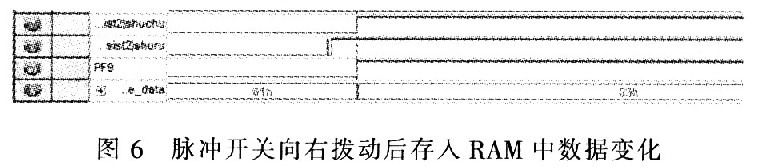

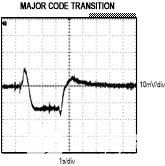

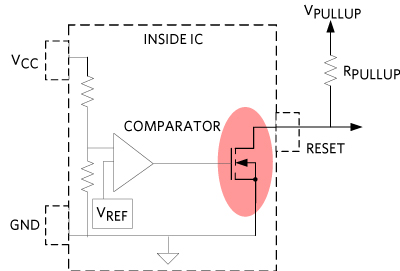

實際要求檢測時間大約1 s,脈沖寬度保持在20 ms左右,采用5片74161級聯,第5片計數器的ROC接D觸發器的使能端。同步信號輸入后,清零并開始計數,若不再出現同步脈沖,經16^5 個時鐘周期后,第5片的RCO端輸出一個高電平,使觸發器的Q輸出D(高電平),再過16^3*2個時鐘周期后使第4片的QA,QB,QC,QD接組合門電路輸出低電平,接到D觸發器的計數器預制端,使Q輸出為零。這樣就實現經一定延時后的一定寬度的脈沖。經仿真結果如圖4所示。

仿真平臺采用Max+PlusⅡ,時鐘周期設為10 ns,經計算可以知道在10.485 928 2 ms處產生寬度為81.92μs的高電平,但由于存在數據建立時間和保持時間,仿真結果中的變化時刻并不是嚴格與計算相符的,其中 q0,q1,q2,q3是第5片74161的輸出,roc1是第4片的進位輸出,roc是第5片的進位輸出,roc1輸出16個高電平后,roc同時輸出一個高電平。圖4中復位信號reset卻在5.247 ms和10.485 297 9 ms處發生。第一個錯誤的原因是,由于計數器累加,內部走線造成的延時,當第5片計數器從0111狀態跳變到1 000時,輸入同時有3位變化,致使進位輸出roc在roc1的第8個輸出時產生了一個尖脈沖,使觸發器的Q端提前發生電平轉變,導致了在5.247 ms處產生錯誤復位信號。同樣的原因,第4片的進位輸出roc1在第14個輸出跳變到第15個輸出時發生毛刺,而該毛刺使第5片161進入計數狀態,在roc端也產生了毛刺,就出現了圖4中復位信號提前翻轉的結果。

對于該電路中存在的毛刺問題,可以采用2種方法修改電路。由于該電路對時間要求的不是很嚴格,對第4,5片74LS161取1110狀態做最后輸出,就避免了由延遲造成的假象全1狀態,仿真結果證明這種方法是有效的。但這種方法增加了邏輯門數量,同時也增加了險象發生的可能性。

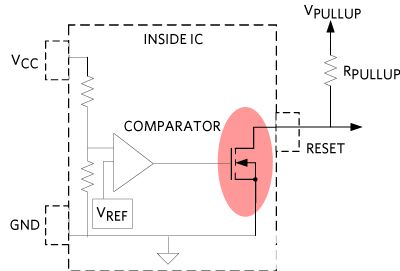

另一種比較可靠且常用的方法是用帶使能端的D觸發器代替原來的觸發器,把計數器最后的輸出roc接到觸發器的使能端,時鐘用統一的計數時鐘,由于毛刺本身是尖脈沖,不能滿足數據的建立時間和保持時間,避免了產生的毛刺對Q的輸出的影響。從仿真結果(圖5)中可以看到,雖然這種方法并不能消除毛刺,但是毛刺已經不具有危害性,故這是一種簡單有效的方法。

5結語

毛刺問題在FPGA設計中非常關鍵,只有深刻理解毛刺的本質,才有可能真正掌握設計的精髓,本文就FPGA設計中的毛刺問題進行了深入的探討,分析其產生的原因和條件,給出了幾種常用的消除方法,希望對FPGA設計者有一定的參考作用。

電子發燒友App

電子發燒友App

評論