1 UART原理

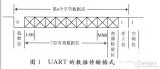

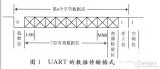

串行通信是指外部設(shè)備和計(jì)算機(jī)間使用一根數(shù)據(jù)線(另外需要地線,可能還需要控制線)進(jìn)行數(shù)據(jù)傳輸?shù)姆绞健?shù)據(jù)在一根數(shù)據(jù)線上一位一位傳輸,每一位數(shù)

2010-08-02 09:37:50 2825

2825

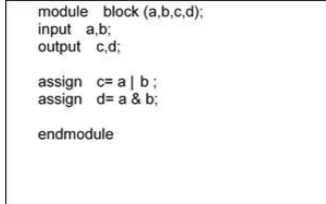

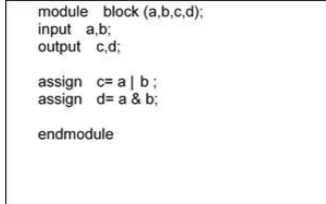

Verilog的基本設(shè)計(jì)單元是“模塊”(block)。一個(gè)模塊是由兩部分組成的,一部分描述接口,另一部分描述邏輯功能,即定義輸入是如何影響輸出的。

2019-06-26 15:30:40 13055

13055

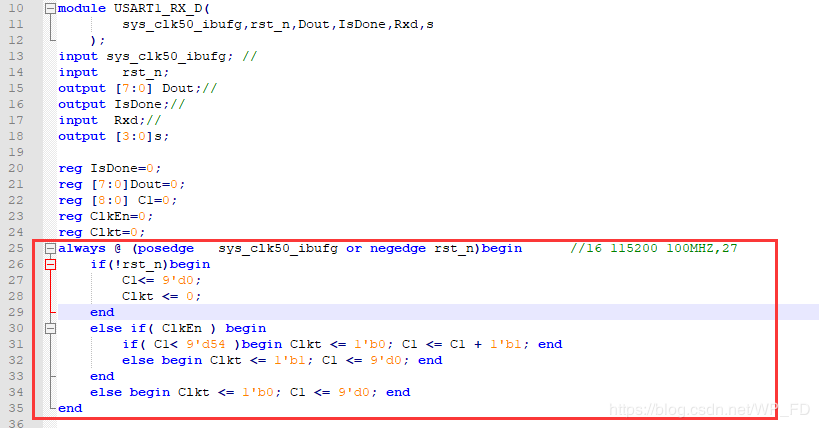

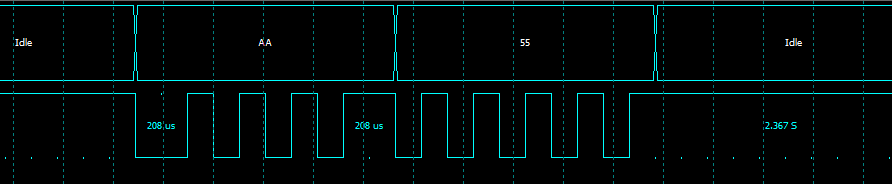

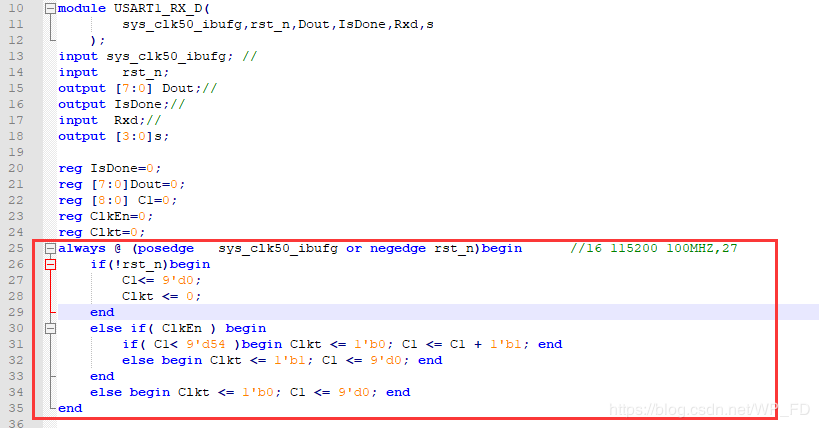

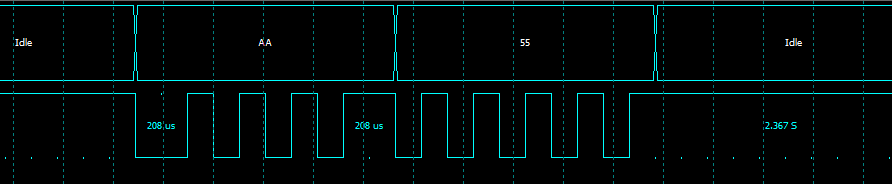

uart接收模塊設(shè)計(jì)主要分為波特率控制計(jì)數(shù)邏輯和按位接收邏輯。

2020-11-25 14:30:20 10174

10174

通用異步收發(fā)傳輸器(Universal Asynchronous Receiver/Transmitter),通常稱作UART。它將要傳輸?shù)馁Y料在串行通信與并行通信之間加以轉(zhuǎn)換。作為把并行輸入信號(hào)轉(zhuǎn)成串行輸出信號(hào)的芯片,UART通常被集成于其他通訊接口的連結(jié)上。

2023-01-05 09:48:46 4852

4852 在做模塊劃分時(shí),通常會(huì)出現(xiàn)這種情形,某個(gè)大的模塊中包含了一個(gè)或多個(gè)功能子模塊,verilog是通過(guò)模塊調(diào)用或稱為模塊實(shí)例化的方式來(lái)實(shí)現(xiàn)這些子模塊與高層模塊的連接的.

2025-05-03 10:29:00 1390

1390

特權(quán)同學(xué)的《FPGA/CPLD邊學(xué)邊練---快速入門Verilog/VHDL》中的UART串口收發(fā)實(shí)驗(yàn)發(fā)送數(shù)據(jù)和接收的數(shù)據(jù)不一致。在每個(gè)有效數(shù)據(jù)的后面都會(huì)多兩個(gè)數(shù)據(jù)。比如發(fā)送的有效數(shù)據(jù)是:FF。則

2017-11-30 09:25:44

你好,在我的項(xiàng)目中有兩個(gè)UART接口,一個(gè)是筆記本電腦,一個(gè)是GSM/GPS模塊。有一臺(tái)筆記本電腦使用UART SCB模式正確地在PIN P1.4和P1.5上工作。我使用UART V2.50為GSM

2019-10-11 14:04:36

Verilog 和 VHDL。本應(yīng)用說(shuō)明 Verilog 在數(shù)字 UART(通用異步接收器和發(fā)送器)的設(shè)計(jì)和驗(yàn)證中的使用。

UART 由兩個(gè)獨(dú)立的 HDL 模塊組成。一個(gè)模塊實(shí)現(xiàn)發(fā)送器,而另一個(gè)模塊實(shí)現(xiàn)接收

2024-04-01 14:41:47

Verilog實(shí)現(xiàn)接收的數(shù)據(jù)進(jìn)行發(fā)送。

2017-05-19 23:03:45

這是自己寫(xiě)的uart頂層模塊,編譯有個(gè)問(wèn)題請(qǐng)求大神解答:Error (10170): Verilog HDL syntax error at uart.v(5) near text "

2016-01-20 22:17:45

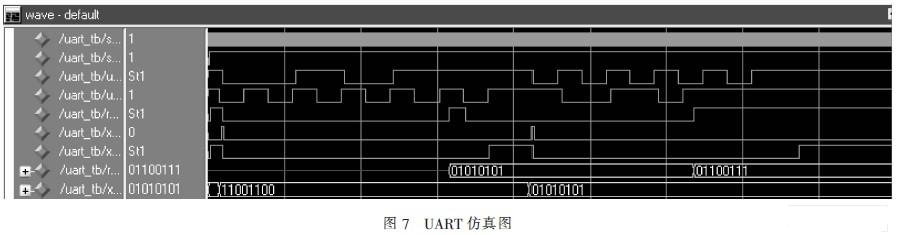

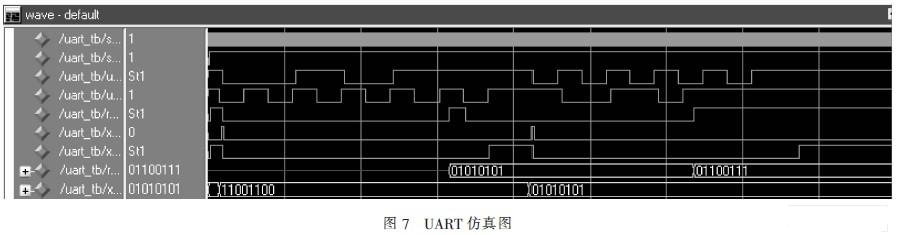

的UART的實(shí)現(xiàn)方法,具體描述了發(fā)送、接收等模塊的設(shè)計(jì),恰當(dāng)使用了有限狀態(tài)機(jī),實(shí)現(xiàn)了FPGA片上UART的設(shè)計(jì),給出了仿真結(jié)果。關(guān)鍵詞:通用異步收發(fā)器;串口通信;現(xiàn)場(chǎng)可編程邏輯器件;有限狀態(tài)機(jī)

2019-06-21 07:17:24

用FPGA 器件實(shí)現(xiàn)了UART 異步收發(fā)器的核心功能,可以實(shí)現(xiàn)對(duì)數(shù)據(jù)的接收和發(fā)送,并可以在接收數(shù)據(jù)時(shí)對(duì)其校驗(yàn)位、停止位進(jìn)行判斷,在發(fā)送數(shù)據(jù)時(shí)可以形成完整的一幀數(shù)據(jù)格式。其接收和發(fā)送數(shù)據(jù)的時(shí)鐘有內(nèi)部

2015-02-05 15:33:30

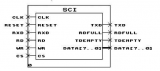

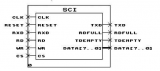

`UART 主要由 UART 內(nèi)核、信號(hào)監(jiān)測(cè)器、移位寄存器、波特率發(fā)生器、計(jì)數(shù)器、總線選擇器和奇偶校驗(yàn)器總共 7 個(gè)模塊組成,如圖 5-5 所示。圖 5-5 UART 實(shí)現(xiàn)原理圖UART 各個(gè)模塊

2018-10-18 09:51:47

如題,HX711模塊能實(shí)現(xiàn)萬(wàn)分之一精度嗎?怎么寫(xiě)處理程序呢?

2017-04-07 16:56:17

5-12 所示。(3)計(jì)數(shù)器模塊計(jì)數(shù)器模塊的功能是在輸入時(shí)鐘的驅(qū)動(dòng)下進(jìn)行計(jì)數(shù),當(dāng)?shù)竭_(dá)計(jì)數(shù)上閾時(shí)給 UART 內(nèi)核一個(gè)提示信號(hào),它們兩者之間的連接方法如圖 5-20 所示。在數(shù)據(jù)接收、數(shù)據(jù)加載和數(shù)據(jù)發(fā)送

2018-10-24 09:58:36

很遺憾很遺憾,中間放了個(gè)暑假時(shí)間拖到了試用期結(jié)束,這篇之后馬上到小處理器。一、UART接收器寫(xiě)了三四遍的verilog代碼,總是覺(jué)得有種必須得寫(xiě)成狀態(tài)機(jī)形式的感覺(jué)。寫(xiě)了幾遍加上sigaltap都調(diào)

2017-09-25 23:42:15

本人對(duì)于uart串口通訊理解比較混亂,不知道設(shè)計(jì)的uart接收模塊和發(fā)送模塊應(yīng)該怎么連接,串口通信是把串行數(shù)據(jù)接收,然后經(jīng)過(guò)接收模塊轉(zhuǎn)換成并行數(shù)據(jù),然后再經(jīng)過(guò)發(fā)送模塊一位一位發(fā)出去嗎?還是說(shuō),串行

2017-12-18 10:47:28

如圖所示在uart中怎么用verilog實(shí)現(xiàn)輸出A轉(zhuǎn)換到a

2019-10-16 16:26:11

;//中間采樣時(shí)鐘//UART接收部分///////////////////////////////////////////////////////////////////////一幀起始檢測(cè)

2014-07-08 23:08:28

基于至簡(jiǎn)設(shè)計(jì)法實(shí)現(xiàn)的紅外接收 verilog

2017-11-05 14:50:39

串行通信的工作方式有哪些?如何實(shí)現(xiàn)Verilog串口發(fā)送及接收一個(gè)字節(jié)數(shù)據(jù)呢?

2021-11-11 06:48:39

你好!我當(dāng)前使用的是ESP-IDF.當(dāng)uart接收不定長(zhǎng)的數(shù)據(jù)時(shí),希望通過(guò)空閑中斷或者事件的方式來(lái)結(jié)束一幀uart數(shù)據(jù)的接收。我看了\esp-idf-v4.4\examples

2023-02-15 07:04:47

DMA有何用途?如何去實(shí)現(xiàn)Stm32 Uart用DMA的方式接收數(shù)據(jù)呢?

2021-12-14 07:37:47

的按鈕,電話應(yīng)用程序?qū)?shù)據(jù)通過(guò)藍(lán)牙發(fā)送到模塊,模塊將uart發(fā)送到目標(biāo)。目標(biāo)響應(yīng),模塊從uart接收數(shù)據(jù)并將數(shù)據(jù)發(fā)送回電話。當(dāng)然可以。

2020-04-20 10:07:50

我的FPGA需要實(shí)現(xiàn)如下功能:接收一個(gè)兩字節(jié)的命令,如:16'h8003,8位字節(jié)接收,然后解析,我的實(shí)現(xiàn)如下,1)一共三個(gè)模塊,頂層模塊uart_top();2)子模塊uart_ctrl( )實(shí)現(xiàn)

2012-11-21 16:17:57

發(fā)燒友們好,我正在開(kāi)始學(xué)習(xí)fpga的知識(shí),現(xiàn)在尋求一個(gè)基于verilog的uart程序,要求是初始位一位,終止位一位,數(shù)據(jù)位8位,實(shí)現(xiàn)回環(huán)功能。大家能幫助一下我嗎?

2020-05-10 22:53:19

大家好,我正在嘗試用DMA實(shí)現(xiàn)PIC32 UART接收,到目前為止,在運(yùn)行代碼時(shí),我沒(méi)有在myBUFF中接收任何數(shù)據(jù),并且當(dāng)我使用PIC32MX130F256Bi通過(guò)rs232電纜從PUTTY發(fā)送

2020-04-06 08:49:21

請(qǐng)問(wèn)Verilog怎么實(shí)現(xiàn)UART/RS232/RS485收發(fā)自動(dòng)校調(diào)功能,降低接收誤碼率?

2021-06-21 07:27:16

SIM800 配置連接上服務(wù)器之后,通過(guò)串口使用(透?jìng)?非透?jìng)?模式傳輸數(shù)據(jù)到服務(wù)器;發(fā)現(xiàn)串口下發(fā)的hex數(shù)據(jù)被轉(zhuǎn)換為ASCII字符如圖所示:由于通信協(xié)議已經(jīng)固定,如何實(shí)現(xiàn)模塊UART接收到的數(shù)據(jù)不轉(zhuǎn)換為ASCII碼呢?

2019-02-15 06:36:04

使用的例程可以參考嗎?

3.基于我的這種應(yīng)用需求(接收不定長(zhǎng)數(shù)據(jù)),是推薦直接開(kāi)uart接收空閑中斷還是使用ESP-IDF中已經(jīng)定義好uart event實(shí)現(xiàn)? 如果使用uart接收空閑中斷有相關(guān)例程嗎?esp-idf-v4.4componentsdrivertesttest_uart.c 只有一個(gè)發(fā)送空閑中斷。

2024-06-05 07:55:00

UART 4 UART參考設(shè)計(jì),Xilinx提供Verilog代碼 uart verilog

THIS DESIGN IS PROVIDED TO YOU "AS IS". XILINX

2009-06-14 08:56:25 156

156 本文介紹了I2C總線規(guī)范,并根據(jù)該規(guī)范對(duì)I2C進(jìn)行模塊化設(shè)計(jì),用Verilog HDL 語(yǔ)言對(duì)每個(gè)模塊進(jìn)行具體描述,并通過(guò)模塊之間的調(diào)用,基本實(shí)現(xiàn)了I2C的主機(jī)從機(jī)的發(fā)送和接收功能。

2009-06-15 10:44:03 144

144 文章介紹了一種采基于FPGA 實(shí)現(xiàn)UART電路的方法,并對(duì)系統(tǒng)結(jié)構(gòu)進(jìn)行了模塊化分解以適應(yīng)自頂向下的設(shè)計(jì)方法。采用有限狀態(tài)機(jī)對(duì)接收器模塊和發(fā)送器模塊進(jìn)行了設(shè)計(jì),所有功能的

2009-08-15 09:27:55 46

46 UART 是廣泛使用的串行數(shù)據(jù)通訊電路。本設(shè)計(jì)包含UART 發(fā)送器、接收器和波特率發(fā)生器。設(shè)計(jì)應(yīng)用EDA 技術(shù),基于FPGA/CPLD 器件設(shè)計(jì)與實(shí)現(xiàn)UART。關(guān)鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 24

24 本文設(shè)計(jì)了一種基于 FPGA 的UART 核,該核符合串行通信協(xié)議,具有模塊化、兼容性和可配置性,適合于SoC 應(yīng)用。設(shè)計(jì)中使用Verilog HDL 硬件描述語(yǔ)言在Xilinx ISE 環(huán)境下進(jìn)行設(shè)計(jì)、仿真,

2009-11-27 15:48:51 20

20 IO模擬UART實(shí)現(xiàn)

本應(yīng)用用于擴(kuò)展UART端口,在單片機(jī)自帶的UART口不夠用的情況下,使用GPIO和定時(shí)器實(shí)現(xiàn)模擬UART通信。可增加兩個(gè)模擬的UART模塊。

2010-03-26 09:20:40 69

69 UART 發(fā)射/接收簡(jiǎn)介本范例用來(lái)實(shí)現(xiàn)HT46RU66 中UART 的接收功能,HT46RU66 將通過(guò)UART 將接收到的資料在LCD 上顯示出來(lái),如果接收出錯(cuò),還可以顯示錯(cuò)誤狀態(tài)。PA 口外接撥碼開(kāi)關(guān),用

2010-04-08 08:18:24 27

27 文章介紹了一種在現(xiàn)場(chǎng)可編程門陣列(FPGA)上實(shí)現(xiàn)UART 的方法。首先闡述了UART 異步串行通信原理,然后介紹了實(shí)現(xiàn)UART異步串行通信的硬件接口電路及各部分硬件模塊,以及用硬件

2010-08-06 16:24:13 55

55 Name : uart // File Name?? : uart.v// Function??? : Simp

2010-06-05 12:12:03 6550

6550 UART(Universal Asynchronous Receiver Transmitter,通用異步收發(fā)器)是廣泛使用的異步串行數(shù)據(jù)通信協(xié)議。下面首先介紹 UART 硬件接口及電平轉(zhuǎn)換電路,分析UART的傳輸時(shí)序并利用Verilog HDL語(yǔ)言進(jìn)

2011-07-22 11:24:35 113

113 在xo640上實(shí)現(xiàn)一個(gè)簡(jiǎn)單的Uart,能夠解析串口數(shù)據(jù),并在寄存器中存儲(chǔ),用FIFO實(shí)現(xiàn)數(shù)據(jù)的傳遞。那么后期可以通過(guò)開(kāi)發(fā)板上的串口經(jīng)CPLD訪問(wèn)各種數(shù)據(jù)。比如PC=CPLD=EEPROM等等,極大方便后期

2011-08-05 16:54:46 2181

2181 UART 是廣泛使用的串行數(shù)據(jù)通訊電路。本設(shè)計(jì)包含UART 發(fā)送器、接收器和波特率發(fā)生器。設(shè)計(jì)應(yīng)用EDA 技術(shù),基于FPGA/CPLD 器件設(shè)計(jì)與實(shí)現(xiàn)UART。

2011-12-17 00:15:00 59

59 UART 即通用異步收發(fā)器,傳統(tǒng)上采用多功能的專用集成電路實(shí)現(xiàn)。但是在一般的使用中往往不需要完整的UART 的功能,比如對(duì)于多串口的設(shè)備或需要加密通訊的場(chǎng)合使用專用集成電路

2012-05-23 10:13:33 3760

3760

設(shè)計(jì)了一種基于NiosⅡ的UART系統(tǒng),采用軟硬件協(xié)作設(shè)計(jì)的思想調(diào)用了UART核并通過(guò)編譯相關(guān)軟件驅(qū)動(dòng)的方式實(shí)現(xiàn)RS232協(xié)議的通信。首先介紹了UART的協(xié)議原理,然后描述了基本的硬件構(gòu)造和

2012-09-25 14:21:02 45

45 數(shù)字系統(tǒng)設(shè)計(jì):VERILOG實(shí)現(xiàn) (第2版)

2015-11-30 10:21:33 0

0 verilog語(yǔ)言開(kāi)發(fā)的串口模塊程序,測(cè)試可用。

2015-12-25 10:25:19 6

6 關(guān)于fpga和LCD方面的知識(shí),verilog實(shí)現(xiàn)的LCD顯示的設(shè)計(jì)

2016-05-16 18:04:33 47

47 當(dāng)并行數(shù)據(jù)準(zhǔn)備好后,如果得到發(fā)送指令,則將數(shù)據(jù)按UART協(xié)議輸出,先輸出一個(gè)低電平的起始位,然后從低到高輸出8個(gè)數(shù)據(jù)位,接著是可選的奇偶校驗(yàn)位,最后是高電平的停止位; 由于發(fā)送時(shí)鐘clk16x為

2017-02-09 09:48:11 979

979

NiosⅡ的UART設(shè)計(jì)與實(shí)現(xiàn)

2017-10-31 15:09:03 17

17 Verilog HDL是一種硬件描述語(yǔ)言(HDL:Hardware Description Language),以文本形式來(lái)描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式

2017-11-09 17:34:58 8783

8783

Verilog是描述復(fù)雜的硬件電路,設(shè)計(jì)人員總是將復(fù)雜的功能劃分為簡(jiǎn)單的功能,模塊是提供每個(gè)簡(jiǎn)單功能的基本結(jié)構(gòu)。

2017-11-20 16:49:36 5885

5885

使用Verilog描述硬件的基本設(shè)計(jì)單元是模塊(module)。構(gòu)建復(fù)雜的電子電路,主要是通過(guò)模塊的相互連接調(diào)用來(lái)實(shí)現(xiàn)的。模塊被包含在關(guān)鍵字module、endmodule之內(nèi)。實(shí)際的電路元件。Verilog中的模塊類似C語(yǔ)言中的函數(shù)

2017-12-08 17:20:57 11274

11274 和UART優(yōu)缺點(diǎn)的基礎(chǔ),提出了一種基于FPGA采用硬件設(shè)計(jì)HCI-UART的實(shí)現(xiàn)方式。本設(shè)計(jì)在Quartus II 9.0集成設(shè)計(jì)環(huán)境下,采用硬件描述語(yǔ)言Verilog分模塊設(shè)計(jì)完成,設(shè)計(jì)經(jīng)過(guò)Modelsim 6.4a仿真與驗(yàn)證。

2017-12-11 13:22:51 12702

12702

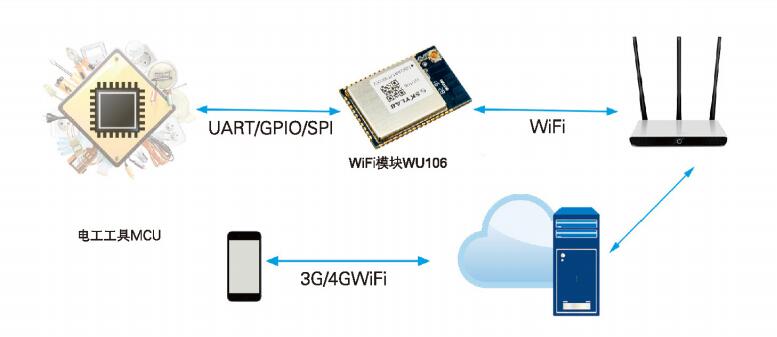

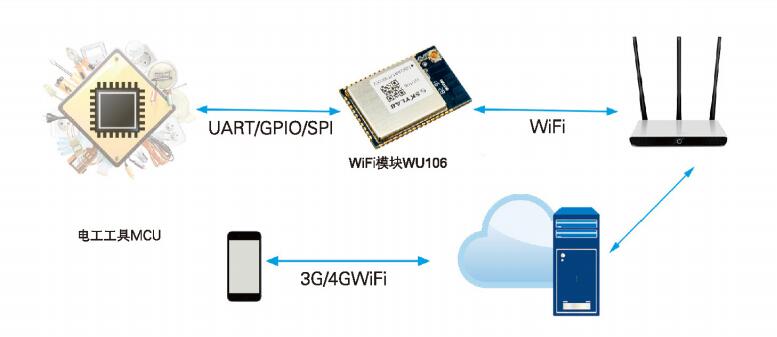

TCP/IP協(xié)議棧,能夠實(shí)現(xiàn)用戶串口或TTL電平數(shù)據(jù)到無(wú)線網(wǎng)絡(luò)之間的轉(zhuǎn)換。通過(guò)UART接口WiFi模塊,傳統(tǒng)的串口設(shè)備也能輕松接入無(wú)線網(wǎng)絡(luò),適合于各類智能家居或智能硬件中,比如現(xiàn)在很多帶WiFi功能的電視

2018-07-30 11:24:50 3834

3834 和IEEE802.11協(xié)議棧,能夠實(shí)現(xiàn)用戶串口到無(wú)線網(wǎng)絡(luò)之間的轉(zhuǎn)換。UART接口WiFi模塊UART接口WiFi模塊是基于UART接口的符合WiFi無(wú)線網(wǎng)絡(luò)標(biāo)準(zhǔn)的嵌入式模塊,內(nèi)置無(wú)線網(wǎng)絡(luò)協(xié)議IEEE802.11

2018-08-09 19:01:00 7679

7679 串口透明數(shù)據(jù)傳輸模式,并且具有多模安全能力。內(nèi)置TCP/IP協(xié)議棧和IEEE802.11協(xié)議棧,能夠實(shí)現(xiàn)用戶串口到無(wú)線網(wǎng)絡(luò)之間的轉(zhuǎn)換。 UART接口WiFi模塊 UART接口WiFi模塊是基于UART

2018-08-13 07:38:01 812

812 實(shí)現(xiàn)RS-232電平和TTL/CMOS電平轉(zhuǎn)換可以用接口芯片來(lái)實(shí)現(xiàn),實(shí)現(xiàn)數(shù)據(jù)的串行到并行轉(zhuǎn)換用的是UART,它們是實(shí)現(xiàn)串行通信必不可少的兩個(gè)部分。雖然目前大部分處理器芯片中都集成了UART,但是一

2019-10-18 07:54:00 3397

3397

本文檔的主要內(nèi)容詳細(xì)介紹的是常用模塊的Verilog HDL設(shè)計(jì)詳細(xì)資料免費(fèi)下載。

2018-10-16 11:12:54 20

20 應(yīng)用設(shè)計(jì),可將用戶的物理設(shè)備連接到WiFi無(wú)線網(wǎng)絡(luò)上,進(jìn)行互聯(lián)網(wǎng)或局域網(wǎng)通信,實(shí)現(xiàn)聯(lián)網(wǎng)功能。UART WiFi+UART藍(lán)牙組合模塊:UART WiFi+UART藍(lán)牙組合模塊WG215是一

2018-12-18 17:19:30 15103

15103 隨著物聯(lián)網(wǎng)智能家居應(yīng)用的日漸豐富,越來(lái)越多的WiFi工程師開(kāi)始更多的關(guān)注UART串口WiFi模塊,為讓新手工程師更快的將UART串口WiFi模塊應(yīng)用于各類智能家居應(yīng)用中,本篇SKYLAB君簡(jiǎn)單為大家

2019-01-14 09:27:02 11633

11633

隨著物聯(lián)網(wǎng)智能家居應(yīng)用的日漸豐富,越來(lái)越多的 WiFi 工程師開(kāi)始更多的關(guān)注 UART 串口 WiFi 模塊,為讓新手工程師更快的將 UART 串口 WiFi 模塊應(yīng)用于各類智能家居應(yīng)用中,本篇 SKYLAB 君簡(jiǎn)單為大家介紹 UART 串口 WiFi 模塊的工作原理及應(yīng)用。

2019-01-08 08:00:00 24

24 接收控制模塊與發(fā)送控制模塊內(nèi)部都有一個(gè)波特率時(shí)鐘產(chǎn)生模塊(BuadRate_set),用于將電路輸入時(shí)鐘(clk)進(jìn)行分頻產(chǎn)生波特率時(shí)鐘,用于接收和發(fā)送數(shù)據(jù)控制。

2019-02-04 11:21:00 4580

4580

Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語(yǔ)言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語(yǔ)言也是一種結(jié)構(gòu)描述的語(yǔ)言。

2019-03-08 14:29:12 13726

13726 UART(UniversalAnynchrONousReceiverTransmitter,通用異步接收發(fā)送器)是廣泛應(yīng)用的串行數(shù)據(jù)傳輸協(xié)議之一,其應(yīng)用范圍遍及計(jì)算機(jī)外設(shè)、工控自動(dòng)化等場(chǎng)合。雖然

2019-09-03 09:01:10 3076

3076

HDL和VHDL的使用比率大概是80%和20%,在中國(guó),大多數(shù)電子行業(yè)企業(yè)都采用Verilog。而模塊化的設(shè)計(jì)讓Verilog HDL語(yǔ)言具有思路清晰、邏輯關(guān)系明確、可讀性強(qiáng)等特點(diǎn),模塊化的設(shè)計(jì)在 Verilog HDL語(yǔ)法設(shè)計(jì)中也成為主流。

2020-03-25 08:00:00 4

4 的UART的實(shí)現(xiàn)方法,具體描述了發(fā)送、接收等模塊的設(shè)計(jì),恰當(dāng)使用了有限狀態(tài)機(jī),實(shí)現(xiàn)了FPGA上的UART的設(shè)計(jì),給出仿真結(jié)果。

2020-07-07 15:51:05 12

12 的實(shí)現(xiàn)方法,具體描述了發(fā)送、接收等模塊的設(shè)計(jì),恰當(dāng)使用了有限狀態(tài)機(jī),實(shí)現(xiàn)了FPGA上的UART的設(shè)計(jì),給出仿真結(jié)果。

2020-07-07 17:28:03 10

10 本文主要介紹verilog基礎(chǔ)模塊,夯實(shí)基礎(chǔ),對(duì)深入學(xué)習(xí)FPGA會(huì)有很大幫助。

2022-02-08 15:04:08 3315

3315

本教程解釋了如何在基于Verilog的設(shè)計(jì)中包含Altera的庫(kù)模塊,這些設(shè)計(jì)是使用Quartus R:II軟件實(shí)現(xiàn)的。

2021-01-22 15:34:12 4

4 UART即通用異步收發(fā)器,傳統(tǒng)上采用多功能的專用集成電路實(shí)現(xiàn)。但是在一般的使用中往往不需要完整的UART的功能,比如對(duì)于多串口的設(shè)備或需要加密通訊的場(chǎng)合使用專用集成電路實(shí)現(xiàn)的UART就不是最合適

2021-04-27 14:07:25 9

9 FPGA邏輯設(shè)計(jì)中通常是一個(gè)大的模塊中包含了一個(gè)或多個(gè)功能子模塊,verilog通過(guò)模塊調(diào)用或稱為模塊實(shí)例化的方式來(lái)實(shí)現(xiàn)這些子模塊與高層模塊的連接,有利于簡(jiǎn)化每一個(gè)模塊的代碼,易于維護(hù)和修改。

2021-04-30 09:30:45 25

25 1、 關(guān)于如何在VHDL模塊調(diào)用一個(gè)Verilog模塊 在VHDL模塊聲明一個(gè)要與調(diào)用的Verilog模塊相同名稱的元件(component),元件的名稱和端口模式應(yīng)與Verilog模塊的名稱和輸入

2021-04-30 14:06:04 11930

11930

的是一個(gè)周期高電平,也可兩個(gè))(無(wú)校驗(yàn)位) 1、prescale是完成一個(gè)bit需要主時(shí)鐘計(jì)數(shù)的次數(shù)(其和主時(shí)鐘以及波特率之間的關(guān)系參考網(wǎng)上文章) 2、進(jìn)入uart模塊的異步信號(hào),最好使用提供的同步器同步 3、異步復(fù)位信號(hào)最好使用提供的同步器同步 4、波特率任

2021-05-27 18:05:00 3057

3057 基于FPGA的UART模塊設(shè)計(jì)與實(shí)現(xiàn)介紹說(shuō)明。

2021-06-01 09:43:30 20

20 夫的。本篇WiFi模塊研發(fā)漲價(jià)SKYLAB君為大家介紹一款能夠簡(jiǎn)化無(wú)線控制方案設(shè)計(jì),縮短智能空調(diào)研發(fā)周期的UART串口WiFi模塊。 UART串口WiFi模塊智能控制原理 WiFi模塊工作STA模式,智能終端(手機(jī)、平板)和WiFi模塊工作在無(wú)線路由器提供的無(wú)線

2021-09-11 16:05:05 2422

2422 Other Parts Discussed in Post: MSP430FR2311作者: TI 工程師 Max Han

簡(jiǎn)介

MSP430FR2311是一款FRAM數(shù)字控制器,可以實(shí)現(xiàn)超低

2022-01-11 10:43:11 2853

2853 一種中斷接收的不等長(zhǎng)不規(guī)則uart數(shù)據(jù)機(jī)制uart接收不規(guī)則的位置長(zhǎng)度或者不固定長(zhǎng)度的數(shù)據(jù)幀時(shí)判斷是否接收完成一幀并可以進(jìn)行處理的機(jī)制demo while(timeOut--

2021-11-16 18:51:02 9

9 連線如下 :這里有幾個(gè)注意點(diǎn):1)PC串口與TMC2225的串口的TX,RX均是直連的,無(wú)需交叉連接。如圖中藍(lán)色、綠色線2)TMC2225的VM引腳也必須同時(shí)加電,否則TMC2225模塊的UART不工作,無(wú)法讀寫(xiě)數(shù)據(jù)TMC2225芯片本身的串口是單線UART。上面圖中的模塊是通過(guò)接入一個(gè)電阻模擬

2021-12-04 16:36:09 52

52 使用查詢方式通過(guò)UART接收數(shù)據(jù)實(shí)驗(yàn)?zāi)康谋竟?jié)實(shí)驗(yàn)?zāi)康臑?b class="flag-6" style="color: red">實(shí)現(xiàn)串口發(fā)送和接收。這一節(jié)計(jì)劃采取查詢的方式來(lái)實(shí)現(xiàn)串口接收,K210串口接收到0x00,則熄滅前節(jié)提到的紅色LED燈,并通過(guò)串口打印Red

2021-12-20 19:37:12 11

11 Uart比較簡(jiǎn)單,所以僅對(duì)tx作比較詳細(xì)的注釋,但里面一些內(nèi)容還是值得新手學(xué)習(xí)的

2022-07-01 17:08:50 2116

2116 UART協(xié)議由三根線組成,Tx,Rx,Gnd即發(fā)送、接收與地,不包含時(shí)鐘線,屬于全雙工異步串行通信協(xié)議。

2022-12-15 12:10:46 1177

1177 UART,即通用異步接收器/發(fā)送器,是最常用的設(shè)備間通信協(xié)議之一,正確配置后,UART可以配合許多不同類型的涉及發(fā)送和接收串行數(shù)據(jù)的串行協(xié)議工作。

2023-02-01 17:54:37 1644

1644 實(shí)現(xiàn)一個(gè)在ARM中通過(guò)APB總線連接的UART模塊(Universal Asynchronous Receiver/Transmitter),包括設(shè)計(jì)與驗(yàn)證兩部分。

2023-06-05 11:48:38 3065

3065

UART接收數(shù)據(jù)部分是接收另一個(gè)串口設(shè)備發(fā)送的數(shù)據(jù),緩存到接收FIFO中。FIFO快要寫(xiě)滿時(shí),產(chǎn)生中斷通知CPU拿取數(shù)據(jù),實(shí)現(xiàn)串口數(shù)據(jù)的接收。

2023-06-05 15:24:28 4827

4827

UART,即通用異步接收器/發(fā)送器,是最常用的設(shè)備間通信協(xié)議之一,正確配置后,UART可以配合許多不同類型的涉及發(fā)送和接收串行數(shù)據(jù)的串行協(xié)議工作。在串行通信中,數(shù)據(jù)通過(guò)單條線路或?qū)Ь€逐位傳輸。在

2023-02-02 10:46:11 3202

3202

超外差接收模塊是一種用于無(wú)線通信領(lǐng)域的接收模塊。它是一種將接收信號(hào)與本地振蕩信號(hào)進(jìn)行混頻處理的接收器。超外差接收模塊的工作原理是將接收到的無(wú)線信號(hào)與本地振蕩器產(chǎn)生的本地振蕩信號(hào)進(jìn)行混頻,得到中頻

2023-08-26 15:25:47 2924

2924

使用UART IDLE中斷接收不定長(zhǎng)數(shù)據(jù)

2023-09-18 15:41:24 2001

2001

在芯片設(shè)計(jì)中,UART(Universal Asynchronous Receiver/Transmitter,通用異步接收/發(fā)送器)模塊是一個(gè)非常重要的外設(shè)模塊。

2023-10-09 14:10:59 2284

2284 第一部分:簡(jiǎn)介 1.1 什么是Verilog模塊? 在Verilog中,模塊是其設(shè)計(jì)層次結(jié)構(gòu)的基本單元。模塊是一個(gè)用于實(shí)現(xiàn)特定功能的單獨(dú)的硬件單元。它可以是一個(gè)組合邏輯電路,也可以是一個(gè)時(shí)序邏輯電路

2024-02-22 15:56:25 8556

8556 在Verilog硬件描述語(yǔ)言中,端口是指連接模塊(Module)與其他模塊、寄存器或是物理設(shè)備的輸入或輸出接口。單向端口可以作為輸入或輸出使用,而雙向端口具有雙重作用,既可以接收輸入信號(hào),又可以輸出

2024-02-23 10:18:54 2549

2549 Verilog是一種硬件描述語(yǔ)言(HDL),廣泛應(yīng)用于數(shù)字電路設(shè)計(jì)和硬件驗(yàn)證。在Verilog中,模塊是構(gòu)建電路的基本單元,而模塊端口對(duì)應(yīng)方式則用于描述模塊之間信號(hào)傳遞的方式。本文將介紹

2024-02-23 10:20:32 3071

3071 以完成各種計(jì)算和控制任務(wù)。本文將詳細(xì)介紹input和output在Verilog中的作用及其使用方式。 一、input的作用及使用方式 作用 在Verilog中,input用于定義模塊的輸入端口。它表示模塊能夠接收外部信號(hào)或者其它模塊輸出的信號(hào)。通過(guò)input端口,模塊可以從外部獲取數(shù)據(jù),并據(jù)此進(jìn)行

2024-02-23 10:29:27 5265

5265

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論