本篇將詳細介紹如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試。SRAM是一種非易失性存儲器,具有高速讀取和寫入的特點。在FPGA中實現SRAM讀寫測試,包括設計SRAM接口模塊

2025-10-22 17:21:38 4118

4118

的面陣CCD驅動時序發生器設計,基于CPLD的面陣CCD驅動時序發生器設計及其硬件實現,基于CPLD的線陣CCD驅動電路的設計,基于CPLD的線陣CCD驅動電路設計與實現,基于CPLD的線陣CCD驅動

2019-06-03 16:45:25

它們的基本設計方法是借助于 EDA 設計軟件,用原理圖、狀態機和硬件描述語言等方法,生成相應的目標文件,最后用編程器或下載電纜,由 CPLD/FPGA 目標器件實現。 生產 CPLD/FPGA

2019-03-04 14:10:13

本人初學CPLD/FPGA,現有一疑問:用verilog寫的一個項目的程序,讀起來類似于C語言那種一條一條執行的指令,這程序燒到CPLD芯片里后是怎么工作的,芯片會自己搭一個門電路出來嗎?

2013-10-01 15:39:47

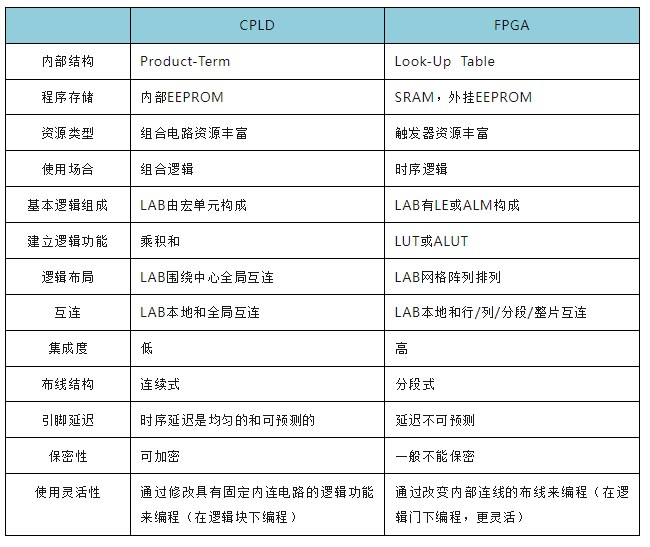

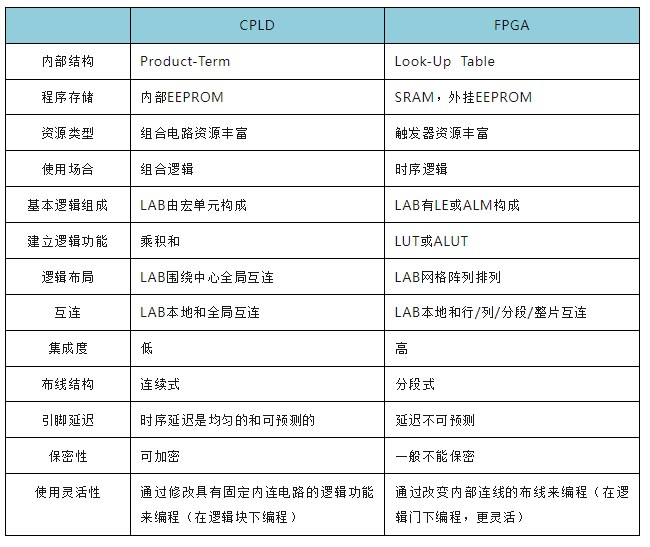

FPGA與CPLD的區別

盡管很多人聽說過CPLD,但是關于CPLD與FPGA之間的區別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復編程的邏輯器件”,但是在技術上卻有一些差異。簡單

2011-09-27 09:49:48

和CPLD最大的區別是他們的存儲結構不一樣,這同時也決定了他們的規模不一樣。但是從使用和實現的角度來看,其實他們所使用的語言以及開發流程的各個步驟幾乎是一致的。對于大多數的初學者來說,學FPGA還是

2019-02-21 06:19:27

器件。內部基本結構為“與或陣列”。因為任意一個組合邏輯都可以用“與—或”表達式來描述,所以該“與—或陣列”結構有利于實現大量的組合邏輯功能。簡單的與或陣列 CPLD邏輯框圖 CPLD和FPGA

2020-08-28 15:41:47

+高級技巧,FPGA高手這樣煉成的FPGA書籍合集:FPGA核心知識詳解與開發技巧FPGA學習指南合集:Verilog HDL那些事兒(建模篇,時序篇,整合篇)Altera FPGA_CPLD

2020-04-24 14:47:56

FPGA入門:Verilog/VHDL語法學習的經驗之談 本文節選自特權同學的圖書《FPGA/CPLD邊練邊學——快速入門Verilog/VHDL》書中代碼請訪問網盤:http

2015-01-29 09:20:41

用“與—或”表達式來描述,所以該“與或陣列”結構能實現大量的組合邏輯功能) 簡單的“與或”陣列:(PAL、GAL、CPLD) 含查找表的邏輯單元:(FPGA) CPLD和FPGA的主要

2020-07-16 10:46:21

配置文件,接著完成下載并進行板級調試驗證。圖5.16 FPGA/CPLD設計簡易流程 本文節選自特權同學的圖書《FPGA/CPLD邊練邊學——快速入門Verilog/VHDL》書中代碼請訪問網盤:http://pan.baidu.com/s/1bndF0bt Xilinx FPGA入門連載

2019-01-28 02:29:05

和CPLD最大的區別是他們的存儲結構不一樣,這同時也決定了他們的規模不一樣。但是從使用和實現的角度來看,其實他們所使用的語言以及開發流程的各個步驟幾乎是一致的。對于大多數的初學者來說,學FPGA還是

2015-03-12 13:54:42

ASIC芯片的建模與設計 基于VHDL或Verilog的USB接口模塊的建模與設計 基于Verilog的MCU嵌入式內核的建模與設計 用VHDL實現搶答器設計 基于PC機串口FPGA配置

2012-02-10 10:40:31

、Actel等。FPGA可以用于實現各種接口,實現各種狀態控制以及數字處理任務。與CPLD比較,FPGA 使用了SRAM 工藝,而CPLD FASTFLASH 工藝;FPGA適合時序邏輯、CPLD更適合

2017-10-24 14:59:23

特權同學的《FPGA/CPLD邊學邊練---快速入門Verilog/VHDL》中的UART串口收發實驗發送數據和接收的數據不一致。在每個有效數據的后面都會多兩個數據。比如發送的有效數據是:FF。則

2017-11-30 09:25:44

用vhdl實現cpld配置fpga,配置成功后在usermode下設置一個重新配置信號,當信號有效時對fpga進行重新配置;fpga配置程序放在flash內;現在遇到的問題是,上電cpld能夠正常配置fpga并且進入usermode ,但是加上重新配置語句過后就不能成功配置fpga,求高人指點~

2013-01-17 22:35:39

verilog寫cpld的程序如何消除按鍵的抖動?

2014-04-02 09:22:03

Altera FPGA/CPLD設計與Verilog數字系統設計教程從網上找到了一些Altera FPGA/CPLD經典教材,包含夏宇聞老師的Verilog數字系統設計教程(第2版)Altera FPGA/CPLD設計與Verilog數字系統設計教程

2014-02-17 09:22:18

立題簡介:內容:MCU+CPLD/FPGA實現GPIO擴展與控制;來源:實際得出;作用:MCU+CPLD/FPGA實現GPIO擴展與控制;仿真環境:Quartus II 11.0;日期

2021-11-04 07:42:16

cpld\fpga\verilog hdl視頻教程入門篇:第1講、FPGA設計基礎(PDF、視頻)第2講、FPGA設計入門(視頻、課后習題)第3講、VerilogHDL

2009-03-26 16:37:40

教程目錄: 入門篇:第1講、FPGA設計基礎(PDF、視頻)第2講、FPGA設計入門(視頻、課后習題)第3講、VerilogHDL基礎(PDF、視頻、課后習題)第4講:Verilog HDL中的組合

2009-03-09 22:56:25

AHB總線交互。

在開發時,MCU部分使用VScode搭建開發環境(我們提供所有安裝包);CPLD/FPGA使用Quartus開發(兼容Altera,代碼可以直接參考Quartus所編寫的Verilog

2024-10-04 21:50:19

學會CPLD的系統設計技術。本書以ALTERA公司的系列芯片為目標載體,簡要分析了可編程邏輯器件的結構和特點,以及相應開發軟件的使用方法,同時,還用大量篇幅介紹了初學者最容易掌握的Verilog

2018-03-30 15:07:50

使用Verilog實現基于FPGA的SDRAM控制器

2012-08-20 19:35:27

如何利用FPGA實現UART的設計?UART的結構和幀格式

2021-04-08 06:32:05

本文介紹了通過處理機用CPLD和Flash實現FPGA配置文件下載更新的方法。

2021-04-28 06:11:19

本文應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2021-05-07 06:33:09

正在學習FPGA,有幾點疑惑,請版上的各位網友指教: 1. FPGA與CPLD究竟有哪些區別?我用verilog寫的程序,燒到CPLD和FPGA上都可以實現功能,那么實際應用的時候,這兩者有什么區別

2013-07-22 10:01:08

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

在下新手,最近在用CPLD實現一個數據采集系統,Verilog模塊已經在Modulesim里面仿真過,下線仿真沒有任何問題,但是將程序下載到CPLD中功能不實現,之前了解到FPGA可以用

2017-03-31 09:35:33

發燒友們好,我正在開始學習fpga的知識,現在尋求一個基于verilog的uart程序,要求是初始位一位,終止位一位,數據位8位,實現回環功能。大家能幫助一下我嗎?

2020-05-10 22:53:19

),有時我們不需要使用完整的UART的功能和這些輔助功能。或者設計上用到了FPGA/CPLD器件,那么我們就可以將所需要的UART功能集成到FPGA內部。使用VHDL將UART的核心功能集成,從而使整個設計更加緊湊、穩定且可靠。本文應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2012-05-23 19:37:24

《Altera FPGA/CPLD設計(高級篇)》結合作者多年工作經驗,深入地討論了Altera FPGA/CPLD的設計、優化技巧。在討論FPGA/CPLD設計指導原則的基礎上,介紹了Altera器件的高級應用;引領讀者

2009-02-12 09:19:12 4807

4807 altera fpga/cpld設計 基礎篇結合作者多年工作經驗,系統地介紹了FPGA/CPLD的基本設計方法。在介紹FPGA/CPLD概念的基礎上,介紹了Altera主流FPGA/CPLD的結構與特點,并通過豐富的實例講解

2009-07-10 17:35:45 58

58 文章介紹了一種在現場可編程門陣列(FPGA)上實現UART 的方法。UART 的波特率可設置調整,工作狀態可讀取。系統結構進行了模塊化分解,使之適應自頂向下(Top-Down)的設計

2009-08-21 11:35:03 52

52 UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。關鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 24

24 基于單片機的CPLD/FPGA被動串行下載配置的實現:介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現CPLD/FPGA器件的被動串行模式的下載配置,闡述了其原理及軟硬件設計。 &nb

2009-10-29 21:57:22 19

19 本文設計了一種基于 FPGA 的UART 核,該核符合串行通信協議,具有模塊化、兼容性和可配置性,適合于SoC 應用。設計中使用Verilog HDL 硬件描述語言在Xilinx ISE 環境下進行設計、仿真,

2009-11-27 15:48:51 20

20 從零開始學CPLD和Verilog HDL編程技術

CPLD(Complex Programmable Logic Device)復雜可編程邏輯器件,是從PAL和GAL器件發展出來的器件,相對而言規模大,結構復雜,屬于大規

2010-03-16 15:42:39 132

132 利用 FPGA 實現UART 的設計引 言隨著計算機技術的發展和廣泛應用,尤其是在工業控制領域的應用越來越廣泛,計算機通信顯的尤為重要。串行通信雖然使設備之間的連線大為減

2010-03-24 09:23:40 49

49 文章介紹了一種在現場可編程門陣列(FPGA)上實現UART 的方法。首先闡述了UART 異步串行通信原理,然后介紹了實現UART異步串行通信的硬件接口電路及各部分硬件模塊,以及用硬件

2010-08-06 16:24:13 55

55 摘 要:通過設計實例詳細介紹了用Verilog HDL語言開發FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優越性。

2009-06-20 11:51:28 2331

2331

摘 要 :UART是廣泛使用的串行數據通訊電路。本設計包含UART發送器、接收器和波特率發生器。設計應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2009-06-20 13:14:52 1267

1267

基于CPLD/FPGA的多功能分頻器的設計與實現

引言

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求

2009-11-23 10:39:48 1599

1599

基于FPGA和CPLD數字邏輯實現ADC技術

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現

2010-05-25 09:39:10 1844

1844

本文討論的四種常用FPGA/CPLD設計思想與技巧:乒乓操作、串并轉換、流水線操作、數據接口同步化,都是FPGA/CPLD邏輯設計的內在規律的

2010-11-04 10:11:28 813

813

本文介紹了通過處理機用CPLD和Flash實現FPGA配置文件下載更新的方法。與傳統的JTAG或PROM串行下載配置方法相比,此方法具有更新配置文件靈活方便、易于操作、適用于大容量FPGA下載的特點

2018-10-25 05:51:00 10535

10535

在我國使用Verilog HDL的公司比使用VHDL的公司多。從EDA技術的發展上看,已出現用于CPLD/FPGA設計的硬件C語言編譯軟件,雖然還不成熟,應用極少,但它有可能會成為繼VHDL和Verilog之后,設計大規模CPLD/FPGA的又一種手段。

2011-03-12 11:21:20 2003

2003 本站提供的fpga實現jpeg Verilog源代碼資料,希望能夠幫你的學習。

2011-05-27 15:09:53 203

203 UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。

2011-12-17 00:15:00 59

59 verilog語言開發的串口模塊程序,測試可用。

2015-12-25 10:25:19 6

6 FPGA和CPLD的區別,以及設計思路思想

2016-02-17 11:20:56 39

39 SVPWM算法優化及其FPGA_CPLD實現

2016-04-13 15:42:35 18

18 關于fpga和LCD方面的知識,verilog實現的LCD顯示的設計

2016-05-16 18:04:33 47

47 Xilinx FPGA工程例子源碼:在FPGACPLD中實現AD或DA的文章(英文Verilog)

2016-06-07 15:07:45 18

18 用 Verilog實現基于FPGA 的通用分頻器的設計時鐘分頻包括奇數和偶數分頻

2016-07-14 11:32:47 46

46 在CPLD中用UART邏輯實現高速異步串行通信

2017-01-24 16:54:24 12

12 基于FPGA/CPLD的UART功能設計

2017-01-23 20:45:37 31

31 FPGA verilog 相關設計實踐

2017-09-06 11:19:34 34

34 CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

2017-09-18 16:35:32 5

5 FPGA/CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。 FPGA/CPLD如同一張白紙或是一堆積木,工程師可以通過傳統的原理圖輸入法

2017-10-09 09:52:20 14

14 FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域

2017-10-24 10:04:00 48952

48952 數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2018-04-26 11:53:00 1765

1765

FPGA LAB和CPLD的LAB設計不同。CPLD LAB由宏單元構成,包括自己的本地可編程陣列,而FPGA LAB由大量的邏輯模塊構成,這些模塊被稱為邏輯單元,即LE,而且本地互連和邏輯分開。LE看起來可能和CPLD宏單元相似,但更容易配置,有更豐富的特性來提高性能,減少邏輯資源的浪費。

2018-04-17 17:02:00 2494

2494

CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

2018-05-24 02:03:00 50934

50934

FPGA芯片卻沒有這個特點,所以使用FPGA作為處理器可以有兩個選擇,第一個選擇是使用UART芯片進行串并轉換,第二個選擇是在FPGA內部實現UART功能。

2019-10-18 07:54:00 3397

3397

CPLD通常用于實現前面提到的簡單組合邏輯功能,并負責“引導”FPGA以及控制整個電路板的復位和引導順序。

2018-09-27 11:56:01 7180

7180 介紹了采用CPLD和Flash器件對FPGA 實現快速并行配置,并給出了具體的硬件電路設計和關鍵模塊的內部編程思路。

2018-10-24 15:15:49 9

9 本文檔的主要內容詳細介紹的是如何使用Verilog-HDL做CPLD設計的時序邏輯電路的實現。

2018-12-12 16:25:46 11

11 本文檔詳細介紹的是FPGA教程之CPLD與FPGA的基礎知識說明主要內容包括了:一、復雜可編程邏輯器件簡介二、CPLD的組成與特點三、FPGA的組成與特點四、CPLD與FPGA的異同五、主要的PLD廠商

2019-02-27 17:09:32 40

40 對于CPLD/FPGA初學者而言,如何實現雙向信號往往是個難題。duoduo 當年初接觸CPLD/FPGA的時候也為這個問題頭疼過。讓我們透過下面這個簡單的例子看看CPLD/FPGA設計中如何實現雙向信號。

2019-06-11 16:13:51 15

15 FPGA/CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。

2020-01-20 09:29:00 4186

4186 的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA上的UART的設計,給出仿真結果。

2020-07-07 17:28:03 10

10 本文主要介紹CPLD和FPGA的基本結構。 CPLD是復雜可編程邏輯器件(Complex Programable Logic Device)的簡稱,FPGA是現場可編程門陣列(Field

2020-09-25 14:56:33 14416

14416

可編程邏輯器件rPGA(現場可編程門陣列)和CPLD(復雜可編程邏輯器件)越來越多的應用于數字信號處理領域,與傳統的ASIC(專用集成電路和DSP數字信號處理器)相比,基于FPGA和CPLD實現

2021-02-01 10:33:06 19

19 CPLD/FPGA的基本知識講解。

2021-03-30 09:55:18 34

34 的。本設計使用Xilinx的FPGA器件,只將UART的核心功能嵌入到FPGA內部,不但實現了電路的異步通訊的主要功能,而且使電路更加緊湊、穩定、可靠。

2021-04-27 14:07:25 9

9 基于FPGA的UART模塊設計與實現介紹說明。

2021-06-01 09:43:30 20

20 基于FPGA的簡易頻譜儀設計與實現

2021-06-16 10:01:36 67

67 FPGA設計中DAC控制的Verilog實現圖文稿(ltspice 放置電源)-該文檔為FPGA設計中DAC控制的Verilog實現圖文稿資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 12:17:02 10

10 FPGA設計中DAC控制的Verilog實現(單片機電源維修)-該文檔為FPGA設計中DAC控制的Verilog實現資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 12:18:48 18

18 FPGA設計中DAC控制的Verilog實現修訂稿(空調電源芯片)-該文檔為FPGA設計中DAC控制的Verilog實現修訂稿資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 13:13:56 10

10 ADC0809驅動FPGA實現的verilog程序(通訊電源技術雜志封面)-該文檔為ADC0809驅動FPGA實現的verilog程序總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-08-31 18:33:38 68

68 Altera FPGA CPLD學習筆記(肇慶理士電源技術有限)-Altera FPGA CPLD學習筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 85

85 FPGA CPLD數字電路設計經驗分享.(電源技術發展怎么樣)-FPGA CPLD數字電路設計經驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 52

52 FPGA CPLD中的Verilog設計小技巧(肇慶理士電源技術有限)-FPGA CPLD中的Verilog設計小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 37

37 的完整 Verilog 代碼 。 在這個FPGA Verilog項目中,一些簡單的處理操作都是在Verilog中實現的,比如反相、亮度控制和閾值操作。圖像處理操作由“parameter.v”文件選擇

2021-09-23 15:50:21 7240

7240 立題簡介:內容:MCU+CPLD/FPGA實現GPIO擴展與控制;來源:實際得出;作用:MCU+CPLD/FPGA實現GPIO擴展與控制;仿真環境:Quartus II 11.0;日期

2021-10-29 10:21:11 2

2 都是FPGA/CPLD邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA/CPLD設計工作種取得事半功倍的效果。

2023-05-18 08:56:57 1007

1007

FPGA需要良好的數電模電基礎,verilog需要良好C語言基礎。

2023-05-22 15:04:29 1434

1434

CPLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。

2023-06-28 11:28:04 2009

2009

可編程邏輯包括 PAL、GAL、PLD 等。通過不斷發展,它已經發展成為現在的CPLD/FPGA。CPLD(復雜可編程邏輯器件)和FPGA(現場可編程門陣列)的功能基本相同,只是實現原理略有不同。當

2023-07-03 14:33:38 10709

10709

FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)都屬于可編程邏輯器件(PLD

2024-01-22 18:05:54 4320

4320 CPLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。CPLD的LAB圍繞中心全局互連排列,隨著器件中邏輯數量的增加,呈指數

2024-01-23 09:17:04 2281

2281 在數字電路設計領域,CPLD和FPGA是兩種常用的可編程邏輯器件。它們都允許工程師根據需要設計和重新配置數字電路,但它們在結構、性能和應用上存在顯著差異。 CPLD和FPGA的定義 CPLD

2025-01-23 09:46:36 2762

2762

電子發燒友App

電子發燒友App

評論