在Linux驅動中,操作時鐘只需要簡單調用內核提供的通用接口即可,clock驅動通常是由芯片廠商開發的,在Linux啟動時clock驅動就已經初始化完成。

2023-05-31 16:10:23 1416

1416

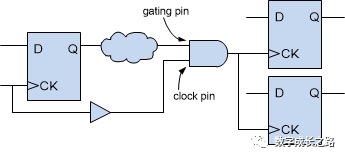

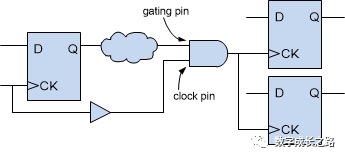

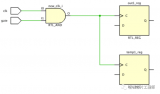

ICG(integrated latch clock gate)就是一個gating時鐘的模塊,通過使能信號能夠關閉時鐘。

2023-09-11 12:24:48 3870

3870

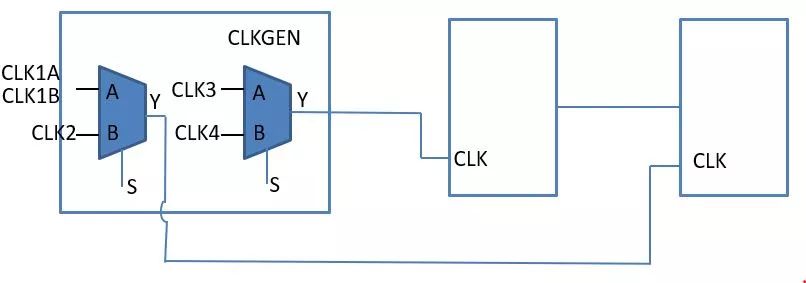

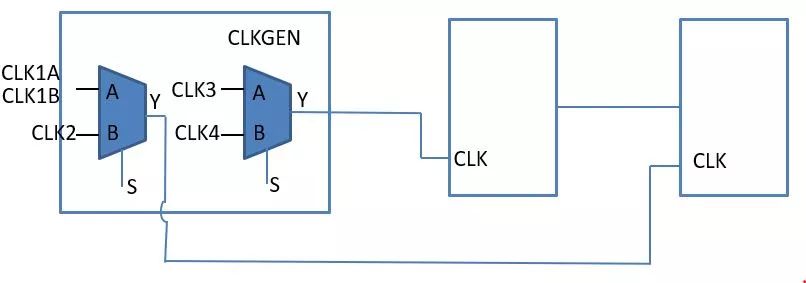

Clock 時鐘就是 SoC 中的脈搏,由它來控制各個部件按各自的節奏跳動。比如,CPU主頻設置,串口的波特率設置,I2S的采樣率設置,I2C的速率設置等等。這些不同的clock設置,都需要從某個或某幾個時鐘源頭而來,最終開枝散葉,形成一棵時鐘樹。

2023-11-29 09:53:57 2033

2033

在時序報告中,會顯示出clock path skew,如果時鐘偏移超過0.5ns,就需要額外關注了。

2024-03-13 09:06:20 3008

3008

` Vivado工具在編譯時通常會自動識別設計中的時鐘網絡,并將其分配到專用的時鐘布局布線資源中。通過對某些時鐘網絡設置CLOCK_DEDICATED_ROUTE值為FALSE,可以將被識別

2020-09-15 13:30:49

CLOCK_DRV_Init 與 Clock_Ip_InitClock 之間的區別哪個更適合非 autosar 應用程序。

2023-04-19 07:21:13

clock信號上并聯電容的作用,機理是什么,在信號的影響是什么

2013-09-05 22:03:22

clock如何配置?怎么使用?

2022-01-26 07:30:43

程序如下:當定時配置按照如下配置TIClockParams.period = 0; TIClockParams.startFlag = FALSE; Clock_construct(&

2020-03-26 07:25:50

有小伙伴知道,HDMI那塊的Clock如何配置嗎??有什么文檔說明嗎?

2024-01-10 07:51:12

1. Clock時鐘組件的基本使用組件說明:Text的子類,所以可以使用Text的一些屬性。常用屬性: 常見方法: 基本用法:xml 文件布局: 默認把當前時間作為一個展示,而且時間是不斷走動

2021-09-06 15:52:23

Multiple Clock System Design Look Step by StepPossible Assign Option–Tpd?? NO! NO! Tpdcan

2008-09-11 09:20:30

The PLL reference clock ofdoes not match the clock frequency input to refclk解決方法這是sopc版本問題,核沒問題

2015-04-02 11:34:42

SysBios 關于clock有這么一段描述:

The Clock module lets you create Clock object instances, which reference

2018-06-19 00:31:30

我按照官網提供的SPI例程,先初始化Module,然后在Channel初始化時,將SPI模式配置為3(clock polarity = 1;clock phase=1)。但是此時CLK的狀態仍然為

2024-02-18 07:09:54

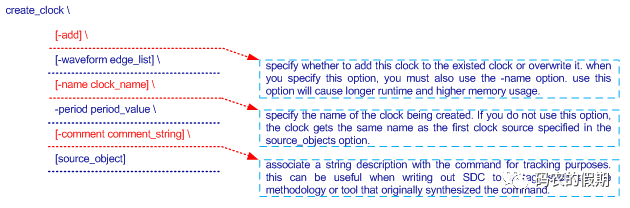

創建一個時鐘:create_clock -period 9.920 -name IncomingClk [get_ports InClk]然后嘗試使用以下命令創建生成的時鐘

2018-11-05 11:32:59

1,在一個verilog程序里,如果循環是一個循環次數不可定的循環,那么它能被綜合工具綜合嗎2,如果程序里有always @(clock)里面又嵌套了@(clock)這樣的控制事件,這個能被綜合嗎

2015-02-03 15:29:11

同步博客地址:從STM32開始的RoboMaster生活:進階篇 V [Clock Tree]項目&教程倉庫:-STM32-RoboMaster-1.0 什么是Clock Tree?1.1

2021-08-11 08:41:57

下問題:上面說我的AO所在的時鐘域不支持,支持的時鐘域是在Data Clock 2x. 而我項目里頂層時鐘設置的是200MHZ, loop timer 我設置的是1 tick. Data Clock 2x

2017-02-09 01:33:31

如圖所示,在TC397的ASCLIN SPI Master Timing表格中,控制器所需要的最小setup time大于最小clock period,這是不滿足時序要求的,請問datasheet是否有誤?

2024-01-29 08:00:24

原子的第一個例程流水燈中用了 Stm32_Clock_Init()函數,現在來解析一下:引用時Stm32_Clock_Init(9);定義(此處省略了跑OS時的代碼)看程序前,請確保理解了這個時鐘樹

2021-08-09 08:29:52

求助大神,clock skew太大,導致時序違規怎么破?時鐘由DCM輸出,已經過BUFG

2016-01-14 17:00:12

分別在CCS 軟仿6678和6678EVM板子上跑程序,用clock計數,板子上選的是CPU EXECUTE CYCLES,軟仿時候選的是CYCLE.CPU,得出的結果卻是軟仿比板子上跑的時鐘數要少

2018-08-07 06:51:00

我用CLOCK()函數去測試FFT時間,但是測試的結果不對。 CLOCK() 是要使能嗎? 那在我的代碼里面我需要怎么做呢? CLOCK()函數返回的是DSP運行的時鐘周期數嗎?

2018-07-24 10:24:14

_Params_init(&clkParams); clkParams.period = 5; clkParams.startFlag = false; gs_clk = Clock

2019-01-24 06:43:04

1 配置RCCHigh Speed Clock(HSE)選擇第三項(即外部時鐘源)2 配置SYSDebug選擇第二項Serial Wire3 設置時鐘切換到Clock Configuration,按

2021-08-10 06:25:36

The ICS557-01 is a clock chip designed for use inPCI-Express Cards as a clock source. It provides a

2008-04-01 15:14:40 19

19 DS108x Spread-spectrum clock modulators reduce peak EMI

Pin-selectable dither rate and magnitude

2008-07-25 01:26:06 10

10 The RoboClock® family of low skew clock buffers includes sixproducts listed in Table 1.

2009-05-26 14:34:08 14

14 The AD807 provides the receiver functions of data quantization,signal level detect, clock recovery

2009-09-15 08:24:25 12

12 The ADN2815 provides the receiver functions of quantization and clock and data recovery

2009-09-15 08:40:06 18

18 The AD9520-51 provides a multioutput clock distribution function with subpicosecond jitter

2009-09-15 14:28:34 17

17 The AD9522-51 provides a multioutput clock distribution function with subpicosecond jitter

2009-09-15 14:39:15 12

12 continuous�data�ow embedded systems� This paper describes the design of aglobal clock sub�system which is an essential component of

2009-11-30 11:37:35 9

9 of the decoded outputs is normally low and sequentially goes high on the low to high transition clock period of the 10 clock period cy

2010-08-10 17:06:58 15

15 PCIe Clock Buffer :

PI6C20800: 1:8 PCIe 100 MHz DifferentialHCSL Clock Buffer View Datasheet |

2008-04-01 14:59:10 3336

3336

Determining Clock Accuracy Requirements for UART Communications

Abstract: This applicati

2009-03-31 22:17:06 1199

1199

an extremely clean clock signal to make sure an external clock source does not contribute undesired noise to the overal dynamic performance of

2009-04-16 16:34:23 1775

1775

Abstract: This application note discusses how to realize gapped clock applications with the DS31256

2009-04-18 11:32:20 1260

1260

This application note describes how the device recovers the low-speed clock signals from the high-speed multiplexed signal for the three modes of operat

2009-04-18 11:56:08 878

878

Abstract: The DS3112 has six different transmit clock and six different receive clock types

2009-04-20 09:51:19 877

877

Abstract: Application Note 354 provides a logical diagram of the clock map of the Dallas

2009-04-20 10:21:38 1027

1027

" of phased signals such as data and clock signals. Skew can be caused by signal delays in the signal path or inherent incompatibilities between s

2009-04-22 11:21:13 1518

1518

Real Time Clock Compensation This document describes how to use software to compensate the real

2011-02-06 10:30:26 30

30 The AD9557 is a low loop bandwidth clock multiplier that provides jitter cleanup

2011-10-29 17:10:44 31

31 The AD9577 provides a multioutput clock generator function along with two on-chip phase-locked loop

2011-10-29 17:14:27 21

21 【好程序系列】Proteus在MCS&ARM中的應用之99s Clock

2016-01-20 15:19:31 9

9 FPGA_Alarm_Clock,好東西,喜歡的朋友可以下載來學習。

2016-02-22 14:46:39 0

0 ICS307 Clock Generator。

2016-03-23 10:41:29 0

0 51黑論壇_12864LCD-clock

2017-03-01 13:17:47 2

2 如果時鐘同時驅動I/O和Slice中的邏輯資源,且負載小于2000時,可通過CLOCK_LOW_FANOUT屬性對相應的時鐘net進行設置,最終可使工具將該時鐘驅動的所有負載放置在同一個時鐘域內。通過命令report_clock_utilization生成的報告可查看每個時鐘的負載,如下圖所示。

2018-11-07 11:08:44 5450

5450

Discrete Jitter是由MMCM/PLL引入的,其具體數值可通過點擊圖2中Clock Uncertainty的數值查看,如圖5所示。通常,VCO的頻率越高,引入

2018-11-12 14:40:00 6147

6147 clock source用于為linux內核提供一個時間基線,如果你用linux的date命令獲取當前時間,內核會讀取當前的clock source,轉換并返回合適的時間單位給用戶空間。

2019-05-10 14:36:12 2400

2400 Collapse可以將Sink,ICG,Buffer等cell不展開顯示,只以一個簡單數字和虛線表示連接關系,下圖藍圈表示該buffer驅動了100個clock sink

2020-05-19 16:20:07 13516

13516

Clock shew是數字集成電路設計中一個重要的因素。本文比較了在同步電路設計中0clock shew和非0clock shew時鐘分布對電路性能的影響,分析了通過調整時鐘樹中CLOCK SKEW

2021-01-14 16:26:52 21

21 AD9518-2: 6-Output Clock Generator with Integrated 2.2 GHz VCO Data Sheet

2021-01-28 02:45:41 0

0 AD9514: 1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Three Output Data Sheet

2021-01-28 09:58:09 8

8 AD9513: 800 MHz Clock Distribution IC, Dividers, Delay Adjust, Three Outputs Data Sheet

2021-01-28 10:00:10 9

9 AD9511: 1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs Data Sheet

2021-01-28 10:06:10 3

3 AD9540:?655 MHz Low Jitter Clock Generator Data Sheet

2021-01-28 15:37:31 6

6 AD9546: Dual DPLL Digitized Clock Synchronizer Data Sheet

2021-01-28 16:38:35 4

4 AD9574:以太網/Gigabit Ethernet Clock數據Sheet

2021-05-12 18:41:46 4

4 View the reference design for AN_Clock_Optimization. http://www.3532n.com/soft/ has thousands of reference designs to help bring your project to life.

2021-07-09 09:39:27 0

0 51單片機——My-Clock項目

2021-11-23 16:51:36 13

13 電子發燒友網站提供《Gowin時鐘資源(Clock)用戶指南.pdf》資料免費下載

2022-09-14 14:23:46 0

0 電子發燒友網站提供《Gowin I3C Dual Clock IP用戶指南.pdf》資料免費下載

2022-09-15 15:29:20 0

0 電子發燒友網站提供《Gowin I3C Single Clock IP用戶指南.pdf》資料免費下載

2022-09-15 15:28:20 0

0 電子發燒友網站提供《Logos系列FPGA時鐘資源(Clock)用戶指南.pdf》資料免費下載

2022-09-26 10:15:21 11

11 電子發燒友網站提供《Compact系列CPLD時鐘資源(Clock/PLL)用戶指南 .pdf》資料免費下載

2022-09-26 10:03:33 7

7 異或邏輯中:clock unate的極性跟另一個input有關,是一個non-unate的信號。pulse generator的輸出不是unate。

2022-12-20 14:19:49 7445

7445 SYSREF和Device Clock需要同源。而且標準中推薦,SYSREF和Device clock都采用同樣的電平類型,以防止在芯片內部產生額外的偏差。

2022-12-30 11:03:59 5509

5509 PTP Clock Manager for Linux Message Log 手冊

2023-01-30 18:55:46 0

0 P_數據表(A-5):Analog-PLL For Spread Spectrum Clock

2023-03-16 19:27:31 0

0 FPGA中的Bank和Clock Region有什么關系?

2023-05-15 09:32:34 1963

1963

對于發送時鐘和接收時鐘是同一時鐘的單周期路徑,時鐘抖動對建立時間有負面影響,但對保持時間沒有影響。

2023-06-12 09:15:48 1128

1128

電子發燒友網站提供《IoT ONE Nixie Clock Arduino Cloud背光控制.zip》資料免費下載

2023-06-14 14:33:38 0

0 Period檢查? 在.lib中,觸發器、latch、Memory這些時序期間的clock input pin上會定義min_period屬性來規定它上面時鐘的最小周期(也就是最高頻率),例如: pin

2023-06-17 14:16:13 3546

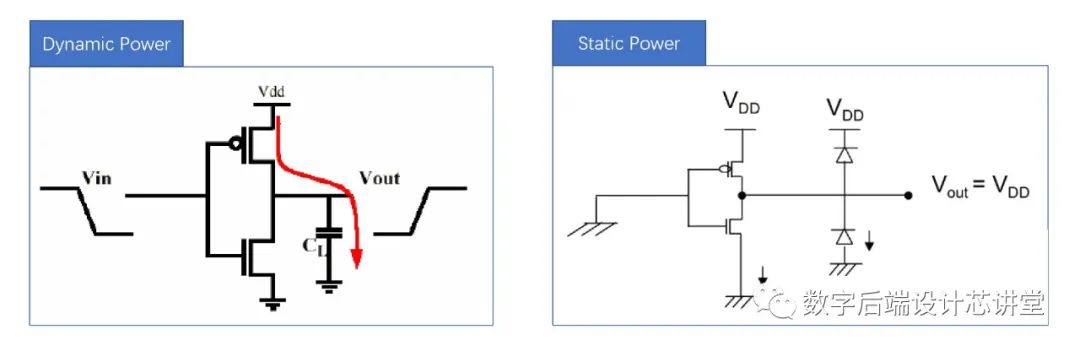

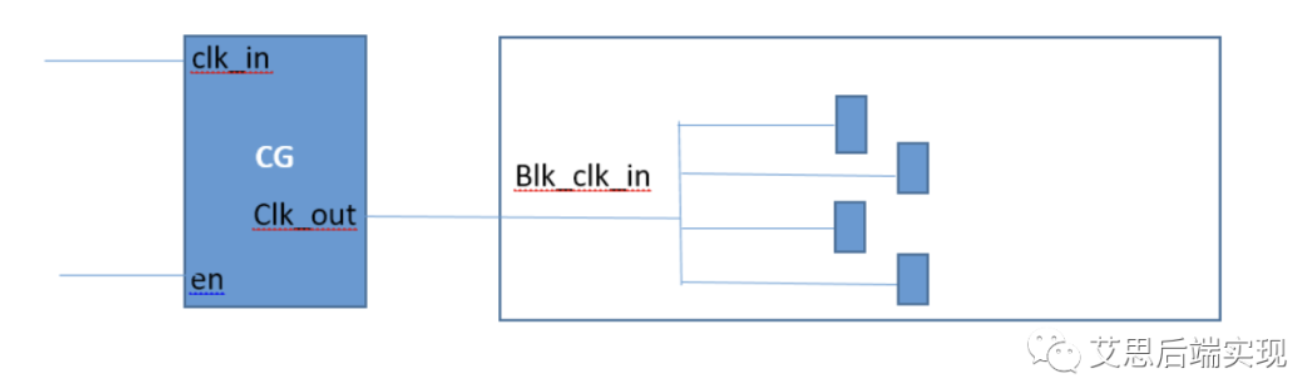

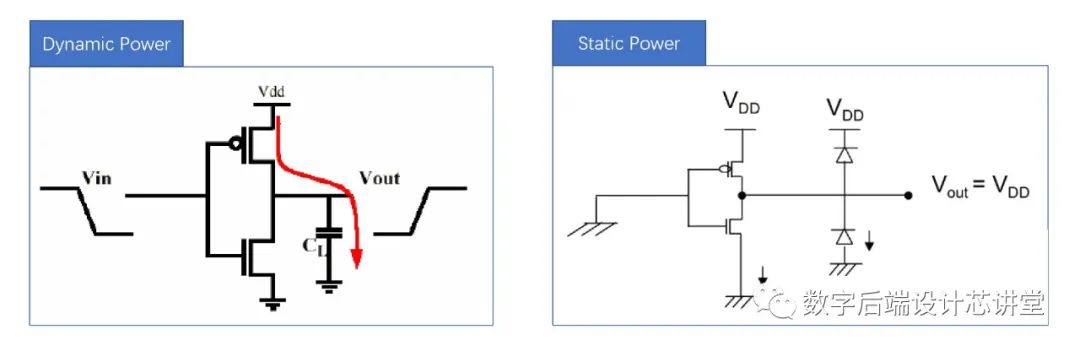

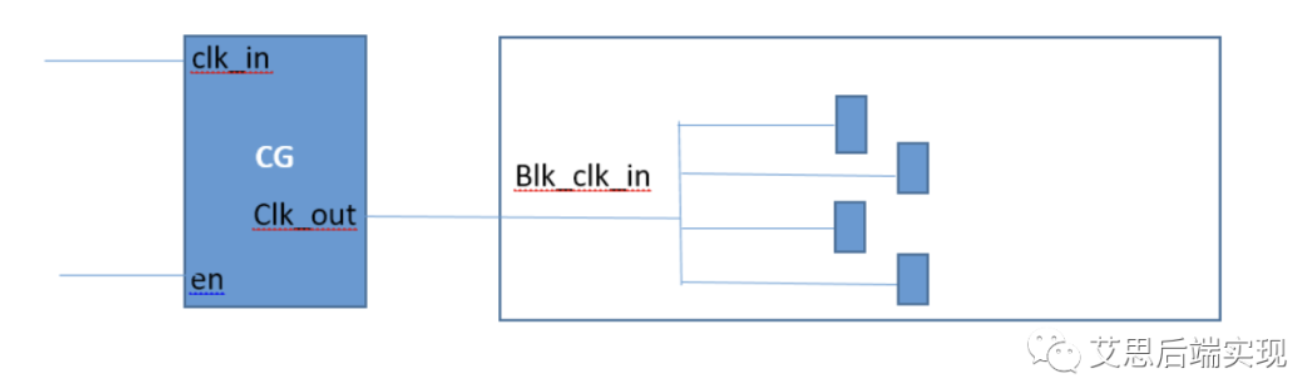

3546 大多數低功耗設計手法在嚴格意義上說并不是由后端控制的,Clock Gating也不例外。

2023-06-27 15:47:35 2632

2632

一個cell的一個輸入為clock信號,另一個輸入為gating信號,并且輸出作為clock使用,這樣的cell為gating cell。

2023-06-29 15:28:34 5065

5065

今天我們要介紹的時序分析基本概念是 **clock group,簡稱時鐘組。** 定義完時鐘后,我們也需要通過設置clock group來確認各個時鐘之間的關系。

2023-07-03 14:37:27 2841

2841

今天我們要介紹的時序分析概念是clock gate。 clock gate cell是用data signal控制clock信號的cell,它被頻繁地用在多周期的時鐘path,可以節省功耗。

2023-07-03 15:06:03 4536

4536

PTP Clock Manager for Linux Message Log 手冊

2023-07-03 20:29:28 2

2 今天我們要介紹的時序分析概念是generate clock。中文名為生成時鐘。generate clock定義在sdc中,是一個重要的時鐘概念。

2023-07-06 10:34:18 3660

3660

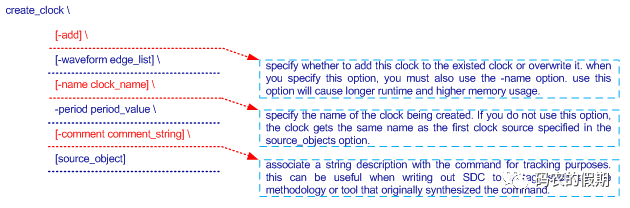

Clock分為兩大類,一類是root clock,其定義指令是create_clock;另外一類是generated clock,其定義指令是create_generated_clock。

2023-07-06 15:31:22 4840

4840

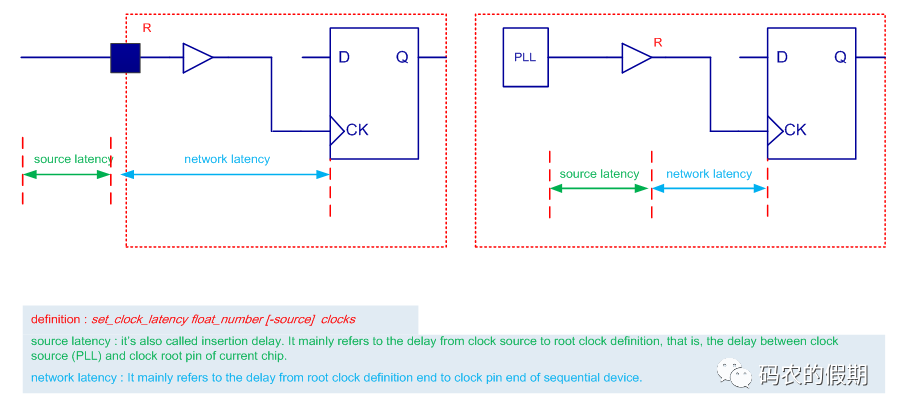

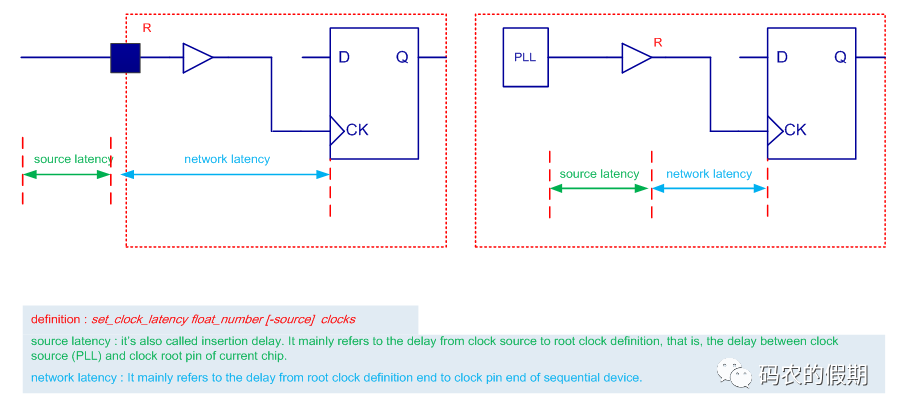

要探討今天的主題,首先需要跟大家一起學習下clock latency這個基本概念。Clock latency通俗意義上是指clock定義點到clock sink point(時序器件的clock

2023-07-06 15:34:44 6393

6393

IP_數據表(A-2):Analog-PLL For Spread Spectrum Clock

2023-07-06 20:13:11 0

0 P_數據表(A-5):Analog-PLL For Spread Spectrum Clock

2023-07-06 20:13:47 0

0 IP_數據表(A-8):Analog-PLL For Spread Spectrum Clock

2023-07-06 20:14:19 0

0 本文聊聊“RQS_CLOCK-12”時鐘設置建議以及它如何幫助達成時序收斂

2023-07-12 15:44:19 1194

1194

當下這社會,沒有幾萬個Clock Gating,出門都不好意思和別人打招呼!

2023-07-17 16:50:29 6546

6546

在本篇博文中,我們來聊聊“RQS_CLOCK-12”時鐘設置建議以及它如何幫助達成時序收斂。

2023-07-26 09:53:50 1538

1538

首先,ASIC芯片的clock gating絕對不能采用下面結構,原因是會產生時鐘毛刺

2023-08-25 09:53:43 1501

1501

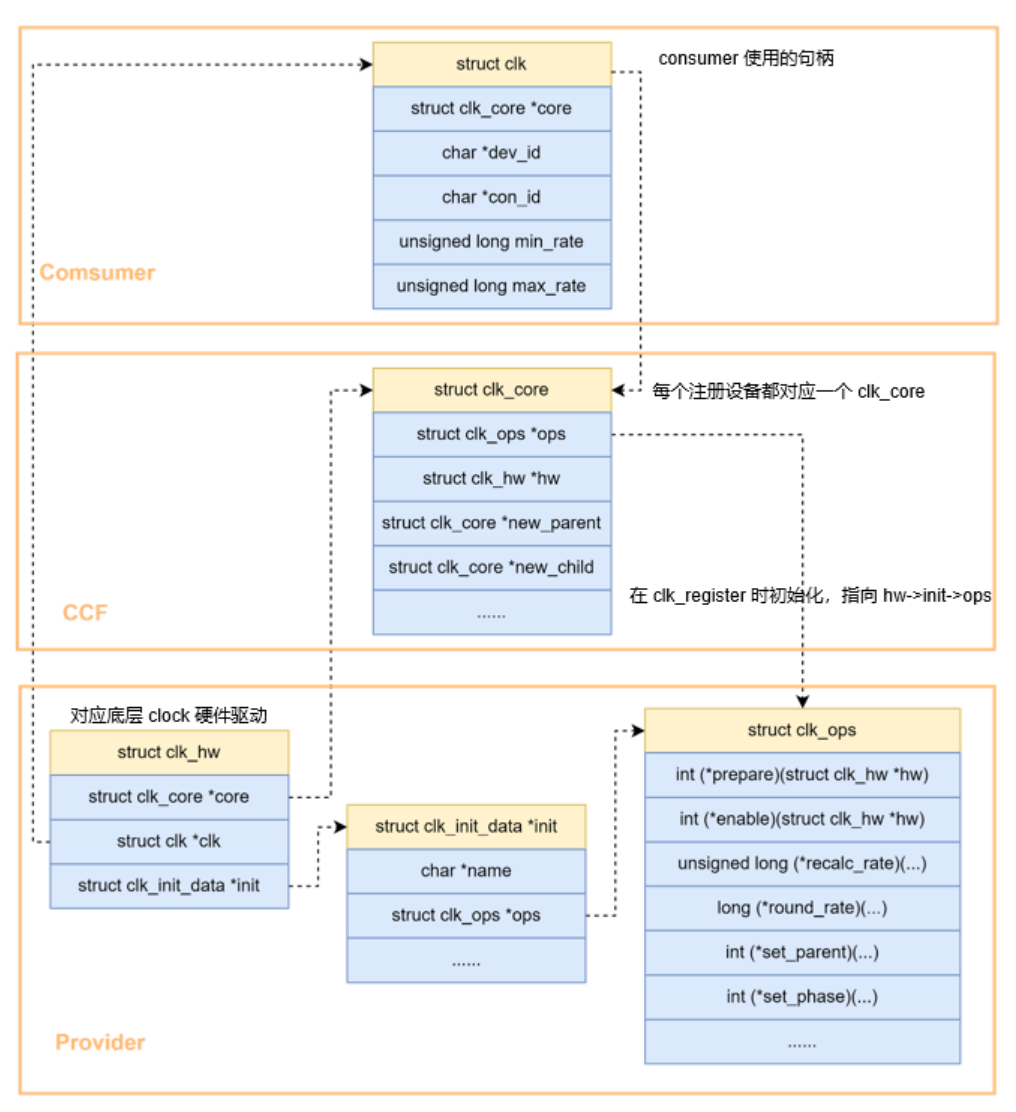

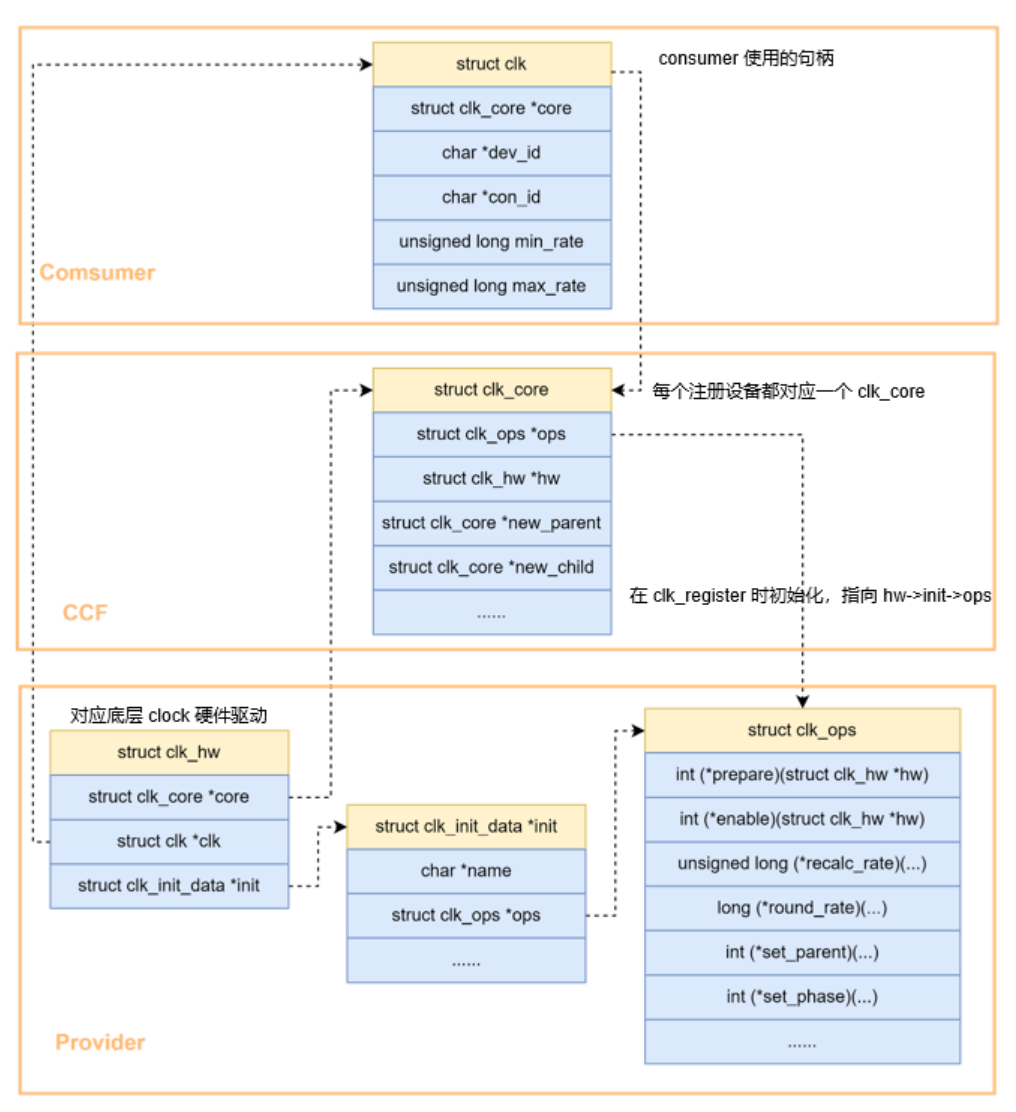

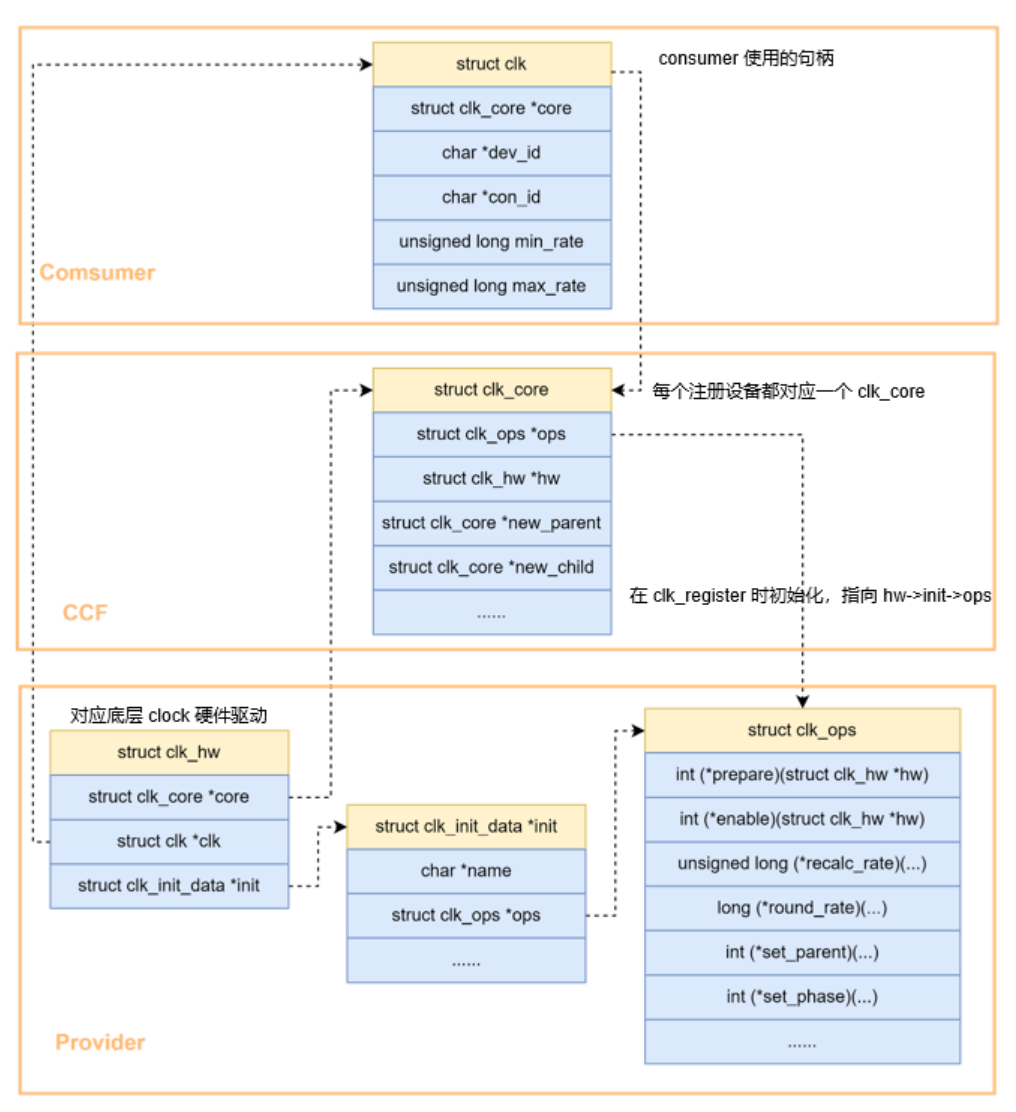

clock子系統 Linux的時鐘子系統由CCF(common clock framework)框架管理, CCF向上給用戶提供了通用的時鐘接口,向下給驅動開發者提供硬件操作的接口 。各結構體關系

2023-09-27 14:25:18 1535

1535

clock驅動實例 clock驅動在時鐘子系統中屬于provider,provider是時鐘的提供者,即具體的clock驅動。 clock驅動在Linux剛啟動的時候就要完成,比 initcall

2023-09-27 14:39:35 1963

1963

電子發燒友網站提供《CLOCK常見問題解答.pdf》資料免費下載

2023-11-23 10:23:38 0

0 電腦主板clock測量,內部絕密

2025-08-26 15:08:35 2

2

電子發燒友App

電子發燒友App

評論