今天我們要介紹的時序分析基本概念是 clock group,簡稱時鐘組。 定義完時鐘后,我們也需要通過設(shè)置clock group來確認各個時鐘之間的關(guān)系。

工具不會對處于不同clock group的時鐘檢查時序。這是很重要的一步,因為通常我們還需要做cross domain check, 如果clock group設(shè)錯了, 會導(dǎo)致整個STA檢查錯誤。一般有三種類型的clock group屬性選擇:

asynchronous

physically_exclusive

logically_exclusive

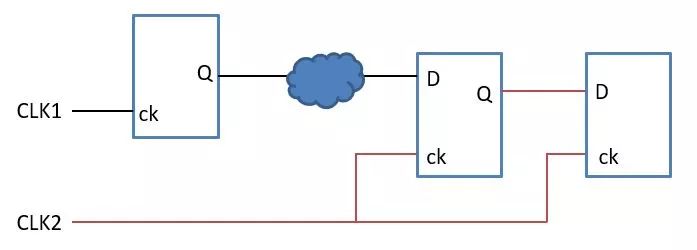

asynchronous代表兩個異步的clock group,工具會做正常的SI分析。

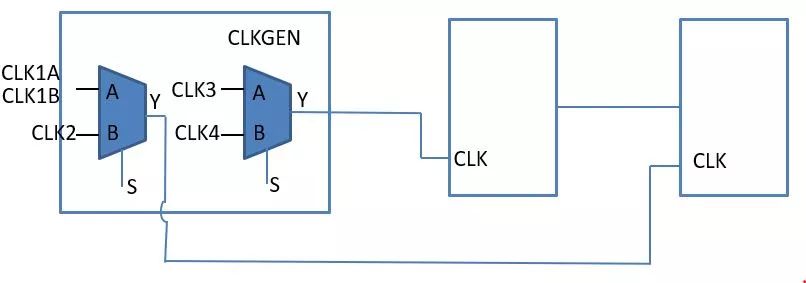

logically_exclusive代表兩個clock group在邏輯上相互排斥,比如兩個clock經(jīng)過MUX選擇器。工具分析SI時,采用 infinite window(信號全部翻轉(zhuǎn)),而不是看具體的timing window,較為悲觀。

physically_exclusive代表兩個clock group在物理意義上相互排斥,比如在一個source pin上定義了兩個時鐘。這時候,工具會禁止分析SI。

一個簡單的例子:

set_clock_group -name groupA -physically_exclusive \\

-group "CLK1A" -group "CLK1B"

set_clock_group -name groupB -logically_exclusive \\

-group "CLK1A CLK1B CLK3" -group "CLK2" -group "CLK4"

set_clock_group -name aysnc_group -asynchronous \\

-group CLK1 -group CLK2

-

時鐘

+關(guān)注

關(guān)注

11文章

1971瀏覽量

134984 -

時序分析

+關(guān)注

關(guān)注

2文章

130瀏覽量

24225 -

Mux

+關(guān)注

關(guān)注

0文章

44瀏覽量

24138 -

選擇器

+關(guān)注

關(guān)注

0文章

111瀏覽量

15130 -

CLK

+關(guān)注

關(guān)注

0文章

132瀏覽量

18040

發(fā)布評論請先 登錄

電源管理之clock驅(qū)動構(gòu)架設(shè)計解決方案

在PSoC4000的UART Bootloader中不能將引導(dǎo)加載程序時鐘資源設(shè)置為extCLK嗎?

請問ad9361各個時鐘關(guān)系是什么?

過孔直徑和線寬有什么關(guān)系?它們之間的關(guān)系是怎么設(shè)置的?

I / O和時鐘區(qū)域之間是什么關(guān)系

輸入時鐘和采樣率之間有什么關(guān)系?

STM32微控制器的時鐘樹和STM32CubeMX Clock Configuration的配置關(guān)系是什么?

Vivado時鐘分組約束的三類應(yīng)用

邊緣計算與云計算之間是怎樣的關(guān)系?

機械周期、時鐘周期、脈沖、晶振頻率之間的關(guān)系

時鐘子系統(tǒng)中clock驅(qū)動實例

怎樣通過設(shè)置clock group來確認各個時鐘之間的關(guān)系?

怎樣通過設(shè)置clock group來確認各個時鐘之間的關(guān)系?

評論