clock驅(qū)動(dòng)實(shí)例

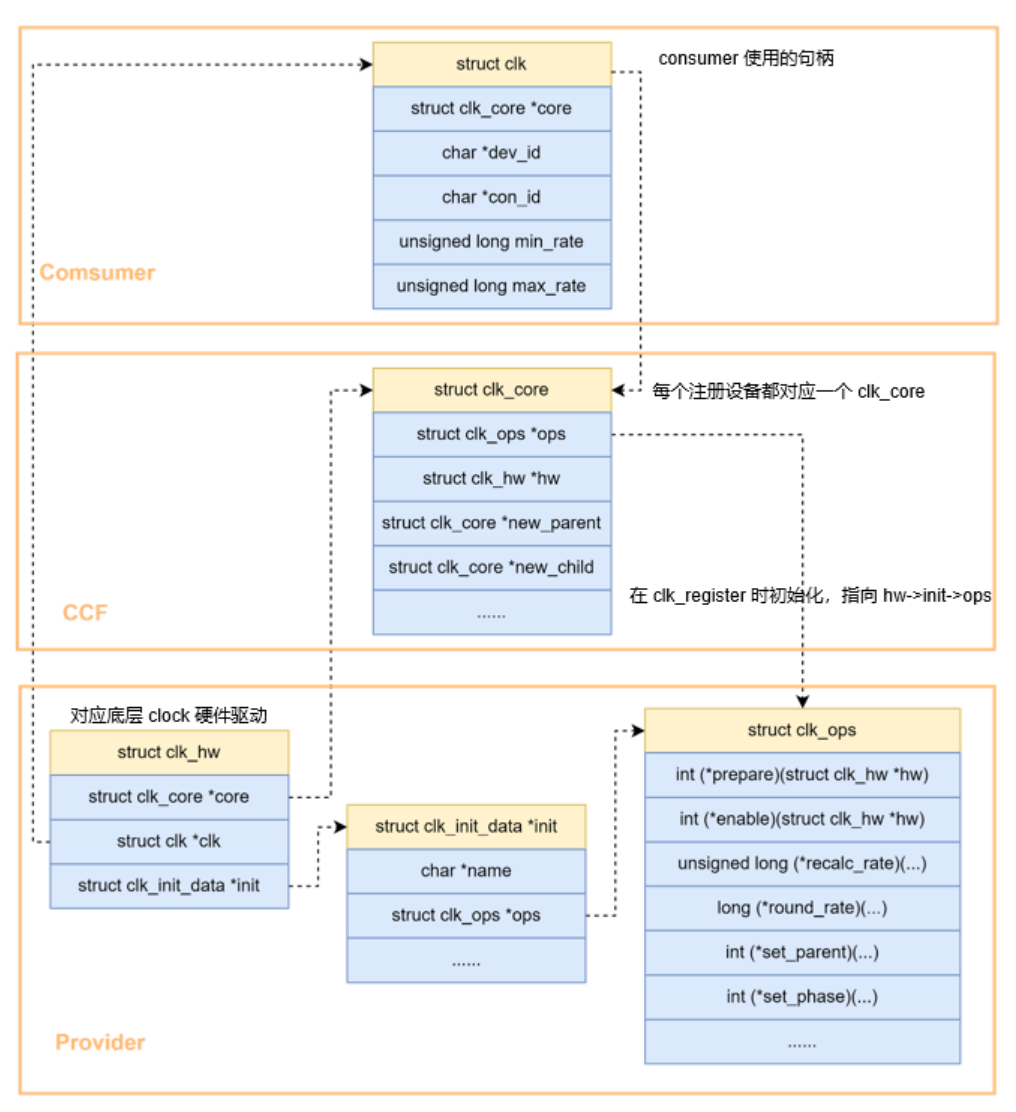

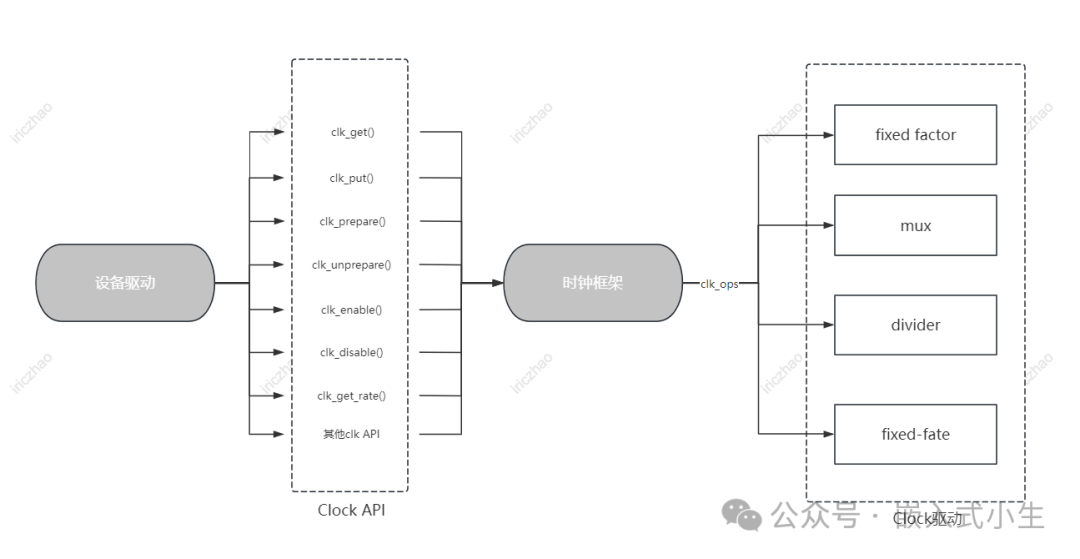

clock驅(qū)動(dòng)在時(shí)鐘子系統(tǒng)中屬于provider,provider是時(shí)鐘的提供者,即具體的clock驅(qū)動(dòng)。

clock驅(qū)動(dòng)在Linux剛啟動(dòng)的時(shí)候就要完成,比initcall都要早期,因此clock驅(qū)動(dòng)是在內(nèi)核中進(jìn)行實(shí)現(xiàn)。 在內(nèi)核的drivers/clk目錄下,可以看到各個(gè)芯片廠商對各自芯片clock驅(qū)動(dòng)的實(shí)現(xiàn):

下面以一個(gè)簡單的時(shí)鐘樹,舉例說明一個(gè)芯片的時(shí)鐘驅(qū)動(dòng)的大致實(shí)現(xiàn)過程:

1、時(shí)鐘樹

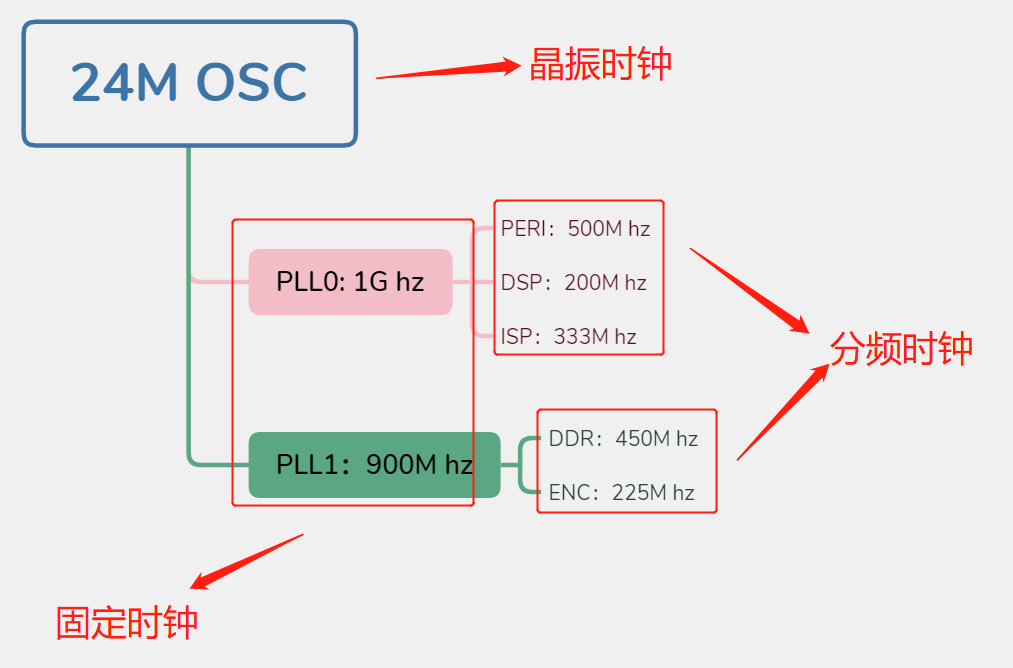

通常來說,一個(gè)芯片的時(shí)鐘樹是比較固定的,例如,以下時(shí)鐘樹:

時(shí)鐘樹的 根節(jié)點(diǎn)一般是晶振時(shí)鐘 ,上圖根節(jié)點(diǎn)為24M晶振時(shí)鐘。根節(jié)點(diǎn)下面是PLL,PLL用于提升頻率。PPL0下又分頻給PERI、DSP和ISP。PLL1分頻給DDR和ENC。

對于PLL來說,PLL的頻率可以通過寄存器設(shè)置,但通常是固定的,所以PLL屬于 固定時(shí)鐘 。

對PERI、DSP等模塊來說,它們的頻率來自于PLL的分頻,因此這些模塊的時(shí)鐘屬于 分頻時(shí)鐘 。

2、設(shè)備樹

設(shè)備樹中表示一個(gè)時(shí)鐘源,應(yīng)有如下屬性,例如24M晶振時(shí)鐘:

clocks{

osc24M:osc24M{

compatible = "fixed-clock";

#clock-cells = < 0 >;

clock-output-name = "osc24M";

clock-frequency = < 24000000 >;

};

};

| 屬性 | 說明 |

|---|---|

| compatible | 驅(qū)動(dòng)匹配名字 |

| #clock-cells | 提供輸出時(shí)鐘的路數(shù)。#clock-cells為0時(shí),代表輸出一路時(shí)鐘#clock-cells為1時(shí),代表輸出2路時(shí)鐘。 |

| #clock-output-names | 輸出時(shí)鐘的名字 |

| #clock-frequency | 輸出時(shí)鐘的頻率 |

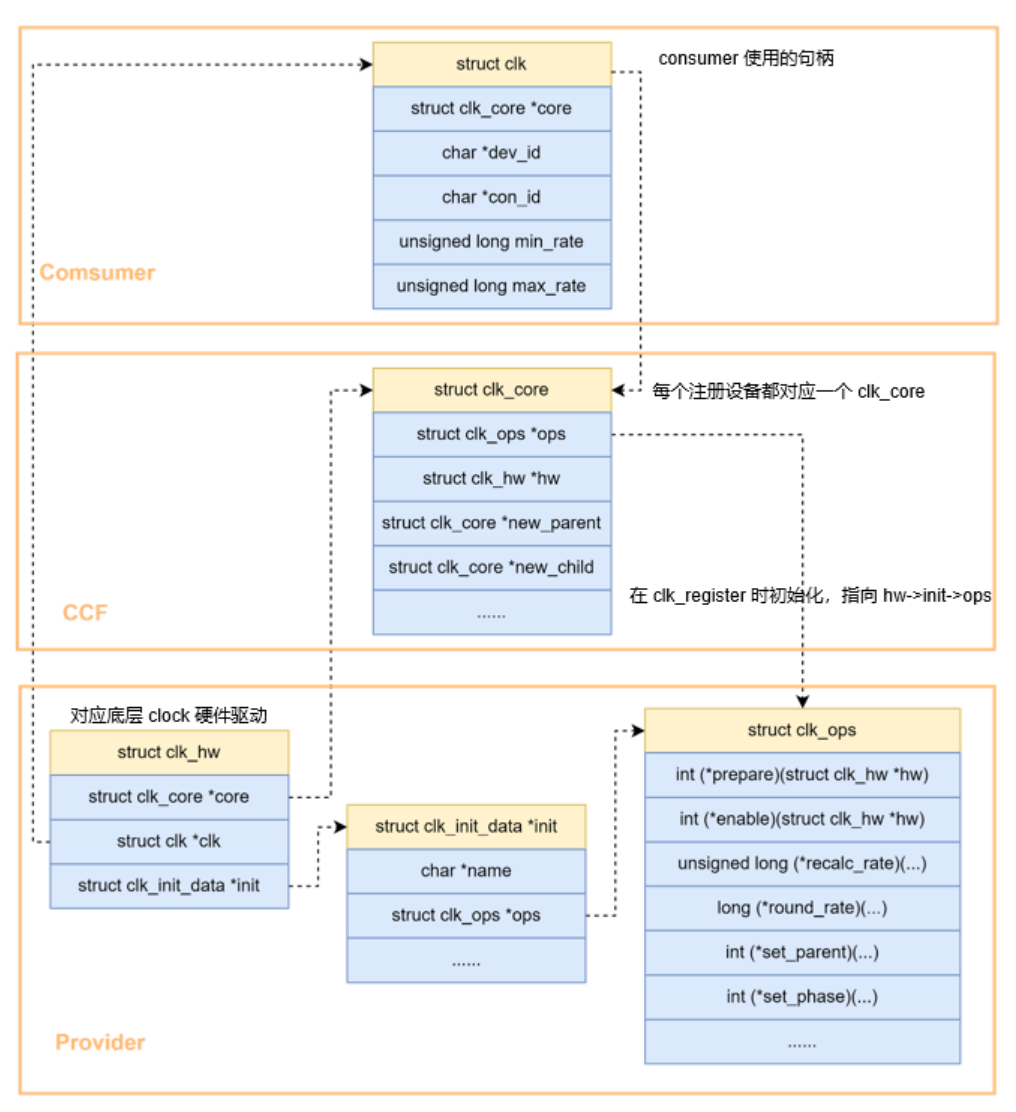

3、驅(qū)動(dòng)實(shí)現(xiàn)

clock驅(qū)動(dòng)編寫的基本步驟:

- 實(shí)現(xiàn)

struct clk_ops相關(guān)成員函數(shù) - 定義分配

struct clk_onecell_data結(jié)構(gòu)體,初始化相關(guān)數(shù)據(jù) - 定義分配

struct clk_init_data結(jié)構(gòu)體,初始化相關(guān)數(shù)據(jù) - 調(diào)用

clk_register將時(shí)鐘注冊進(jìn)框架 - 調(diào)用

clk_register_clkdev注冊時(shí)鐘設(shè)備 - 調(diào)用

of_clk_add_provider,將clk provider存放到of_clk_provider鏈表中管理 - 調(diào)用

CLK_OF_DECLARE聲明驅(qū)動(dòng)

-

驅(qū)動(dòng)

+關(guān)注

關(guān)注

12文章

1984瀏覽量

88651 -

Linux

+關(guān)注

關(guān)注

88文章

11793瀏覽量

219385 -

Clocks

+關(guān)注

關(guān)注

0文章

5瀏覽量

9905 -

系統(tǒng)

+關(guān)注

關(guān)注

1文章

1047瀏覽量

22378

發(fā)布評論請先 登錄

Linux clock子系統(tǒng)及驅(qū)動(dòng)實(shí)例

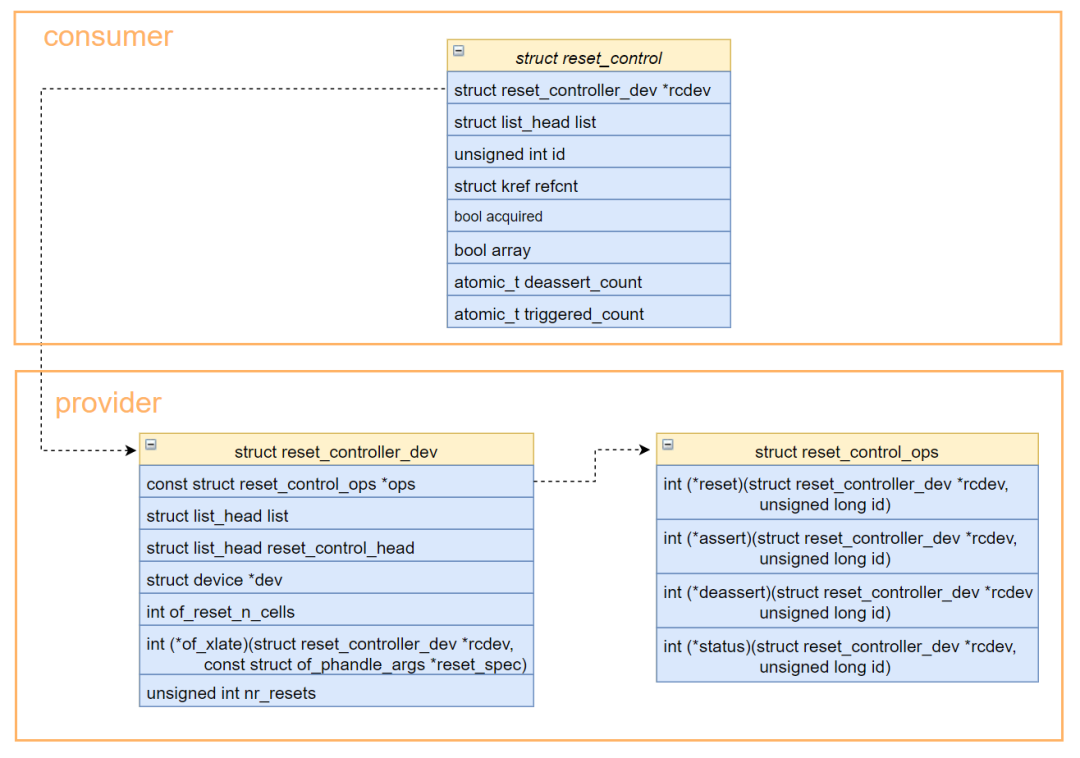

Linux reset子系統(tǒng)及驅(qū)動(dòng)實(shí)例

FPGA數(shù)字電子系統(tǒng)設(shè)計(jì)與開發(fā)實(shí)例導(dǎo)航

FPGA_數(shù)字電子系統(tǒng)設(shè)計(jì)與開發(fā)實(shí)例導(dǎo)航

SYSBIOS6中驅(qū)動(dòng)clock的timer配置問題如何解決

電子系統(tǒng)設(shè)計(jì)實(shí)例

FPGA_數(shù)字電子系統(tǒng)設(shè)計(jì)與開發(fā)實(shí)例導(dǎo)航

三個(gè)命令生成的報(bào)告中均可顯示Clock Skew的具體數(shù)值

Linux時(shí)間子系統(tǒng)之一:clock source(時(shí)鐘源)

為什么需要時(shí)鐘門控?時(shí)鐘門控終極指南

Linux reset子系統(tǒng)有什么功能

Linux clock子系統(tǒng)是什么

SOC設(shè)計(jì)中Clock Gating的基本原理與應(yīng)用講解

深度解析linux時(shí)鐘子系統(tǒng)

時(shí)鐘子系統(tǒng)中clock驅(qū)動(dòng)實(shí)例

時(shí)鐘子系統(tǒng)中clock驅(qū)動(dòng)實(shí)例

評論