ZYNQ 、AXI協議、PS與PL內部通信 三種AXI總線分別為: AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址

2018-01-09 14:10:42 9365

9365

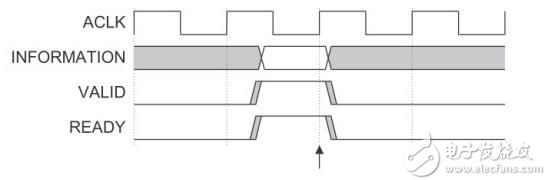

Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,專用于和元器件內的控制寄存器進行通信。AXI-Lite允許構建簡單的元件接口。這個接口規模較小,對設計和驗證方面的要求更少

2020-09-27 11:33:02 9821

9821

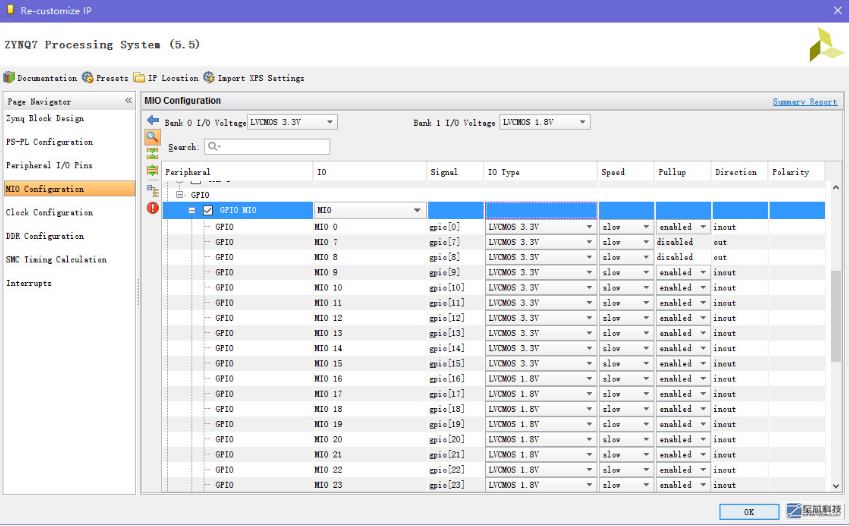

芯片型號:XC7Z010-1CLG400C Vivado版本:2016.1 點亮流水燈,共使用了三種方式: (1)PS通過MIO點亮PS端LED (2)PS通過EMIO點亮PL端LED (3)PS

2020-11-24 14:32:33 25768

25768

4 版本。 AXI總線 ZYNQ有三種AXI總線: (A)AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求

2020-12-04 12:22:44 9054

9054

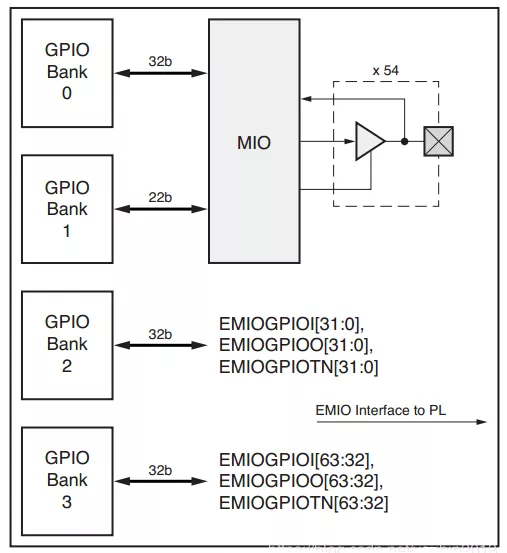

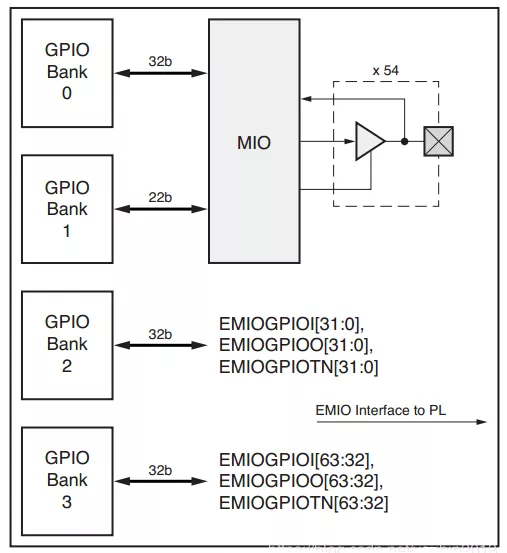

GPIO的結構體系 zynq的GPIO,分為兩種,MIO(multiuse I/O)和EMIO(extendable multiuse I/O)。 ZYNQ的GPIO由4個BANK組成,其體系結構

2020-12-09 11:41:46 5018

5018

FPGA+ARM是ZYNQ的特點,那么PL部分怎么和ARM通信呢,依靠的就是AXI總線。這個實驗是創建一個基于AXI總線的GPIO IP,利用PL的資源來擴充GPIO資源。通過這個實驗迅速入門

2020-12-25 14:07:02 6724

6724

前言: ZYNQ 7000有三種GPIO:MIO,EMIO,AXI_GPIO MIO是固定管腳的,屬于PS,使用時不消耗PL資源;EMIO通過PL擴展,使用時需要分配管腳,使用時消耗PL管腳資源

2020-12-26 10:12:57 5259

5259

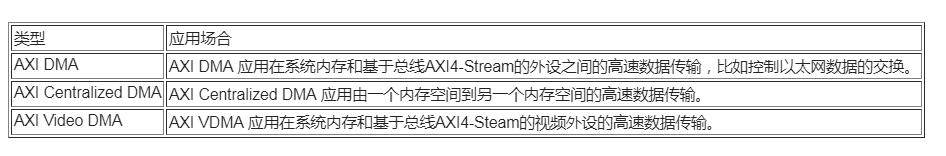

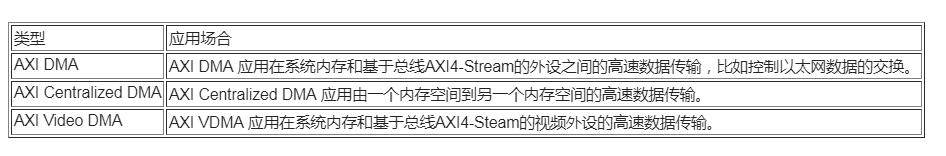

一、AXI DMA介紹 本篇博文講述AXI DMA的一些使用總結,硬件IP子系統搭建與SDK C代碼封裝參考米聯客ZYNQ教程。若想讓ZYNQ的PS與PL兩部分高速數據傳輸,需要利用PS的HP

2020-12-31 09:52:02 10713

10713

如果想用PS點亮PL的LED燈,該如何做呢?一是可以通過EMIO控制PL端LED燈,二是通過AXI GPIO的IP實現控制。本章介紹如何使用EMIO控制PL端LED燈的亮滅。同時也介紹了,利用EMIO連接PL端按鍵控制PL端LED燈。

2021-01-30 10:05:00 8761

8761

使用zynq最大的疑問就是如何把PS和PL結合起來使用,在其他的SOC芯片中一般都會有GPIO,本實驗使用一個AXI GPIO的IP核,讓PS端通過AXI總線控制PL端的LED燈,實驗雖然簡單,不過可以讓我們了解PL和PS是如何結合的。

2021-02-01 10:06:00 7851

7851

本文主要介紹ZYNQ PS + PL異構多核案例的使用說明,適用開發環境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4

2021-09-07 17:03:30 3710

3710

AXI接口FIFO是從Native接口FIFO派生而來的。AXI內存映射接口提供了三種樣式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的應用外,AXI FIFO還可以用于AXI系統總線和點對點高速應用。

2025-03-17 10:31:11 1914

1914

AXI GPIO簡介

AXI-GPIO是一種Xilinx公司開發的外設IP,可以連接到AXI總線上,并提供GPIO(General Purpose Input Output)功能。AXI-GPIO

2025-10-22 08:14:59

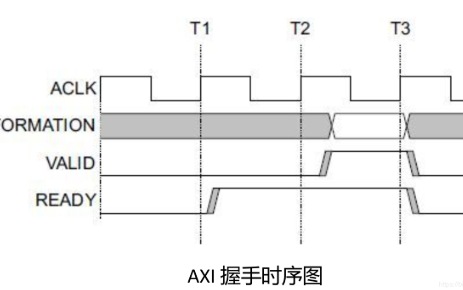

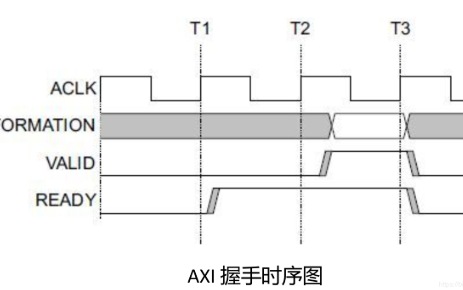

1、AXI接口協議詳解 AXI 總線 上面介紹了AMBA總線中的兩種,下面看下我們的主角—AXI,在ZYNQ中有支持三種AXI總線,擁有三種AXI接口,當然用的都是AXI協議。其中三種AXI總線

2022-10-14 15:31:40

AXI 總線上面介紹了AMBA總線中的兩種,下面看下我們的主角—AXI,在ZYNQ中有支持三種AXI總線,擁有三種AXI接口,當然用的都是AXI協議。其中三種AXI總線分別為:AXI

2022-04-08 10:45:31

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-02-02 07:30:07

本帖最后由 何立立 于 2018-1-9 15:03 編輯

ZYNQ 、AXI協議、PS與PL內部通信 三種AXI總線分別為:AXI4:(For high-performance

2018-01-08 15:44:39

ZYNQ AXI RRESP ERR。發生RRESP時會發生什么?如何獨立檢測這個錯誤?現在,當rresp發生錯誤時,axi讀取函數xil_in32只是失速?有任何超時或不同的方式來閱讀這個錯誤。

2020-05-18 06:29:17

。1 axi_gpio_led_demo案例1.1 案例功能案例功能:PS端通過AXI4-Lite總線發送命令至PL端AXI GPIO IP核,IP核再根據命令控制評估底板PL端LED5的狀態?圖

2021-05-28 14:28:28

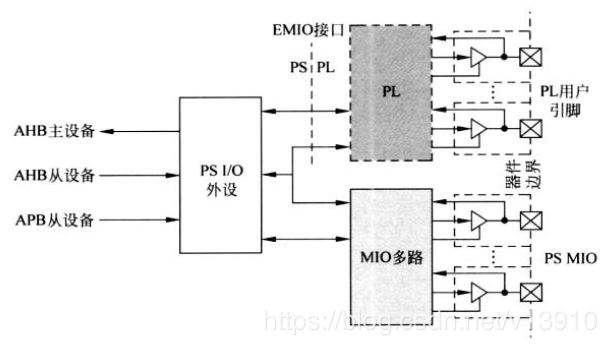

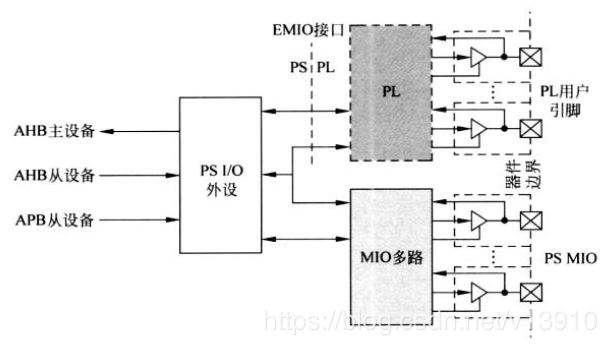

上,也可以通過 EMIO 連接到 PL 端的引腳。Zynq-7000 系列芯片一般有 54 個 MIO,個別芯片如 7z007s 只有 32 個。GPIO 是英文“general purpose I

2022-02-08 07:27:16

大部分器件的接口要求,提供互聯架構的靈活性與獨立性。

(1)AXI總線

總線是一組傳輸通道,是各種邏輯器件構成的傳輸數據的通道,一般由數據線、地址線、控制線等構成。在ZYNQ中支持三種AXI總線

2023-11-03 10:51:39

ZYNQ學習筆記_GPIOGPIO介紹MIO介紹EMIO介紹控制GPIO接口的寄存器原理GPIO介紹GPIO的英文全稱為General-purpose input/output,即一種通用外設,可以

2022-02-08 07:30:36

進行編程的初步PS和PL。如果上面有必要的信息,請提供。7.請提供ZYNQ 7Z020-CLG484芯片的所有I / O文檔8.如何在沒有AXI的情況下將處理器(PS)地址,數據,WRB,RDB連接到PL)。如何使用emio PINS來PL和PL到PS)。請提供必要的信息

2020-03-12 14:39:42

三種常見的PCB錯誤是什么

2021-03-12 06:29:32

三種遠程測控終端(RTU)產品之間的比較

2021-05-28 06:27:08

FCC三種認證方式主要是針對不同類別產品。無線、射頻類產品必須申請FCC ID,電腦及電腦周邊產品需申請FCC DOC或ID,其它產品一般申請FCC VOC即可。三種認證方式中級別ID最高,需TCB

2015-10-22 14:11:47

HAL庫中UART的三種收發方式是什么?

2022-02-18 06:33:52

HFSS三種輻射邊界的區別與選擇技巧是什么?

2021-05-21 06:54:59

QSPI特點QSPI三種工作模式

2020-12-31 06:36:55

STM32三種啟動方式是什么

2021-12-15 07:16:54

STM32三種啟動模式對應的存儲介質是什么?

2022-01-27 07:00:03

STM32的三種Boot模式有何差異呢?如何去驗證這種差異呢?

2021-11-26 07:15:38

淺識STM32的三種boot模式文章目錄淺識STM32的三種boot模式任務摘要一、認識boot1.三種BOOT模式介紹2.開發BOOT模式選擇3.STM32三種啟動模式4.三種模式的存儲地址二

2021-12-10 07:46:37

USB設備端點有三種操作模式,包括自動驗證模式、手動驗證模式和Fly模式。 它們的功能是什么?

2020-12-03 06:46:02

while的三種使用形式是什么樣的?

2021-11-02 08:35:34

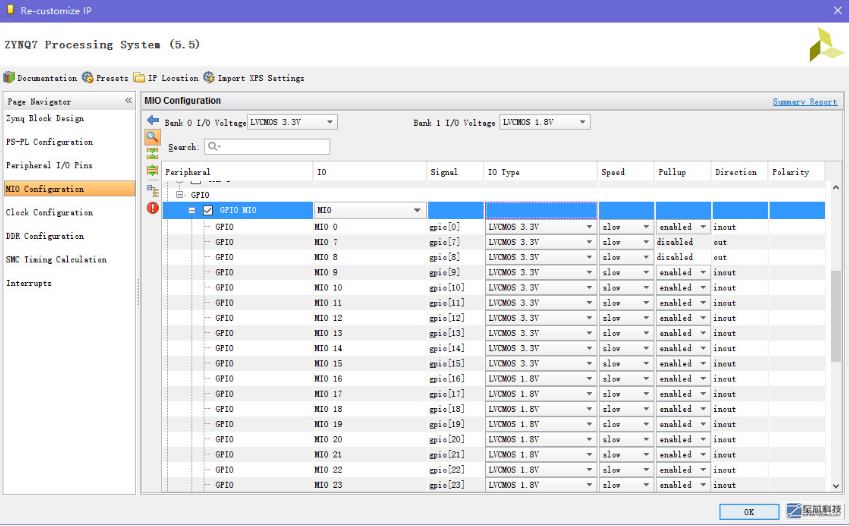

zynq芯片集成了兩片arm a9的內核,和xilinx的fpga可編程部分集成在一塊芯片上面。剛開始學習的時候使用vivado,現在已經在純玩Linux了。第一步:選擇MIO

2015-06-14 14:27:17

持PS+PL的架構,靈活使用PL。Zynq上的存儲器接口也很豐富,包括DDR控制器,Quad-SPI控制器、Nand/NOR/SRAM控制器等。通用IO(GPIO)在Zynq上,我們可以通過MIO引出最多54個

2015-07-07 20:22:49

)簡稱為GPIO,中文意思為通用IO口,很多簡單控制開關的設備只需要開關兩種狀態就可以來了,用傳統的串口顯得復雜,所以嵌入式微處理器通常用IO口即可。本文主要介紹Zynq的GPIO基本原理和相關寄存器配置

2015-07-17 12:44:38

原子公眾號,獲取最新資料第三章GPIO之EMIO按鍵控制LED實驗PS和外部設備之間的通信主要是通過復用的輸入/輸出(Multiplexed Input/Output,MIO)實現的。除此之外,PS還可

2020-08-29 16:20:36

通過EMIO連接到PL端的引腳。Zynq-7000系列芯片一般有54個MIO,個別芯片如7z007s只有32個。 GPIO是英文“general purpose I/O”的縮寫,即通用的輸入/輸出

2020-08-29 16:17:15

原子公眾號,獲取最新資料第四章GPIO之MIO按鍵中斷實驗中斷是一種當滿足要求的突發事件發生時通知處理器進行處理的信號。中斷可以由硬件處理單元和外部設備產生,也可以由軟件本身產生。對硬件來說,中斷信號

2020-08-29 16:21:47

一燈雙控的三種接線方法有哪些利弊

2021-03-11 07:10:04

什么是Boot模式?STM32三種Boot模式有什么差異?怎么實現STM匯編程序設計?

2021-11-29 06:04:54

本文逐一介紹三種視頻數字接口的標準。

2021-06-03 06:24:31

一般伺服都有三種控制方式:速度控制方式,轉矩控制方式,位置控制方式。大多數人想知道的就是這三種控制方式具體根據什么來選擇的?

2021-01-29 07:28:36

伺服電機的三種控制方式

2021-01-21 06:45:01

伺服有哪幾種控制方式?伺服的三種控制方式具體根據什么來選擇的?

2021-10-11 08:17:43

RJ45插頭實現GE_T模式的電口應用。Zynq-7000 PS部分包含兩個千兆以太網MAC層硬核,因此還需要以太網物理層傳輸芯片實現千兆以太網接口。MAC層硬核所對應的接口引腳,既可從PS端的MIO引腳

2021-10-22 09:43:10

從不同的側重點給出了幾種拓撲,將對其進行分析比較三種拓撲有其各自的有缺點,如何來選擇它們?

2021-04-07 06:05:16

刷機時用到的三種工具分別是什么?SD卡有何作用?fastboot是什么?fastboot有何作用?

2021-12-27 06:18:48

常用的FBAR模型有哪三種?

2021-03-11 06:16:18

藍牙無線組網的優點是什么?常見的三種無線接入方式是什么?藍牙無線組網原理與上網方案分享

2021-05-26 06:33:11

LABVIEW 小白 想做一個軸承故障檢測系統 需要選擇軸承內圈外圈滾子三種故障計算公式算出的結果 要用枚舉控件有人能給編一下嗎就類似于用枚舉控件選擇三種不同類型的數值 可用數值常量代替

2018-04-27 16:51:41

`玩轉Zynq連載2——Zynq PS的GPIO外設更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s1 概述 Zynq的GPIO外設控制最多54個MIO引腳,也

2019-04-18 16:33:51

GPIO的PS系統配置打開ZYNQ7 ProcessingSystem的配置頁面Peripheral I/O Pins,可以看到右側若勾選GPIO MIO選項,在對應的MIO號若點擊變綠,則表示該MIO號

2019-10-10 11:21:06

的就是PL的引腳)。關于MIO和EMIO的關系,更形象直接的可以示意如圖所示。MIO和EMIO都是PS的一部分,但是MIO可以直接連接到Zynq芯片的引腳上,和PL無關;而EMIO需要通過PL的IO

2019-10-12 17:35:16

` 1概述Zynq將ARM和FPGA整合到了一個芯片上,它的過人之處不僅是功耗、面積、成本的優化,更多的是將二者之間原本極為受限的數據交互方式轉移到芯片內部完成,4條AXI GP通道(2個從機、2個

2019-11-12 10:23:42

1概述AXI HP總線是Zynq芯片非常重要的一個功能,它可以實現Cortex A9與PL之間大吞吐量的數據通信。可以說,Zynq芯片最大的賣點恐怕就是這條總線。對不起,不是1條,是4條這樣的AXI

2019-11-26 09:47:20

不同通道使用情況下的數據吞吐量。大家可以在此基礎上,更改不同的AXI HP總線時鐘頻率,以評估時鐘頻率對AXI HP總線的影響。2 AXI總線協議介紹參考文檔《玩轉Zynq-基礎篇:AXI總線協議介紹

2019-11-28 10:11:38

●在從機與互聯總線之間 ●在主機與從機之間大多數系統使用以下三種互聯方式中的一種: ●地址和數據總線共享 ●地址共享,有多個數據總線 ● 多層互聯,即有多個地址和數據總線在大多數系統中,對地址通道

2019-05-06 16:55:32

第三種WiFi模塊是什么?有什么特點?

2021-05-14 06:49:07

編譯的三種類型是什么?ARM_Linux制作嵌入式遠程調試工具

2021-12-24 06:42:58

原理圖的Grid Preset的默認情況下有三種設置,請問這三種設置有什么區別,是怎么使用的

2019-04-10 07:35:06

請群主詳細解釋下這三種啟動方式,看了參考資料不是很明白其意!謝謝!

2019-07-17 04:35:12

進程類型進程的三種狀態

2021-04-02 07:06:39

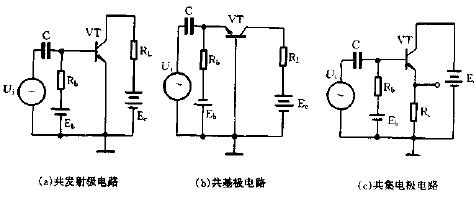

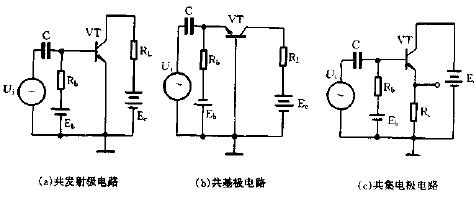

半導體三極管的三種基本放大電路的三種連接法電路圖

2009-05-06 14:55:21 5904

5904

三種不同的“防 Ping”技巧

淺析三種不同的“防 Ping”方法

眾所周知,Ping命令是一個非常有用的網絡命令,大家常用它

2010-04-14 13:53:00 1287

1287 本文介紹zynq上三種方式啟動文件的生成和注意事項,包括只用片上RAM(OCM)和使用DDR3兩種情況。 JTAG方式 JTAG方式是調試中最常用的方式,在SDK中 在“Project

2017-11-10 14:49:02 15928

15928

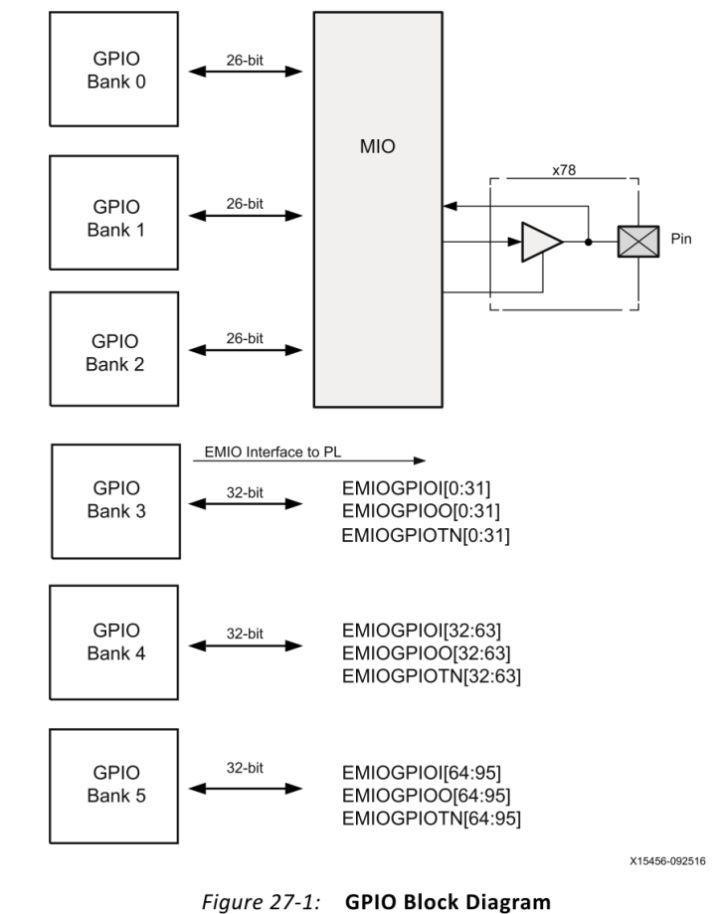

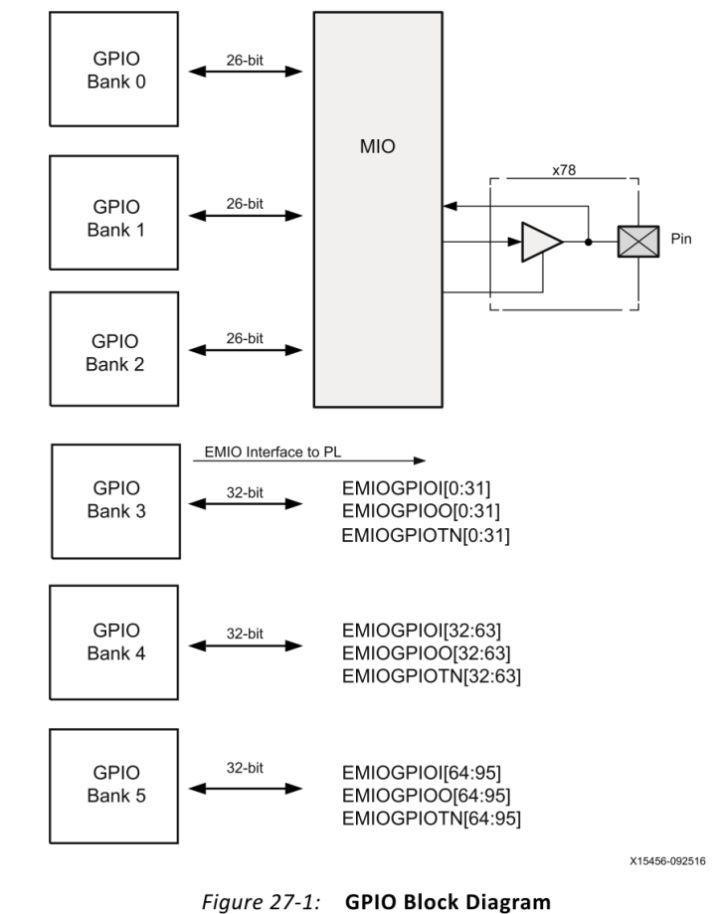

通過EMIO布線到PL; c)新增了四通道的高速GTR收發器; d)DDR控制更新到可支持DDR4L-2400速率。 (1)MIO資源 Zynq UltraScale+具有78個可配置復用的MIO,這些MIO可用作將PS內的相關外設控制器引出,同時

2017-02-08 08:29:11 1469

1469

本文主要介紹zynq linux AXI DMA傳輸步驟教程,具體的跟隨小編一起來了解一下。

2018-07-08 05:46:00 32067

32067

歡迎大家發言指出。 Zynq器件主要包括三種類型的存儲控制接口: ① DDR控制器,主要特性如下: ·支持DDR3、DDR2、LPDDR2; ·支持位寬為16比特或32比特,位寬為16比特時支持ECC。

2017-11-22 08:23:54 7949

7949

Zynq Qspi控制器支持三種模式:I/O模式、線性地址模式和傳統SPI模式,其中線性地址模式雙片選支持最大的線性地址空間為32MB,可通過PS DMA讀取。

2018-07-02 09:34:00 21624

21624

我們先看有哪三種GPIO:MIO、EMIO、AXI_GPIO。其中MIO和EMIO是直接掛在PS上的GPIO。而AXI_GPIO是通過AXI總線掛在PS上的GPIO上。

2018-07-07 08:23:00 5854

5854 GPIO功能,PS部分通過M_AXI_GP接口來控制該GPIO IP模塊;另外EMIO模塊雖然使用PS部分GPIO但也使用了PL部分的管腳資源。MIO方式實現GPIOvivado中zynq設置如下圖由圖中

2018-08-07 10:16:49 3810

3810

了解訪問集成Xilinx模數轉換器(XADC)的三種方法;

通過直接連接到PS,作為PS或Microblaze的AXI外設,或作為邏輯的IP核。

2018-11-20 06:16:00 3120

3120 了解MIO和EMIO如何相關以及如何使用首選的PlanAhead / XPS流將信號傳遞到“真實世界”。

2018-11-26 06:27:00 4113

4113 如何設計高效的 PL 和 PS 數據交互通路是 ZYNQ 芯片設計的重中之重。AXI 全稱 Advanced eXtensible Interface,是 Xilinx 從 6 系列的 FPGA 開始引入的一個接口協議,主要描述了主設備和從設備之間的數據傳輸方式。

2020-03-15 17:04:00 12879

12879

PS部分框圖如上圖所示,PS 和外部接口之間的通信主要是通過復用的輸入 / 輸出( Multiplexed Input/Output,MIO)實現的,它提供了可以做靈活配置的 54 個引腳,這表明外部設備和引腳之間的映射是可以按需定義的。

2020-08-27 14:30:35 5424

5424

為了簡化使用GPIO,編寫了以下腳本。使用下列腳本,一條命令就能設置一個GPIO的輸出值。腳本接受兩個輸入參數。第一個參數表示GPIO編號,MIO GPIO從0開始,EMIO GPIO從78開始。第二個參數是輸出值。如果輸出值是1,可以省略第二個參數。

2020-09-03 09:50:19 3212

3212

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過AXI-Lite或

2020-09-24 09:50:30 7201

7201

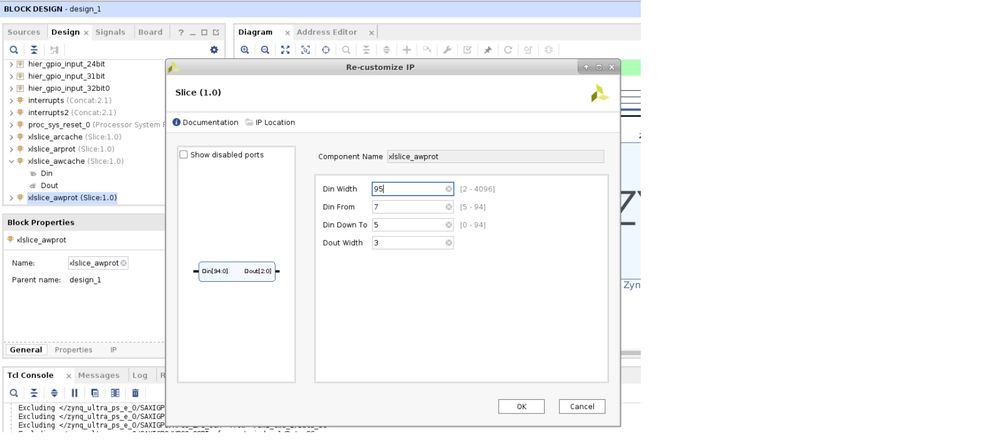

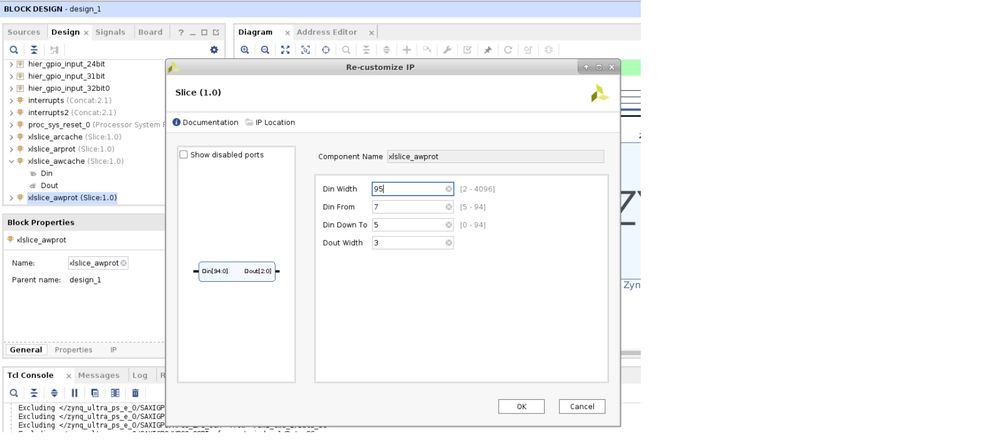

。 Slice配置界面 上圖中,輸入寬度是95,因為pl_reset占用率一個管腳。slice從輸入中提取emio的[7:5]三位,作為輸出。 Xilinx Linux 中缺省使能了GPIO驅動。對于

2020-11-04 14:57:17 2474

2474

帶寬會受限于SPI接口有效速率,本文采用芯片為W5500,支持10M/100M自適應,其理論值高達80Mbps,基本達到算法驗證的要求。 ZYNQ可以通過靈活的EMIO模擬SPI接口,從而在最少改動官方demo的前提下移植C語言驅動程序。本文著重講述EMIO的C語言軟件驅動方式及可重用封裝

2020-12-25 17:22:19 2776

2776 不同類型的DMA GPIO PL general purpose AXI GP AXI utlilizing PS DMAC High performance w/DMA ACP w/DMA 幾種

2020-10-09 18:05:57 8938

8938

基于AXI的DMA對內部寄存器的讀寫有著相同的方式。在普通傳輸模式下,DMA內部的寄存器都是由處理器通過AXI-Lite總線進行讀寫的;但基于AXI總線的三種DMA,都增加了S/G傳輸模式,它卸載了

2020-10-10 10:23:37 7886

7886

和接口的構架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過

2020-11-02 11:27:51 5032

5032

學習重點包括 MIO、 EMIO 的使用,中斷資源的使用,熟悉了解 ZYNQ 中斷的庫函數,學會推導 XILINX SDK 中斷函數的構架,掌握 AXI-LITE 總線協議,掌握自定義 IP 的創建,封裝。掌握 VIVADO 軟件的調試技巧等。

2020-11-09 08:00:00 4

4 ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2022-07-25 17:41:58 3555

3555

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-01-31 06:50:04 12

12 。如圖2.1所示,在相對較高層次對比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復雜。本章,將介紹這三種器件的特點。 2.1 技術時間線 進一步介紹之前,需要指出這三種

2021-04-02 17:20:14 18829

18829

上,也可以通過 EMIO 連接到 PL 端的引腳。Zynq-7000 系列芯片一般有 54 個 MIO,個別芯片如 7z007s 只有 32 個。GPIO 是英文“general purpose I

2021-12-04 18:51:06 16

16 ZYNQ學習筆記_GPIOGPIO介紹MIO介紹EMIO介紹控制GPIO接口的寄存器原理GPIO介紹GPIO的英文全稱為General-purpose input/output,即一種通用外設,可以

2021-12-04 19:36:10 10

10 [導讀] 前面寫過篇介紹ZYNQ基本情況的文章,今天來肝一篇實戰文章介紹AXI quad SPI 使用方法,如果你正使用ZYNQ的這個IP,希望對你有所...

2022-01-26 17:01:47 7

7 ARM 的 AXI 是一種面向突發的協議,旨在提供高帶寬同時提供低延遲。每個 AXI 端口都包含獨立的讀寫通道。要求不高的接口使用的 AXI 協議的一個版本是 AXI4-Lite,它是一種更簡單

2022-05-10 09:52:12 4732

4732 前面簡單學習了關于GPIO的操作,本次將使用PL 端調用 AXI GPIO IP 核, 并通過 AXI4-Lite 接口實現 PS 與 PL 中 AXI GPIO 模塊的通信。

2022-07-19 17:36:52 6442

6442 Zynq MPSoC是Zynq-7000 SoC(之后簡稱Zynq)的進化版本。Zynq是賽靈思發布的集成PL(FPGA)和PS設計的最早的一代產品。如圖2.1所示,在相對較高層次對比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復雜。本章,將介紹這三種器件的特點.

2022-08-15 09:16:38 3750

3750 zynq 中帶有兩個硬核千兆以太網MAC,ENET0,ENET1。與普通SOC 芯片不同,zynq PS 斷地外設可以通過MIO連接到芯片的引腳上,也可以通過EMIO 接口連接到PL 端。連接到PL端后,帶來了靈活性,可以轉換成各種接口。比如設計一個交換機。定義端其它的引腳。

2022-09-23 15:19:58 4191

4191 Zynq UltraScale+ PS MIO 可能在 VCCO_PSMIO 電源上電緩升期間輸出高位毛刺

2023-07-10 16:47:39 1829

1829

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關IP核中,經常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 2142

2142

Xilinx官方也提供有一些DMA的IP,通過調用API函數能夠更加靈活地使用DMA。 1. AXI DMA的基本接口 axi dma IP的基本結構如下,主要分為三個部分,分別是控制axi dma寄存器

2025-01-06 11:13:54 3773

3773

電子發燒友App

電子發燒友App

評論