Xilinx公司的7系列FPGA包括Artix-7,Kintex-7 和Virtex-7 三個(gè)系列。具有超高端連接帶寬,邏輯容量和信號(hào)完整性,提供低成本,小型尺寸和大容量的要求嚴(yán)格的高性能應(yīng)用。

2012-04-13 09:44:44 5189

5189

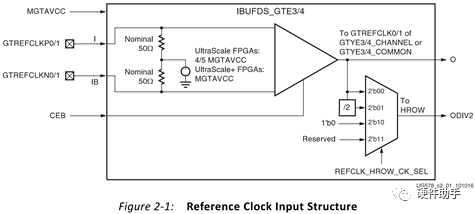

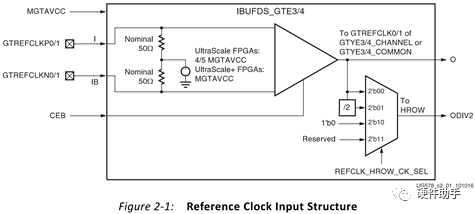

本文主要介紹Xilinx FPGA的GTx的參考時(shí)鐘。下面就從參考時(shí)鐘的模式、參考時(shí)鐘的選擇等方面進(jìn)行介紹。 參考時(shí)鐘的模式 參考時(shí)鐘可以配置為輸入模式也可以是輸出模式,但是在運(yùn)行期間不能切換。作為

2020-11-14 11:39:15 17609

17609

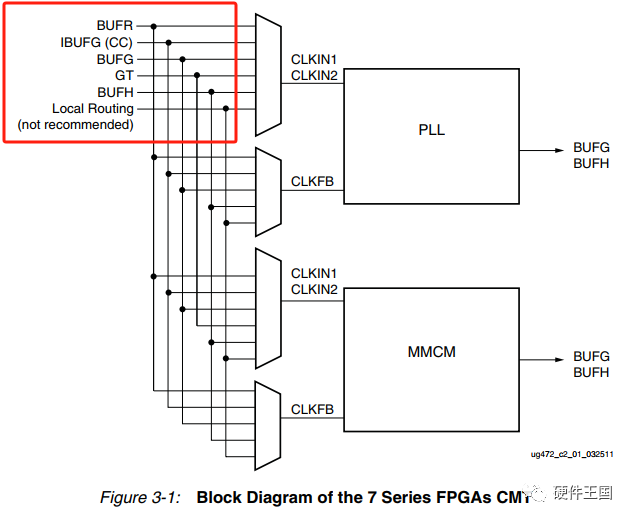

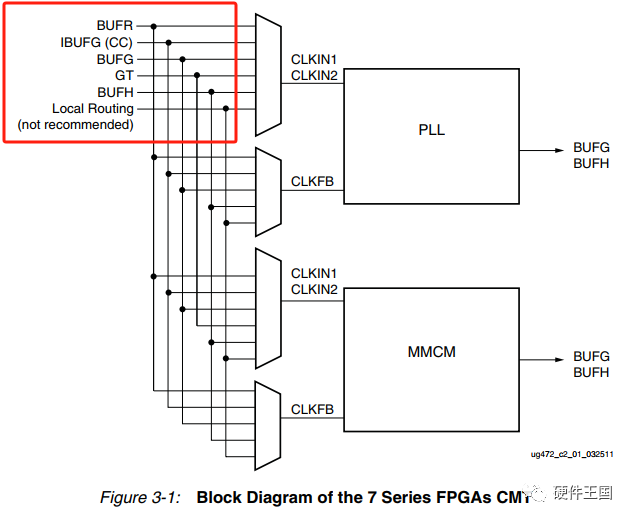

7系列FPGA擁有豐富的時(shí)鐘資源。各種緩沖器類型、時(shí)鐘輸入管腳和時(shí)鐘連接,可以滿足許多不同的應(yīng)用需求。選擇合適的時(shí)鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 3922

3922 7系列FPGA時(shí)鐘資源通過專用的全局和區(qū)域I/O和時(shí)鐘資源管理符合復(fù)雜和簡單的時(shí)鐘要求。時(shí)鐘管理塊(CMT)提供時(shí)鐘頻率合成、減少偏移和抖動(dòng)過濾等功能。非時(shí)鐘資源,如本地布線,不推薦用于時(shí)鐘功能。

2022-07-28 09:07:34 2068

2068 鎖相環(huán)基本上是每一個(gè)fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時(shí)鐘資源對(duì)xilinx fpga的底層時(shí)鐘資源做過說明,但是對(duì)于fpga的應(yīng)用來說,使用Clocking Wizard IP時(shí)十分方便的。

2023-06-12 17:42:03 8964

8964

。Xilinx FPGA7系列分為全局時(shí)鐘(Global clock)和局部時(shí)鐘(Regional clock)資源。目前,大型設(shè)計(jì)一般推薦使用同步時(shí)序電路。同步時(shí)序電路基于時(shí)鐘觸發(fā)沿設(shè)計(jì),對(duì)時(shí)鐘的周期

2023-07-24 11:07:04 1443

1443

通過上一篇文章“時(shí)鐘管理技術(shù)”,我們了解Xilinx 7系列FPGA主要有全局時(shí)鐘、區(qū)域時(shí)鐘、時(shí)鐘管理塊(CMT)。 通過以上時(shí)鐘資源的結(jié)合,Xilinx 7系列FPGA可實(shí)現(xiàn)高性能和可靠的時(shí)鐘分配

2023-08-31 10:44:31 4432

4432

本文主要介紹Xilinx FPGA的GTx的參考時(shí)鐘。下面就從參考時(shí)鐘的模式、參考時(shí)鐘的選擇等方面進(jìn)行介紹。

2023-09-15 09:14:26 5117

5117

7系列FPGA包含最多24個(gè)CMT塊,CMT具體的分布和與其他時(shí)鐘資源的關(guān)系請(qǐng)參考本合集(FPGA應(yīng)用開發(fā))的上一篇文章。本文主要介紹CMT內(nèi)部MMCM和PLL的區(qū)別以及在實(shí)際開發(fā)中怎么使用CMT,怎么實(shí)現(xiàn)跨時(shí)鐘區(qū)域,第一次讀者最好先閱讀上一篇文章——解剖時(shí)鐘結(jié)構(gòu)篇。

2023-11-17 17:08:11 11730

11730

Multiboot是一種在AMD Xilinx 7系列FPGA上實(shí)現(xiàn)雙鏡像(或多鏡像)切換的方案。它允許在FPGA中加載兩個(gè)不同的配置鏡像,并在需要時(shí)切換。

2024-02-25 10:54:32 2399

2399

。Ultrascale+采用16ns,有3個(gè)系列:Artix,Kintex,Virtex。不僅是工藝制程方面,在其他方面也存在較大改進(jìn),如時(shí)鐘資源與架構(gòu),本文將重點(diǎn)介紹Ultrascale的時(shí)鐘資源與架構(gòu),Ultrascale+和Ultrascale大體上相似。

2025-04-24 11:29:01 2264

2264

Xilinx7系列普及講座內(nèi)容請(qǐng)下載附件pdf,更多內(nèi)容請(qǐng)登錄www.rocetech.com

2013-03-31 14:20:25

Xilinx7系列普及講座內(nèi)容請(qǐng)下載附件pdf,更多內(nèi)容請(qǐng)登錄www.rocetech.com

2013-03-31 14:27:04

Xilinx7系列普及講座內(nèi)容請(qǐng)下載附件pdf,更多內(nèi)容請(qǐng)登錄www.rocetech.com

2013-03-31 14:09:45

你好我嘗試使用xilinx 7系列收發(fā)器IP生成器示例(Vivdao提供)Thegt0_qplllock_in,gt0_qplloutclk_in,gt0_qplloutrefclk_in

2018-11-05 11:34:22

嗨,我想了解7系列收發(fā)器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

Xilinx 7系列FPGA簡介--選型參考

2021-02-01 06:10:55

1特點(diǎn) Xilinx 7 系列的提供的bank分為HP(High-performance)和HR(High-range)。HP主要為了滿足高速內(nèi)存的性能要求以及其他chip-to-chip接口

2020-12-23 17:17:47

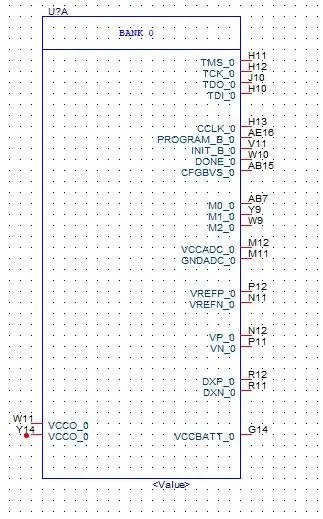

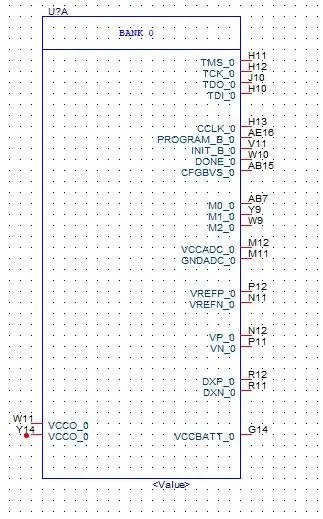

:Xilinx 7系列FPGA管腳是如何定義的原理圖設(shè)計(jì)時(shí)如何下載FPGA管腳文件(Pinout文件)1.Xilinx7系列FPGA管腳定義表1-1、Xilinx 7系列FPGA管腳定義FPGA的器件管腳

2021-05-28 09:23:25

:Xilinx 7系列FPGA管腳是如何定義的原理圖設(shè)計(jì)時(shí)如何下載FPGA管腳文件(Pinout文件)1.Xilinx7系列FPGA管腳定義表1-1、Xilinx 7系列FPGA管腳定義FPGA的器件管腳

2021-07-08 08:00:00

Xilinx_A7_K7_V7系列Cadence符號(hào)庫及PCB庫

2021-01-28 06:39:41

xilinx公司的7系列FPGA應(yīng)用指南

2012-08-14 12:17:40

前言TLK7-EVM是一款由廣州創(chuàng)龍基于Xilinx Kintex-7系列FPGA自主研發(fā)的核心板+底板方式的開發(fā)板,可快速評(píng)估FPGA性能。核心板尺寸僅80mm*58mm,底板采用沉金無鉛工藝的6

2020-09-24 16:46:18

TLK7-EVM是一款由廣州創(chuàng)龍基于Xilinx Kintex-7系列FPGA自主研發(fā)的核心板+底板方式的開發(fā)板,可快速評(píng)估FPGA性能。核心板尺寸僅80mm*58mm,底板采用沉金無鉛工藝的6層板

2020-09-16 10:40:31

:1、Xilinx A7系列FPGA芯片與S6系列FPGA芯片的對(duì)比2、Vivado軟件安裝與介紹3、使用Vivado 編寫Verilog代碼進(jìn)行開發(fā)數(shù)字邏輯開發(fā)和驗(yàn)證的全流程4、使用Vivado軟件

2016-10-11 18:15:20

丑。大神勿噴。因有小伙伴想學(xué)習(xí)Xilinx的FPGA,現(xiàn)在打算拿出兩塊板子,和有需要的朋友交換一下。現(xiàn)在只打算換Xilinx的FPGA的板子,這里再簡單介紹一下板子上面的資源,或者可以實(shí)現(xiàn)的資源:1

2015-06-19 21:38:36

引言:本文我們介紹Xilinx 7系列FPGA收發(fā)器硬件設(shè)計(jì)主要注意的一些問題,指導(dǎo)硬件設(shè)計(jì)人員進(jìn)行原理圖及PCB設(shè)計(jì)。本文介紹以下內(nèi)容:GTX/GTH收發(fā)器管腳概述GTX/GTH收發(fā)器時(shí)鐘

2021-11-11 07:42:37

全局時(shí)鐘資源怎么使用?全局時(shí)鐘資源的例化方法有哪幾種?

2021-05-06 07:28:18

RAM)的時(shí)延和抖動(dòng)都為最小。為了適應(yīng)復(fù)雜設(shè)計(jì)的需要,Xilinx的FPGA中集成的專用時(shí)鐘資源與數(shù)字延遲鎖相環(huán)(DLL)的數(shù)目不斷增加,最新的Virtex II器件最多可以提供16個(gè)全局時(shí)鐘輸入端口和8

2019-10-22 06:01:34

賽靈思(XILINX)全新7系列FPGA詳述

2012-08-14 12:20:22

典型應(yīng)用以及芯片未來展望等方面,深入闡述工程師選擇Xilinx FPGA芯片的理由。 理由1 業(yè)界性價(jià)比之王 賽靈思的最新7系列FPGA芯片包括3個(gè)子系列,Artix-7、 Kintex-7

2012-09-06 16:24:35

XC7A100T-2FGG484I是賽靈思(Xilinx)公司Artix-7系列FPGA的一款產(chǎn)品。以下是關(guān)于該型號(hào)的主要信息和應(yīng)用領(lǐng)域: ## 主要信息 - 屬于Artix-7

2024-04-06 20:36:22

XC7K70T-2FBG484I是AMD/Xilinx公司生產(chǎn)的Kintex-7系列FPGA,具有以下主要信息: 1. 邏輯資源: - 65,600個(gè)可配置邏輯塊

2024-04-06 20:38:20

XC6SLX9-2TQG144C是AMD/Xilinx公司生產(chǎn)的Spartan-6 LX系列FPGA,具有以下主要信息:1. 邏輯資源: - 9,152個(gè)邏輯單元2. 封裝形式: 144

2024-04-06 20:39:41

目前,大型設(shè)計(jì)一般推薦使用同步時(shí)序電路。同步時(shí)序電路基于時(shí)鐘觸發(fā)沿設(shè)計(jì),對(duì)時(shí)鐘的周期

2010-11-03 16:24:44 121

121 MYC-J7A100T核心板及開發(fā)板Xilinx Artix-7系列XC7A100T開發(fā)平臺(tái),F(xiàn)PGA工業(yè)芯XC7A100T-2FGG484I具有高度的可編程性和靈活性;高速傳輸和處理,具有285個(gè)

2024-05-31 15:28:07

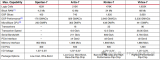

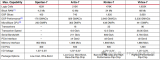

本文是關(guān)于 xilinx公司的7系列FPGA應(yīng)用指南。xilinx公司的7系列FPGA包括3個(gè)子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對(duì)這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對(duì)比表

2012-08-07 17:22:55 201

201 全新賽靈思(Xilinx)FPGA 7系列芯片精彩剖析:賽靈思的最新7系列FPGA芯片包括3個(gè)子系列,Artix-7、 Kintex-7和Virtex-7。在介紹芯片之前,先看看三個(gè)子系列芯片的介紹表,如下表1所示: 表

2012-08-08 15:04:04 396

396 如何正確使用FPGA的時(shí)鐘資源

2017-01-18 20:39:13 22

22 當(dāng)Xilinx 7Series FPGA中,存在3種主要的時(shí)鐘網(wǎng)絡(luò):BUFG,BUFR,BUFIO以及他們所衍生出的各種變種。那么他們有什么主要特點(diǎn)和區(qū)別呢? BUFIO是IO時(shí)鐘網(wǎng)絡(luò),顧名思義,它

2017-02-08 05:31:40 3409

3409

使用, 而且從性能上講也比消耗邏輯資源的FIFO性能要好一點(diǎn)。XILINX 7系列中的FIFO是支持同步和異步讀寫操作,不需要時(shí)鐘和數(shù)據(jù)之間有一個(gè)相位的便宜。空信號(hào),滿信號(hào),和可以編程的空滿信號(hào)都可以被用作控制FIFO的信號(hào),從而可以實(shí)現(xiàn)不同的功能。同步FIFO可以消除異步FIFO的固有的

2017-02-08 08:18:37 644

644

寫寫代碼,調(diào)調(diào)時(shí)序的小工程師的級(jí)別。我想,這應(yīng)該不是我們所有年輕人的一個(gè)追求。 1.1 CLB的初探 首先CLB的最基本資源分為兩種,一種是實(shí)現(xiàn)組合邏輯資源功能的,一般稱為LUT。XILINX的LUT是6輸入查找表。一種是Flip-flop,也就是經(jīng)常聽課大家聽說的FF,我就

2017-02-08 10:10:34 496

496

1. Xilinx 時(shí)鐘資源 xilinx 時(shí)鐘資源分為兩種:全局時(shí)鐘和第二全局時(shí)鐘。 1. 全局時(shí)鐘資源 Xilinx 全局時(shí)鐘采用全銅工藝實(shí)現(xiàn),并設(shè)計(jì)了專用時(shí)鐘緩沖與驅(qū)動(dòng)結(jié)構(gòu),可以到達(dá)芯片內(nèi)部

2017-02-09 08:43:41 2076

2076 7系列FPGA是Xilinx新推出的基于28nm工藝的FPGA,其中包含三個(gè)系列:Artix、Kintex和Virtex。因項(xiàng)目要使用kintex7為平臺(tái)做設(shè)計(jì),需要對(duì)其內(nèi)部結(jié)構(gòu)做了研究,首先從CLB(Configurable Logic Block)開始

2017-02-10 16:13:38 5726

5726

在 Xilinx 系列 FPGA 產(chǎn)品中,全局時(shí)鐘網(wǎng)絡(luò)是一種全局布線資源,它可以保證時(shí)鐘信號(hào)到達(dá)各個(gè)目標(biāo)邏輯單元的時(shí)延基本相同。其時(shí)鐘分配樹結(jié)構(gòu)如圖1所示。 圖1.Xilinx FPGA全局時(shí)鐘分配

2017-11-22 07:09:36 12586

12586

目前,大型設(shè)計(jì)一般推薦使用同步時(shí)序電路。同步時(shí)序電路基于時(shí)鐘觸發(fā)沿設(shè)計(jì),對(duì)時(shí)鐘的周期、占空比、延時(shí)和抖動(dòng)提出了更高的要求。為了滿足同步時(shí)序設(shè)計(jì)的要求,一般在FPGA設(shè)計(jì)中采用全局時(shí)鐘資源驅(qū)動(dòng)設(shè)計(jì)的主時(shí)鐘,以達(dá)到最低的時(shí)鐘抖動(dòng)和延遲。

2017-11-25 01:43:01 2136

2136 Xilinx 7系列FPGA的HP bank都支持DCI,目的是在高速單板信號(hào)傳輸中保持信號(hào)完整性,減少反射等因素影響,那么DCI是什么?digitally controlled impedance

2018-06-27 09:11:00 21240

21240

首次演示新型Xilinx 7系列GTH收發(fā)器,通過背板以13.1 Gb / s的速度運(yùn)行。

2019-01-03 13:25:38 4916

4916 該視頻介紹了7系列FPGA中的片式觸發(fā)器資源。

討論如何設(shè)計(jì)您的設(shè)備觸發(fā)器控制信號(hào)資源以及您的HDL編碼風(fēng)格如何影響您的設(shè)備的速度和設(shè)備利用率的含義...

2018-11-26 06:05:00 3632

3632 嵌入式世界2012的Xilinx 7系列模擬混合信號(hào)評(píng)估平臺(tái)演示

2018-11-22 06:24:00 3726

3726 本文檔的主要內(nèi)容詳細(xì)介紹的是Xilinx所有可編程7系列產(chǎn)品選擇指南資料免費(fèi)下載。包括:1.SPARTAN-7 FPGA,2.ARTIX-7 FPGA,3.KNTEX-7 FPGA,4.VIETEX-7 FPGA

2019-02-22 11:47:29 9

9 Xilinx 7系列FPGA包括四個(gè)可滿足全系列系統(tǒng)需求的FPGA系列,從低成本、小尺寸、成本敏感、大容量應(yīng)用到超高端連接帶寬、邏輯容量和信號(hào)處理能力,滿足最苛刻的高性能應(yīng)用。7系列FPGA包括:

2019-02-25 16:43:37 81

81 些大材小用,因此xilinx公司在其FPGA內(nèi)部專門集成了很多存儲(chǔ)器模塊,稱作Block RAM,其猶如slice海洋當(dāng)中的一顆顆明珠,專門實(shí)現(xiàn)數(shù)據(jù)暫存功能,且每個(gè)時(shí)鐘區(qū)域都布置了若干個(gè)Block

2020-11-23 14:08:43 9097

9097

Xilinx 7系列FPGA概覽 文章目錄 Xilinx 7系列FPGA概覽 1.Xilinx的四個(gè)工藝級(jí)別 2.Virtex、Kintex、Artix和Spartan 3.7系列特點(diǎn) 4.7系列

2020-11-13 18:03:30 16550

16550 Xilinx7系列FPGA包括四個(gè)FPGA系列,它們都是為最低功耗而設(shè)計(jì)的,以使一個(gè)通用設(shè)計(jì)能夠跨系列擴(kuò)展以獲得最佳的功率、性能和成本。斯巴達(dá)?-7系列是7系列產(chǎn)品中密度最低、成本最低的入門級(jí)產(chǎn)品

2020-12-09 14:49:00 25

25 Xilinx7系列FPGA包括四個(gè)FPGA系列,它們都是為最低功耗而設(shè)計(jì)的,以使一個(gè)通用設(shè)計(jì)能夠跨系列擴(kuò)展以獲得最佳的功率、性能和成本。斯巴達(dá)?7系列是7系列產(chǎn)品中密度最低、成本最低的入門級(jí)產(chǎn)品

2020-12-09 14:49:00 6

6 區(qū)域(Region):每個(gè)FPGA器件被分為多個(gè)區(qū)域,不同的型號(hào)的器件區(qū)域數(shù)量不同。

FPGA時(shí)鐘資源主要有三大類:時(shí)鐘管理模、時(shí)鐘IO、時(shí)鐘布線資源。

時(shí)鐘管理模塊:不同廠家及型號(hào)的FPGA中

2020-12-09 14:49:03 21

21 Xilinx7系列FPGA包括四個(gè)FPGA系列,它們都是為最低功耗而設(shè)計(jì)的,以使一個(gè)通用設(shè)計(jì)能夠跨系列擴(kuò)展以獲得最佳的功率、性能和成本。斯巴達(dá)?-7系列是7系列產(chǎn)品中密度最低、成本最低的入門級(jí)產(chǎn)品

2020-12-09 15:31:13 10

10 Xilinx7系列FPGA的體系結(jié)構(gòu)具有靈活的內(nèi)部內(nèi)存資源,可以配置為各種不同的大小。本白皮書詳細(xì)介紹了可用的功能,說明了各種可用內(nèi)存大小,并顯示了使用不同資源執(zhí)行不同大小內(nèi)存功能的利弊。

2020-12-09 16:15:00 8

8 Xilinx7系列FPGA包括四個(gè)FPGA系列,它們都是為最低功耗而設(shè)計(jì)的,以使一個(gè)通用設(shè)計(jì)能夠跨系列擴(kuò)展以獲得最佳的功率、性能和成本。斯巴達(dá)-7系列是7系列產(chǎn)品中密度最低、成本最低的入門級(jí)產(chǎn)品

2020-12-10 14:20:00 18

18 本章介紹了高云半導(dǎo)體FPGA 產(chǎn)品的時(shí)鐘資源,包括專用的時(shí)鐘輸入、緩沖區(qū)和布線資源。時(shí)鐘的基礎(chǔ)設(shè)施提供了一系列低電容、低偏移互連線,非常適合承載高頻信號(hào),最大限度地減少時(shí)鐘偏差和提高性能,可應(yīng)用于所有的時(shí)鐘信號(hào)。

2020-12-10 14:20:13 9

9 Xilinx7系列FPGA包括四個(gè)FPGA系列,它們都是為最低功耗而設(shè)計(jì)的,以使一個(gè)通用設(shè)計(jì)能夠跨系列擴(kuò)展以獲得最佳的功率、性能和成本。斯巴達(dá)?-7系列是7系列產(chǎn)品中密度最低、成本最低的入門級(jí)產(chǎn)品

2020-12-10 15:27:48 24

24 全局時(shí)鐘資源是一種專用互連網(wǎng)絡(luò),它可以降低時(shí)鐘歪斜、占空比失真和功耗,提高抖動(dòng)容限。Xilinx的全局時(shí)鐘資源設(shè)計(jì)了專用時(shí)鐘緩沖與驅(qū)動(dòng)結(jié)構(gòu),從而使全局時(shí)鐘到達(dá)CLB、IOB和BRAM的延時(shí)最小。

2020-12-29 16:59:35 8

8 所有的7系列FPGA都有可配置的SelectIO驅(qū)動(dòng)器和接收器,支持各種標(biāo)準(zhǔn)接口;可以通過編程控制輸出強(qiáng)度、壓擺率、片內(nèi)阻抗以及生成內(nèi)部參考電壓(INTERNAL_VERF)。

2020-12-29 17:27:26 11

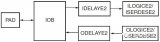

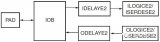

11 本篇咱們接著介紹I/O邏輯資源,先貼上兩張圖。圖1為HPBANK的I/O模塊,圖2為HRBANK的I/O模塊,兩者區(qū)別在于后者無ODELAYE模塊。

2020-12-29 17:27:00 3

3 本文檔的主要內(nèi)容詳細(xì)介紹的是Xilinx 7 系列FPGA中的Serdes總結(jié)。

2020-12-31 17:30:58 26

26 Xilinx_A7_K7_V7系列Cadence符號(hào)庫及PCB庫,包含的型號(hào)有XC7A100T-1FGG484I;XC7A200T-1FBG676I;XC7K325T-2FFG900I;XC7K410T-2FFG900I;XC7VX690T-2FFG1927I。原理圖符號(hào)按照BANK建立,很規(guī)范。

2022-02-08 14:13:59 4142

4142

Xilinx_A7_K7_V7系列Cadence符號(hào)庫及PCB庫,包含的型號(hào)有XC7A100T-1FGG484I;XC7A200T-1FBG676I;XC7K325T-2FFG900I;XC7K410T-2FFG900I;XC7VX690T-2FFG1927I。原理圖符號(hào)按照BANK建立,很規(guī)范。

2021-01-26 09:51:00 158

158 Xilinx-7系列FPGA主要包括:Spartan?-7、Artix?-7、Kintex?-7、Virtex?-7。其性能、密度、價(jià)格也隨著系列的不同而提升。和前幾代FPGA產(chǎn)品不同的是,7系列

2021-01-30 06:00:11 21

21 Xilinx 7系列FPGA由四類FPGA系列組成,解決了從低成本、小尺寸、成本敏感、高容量應(yīng)用到最苛刻的高性能應(yīng)用的超高端連接帶寬、邏輯容量和信號(hào)處理能力等完整的系統(tǒng)需求。 首先我們先看

2021-03-09 11:44:22 8099

8099 同步接口設(shè)計(jì)特別有用。7系列器件中的I/O Bank與時(shí)鐘區(qū)域的大小相同。為了理解區(qū)域時(shí)鐘是如何工作的,理解區(qū)域時(shí)鐘信號(hào)的信號(hào)路徑是很重要的。7系列設(shè)備中的區(qū)域時(shí)鐘資源和網(wǎng)絡(luò)由以下路徑和組件組成: 時(shí)鐘輸入I/O I/O時(shí)鐘緩沖器:BUFIO 區(qū)域時(shí)

2021-03-22 09:47:30 6215

6215

支持非常高頻率的信號(hào)。了解全局時(shí)鐘的信號(hào)路徑可以擴(kuò)展對(duì)各種全局時(shí)鐘資源的理解。全局時(shí)鐘資源和網(wǎng)絡(luò)由以下路徑和組件組成: 時(shí)鐘樹和網(wǎng)絡(luò):GCLK 時(shí)鐘區(qū)域 全局時(shí)鐘緩沖器 1. 時(shí)鐘樹和網(wǎng)絡(luò):GCLK 7系列FPGA時(shí)鐘樹設(shè)計(jì)用于低偏差和低功

2021-03-22 10:09:58 14973

14973

是最佳的,然后通過使用適當(dāng)?shù)腎/O和時(shí)鐘緩沖器來訪問這些時(shí)鐘路由資源。該章節(jié)包括: 時(shí)鐘緩沖選擇考慮 時(shí)鐘輸入管腳 1.時(shí)鐘緩沖器選擇考慮 7系列FPGA擁有豐富的時(shí)鐘資源。各種緩沖器類型、時(shí)鐘輸入管腳和時(shí)鐘連接,可以滿足許多不同的應(yīng)用需求

2021-03-22 10:16:18 6115

6115

引言:從本文開始,我們陸續(xù)介紹Xilinx 7系列FPGA的時(shí)鐘資源架構(gòu),熟練掌握時(shí)鐘資源對(duì)于FPGA硬件設(shè)計(jì)工程師及軟件設(shè)計(jì)工程師都非常重要。本章概述7系列FPGA時(shí)鐘,比較了7系列FPGA時(shí)鐘

2021-03-22 10:25:27 6070

6070 引言: 我們?cè)谶M(jìn)行FPGA原理圖和PCB設(shè)計(jì)時(shí),都會(huì)涉及到FPGA芯片管腳定義和封裝相關(guān)信息,本文就Xilinx 7系列FPGA給出相關(guān)參考,給FPGA硬件開發(fā)人員提供使用。通過本文,可以了解到:

2021-05-01 09:47:00 11807

11807

我們?cè)谶M(jìn)行FPGA原理圖和PCB設(shè)計(jì)時(shí),都會(huì)涉及到FPGA芯片管腳定義和封裝相關(guān)信息,本文就Xilinx 7系列FPGA給出相關(guān)參考,給FPGA硬件開發(fā)人員提供使用。

2021-04-27 10:45:29 9045

9045

XILINX ARTIX7系列FPGA芯片產(chǎn)品目錄

2021-10-08 17:09:20 27

27 下電源軌:1,VCCINTFPGA內(nèi)部核心電壓。其不損壞FPGA器件的范圍為-0.5V~1.1V。對(duì)于-2和-1的spartan7系列,正常工作電壓為0.95V~1.05V,推薦工作電壓為1.00V。對(duì)于 -1L的spartan7系列,正常工作電壓為0.92V~0.98V...

2021-11-06 19:51:00 20

20 引言:本文我們介紹Xilinx 7系列FPGA收發(fā)器硬件設(shè)計(jì)主要注意的一些問題,指導(dǎo)硬件設(shè)計(jì)人員進(jìn)行原理圖及PCB設(shè)計(jì)。本文介紹以下內(nèi)容:GTX/GTH收發(fā)器管腳概述 GTX/GTH收發(fā)器時(shí)鐘

2021-11-06 19:51:00 35

35 HROW:水平時(shí)鐘線,從水平方向貫穿每個(gè)時(shí)鐘區(qū)域的中心區(qū)域,將時(shí)鐘區(qū)域分成上下完全一致的兩部分。全局時(shí)鐘線進(jìn)入每個(gè)時(shí)鐘區(qū)域的邏輯資源時(shí),必須經(jīng)過水平時(shí)鐘線。

2022-06-13 10:07:26 2543

2543 ?xilinx 的 FPGA 時(shí)鐘結(jié)構(gòu),7 系列 FPGA 的時(shí)鐘結(jié)構(gòu)和前面幾個(gè)系列的時(shí)鐘結(jié)構(gòu)有了很大的區(qū)別,7系列的時(shí)鐘結(jié)構(gòu)如下圖所示。

2022-07-03 17:13:48 4699

4699 電子發(fā)燒友網(wǎng)站提供《Xilinx Zynq 7000系列(XC7Z015)電源解決方案.zip》資料免費(fèi)下載

2022-09-08 09:20:52 12

12 電子發(fā)燒友網(wǎng)站提供《Logos系列FPGA時(shí)鐘資源(Clock)用戶指南.pdf》資料免費(fèi)下載

2022-09-26 10:15:21 11

11 電子發(fā)燒友網(wǎng)站提供《Compact系列CPLD時(shí)鐘資源(Clock/PLL)用戶指南 .pdf》資料免費(fèi)下載

2022-09-26 10:03:33 7

7 XILINX是可編程邏輯芯片,由多個(gè)系列的性能可以滿足一般的邏輯設(shè)計(jì)要求,如賽靈思7系列,Xilinx?7系列FPGA由四個(gè)FPGA系列組成 7A 7V 7S 7K,可滿足各種系統(tǒng)要求,從低

2022-11-03 14:39:54 3344

3344 本文介紹了Xilinx Zynq-7000系列XC7Z035/XC7Z045系列主要特性,資源框圖及PS端ETH RJ45接口引腳說明

2022-11-21 09:17:10 4663

4663

業(yè)界高端FPGA的卓越性能和高口碑聲譽(yù)都有哪些因素了?其中很重要的一個(gè)因素就是FPGA內(nèi)部豐富的時(shí)鐘資源使得FPGA在處理復(fù)雜時(shí)鐘結(jié)構(gòu)和時(shí)序要求的設(shè)計(jì)中具有很大優(yōu)勢(shì)。設(shè)計(jì)師可以更好地控制和管理時(shí)鐘信號(hào),提高時(shí)序性能、減少時(shí)鐘相關(guān)問題,并滿足設(shè)計(jì)的高性能和穩(wěn)定性要求。

2023-08-31 10:44:01 1538

1538 電子發(fā)燒友網(wǎng)站提供《7系列FPGA Select IO資源用戶指南.pdf》資料免費(fèi)下載

2023-09-15 10:26:12 3

3 Xilinx是一家專業(yè)的可編程邏輯器件(PLD)廠商,其產(chǎn)品包括FPGA、CPLD、SOC等。Xilinx的FPGA產(chǎn)品線有多個(gè)系列,其中7系列和Ultrascale系列是比較常見的兩種。那么,這兩個(gè)系列有什么區(qū)別呢?

2023-09-15 14:44:54 9018

9018

如果FPGA沒有外部時(shí)鐘源輸入,可以通過調(diào)用STARTUP原語,來使用FPGA芯片內(nèi)部的時(shí)鐘和復(fù)位信號(hào),Spartan-6系列內(nèi)部時(shí)鐘源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 3484

3484

Xilinx 7系列芯片應(yīng)用非常廣泛,具有成本低、性能強(qiáng)悍、成熟穩(wěn)定的特點(diǎn),目前Xilinx(AMD)已延長該系列芯片的生命周期至少到2035年。

2023-11-27 09:26:10 1804

1804

Xilinx 7系列 芯片 應(yīng)用非常廣泛,具有成本低、性能強(qiáng)悍、成熟穩(wěn)定的特點(diǎn),目前Xilinx( AMD )已延長該系列芯片的生命周期至少到2035年。 本文主要介紹Xilinx 7系列 FPGA

2023-11-28 10:20:02 2842

2842

Xilinx7系列FPGA由四個(gè)FPGA系列組成,可滿足一系列系統(tǒng)需求,從低成本、小尺寸、成本敏感的大容量應(yīng)用到最苛刻的高性能應(yīng)用的超高端連接帶寬、邏輯容量和信號(hào)處理能力。

2024-04-22 10:49:49 9207

9207

本文我們介紹下Xilinx SelectIO資源內(nèi)部IDELAYE2資源應(yīng)用。IDELAYE2原句配合IDELAYCTRL原句主要用于在信號(hào)通過引腳進(jìn)入芯片內(nèi)部之前,進(jìn)行延時(shí)調(diào)節(jié),一般高速端口信號(hào)由于走線延時(shí)等原因,需要通過IDELAYE2原語對(duì)數(shù)據(jù)做微調(diào),實(shí)現(xiàn)時(shí)鐘與數(shù)據(jù)的源同步時(shí)序要求。

2024-04-26 11:33:29 4628

4628

本文介紹下Xilinx ZYNQ 7000系列SoC的功能特性、資源特性、封裝兼容性以及如何訂購器件。

2024-10-24 15:04:52 4025

4025

Xilinx7系列FPGA集成了新一代PCI Express集成塊,支持8.0Gb/s數(shù)據(jù)速率的PCI Express 3.0。本文介紹了7系列FPGA PCIe Gen3的應(yīng)用接口及一些特性。

2024-11-05 15:45:10 4694

4694

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論