如何通過(guò)仿真有效提高數(shù)模混合設(shè)計(jì)性

一 、數(shù)模混合設(shè)計(jì)的難點(diǎn) 二、提高數(shù)模混合電路性能的關(guān)鍵 三、仿真工具在數(shù)模混合設(shè)計(jì)中的應(yīng)用 四、小結(jié) 五、混合信號(hào)PC

2009-08-01 19:28:17 1928

1928

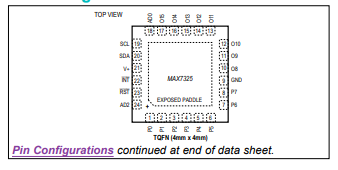

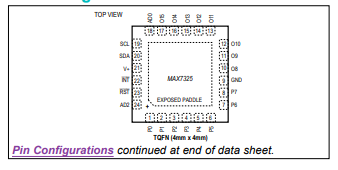

MAX7325 2線串行接口外設(shè)具有16路I/O端口。其中8路為推挽輸出,另外8路為I/O端口,帶有可選擇的內(nèi)部上拉和瞬態(tài)檢測(cè)功能。

2012-11-02 09:47:03 2263

2263

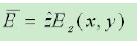

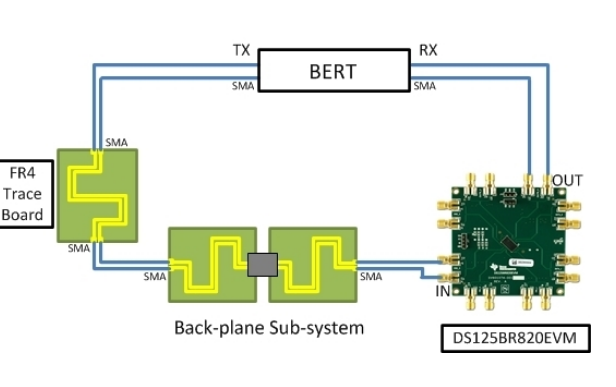

對(duì)信號(hào)完整性工程師而言,高速串行鏈路仿真是功能強(qiáng)大的工具。這些仿真可讓設(shè)計(jì)人員大致了解系統(tǒng)性能預(yù)測(cè),使他們?cè)趯⒃O(shè)計(jì)交付耗資巨大的電路板生產(chǎn)之前更容易做出正確決定以達(dá)到設(shè)計(jì)目標(biāo)。 TI的WEBENCH

2018-04-23 09:31:45 7295

7295

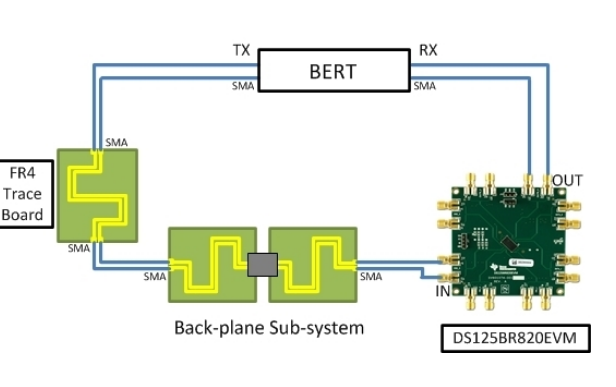

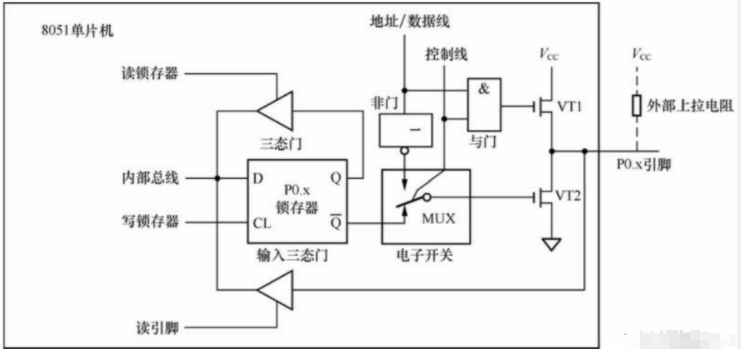

單片機(jī)的I/O端口是輸入信號(hào)和輸出信號(hào)的通道。8051單片機(jī)有P0、P1、P2、P3四組I/O 端口,每組端口有8個(gè)引腳。

2022-08-05 16:18:40 14395

14395

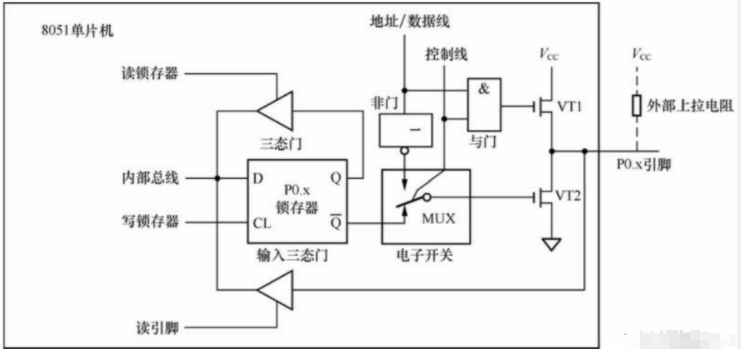

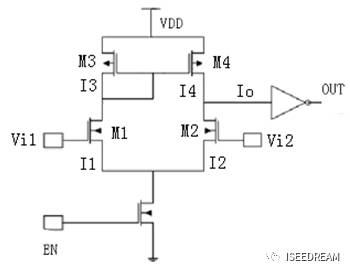

在高速I/O電路設(shè)計(jì)中,輸入I/O的比較器是一個(gè)非常重要的模塊。

2023-10-30 15:02:05 2774

2774

數(shù)據(jù)和時(shí)鐘的關(guān)系。因此,LatticeSC FPGA可以實(shí)現(xiàn)可靠的源同步接口,運(yùn)行的數(shù)據(jù)傳輸速率可達(dá)2Gbps。為了使輸入的數(shù)據(jù)速率與FPGA的運(yùn)行速度相匹配,I/O引腳還提供了一個(gè)變速功能,可將進(jìn)入

2018-11-26 11:17:24

FPGA仿真有什么方法?(1)交互式仿真方法:利用EDA工具的仿真器進(jìn)行仿真,使用方便,但輸入輸出不便于記錄規(guī)檔,當(dāng)輸入量較多時(shí)不便于觀察和比較。(2)測(cè)試平臺(tái)法:為設(shè)計(jì)模塊專門(mén)設(shè)計(jì)的仿真程序,可以實(shí)現(xiàn)對(duì)被測(cè)模塊自動(dòng)輸入測(cè)試矢量,并通過(guò)波形輸出文件記錄輸出,便于將仿真結(jié)果記錄歸檔和比較。

2019-08-30 07:13:54

上。(特權(quán)同學(xué),版權(quán)所有)●差分信號(hào)對(duì)必須分配到支持差分傳輸的專用引腳上。(特權(quán)同學(xué),版權(quán)所有)●高速信號(hào)分配到支持高速傳輸的專用引腳上,如支持DDR的專用I/O接口。(特權(quán)同學(xué),版權(quán)所有)●一些硬核

2019-04-12 06:35:33

評(píng)估其內(nèi)部資源是否足夠支持SATA接口的設(shè)計(jì)。包括邏輯單元、內(nèi)存塊、I/O端口等資源的數(shù)量,以及是否有足夠的SerDes(串行解串器)資源用于高速數(shù)據(jù)傳輸。

時(shí)鐘配置 :

SATA接口使用高速串行傳輸

2024-05-27 16:20:22

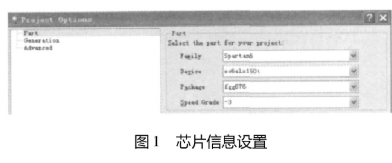

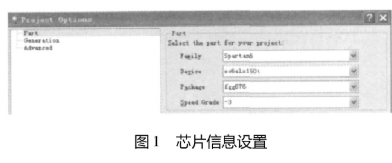

行,速度快。Xilinx Spartan-7 FPGA器件適用于那些成本敏感型應(yīng)用。它采用小型封裝卻擁有高比例的I/O數(shù)量,單位功耗性價(jià)比相較前代產(chǎn)品提升多達(dá)四倍,可提供靈活的連接能力、接口橋接和輔助芯片

2018-08-02 09:37:08

這里寫(xiě)目錄標(biāo)題I/O端口原理單片機(jī)知識(shí)點(diǎn)補(bǔ)充實(shí)戰(zhàn)1——閃爍LED指示燈I/O端口原理I/O英文全稱是 Input/Output,即輸入/輸出。單片機(jī)端口是標(biāo)準(zhǔn)雙向口,就是說(shuō),單片機(jī)的端口既可以

2022-01-20 07:55:51

所要求的串行時(shí)鐘速率,由于裸片和封裝尺寸及占據(jù)的板空間較小,這種方案可以節(jié)省大量成本。同時(shí),信號(hào)線數(shù)量的減少也會(huì)降低PCB布線的難度,進(jìn)而降低了信號(hào)完整性的挑戰(zhàn)。 但即使是現(xiàn)有的I/O標(biāo)準(zhǔn)也面臨著挑戰(zhàn)

2019-05-20 05:00:07

receiver transmitter,USART),同步和異步模式 總線選擇所采用的標(biāo)準(zhǔn):1.元件只能通過(guò)一種總線提供2. MCU上可用的總線:a. SPI和I2C或同步串行端口

2019-06-06 05:00:36

使用LabVIEW FPGA 模塊和可重新配置I/O 設(shè)備開(kāi)發(fā)測(cè)量與控制應(yīng)用通過(guò)使用LabVIEW FPGA 模塊和可重新配置I/O(RIO)硬件,NI 為您提供了一種直觀可用的解決方案,它可以將

2009-07-23 08:15:57

本文檔指定了一個(gè)串行傳輸端口(STP)來(lái)替代現(xiàn)有的并行數(shù)據(jù)輸出端口適用于在芯片外傳輸高帶寬數(shù)據(jù),例如來(lái)自ARM的嵌入式跟蹤宏單元。這將更低的ASIC引腳數(shù),增加可能的帶寬,并且在某些情況下,減少硅

2023-08-02 06:45:51

高速DAP仿真器 BURNER

2023-03-28 13:06:20

隨著通信系統(tǒng)中高速板設(shè)計(jì)復(fù)雜性的日益提高,依賴某一種特定的CAD工具已經(jīng)無(wú)法在可接受的精度范圍內(nèi)完成整個(gè)設(shè)計(jì)仿真。PCB設(shè)計(jì)工程師和信號(hào)完整性(SI)設(shè)計(jì)工程師需要采用各種仿真工具。除了價(jià)格、性能

2014-12-12 16:14:49

:通過(guò)優(yōu)化電路設(shè)計(jì)與散熱結(jié)構(gòu),降低系統(tǒng)設(shè)計(jì)復(fù)雜度,提升整體能效。一站式配套服務(wù)完整解決方案:提供電源模塊+旋變信號(hào)轉(zhuǎn)換+EtherCAT從站遠(yuǎn)程I/O的一站式配套服務(wù),降低客戶開(kāi)發(fā)成本與周期。多領(lǐng)域適配性:適用于工業(yè)自動(dòng)化、機(jī)器人、電機(jī)控制、高精度工業(yè)儀器設(shè)備等多個(gè)領(lǐng)域,滿足不同場(chǎng)景的嚴(yán)苛需求。

2025-11-05 09:50:40

中,都要保證每個(gè)Dword的正確性和完整性,否則將導(dǎo)致數(shù)據(jù)出錯(cuò)或原語(yǔ)流失。另外,目前高速數(shù)據(jù)傳輸接口或總線常用8B/10B編碼來(lái)編碼,其根本目的是實(shí)現(xiàn)直流平衡(DC Balance)。當(dāng)高速串行流

2018-12-11 11:04:22

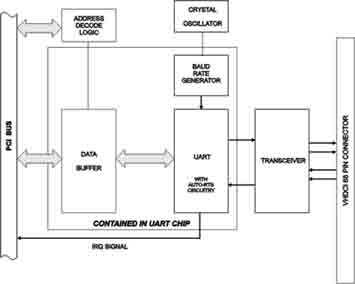

描述SBC-85 串并 I/O 板該板有四個(gè) I/O 設(shè)備:一個(gè) Intel 8255 PPI,提供三個(gè) 8 位可編程 I/O 端口;一個(gè) Intel 8251 USART,用于 RS232 串行

2022-08-31 06:06:10

在電子產(chǎn)品設(shè)計(jì)中,為了截?cái)喈a(chǎn)品內(nèi)部電路與外界的干擾傳輸通道,或出于安全隔離的考慮,通常會(huì)在I/O端口或內(nèi)部電路信號(hào)傳輸過(guò)程中采用隔離的方式,這種隔離技術(shù)是EMC 中的重要技術(shù)之一,其主要目的是試圖

2021-11-11 06:32:19

的準(zhǔn)確性與穩(wěn)定性。2 系統(tǒng)硬件設(shè)計(jì)2.1 USB3.0高速傳輸模塊本設(shè)計(jì)采用的賽普拉斯EZ-USB FX3 CYUSB3014是新一代的USB 3.0外設(shè)控制器,其數(shù)據(jù)傳輸速率可達(dá)320MBps,具有

2018-08-09 14:18:42

串行總線。在眾多串行總線中,SPI 總線與I2C 總線、CAN 總線、USB 等其他常用總線相比有很大優(yōu)勢(shì),如SPI 總線的數(shù)據(jù)傳輸速度可達(dá)若干Mbps, 比I2C 總線快很多。SPI 總線最典型

2015-01-28 14:09:51

精準(zhǔn)的數(shù)據(jù)收發(fā)信息,更好的為工程項(xiàng)目服務(wù)。傳統(tǒng)的并行傳輸方式由于走線多、信號(hào)間串?dāng)_大等缺陷,無(wú)法突破自身的速度瓶頸。而串行傳輸擁有更高的傳輸速率但只需要少量的信號(hào)線,降低了板開(kāi)發(fā)成本和復(fù)雜度,滿足高頻率遠(yuǎn)距離的數(shù)據(jù)通信需求,被廣泛應(yīng)用到各種高速數(shù)據(jù)通信系統(tǒng)設(shè)計(jì)中。

2019-10-21 06:29:57

FPGA與專用芯片(比如AD/DA)之間的高速LVDS數(shù)據(jù)傳輸.本人非常熟悉AD接口,包括高速并行AD、串行AD,比如ADS5474,LTC2175,E2V高速AD等,基于FPGA設(shè)計(jì)高速并行/串行

2014-03-01 18:47:47

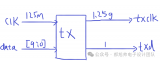

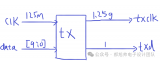

通信,就要使用主控制器的I/O口通過(guò)軟件來(lái)模擬,這就在很大程度上限制了其應(yīng)用且給數(shù)據(jù)傳輸帶來(lái)不便。在FPGA技術(shù)迅速發(fā)展的時(shí)代,解決這個(gè)問(wèn)題最方便的辦法就是集成一個(gè)SPI核到芯片上。這里根據(jù)業(yè)界通用

2019-05-28 05:00:05

一條物理鏈路的速度從600Mbps到10Gbps,高速I/O的測(cè)試和驗(yàn)證更成為傳統(tǒng)專注于FPGA內(nèi)部邏輯設(shè)計(jì)的設(shè)計(jì)人員所面臨的巨大挑戰(zhàn)。這些挑戰(zhàn)使設(shè)計(jì)人員非常容易地將絕大部分設(shè)計(jì)時(shí)間放在調(diào)試和檢驗(yàn)設(shè)計(jì)上。

2019-08-29 07:59:05

基于FPGA的通用高速串行互連協(xié)議設(shè)計(jì)基于FPGA的通用高速串行互連協(xié)議設(shè)計(jì)

2012-08-11 15:46:52

設(shè)計(jì)方法或經(jīng)驗(yàn)很難預(yù)測(cè)和保證信號(hào)的完整性,仿真已成為高速信號(hào)設(shè)計(jì)的必要手段。本文采用全電荷格林函數(shù)法結(jié)合矩量法對(duì)傳輸線提取分布參數(shù),建立等效時(shí)域網(wǎng)絡(luò)模型,應(yīng)用端接I/O緩沖器的IBIS瞬態(tài)行為模型

2018-08-27 16:00:07

引 言在高速的數(shù)據(jù)采集或傳輸中,目前使用較多的都是采用USB 2.0接口控制器和FPGA或DSP實(shí)現(xiàn)的,本設(shè)計(jì)在USB 2.0接口芯片CY7C68013的Slave FIFO模式下,利用FPGA作為

2021-06-24 07:00:00

多FPGA系統(tǒng)中自定義高速串行數(shù)據(jù)接口設(shè)計(jì)為方便多FPGA系統(tǒng)中主從FPGA之間的命令與數(shù)據(jù)傳輸,節(jié)省連接的引腳數(shù)量,設(shè)計(jì)了一種基于FPGA的自定義高速串行數(shù)據(jù)傳輸模塊。對(duì)主從串行模塊進(jìn)行了詳盡

2012-08-11 11:49:57

、rb12、rb13作為I/O端口。下面:無(wú)效init_pwm1

2019-10-21 12:16:33

您好,我正在使用VC707評(píng)估套件。我通過(guò)UART - > USB連接與FPGA連接。我想將ascii命令從FPGA發(fā)送到另一個(gè)設(shè)備,這比uart簡(jiǎn)單,但我已經(jīng)在使用它了。有沒(méi)有辦法使用以太網(wǎng)或micro u***端口進(jìn)行I / O?謝謝!

2019-09-16 14:39:50

嵌入式測(cè)試是什么?如何用FPGA技術(shù)去實(shí)現(xiàn)嵌入式設(shè)計(jì)?如何測(cè)試FPGA中的高速串行I/O?

2021-04-13 07:03:58

一定能夠滿足特殊 I/O 的需要。 近期最值得一提的技術(shù)躍進(jìn),即為適用于 PXI 的 NI FlexRIO 硬體;不僅整合了其他 NI 系統(tǒng)中的 LabVIEW FPGA 技術(shù),并具有開(kāi)放式的使用者客

2019-04-28 10:04:14

差等缺點(diǎn),難以滿足對(duì)高速寬帶信號(hào)采集和處理的要求。FPGA具有時(shí)鐘頻率高、速度快、采集實(shí)時(shí)性高、控制靈活等特點(diǎn),與A/D轉(zhuǎn)換器等外圍電路結(jié)合,更適于高速數(shù)字信號(hào)處理。光纖傳輸與電氣傳輸相比,具有傳輸

2019-09-02 06:01:52

本文介紹了基于Xilinx Virtex-6 FPGA的高速串行數(shù)據(jù)傳輸系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn),系統(tǒng)包含AXI DMA和GTX串行收發(fā)器,系統(tǒng)增加了流量控制機(jī)制來(lái)保證高速數(shù)據(jù)傳輸的可靠性。最后進(jìn)行了仿真測(cè)試,測(cè)試結(jié)果顯示系統(tǒng)可以高速可靠地傳輸數(shù)據(jù)。

2021-05-25 06:45:36

需要進(jìn)行調(diào)整,在采用這一方法晨這些問(wèn)題通常也已經(jīng)局部化了,只需要在PCB或FPGA設(shè)計(jì)中進(jìn)行很小的設(shè)計(jì)修改。

步驟1: 評(píng)估設(shè)計(jì)參數(shù)

那么,從哪里開(kāi)始呢? 首先應(yīng)當(dāng)盡早制定I/O分配策略。 但沒(méi)有優(yōu)化

2024-07-22 00:40:11

脈沖電鍍電源的優(yōu)越性及適用性:在脈沖導(dǎo)通期內(nèi),由于使用較高的電流密度,使晶核的形成速率遠(yuǎn)遠(yuǎn)大于原有晶體的生長(zhǎng)速率,因此可形成結(jié)晶細(xì)致的鍍層。鍍層結(jié)晶細(xì)致則密度大、硬度高、孔隙率低,即:大大提高鍍層

2011-11-17 17:14:58

輕松實(shí)現(xiàn)高速串行I/OFPGA應(yīng)用設(shè)計(jì)者指南輸入/輸出(I/O)在計(jì)算機(jī)和工業(yè)應(yīng)用中一直扮演著關(guān)鍵角色。但是,隨著信號(hào)處理越來(lái)越復(fù)雜,I/O通信會(huì)變得不可靠。在早期的并行I/O總線中,接口的數(shù)據(jù)對(duì)齊

2020-01-02 12:12:28

本文由Xilinx公司連接功能解決方案部市場(chǎng)營(yíng)銷經(jīng)理Abhijit Athavale編寫(xiě),針對(duì)FPGA高速串行I/O接口的實(shí)現(xiàn)進(jìn)行了全面而詳細(xì)的介紹,是FPGA設(shè)計(jì)人員不可多得的專業(yè)參考資料。

2020-01-28 08:45:42

如何通過(guò)仿真有效提高數(shù)模混合設(shè)計(jì)性:一 、數(shù)模混合設(shè)計(jì)的難點(diǎn) 二、提高數(shù)模混合電路性能的關(guān)鍵 三、仿真工具在數(shù)模混合設(shè)計(jì)中的應(yīng)用 四、小結(jié) 五、混合信號(hào)PCB設(shè)計(jì)基礎(chǔ)問(wèn)

2009-09-16 12:31:33 12

12 現(xiàn)代通信技術(shù)朝著高速、精確的方向發(fā)展,尤其是高速串行通信,逐漸成為通信技術(shù)的主流,在各行各業(yè)扮演著極其重要的角色,文中簡(jiǎn)述了高速I/O的相關(guān)技術(shù),如SERDES (串行器/解串器)

2010-09-22 08:32:48 51

51 利用RocketIO高速串行傳輸模塊將數(shù)字圖像和控制指令串行化,實(shí)現(xiàn)對(duì)高幀頻、多通道數(shù)字圖像的高速遠(yuǎn)程傳輸和反饋控制。利用Virtex2II Pro系列FPGA設(shè)計(jì)的光纖數(shù)字圖像傳輸模塊,可將

2010-09-22 08:34:12 36

36 摘 要:介紹了FPGA最新一代器件Virtex25上的高速串行收發(fā)器RocketIO。基于ML505開(kāi)發(fā)平臺(tái)構(gòu)建了一個(gè)高速串行數(shù)據(jù)傳輸系統(tǒng),重點(diǎn)說(shuō)明了該系統(tǒng)采用RocketIO實(shí)現(xiàn)1. 25Gbp s高速串行傳輸的設(shè)

2010-09-22 08:41:18 44

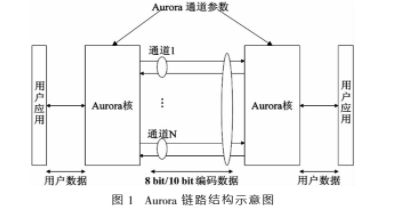

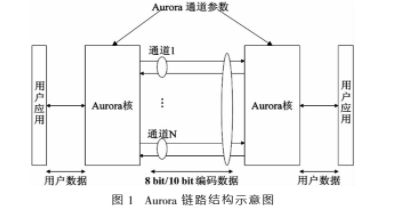

44 摘要: 串行傳輸技術(shù)具有更高的傳輸速率和更低的設(shè)計(jì)成本, 已成為業(yè)界首選, 被廣泛應(yīng)用于高速通信領(lǐng)域。提出了一種新的高速串行傳輸接口的設(shè)計(jì)方案, 改進(jìn)了Aurora 協(xié)議數(shù)據(jù)幀

2010-09-22 08:42:29 31

31 采用Xilinx 公司Virtex- II Pro 系列FPGA 內(nèi)嵌得SERDES 模塊———RocketIO 作為高速串行協(xié)議的物理層, 利用其8B/10B的編解碼和串化、解串功能, 實(shí)現(xiàn)了兩板間基于數(shù)據(jù)幀的簡(jiǎn)單高速串行傳輸

2010-09-22 08:44:28 28

28 為解決目前高速信號(hào)處理中的數(shù)據(jù)傳輸速度瓶頸以及傳輸距離的問(wèn)題,設(shè)計(jì)并實(shí)現(xiàn)了一種基于FPGA 的高速數(shù)據(jù)傳輸系統(tǒng),本系統(tǒng)借助Altera Cyclone III FPGA 的LVDS I/O 通道產(chǎn)生LVDS 信號(hào),穩(wěn)

2010-11-02 15:27:43 42

42 的FPGA技術(shù),推出ATLANTiS Rev 2.0(新TigerSHARC使用的高級(jí)傳輸鏈路架構(gòu))、I/O切

2006-03-13 13:00:52 1012

1012 中圖儀器CEM3000大空間適用性臺(tái)式掃描電鏡不僅抗振性能強(qiáng)、工業(yè)應(yīng)用能力高效,而且操作靈活和成像質(zhì)量可靠。通過(guò)加裝各類探頭和附件,滿足用戶的拓展性需求,這使其在材料科學(xué)、生命科學(xué)、納米技術(shù)、能源等

2024-10-22 16:54:40

??? 隨著人們對(duì)信息需求的不斷提高,高速串行傳輸憑借傳輸高的特性越來(lái)越受到市場(chǎng)的青睞,各種高速串行傳輸標(biāo)準(zhǔn)層出不窮,串行總線的傳輸速率也已經(jīng)達(dá)到甚至超過(guò)

2009-04-23 10:40:58 810

810 摘要: 介紹了采用Videx-ⅡPR0系列FPCA設(shè)計(jì)的應(yīng)用于下一代無(wú)線通信系統(tǒng)中的高速I/O。由于充分利用芯片中集成的Rocket I/O模塊,并采用差分輸入?yún)⒖紩r(shí)鐘、

2009-06-20 10:45:35 1632

1632

面對(duì)似乎層出不窮的新 I/O 標(biāo)準(zhǔn),目前嵌入式系統(tǒng)設(shè)計(jì)人員繼續(xù)依靠 FPGA 來(lái)部署系統(tǒng)日益重要的外部 I/O 接口,這點(diǎn)絲毫不足為奇。FPGA 可提供大量可配置的 I/O,能在適當(dāng) IP 基

2010-11-02 09:50:36 5446

5446 針對(duì) 2.5GHz 高速 串行信號(hào) 的特點(diǎn),本文在微波網(wǎng)絡(luò)理論的基礎(chǔ)上,對(duì)高速通道的各個(gè)部分進(jìn)行了精確的建模,推導(dǎo)出各個(gè)部分的散射參數(shù),最后對(duì)整個(gè)通道進(jìn)行了仿真,仿真數(shù)據(jù)和實(shí)際

2011-07-05 15:42:47 34

34 針對(duì)現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)芯片的特點(diǎn),研究FPGA中雙向端口I/O的設(shè)計(jì),同時(shí)給出仿真初始化雙向端口I/O的方法。采用這種雙向端口的設(shè)計(jì)方法,選用Xilinx的Spartan2E芯片設(shè)計(jì)一個(gè)多通道圖像信

2011-09-27 16:17:21 89

89 一名設(shè)計(jì)工程師怎樣才能真正充分利用串行I/O的各種技術(shù)呢?在開(kāi)始設(shè)計(jì)之前,我們需要知道什么對(duì)于實(shí)現(xiàn)串行I/O是有益的。我們需要研究一些基于串行設(shè)計(jì)的單元器件,從而了解一下

2012-04-01 15:01:36 29

29 隨著面向應(yīng)用的增加,單片機(jī)系統(tǒng)I/O端口數(shù)量有限的問(wèn)題日益突出。根據(jù)74HC164串行輸入、并行輸出的工作原理,對(duì)單片機(jī)系統(tǒng)的I/O端口進(jìn)行擴(kuò)展。設(shè)計(jì)具有16個(gè)按鍵的中斷串行鍵盤(pán)和具有

2013-09-09 17:09:41 86

86 一種基于FPGA的以太網(wǎng)高速傳輸平臺(tái),采用DM9000和FPGA芯片,實(shí)現(xiàn)100M以太網(wǎng)數(shù)據(jù)傳輸

2016-02-25 14:45:56 17

17 Delphi教程實(shí)現(xiàn)Windows95/98的I/O端口讀寫(xiě),很好的Delphi學(xué)習(xí)資料。

2016-03-16 14:59:35 6

6 基于FPGA的通用高速串行互連協(xié)議設(shè)計(jì)。

2016-05-11 09:46:01 18

18 引腳極高的靈活性(與ASIC相比)且低功耗想結(jié)合。 DDR-2400需要的性能增加了,但并沒(méi)有降低I/O引腳的運(yùn)行其他任務(wù)的性能,照樣以高速串行I/O端口運(yùn)行或者作為L(zhǎng)ED驅(qū)動(dòng)。此外

2017-02-09 09:53:07 389

389 NI可重配置I/O(RIO)產(chǎn)品可在靈活的開(kāi)發(fā)平臺(tái)上實(shí)現(xiàn)高精度測(cè)量,適用于需要高速閉環(huán)控制的系統(tǒng)級(jí)應(yīng)用。這些應(yīng)用有時(shí)需要比核心系統(tǒng)可提供的更多的通道數(shù)或分布更廣的架構(gòu)。而擴(kuò)展I/O系統(tǒng)可以實(shí)現(xiàn)1個(gè)

2017-11-18 02:44:01 6297

6297

。另外,用戶還可以使用NI VeriStand,通過(guò)基于FPGA 的I/O接口創(chuàng)建用戶自定義的I/O硬件。本文說(shuō)明了使用基于FPGA I/O接口的益處,以及如何同NI VeriStand一起使用它們。

2017-11-18 07:47:35 10135

10135

隨著FPGA應(yīng)用范圍的不斷擴(kuò)大以及對(duì)速度需求的不斷提升,集成高速串行模塊的FPGA已經(jīng)應(yīng)用于市場(chǎng)。以Xilinx的Virtex5系列為代表的集成GTPRocketIO模塊的FPGA受到廣泛關(guān)注。以

2018-07-20 11:42:00 2009

2009

32mb串行閃存133mhz多I/O SPI和四I/O QPI DTR接口數(shù)據(jù)手冊(cè)

2018-01-30 14:37:50 20

20 隨著第三代I/O技術(shù)的出現(xiàn),人們開(kāi)始步入高速傳輸的時(shí)代。在使用PCI Express、SATA等高速串行總線時(shí),如何保持信號(hào)的完整性是一個(gè)挑戰(zhàn)。本文結(jié)合實(shí)例,介紹信號(hào)完整性驗(yàn)證的基礎(chǔ)知識(shí)和方法。

2018-02-26 15:36:24 2784

2784

本章提供關(guān)于 PIC24H 器件系列的 I/O 端口的信息。所有器件引腳 (除 VDD、 VSS、 MCLR 和 OSC1/CLKI 外),均為外設(shè)與通用 I/O 端口所共用。

2018-06-25 05:20:00 2

2 本章提供關(guān)于 dsPIC33F 系列器件的帶外設(shè)引腳選擇的 I/O 端口的信息。所有的器件引腳 (除 VDD、 VSS、 MCLR 和 OSC1/CLKI 外),均為外設(shè)與通用 I/O 端口所共用。

2018-06-25 04:20:00 0

0 內(nèi)容包括:LabVIEW嵌入式產(chǎn)品族,FPGA技術(shù),FPGA在系統(tǒng)中的重要性,簡(jiǎn)化的FPGA范例,圖形化FPGA編程,圖形化功能仿真,通信與I/O,商業(yè)現(xiàn)成可用的硬件(COTS),常見(jiàn)應(yīng)用。

2018-06-25 13:01:00 5069

5069

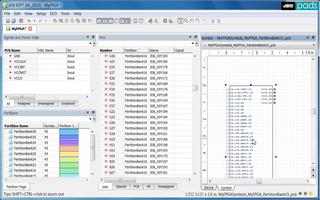

FPGA I/O 優(yōu)化功能提供了自動(dòng)化 FPGA 符號(hào)生成流程,該流程與原理圖設(shè)計(jì)和 PCB 設(shè)計(jì)相集成,可節(jié)省大量創(chuàng)建 PCB 設(shè)計(jì)的時(shí)間,同時(shí)提高原理圖符號(hào)的總體質(zhì)量和準(zhǔn)確性。

2019-05-20 06:16:00 3867

3867

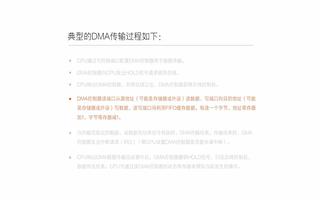

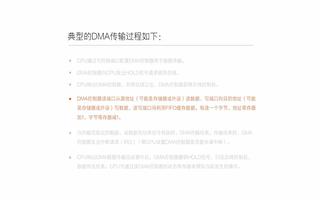

DMA方式主要適用于一些高速的I/O設(shè)備。這些設(shè)備傳輸字節(jié)或字的速度非常快。對(duì)于這類高速I/O設(shè)備,如果用輸入輸出指令或采用中斷的方法來(lái)傳輸字節(jié)信息,會(huì)大量占用CPU的時(shí)間,同時(shí)也容易造成數(shù)據(jù)的丟失。而DMA方式能使I/O設(shè)備直接和存儲(chǔ)器進(jìn)行成批數(shù)據(jù)的快速傳送。

2019-12-10 07:00:00 4093

4093

串行總線接口只能實(shí)現(xiàn)FPGA 和ARM 之間的低速通信 ;當(dāng)傳輸的數(shù)據(jù)量較大.要求高速傳輸時(shí),就需要用并行總線來(lái)進(jìn)行兩者之間的高速數(shù)據(jù)傳輸.

2019-08-08 15:37:50 7134

7134

加利福尼亞州圣地亞哥 - 董事會(huì)制造商 ACCES I/O產(chǎn)品正在推出其型號(hào)LPCI-COM-8SM 串行通信卡。它是一個(gè)八端口低配置 PCI 總線卡,可逐個(gè)端口提供異步現(xiàn)場(chǎng)可選的RS-232,RS-422和RS-485連接。

2019-09-15 17:47:00 4280

4280

,Xilinx提供的IBERT(Integrated Bit Error Ratio Tester)作為一種高速串行信號(hào)測(cè)試的輔助工具,使得測(cè)試更便捷,其具有不占用額外的I/O管腳和PCB空間、不破環(huán)接口信號(hào)的完整性、無(wú)干擾、使用簡(jiǎn)單和價(jià)格低廉等特點(diǎn)。

2020-07-10 10:11:17 7187

7187

在數(shù)字系統(tǒng)互連設(shè)計(jì)中,高速串行/O技術(shù)取代傳統(tǒng)的并行/O技術(shù)成為當(dāng)前發(fā)展的趨勢(shì)。與傳統(tǒng)并行丨/技術(shù)相比,串行方案提供了更大的帶寬、更遠(yuǎn)的距離、更低的成本和更高的擴(kuò)展能力,克服了并行l(wèi)/O設(shè)計(jì)存在的缺陷在實(shí)際設(shè)計(jì)應(yīng)用中,采用現(xiàn)場(chǎng)可編程門(mén)陣列FPGA實(shí)現(xiàn)高速串行接口是一種性價(jià)比較高的技術(shù)途徑。

2020-08-24 17:28:00 15

15 ATmega16的4個(gè)8位的端口都有各自對(duì)應(yīng)的3個(gè)I/O端口寄存器,它們占用了I/O空間的12個(gè)地址

2022-02-16 11:28:15 3576

3576

AD7769:CMOS模擬I/O端口數(shù)據(jù)Sheet

2021-04-17 09:23:13 0

0 AD8401:8位I/O端口數(shù)據(jù)Sheet

2021-04-20 09:21:01 0

0 介紹了基于模塊化方法在FPGA上實(shí)現(xiàn)高速通信的設(shè)計(jì)方案。系統(tǒng)在Aurora協(xié)議下采用高速串行收發(fā)器Rocket I/O,解決了不同

2021-05-05 14:35:00 11601

11601

AN-325:12位模擬I/O端口采用AD7549雙12位DAC和8051單片機(jī)

2021-05-08 09:57:13 5

5 本文主要介紹51單片機(jī)I/O端口P0、P1、P2、P3四個(gè)端口的內(nèi)部結(jié)構(gòu)電路圖和功能

2021-11-10 18:20:59 8

8 51單片機(jī)系列--并行I/O端口基本概念數(shù)據(jù)的傳送方式I/O 端口特性基本概念51系列單片機(jī)的每個(gè)端口都是8位準(zhǔn)雙向口,共占32位引腳。每個(gè)端口都包括一個(gè)鎖存器(一個(gè)D觸發(fā)器構(gòu)成)、一個(gè)輸出驅(qū)動(dòng)器

2021-11-20 11:21:05 12

12 CC2530并行I/O端口應(yīng)用CC2530總共具有21個(gè)數(shù)字I/O引腳,這些引腳可以組成3個(gè)8位端口,分別為端口0、端口1和端口2,通常表示為P0、P1和P2。其中,P0和P1是完全的8位端口,而

2021-11-29 21:06:03 7

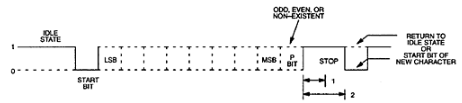

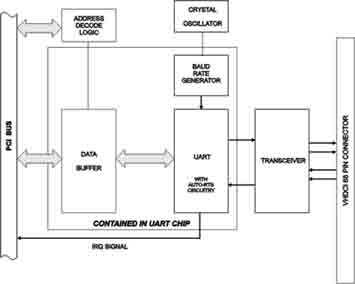

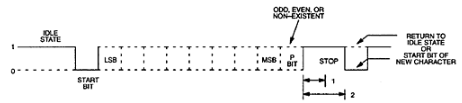

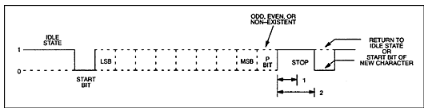

7 Maxim DS80C320和其他高速微控制器具有兩個(gè)相同的串行端口。本應(yīng)用筆記向用戶介紹微控制器中使用的通用同步/異步接收器/發(fā)送器(USART)。應(yīng)用筆記討論了波特時(shí)鐘源、輪詢和中斷模式、波特率生成、異步10位操作和雙串行端口操作。代碼示例用于突出顯示用作波特率生成器的計(jì)時(shí)器的使用。

2023-02-21 10:17:46 1607

1607

本應(yīng)用筆記描述了ESD如何威脅電子系統(tǒng)、造成的損壞類型、ESD的產(chǎn)生方式、使用的測(cè)試方法和波形、用于測(cè)試的人體和機(jī)器模型、IEC合規(guī)性水平、接觸和空氣放電。本文介紹了保護(hù)方法,詳細(xì)介紹了Maxim的ESD保護(hù)方法。給出了選擇具有高ESD電阻的IC的指南。RS-232 I/O 端口是專門(mén)考慮的。

2023-03-28 10:51:04 6623

6623

模擬DS80C320和其他高速微控制器具有兩個(gè)相同的串行端口。本應(yīng)用筆記向用戶介紹微控制器中使用的通用同步/異步接收器/發(fā)送器(USART)。應(yīng)用筆記討論了波特時(shí)鐘源、輪詢和中斷模式、波特率生成、異步10位操作和雙串行端口操作。代碼示例用于突出顯示用作波特率生成器的計(jì)時(shí)器的使用。

2023-06-13 14:52:35 958

958

中穎8bit 單片機(jī)I/O設(shè)置介紹

2023-10-27 15:41:08 1829

1829

點(diǎn)擊上方 藍(lán)字 關(guān)注我們 隨著網(wǎng)絡(luò)技術(shù)的不斷發(fā)展,數(shù)據(jù)交換、數(shù)據(jù)傳輸流量越來(lái)越大。尤其像雷達(dá),氣象、航天等領(lǐng)域,不僅數(shù)據(jù)運(yùn)算率巨大,計(jì)算處理復(fù)雜,而且需要實(shí)時(shí)高速遠(yuǎn)程傳輸,需要長(zhǎng)期穩(wěn)定有效的信號(hào)加以

2023-09-21 11:05:01 4898

4898

一、引言 高速串行傳輸技術(shù)是一種數(shù)據(jù)傳輸方式,通過(guò)在單一通道上按順序傳輸數(shù)據(jù),實(shí)現(xiàn)了高速、高效的數(shù)據(jù)交換。這種技術(shù)在通信、計(jì)算機(jī)和電子行業(yè)中發(fā)揮著重要作用,為信息時(shí)代的發(fā)展提供了強(qiáng)大的支持。 二

2024-05-31 16:02:41 1419

1419 高速信息傳輸在現(xiàn)代通信系統(tǒng)中起著至關(guān)重要的作用。串行和并行傳輸是兩種基本的數(shù)據(jù)傳輸方式。本文將詳細(xì)探討這兩種傳輸方式的特點(diǎn)、優(yōu)缺點(diǎn)以及在高速信息傳輸中的應(yīng)用。 1. 串行傳輸(Serial

2024-05-31 16:16:54 2870

2870 高速串行通信的“高速”一般比較高,基本至少都會(huì)上G。如果利用FPGA內(nèi)部的LUT、觸發(fā)器和普通IO是無(wú)法滿足這樣高的輸入輸出速率的。

2024-08-05 11:12:59 2243

2243

在計(jì)算機(jī)系統(tǒng)中,I/O接口與I/O端口是實(shí)現(xiàn)CPU與外部設(shè)備數(shù)據(jù)交換的關(guān)鍵組件,它們?cè)诠δ堋⒔Y(jié)構(gòu)、作用及運(yùn)作機(jī)制上均存在顯著差異,卻又相互協(xié)同工作,共同構(gòu)建起CPU與外部設(shè)備之間的橋梁。本文旨在深入探討I/O接口與I/O端口的定義、特性、功能及其區(qū)別,為讀者提供全面、深入的技術(shù)解析。

2025-02-02 16:00:00 3196

3196 MAX7325 2線串行接口外設(shè)具有16路I/O端口。其中8路為推挽輸出,另外8路為I/O端口,帶有可選擇的內(nèi)部上拉和瞬態(tài)檢測(cè)功能。8路I/O口可以用作邏輯輸入或漏極開(kāi)路輸出。所有端口均過(guò)壓保護(hù)至+6V。

2025-05-22 15:27:41 807

807

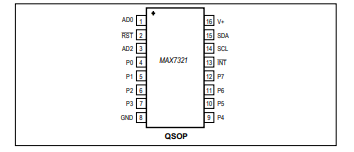

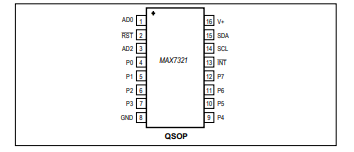

MAX7321 2線串行接口外設(shè)具有8個(gè)漏極開(kāi)路I/O口,可選擇內(nèi)部上拉和瞬態(tài)檢測(cè)功能。每個(gè)端口均可以配置成邏輯輸入和漏極開(kāi)路輸出端口。端口具有+6V過(guò)壓保護(hù),與電源電壓無(wú)關(guān)。

器件連續(xù)監(jiān)視

2025-05-23 11:41:16 783

783

探索DS32EL0421/DS32ELX0421:高速串行傳輸的理想之選 在高速數(shù)據(jù)傳輸的領(lǐng)域中,DS32EL0421和DS32ELX0421這兩款125 - 312.5 MHz FPGA

2025-12-25 16:30:12 92

92

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論