BittWare采用FPGA實現I/O開關,每簇通信量大于5

- Gbps(10007)

- Bitt(6098)

相關推薦

熱點推薦

virtio I/O通信流程及設備框架的實現

virtio 是一種通用的半虛擬化的 I/O 通信協議,提供了一套前后端 I/O 通信的的框架協議和編程接口。根據該協議實現的設備通過前后端的配合,相比全模擬設備可以大幅減少陷入陷出以及內存拷貝的次數,使 guest 獲得高效的 I/O 性能。

2022-03-10 13:37:10 8024

8024

8024

802489C51 單片機I/O 口模擬串行通信的實現方法 ·嚴天峰·

的方法是擴展一片8251 或 8250 通用同步/異步接收發送芯片(USART),需額外占用單片機I/O 資源。本文介紹一種用單片機普通I/O 口實現串行通信的方法,可在單片機的最小應用系統中實現與兩個

2012-06-07 15:17:42

5V Tolerant I/O的意思是STM32和5V供電的芯片可以直接通信嗎?

5V Tolerant I/O的意思是STM32和5V供電的芯片可以直接通信(不需要加電平轉換芯片)么?

2024-05-17 16:38:13

FPGA I/O架構朝向更高吞吐量要求方向演進

萊迪思半導體公司CPU 、ASIC和存儲器的設計者為了使器件擁有盡可能高的通信帶寬,他們在設計過程中充分利用I/O單元中的每一個晶體管來達到這個目標。這些器件常與FPGA相連接。因此,FPGA

2018-11-26 11:17:24

FPGA與DSP的高速通信接口設計與實現

并行處理的方式被普遍采用,它們共享總線以互相映射存儲空間,如果再與FPGA通過總線連接,勢必導致FPGA與DSP的總線競爭。同時采用總線方式與FPGA通信,DSP的地址、數據線引腳很多,占用FPGA的I

2018-12-04 10:39:29

FPGA與DSP的高速通信接口設計與實現

并行處理的方式被普遍采用,它們共享總線以互相映射存儲空間,如果再與FPGA通過總線連接,勢必導致FPGA與DSP的總線競爭。同時采用總線方式與FPGA通信,DSP的地址、數據線引腳很多,占用FPGA的I

2019-06-19 05:00:08

FPGA中的I_O時序優化設計

FPGA中的I_O時序優化設計在數字系統的同步接口設計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優化設計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

FPGA的I/O與外設的連接擴展要點

外設電路(I/O應用)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCttFPGA器件擁有著豐富的I/O資源,它

2019-04-12 06:35:33

FPGA設計筆記:QSPI Flash與DDR3L SDRAM采用同一I/O分區

行,速度快。Xilinx Spartan-7 FPGA器件適用于那些成本敏感型應用。它采用小型封裝卻擁有高比例的I/O數量,單位功耗性價比相較前代產品提升多達四倍,可提供靈活的連接能力、接口橋接和輔助芯片

2018-08-02 09:37:08

采用FPGA來實現SVPWM調制算法

1. 為什么要使用FPGA實現在全控型電力電子開關器件出現以后,為了改善交流電動機變壓變頻調速系統的性能,科技工作者在20世紀80年代開發出了應用脈寬調制(PWM)技術的變壓變頻器,由于它的優良

2022-01-20 09:34:26

采用Cyclone III FPGA實現DDR2接口設計

CAS。我們的設計(圖1)采用Altera公司Cyclone III系列型號為EP3C16F484C6N的FPGA作為控制器,以Micron公司生產的型號為MT47H16M16BG-5E(16M

2019-05-31 05:00:05

采用FT245BM和FPGA實現USB接口設計

USB數據與并行I/O口數據的交換緩沖區。FIFO實現與外界(微控制器、FPGA或其它器件)的接口,主要通過8根數據線D0~D7、讀寫控制線RD#和WR#以及FIFO發送緩沖區空標志TXE#和FIFO接收

2019-04-22 07:00:07

采用FT245BM和FPGA實現USB接口設計

USB數據與并行I/O口數據的交換緩沖區。FIFO實現與外界(微控制器、FPGA或其它器件)的接口,主要通過8根數據線D0~D7、讀寫控制線RD#和WR#以及FIFO發送緩沖區空標志TXE#和FIFO接收

2019-04-26 07:00:12

采用LabVIEW FPGA模塊和可重新配置I/O設備開發測量與控制應用

使用LabVIEW FPGA 模塊和可重新配置I/O 設備開發測量與控制應用通過使用LabVIEW FPGA 模塊和可重新配置I/O(RIO)硬件,NI 為您提供了一種直觀可用的解決方案,它可以將

2009-07-23 08:15:57

SEP3203處理器實現FPGA數據通信接口設計

與FPGA的接口電路設計2.1 硬件設計系統中的FPGA輸入時鐘由外部晶振提供,為20MHz。FPGA的復位信號通過SEP3203的I/O口實現。本系統有2個觸發信號:硬件觸發信號和軟件觸發信號。硬件觸發

2019-04-26 07:00:06

labview怎么實現像PLC一樣通過I/O控制外部開關量?

labview怎么實現像plc一樣的通過輸入輸出I/O量,控制開關量,比如通過I/O點控制繼電器的吸合。怎么給I/O量分配地址,怎么在程序里使用這些變量實現一系列有序的動作。希望能附上一份樣例程序,讓小弟學習領會,請多指教,謝謝。

2016-04-25 00:51:33

使用XILINX的ROCKET I/O 實現150M的光纖通信合適/可行嗎?

要使用FPGA實現150M的光纖通訊,使用XILINX XAPP244的串行數據恢復功能感覺有些麻煩。使用XILINX的ROCKET I/O 實現150M的光纖通信合適/可行嗎?

2013-03-26 16:06:30

基于FPGA的CPCI總線多功能通信卡的設計

圖2所示。2.2 總線接口設計本設計中采用32bit/33 MHz CPCI總線接口,其傳輸率可達133MB/s,實現了設備之間的高速通信。通過CPCI連接器,CPCI總線信號與FPGA的I/O口互連

2016-01-14 10:59:18

基于能量和距離的無線傳感器網絡分簇路由算法研究

的區別。每輪選出的第一層簇頭成為第二層簇頭的普通節點,在LEACH中這些節點直接與基站通信。由式(1)可以看出,放大器能耗遠大于電路能耗,且放大器能耗中與通信距離d有直接關系,因此在產生第二層簇頭

2018-11-02 15:19:38

如何通過JTAG監控PC中FPGA I / O的狀態?

嗨專家,我正在使用Spartan3AN(XC3S50AN)FPGA板和平臺線USB II。你能告訴我如何通過JTAG監控PC中FPGA I / O的狀態嗎?謝謝,V。Prakash以上來自于谷歌翻譯

2019-06-18 09:05:14

建立專屬的LabVIEW FPGA I/O

趨勢,而 NI FlexRIO 正是重要的下一步。透過可互換的轉接器模組,工程師可確實針對 I/O 需求建立解決方案。再整合 LabVIEW FPGA 與 Virtex-5 FPGA 系統的強大架構,即便是為復雜的設計與測試應用,NI FlexRIO 亦可提供圖形化系統設計 (GSD) 的彈性。

2019-04-28 10:04:14

怎么使用FPGA實現SPI總線的通信接口?

隨著現代技術的發展,SPI接口總線已經成為了一種標準的接口,由于協議實現簡單,并且I/O資源占用少,為此SPI總線的應用十分廣泛。目前,SPI接口的軟件擴展方法雖然簡單方便,但若用來通信,則速度

2019-08-09 08:14:34

檢查FPGA的FPGA功能和I/O引腳的方法

大家好,我想檢查FPGA功能和I / O引腳功能在我的主板上使用“Selftest application”。在我的Selftest應用程序中,我可以使用哪些方法來檢查這些?請提供一些想法。謝謝

2019-04-01 12:33:26

淺談如何克服FPGA I/O引腳分配挑戰

需要進行調整,在采用這一方法晨這些問題通常也已經局部化了,只需要在PCB或FPGA設計中進行很小的設計修改。

步驟1: 評估設計參數

那么,從哪里開始呢? 首先應當盡早制定I/O分配策略。 但沒有優化

2024-07-22 00:40:11

深入理解 FPGA 的基礎結構

簇中 BLE 的數量 N,邏輯塊的面積只按二次函數增長。

2、I/O 塊的結構

I/O

塊放置在芯片的外圍。FPGA 的 I/O 口除了固定用途的電源、時鐘等專用引腳,還有用戶可以配置的用戶 I/O

2024-04-03 17:39:53

請問VIRTEX-6 FPGA的I / O支持的最大數據速率是多少?

VIRTEX-6 FPGA的I / O支持的最大數據速率是多少?我想在Virtex-6的I / O接收625MSPS的數據。這可以實現嗎?

2020-07-13 09:45:20

輕松實現高速串行I/O (FPGA應用設計者指南)

輕松實現高速串行I/OFPGA應用設計者指南輸入/輸出(I/O)在計算機和工業應用中一直扮演著關鍵角色。但是,隨著信號處理越來越復雜,I/O通信會變得不可靠。在早期的并行I/O總線中,接口的數據對齊

2020-01-02 12:12:28

通過FPGA實現溫控電路接口及其與DSP通信接口的設計

是整個溫控系統的硬件基礎,其中涉及到溫度采集,與微處理器通信,串口輸出,控制數模轉換芯片等多個組成部分。本文提出一種高效實用的FPGA接口設計,它能夠完成協調各個組成部分有序工作,準確、快速實現數據傳輸

2020-08-19 09:29:48

MANET分簇節點組通信功能的設計與實現

提出一種將源路由(DSR)協議與自適應按需加權(AOW)分簇算法相結合的Ad hoc網絡體系結構設計方案。利用AOW算法進行分簇,將簇半徑嚴格控制在1跳以內,簇內成員無需路由功能,大大減

2009-04-14 09:40:05 15

15

15

15使用LabVIEW FPGA模塊和可重新配置I/O設備開發測

使用 LabVIEW FPGA 模塊和可重新配置I/O 設備開發測量與控制應用通過使用LabVIEW FPGA 模塊和可重新配置I/O(RIO)硬件,NI 為您提供了一種直觀可用的解決方案,它可以將FPGA技術的靈活性

2009-07-23 08:09:28 68

68

68

68數字I/O介紹

數字I/O腳有專用和復用。數字I/O腳的功能通過9個16位控制寄存器來控制。控制寄存器分為兩類:(1)I/O復用控制寄存器(MCRX),來選擇I/O腳是外設功能還是I/O功能。(

2009-09-16 12:20:48 19

19

19

19選擇適合您FPGA系統的I/O體系結構

選擇適合您FPGA系統的I/O體系結構:即使在幾年前, 設計師還主要是把FPGA作為設計原型的工具。但隨著近十年來FPGA 數據速率的迅速提高, 現在已完全能與CMOS ASIC相匹敵。系統性能的急

2009-11-20 17:41:32 21

21

21

21EDA9060開關量I/O 模塊在電氣控制柜中的典型應用

EDA9060開關量I/O 模塊在電氣控制柜中的典型應用—— EDA9060結合交流接觸器實現遠程控制EDA9060開關量I/O模塊是山東力創科技自主研發的一款分布式DI/DO工控模塊,主

2009-12-07 13:42:34 44

44

44

44冗余I/O

6.1 冗余I/O的定義當I/O模塊以每兩個一組組態成冗余對運行時,I/O模板即認為是冗余配置。這樣意味著S7-400H系統的所有元件都可以冗余。使用冗余I/O可以使H系統提高可用性。6.2

2010-07-23 00:29:04 26

26

26

26基于Rocket I/O模塊的高速I/O設計

摘要: 介紹了采用Videx-ⅡPR0系列FPCA設計的應用于下一代無線通信系統中的高速I/O。由于充分利用芯片中集成的Rocket I/O模塊,并采用差分輸入參考時鐘、

2009-06-20 10:45:35 1632

1632

1632

1632

什么是I/O地址

什么是I/O地址

I/O地址中I是input的簡寫,O是output的簡寫,也就是輸入輸出地址。每個設備都會有一個專用的I/O地址(如圖 ),用來處理自己的輸入輸

2010-02-05 10:01:50 1464

1464

1464

1464什么是通信量控制/管理器

什么是通信量控制/管理器

通信量控制器CC(Communication Controller):CC是用以對數據信息各個階段進行控制的設備。

2010-03-26 15:52:15 1005

1005

1005

1005基于FMC標準的FPGA夾層卡I/O設計

面對似乎層出不窮的新 I/O 標準,目前嵌入式系統設計人員繼續依靠 FPGA 來部署系統日益重要的外部 I/O 接口,這點絲毫不足為奇。FPGA 可提供大量可配置的 I/O,能在適當 IP 基

2010-11-02 09:50:36 5446

5446

5446

5446免費的I/O改進FPGA時鐘分配控制

本文將探討FPGA時鐘分配控制方面的挑戰,協助開發團隊改變他們的設計方法,并針對正在考慮如何通過縮小其時鐘分配網絡的規模來擁有更多的FPGA I/O,或提高時鐘網絡性能的設計者們

2011-03-30 17:16:32 1241

1241

1241

1241遠程智能I/O裝置在DCS中的應用

針對目前分散控制系統( DCS ) 中I/ O 點設計過多而導致的系統資源浪費問題,提出了采用遠程智能I/O 裝置實現數據采集,并簡要介紹了遠程智能I/ O 裝置的構成、性能,以及與DCS 實現聯網通

2011-06-17 17:42:34 26

26

26

26XAPP520將符合2.5V和3.3V I/O標準的7系列FPGA高性能I/O Bank進行連接

XAPP520將符合2.5V和3.3V I/O標準的7系列FPGA高性能I/O Bank進行連接 The I/Os in Xilinx 7 series FPGAs are classified

2012-01-26 18:47:15 75

75

75

75采用高速串行端口的I/O bit傳輸比FPGA仿真有更廣的適用性

作者:Steve Leibson, 賽靈思戰略營銷與業務規劃總監 Luis Bielich所撰寫的名為Zero Latency Multiplexing I/O for ASIC Emulation

2017-02-08 02:18:33 552

552

552

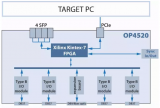

552OP4520 FPGA處理器和I/O擴展單元助推您的項目

,eMEGAsim,HYPERSIM,和ePHASORsim。 OP4520是緊湊型I/O擴展單元配置,具備以下特點: FPGA芯片上實現250納秒仿真步長的實時仿真 擁有326080個邏輯單元以及

2017-02-09 01:18:11 643

643

643

643

Java I/O 的相關方法分析

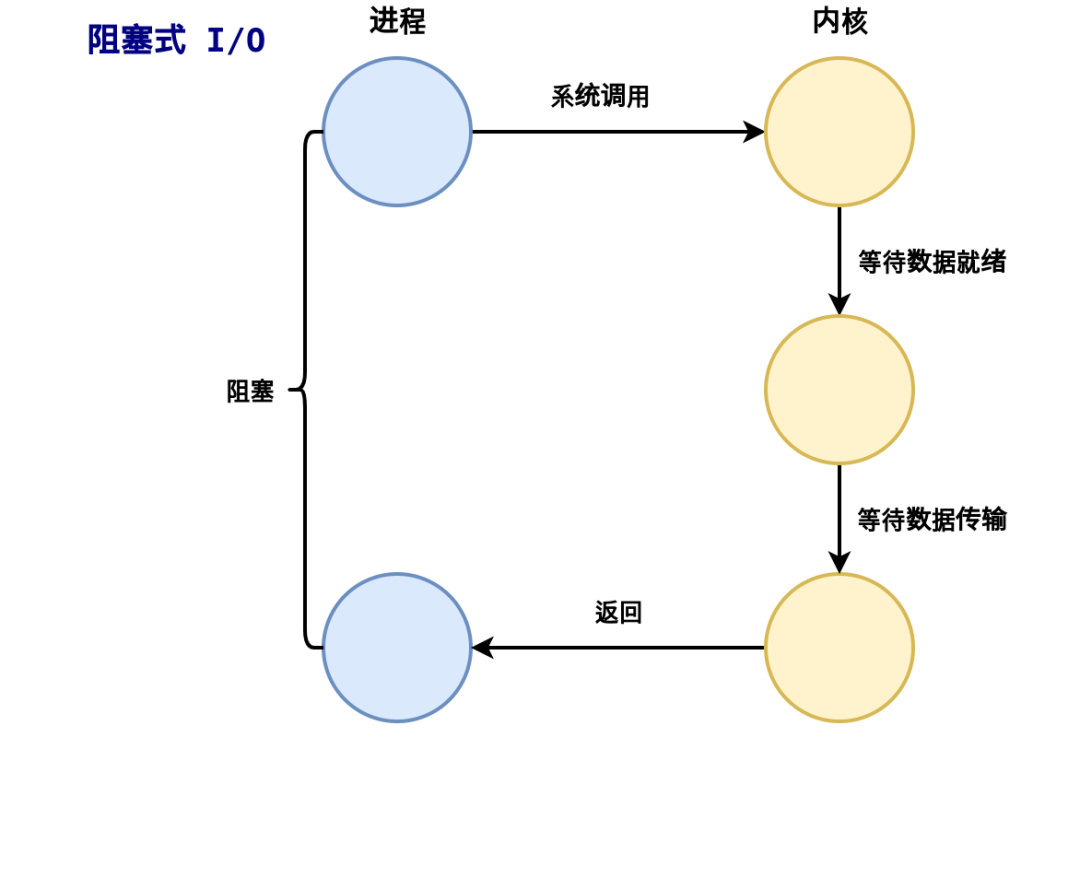

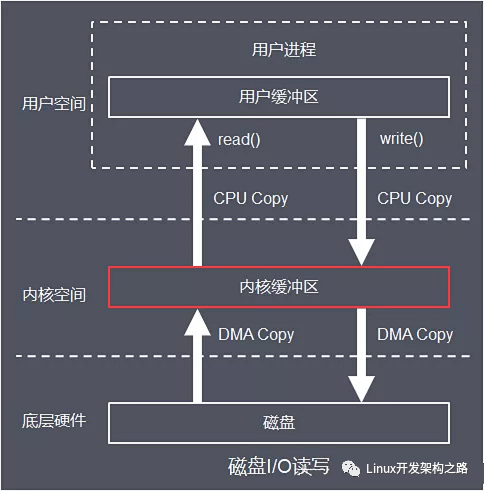

I/O,即 Input/Output(輸入/輸出) 的簡稱。就 I/O 而言,概念上有 5 種模型:blocking I/O,nonblocking I/O,I/O multiplexing

2017-09-27 13:18:14 0

0

0

0FPGA設計約束技巧之XDC約束之I/O篇(下)

XDC中的I/O約束雖然形式簡單,但整體思路和約束方法卻與UCF大相徑庭。加之FPGA的應用特性決定了其在接口上有多種構建和實現方式,所以從UCF到XDC的轉換過程中,最具挑戰的可以說便是本文將要

2017-11-17 19:01:00 8139

8139

8139

8139

LabVIEW的RIO與I/O對比

對N個的系統拓撲結構,該拓撲結構使用一個控制器、“N”個現場可編程門陣列(FPGA)和多個I/O節點構成,該結構用于實現靈活的高通道數系統,這樣的系統可以執行分布式控制和本地化處理。

2017-11-18 02:44:01 6297

6297

6297

6297

基于FPGA I/O接口的五大優勢與FPGA深層分析

NI VeriStand是一款用于配置實時測試系統應用的軟件環境,如硬件在環(HIL)測試系統等。當向NI VeriStand添加實時I/O接口時,用戶能夠快速配置多種標準模擬、數字和通信總線接口

2017-11-18 07:47:35 10135

10135

10135

10135

BittWare發布FPGA服務器_服務器I/O帶寬竟達到驚人的3.2Tbps!

你相信一臺服務器的I/O帶寬可以達到3.2Tbps嗎?BittWare最新發布的TeraBox 1432D 1U FPGA服務器,一款提供32個100GbE的QSFP 端口,通過它們,帶寬可以達到驚人的3.2Tbps。很吃驚,對吧!大家肯定迫不及待地想要了解這是一款什么樣的服務器了吧?

2018-06-28 07:48:00 5050

5050

5050

5050Lattice ECP5和ECP5-5G FPGA系列VIP處理器解決方案

lattice公司的ECP5/ECP5-5G FPGA系列提供了高性能特性如增強DSP架構,高速SERDES和高速源同步接口,采用40nm技術,使得器件非常適合于量大高速和低成本的應用.器件的查找表

2018-04-06 10:19:00 13531

13531

13531

13531

如何減少器件間通信所用的I/O引腳數實現雙向通信

隨著嵌入式系統的小型化趨勢,市場對減少器件間通信所用的I/O 引腳數的需求與日俱增。Microchip 開發的UNI/O? 總線滿足了這一需求,這一低成本且易于實現的解決方案,僅需要使用一個I/O 引腳就可實現雙向通信。

2018-04-27 16:14:24 8

8

8

8介紹 I/O NI系統,C系列的I/O模塊

內容包括:理想的確定性以太網I/O,具有確定性分布式I/O的NI系統,C系列的I/O模塊,與LabVIEW的無縫集成,

2018-06-14 06:19:00 5059

5059

5059

5059

FPGA器件的I/O引腳布局的優化方案分析

對于需要在PCB板上使用大規模FPGA器件的設計人員來說,I/O引腳分配是必須面對的眾多挑戰之一。 由于眾多原因,許多設計人員發表為大型FPGA器件和高級BGA封裝確定I/O引腳配置或布局方案越來越困難。 但是組合運用多種智能I/O規劃工具,能夠使引腳分配過程變得更輕松。

2019-06-03 08:06:00 3627

3627

3627

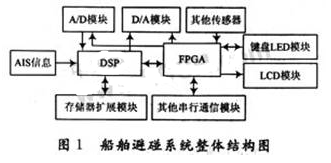

3627采用DSP和FPGA實現船舶自動避碰系統的設計

功能,實現外圍輸入輸出接口如其他串行口、ADC數據采集緩存等硬件電路,使部分數據采集和數據通信的I/O任務由DSP和FPGA協同承擔,從而使DSP減輕負擔,可以更專注于避碰的復雜算法。FPGA還可以實現

2020-05-13 07:57:00 2679

2679

2679

2679

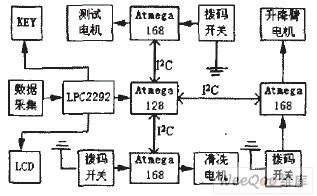

如何通過I2C總線I/O口實現系統的多個功能?

儀器的開發領域得到了廣泛應用,本文介紹了一個測試系統通過FC總線擴展I/O口實現了系統的多個功能。給出了系統的硬件連接以及Atmega128與三個Atmega168之間的軟件通信流程圖。

2018-08-30 10:05:12 7144

7144

7144

7144

使用Kintex-7 FPGA實現最佳的每瓦性能

憑借Kintex?-7 FPGA系列,Xilinx可實現每瓦性價比的理想平衡。

通過提供具有競爭力的價位的高端功能,如尖端收發器和高速集成IP,Kintex-7 FPGA是理想的選擇。

2018-11-28 06:25:00 3590

3590

3590

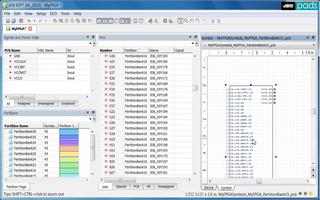

3590FPGA I/O優化功能自動生成FPGA符號

FPGA I/O 優化功能提供了自動化 FPGA 符號生成流程,該流程與原理圖設計和 PCB 設計相集成,可節省大量創建 PCB 設計的時間,同時提高原理圖符號的總體質量和準確性。

2019-05-20 06:16:00 3867

3867

3867

3867

Achronix和BittWare推出采用FPGA芯片的加速卡

近日,基于現場可編程門陣列(FPGA)的數據加速器件和高性能嵌入式FPGA(eFPGA)半導體知識產權(IP)領導性企業Achronix半導體公司,與Molex旗下的一家領先企業級FPGA加速器產品供應商BittWare今日聯合宣布:推出一類全新的、面向高性能計算和數據加速應用的FPGA加速卡。

2019-10-31 15:11:33 1229

1229

1229

1229Achronix與BittWare共同研發FPGA芯片VectorPath加速卡

Achronix半導體公司與Mo-lex旗下FPGA加速器產品供應商BittWare聯合推出全新的、面向高性能計算和數據加速應用的FPGA加速卡,可實現云計算與邊緣計算加速,助力高帶寬應用。

2019-11-08 15:07:23 910

910

910

910BittWare和Achronix合作推出采用7納米的Speedster7t FPGA

Molex旗下的 BittWare 公司是一家領先的企業級 FPGA 加速卡產品的供應商,產品適合各種高要求的計算、網絡及存儲應用使用,公司宣布已經與 Achronix 半導體公司達成戰略協作關系

2019-11-19 15:03:11 931

931

931

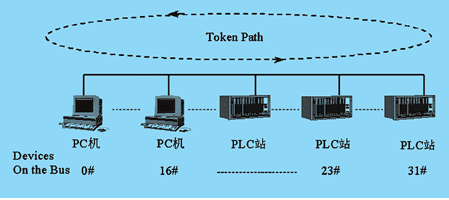

931Geinus I/O總線的特性、網絡實現及應用分析

geinus i/o總線是美國ge fanuc自動化公司推出的一種工業控制總線,它既是i/o總線又是通信網絡,非常適合于大量i/o處理和數據傳輸。可作為一個網絡、或作為一個交換實時信息的高速局域通信網絡而進行工作,對安裝在不同位置上的i/o系統進行控制。

2020-04-02 09:33:15 2952

2952

2952

2952

BittWare新型200DE邊緣服務器,實現一流的FPGA加速功能

Molex旗下BittWare 公司是企業級 FPGA 加速器產品領域一家領先的供應商,現推出全新的TeraBox? 200DE邊緣服務器。TeraBox 服務器產品系列是專為數據中心提供的領先產品

2020-04-21 15:17:32 4129

4129

4129

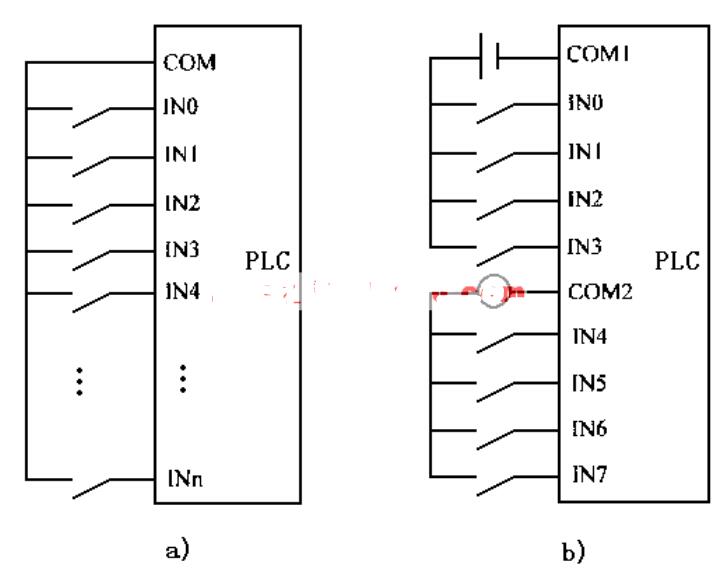

4129PLC的I/O模塊如何選擇

一般I/O模塊的價格占PLC價格的一半以上。PLC的I/O模塊有開關量I/O模塊、模擬量I/O模塊及各種特殊功能模塊等。不同的I/O模塊,其電路及功能也不同,直接影響PLC的應用范圍和價格,應當根據實際需要加以選擇。

2020-05-19 08:54:16 10599

10599

10599

10599

單片機如何通過I/O口實現斷電自關機

單片機應用系統中,常有用單片機的I/O口來實現自關機(徹底關機)的功能。一般用單片機的一個I/O口控制一個電子開關來實現,因單片機關電后,失去電源,所以在關機時,實現關機的IO口的電平必須用低電平。

2020-09-08 13:53:00 6105

6105

6105

6105

如何使用環分塊實現能耗均衡分簇路由算法

,優化每環的簇數目,并對每環進行均勻分塊,且在每塊中選取能量最高的節點擔任簇頭,以均衡網絡能耗;最后,設計傳輸代價函數,搜索簇頭和匯聚節點之間數據的最佳傳輸路徑,以提高網絡能量效率。仿真結果表明,EBCR-RP與模糊理論簇形成協議(

2021-01-15 16:55:00 11

11

11

11Linux中如何使用信號驅動式I/O?

一、Linux 的 5 種 IO 模型 二、如何使用信號驅動式 I/O? 三、內核何時會發送 “IO 就緒” 信號? 四、最簡單的示例 五、擴展知識 一、Linux 的 5 種 IO 模型 阻塞式

2021-03-12 14:47:30 2953

2953

2953

2953

BittWare擴展其采用IntelAgilex FPGA的IA-系列FPGA加速器

Molex莫仕公司旗下的BittWare是致力于邊緣計算和云計算應用企業級加速器的領先供應商,宣布擴展其采用IntelAgilex FPGA的IA-系列FPGA加速器。BittWare的IA系列

2021-06-25 17:58:50 3850

3850

3850

3850基于英特爾?AGILEX? FPGA和SOC FPGA的BittWare加速“雙星”發布

BittWare 在之前發布的 IA-840F 企業級 FPGA 加速器中添加了兩款基于英特爾 Agilex FPGA 和 SoC FPGA 的新加速器產品(詳見此前報道)。 全新的 IA-420F

2021-06-30 10:48:07 2706

2706

2706

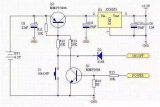

2706可靠的邏輯高電平I/O電路

可靠的邏輯高電平I/O電路(輸入) 微控制器I/O端口線能承受的最大電壓不超過5V(不同微控制器有所區別),否則有可能燒壞I/O端口。本電路中,即使使用較大的電源電壓,分壓網絡也會送一個安全的(5

2021-08-16 14:52:33 9694

9694

9694

9694

單片機如何通過I/O口實現斷電自關機

單片機應用系統中,常有用單片機的I/O口來實現自關機(徹底關機)的功能。一般用單片機的一個I/O口控制一個電子開關來實現,因單片機關電后,失去電源,所以在關機時,實現關機的IO口的電平必須用低電平。

2022-02-09 10:42:12 4

4

4

4單片機如何通過I/O口實現斷電自關機

單片機應用系統中,常有用單片機的I/O口來實現自關機(徹底關機)的功能。一般用單片機的一個I/O口控制一個電子開關來實現,因單片機關電后,失去電源,所以在關機時,實現關機的IO口的電平必須用低電平。

2022-02-09 11:17:27 4

4

4

4如何實現單片機用一個I/O采集多個按鍵信號?

普通I/O口的話,只能檢測識別一個按鍵。

日常設計中,如果碰到按鍵數量較多的話,會采用行列式鍵盤,例如最常見的4X4矩陣鍵盤,這樣可以實現用8個I/O口檢測16個按鍵。

還有就是鍵盤接口,...

2022-02-11 14:23:22 11

11

11

11基于Intel Agilex FPGA的新型存儲卡和服務器級解決方案

BittWare還新增了Intel I系列FPGA產品,推出支持高性能接口的IA-440i和IA-640i加速器,包括400G以太網和PCIeGen 5。這些最新的型號與BittWare現有的IntelAgilex F系列產品相得益彰,是市場上數一數二基于FPGA的最廣泛IntelAgilex產品組合之一。

2022-08-04 15:38:32 879

879

879

879工業遠程I/O模塊CANopen I/O模塊產品概述

Mxxc系列CANopen工業I/O數據采集模塊按照苛刻的工業應用環境需求而設計,廣泛應用于各種工業自動化生產、安防監控系統、自動化測量與控制系統中。用戶可以采用不同的I/O的模塊,來擴展IO,實現現場擴展控制和數據采集。

2022-12-30 14:00:14 1446

1446

1446

1446XDC約束技巧之I/O篇(上)

《XDC 約束技巧之時鐘篇》中曾對 I/O 約束做過簡要概括,相比較而言,XDC 中的 I/O 約束雖然形式簡單,但整體思路和約束方法卻與 UCF 大相徑庭。加之 FPGA 的應用特性決定了其在接口

2023-04-06 09:53:30 2523

2523

2523

2523基于FPGA的PCIE I/O控制卡通信方案

本文介紹一個FPGA 開源項目:PCIE I/O控制卡。上一篇文章《FPGA優質開源項目– PCIE通信》開源了基于FPGA的PCIE通信Vivado工程,用于實現上位機通過PCIE接口訪問FPGA的DDR3以及RAM內存數據。PCIE I/O控制卡工程是在上一個工程的基礎上進行了部分模塊和參數的修改。

2023-09-01 16:18:36 5107

5107

5107

5107

Linux I/O 接口的類型及處理流程

()、lseek() 等。 網絡 I/O 接口:用于網絡通信的接口,包括 socket()、connect()、bind()、listen()、accept() 等。 設備 I/O 接口:用于對設備(e.g. 字符

2023-11-08 16:43:02 2048

2048

2048

2048

FANUC外部I/O點數不夠用了怎么辦?可以擴展I/O點數嗎?

FANUC外部I/O點數不夠用了怎么辦?可以擴展I/O點數嗎? 擴展FANUC的外部I/O點數是一種常見的需求,這可以通過一些方法來實現。 在FANUC控制系統中,I/O模塊被用于將外部設備與控制器

2024-02-18 15:21:47 3600

3600

3600

3600Bittware提供開放式FPGA堆棧和支持英特爾?oneAPI的加速卡

通過使用開放式 FPGA 堆棧 (OFS) ,BittWare 在其 FPGA 解決方案上提供對 oneAPI 的支持。

2024-03-29 14:57:03 1393

1393

1393

1393

BittWare提供基于英特爾Agilex? 7 FPGA最新加速板

BittWare 當前的加速板產品組合包括最新的英特爾 Agilex 7 FPGA F、I 和 M 系列,包括 Compute Express Link (CXL) 和 PCIe* 5.0

2024-04-30 15:22:10 1658

1658

1658

1658

I/O接口與I/O端口的區別

在計算機系統中,I/O接口與I/O端口是實現CPU與外部設備數據交換的關鍵組件,它們在功能、結構、作用及運作機制上均存在顯著差異,卻又相互協同工作,共同構建起CPU與外部設備之間的橋梁。本文旨在深入探討I/O接口與I/O端口的定義、特性、功能及其區別,為讀者提供全面、深入的技術解析。

2025-02-02 16:00:00 3196

3196

3196

3196 電子發燒友App

電子發燒友App

評論